Программно-управляемый цифровой фильтр

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1513475

Авторы: Парижский, Петрова, Шполянский

Текст

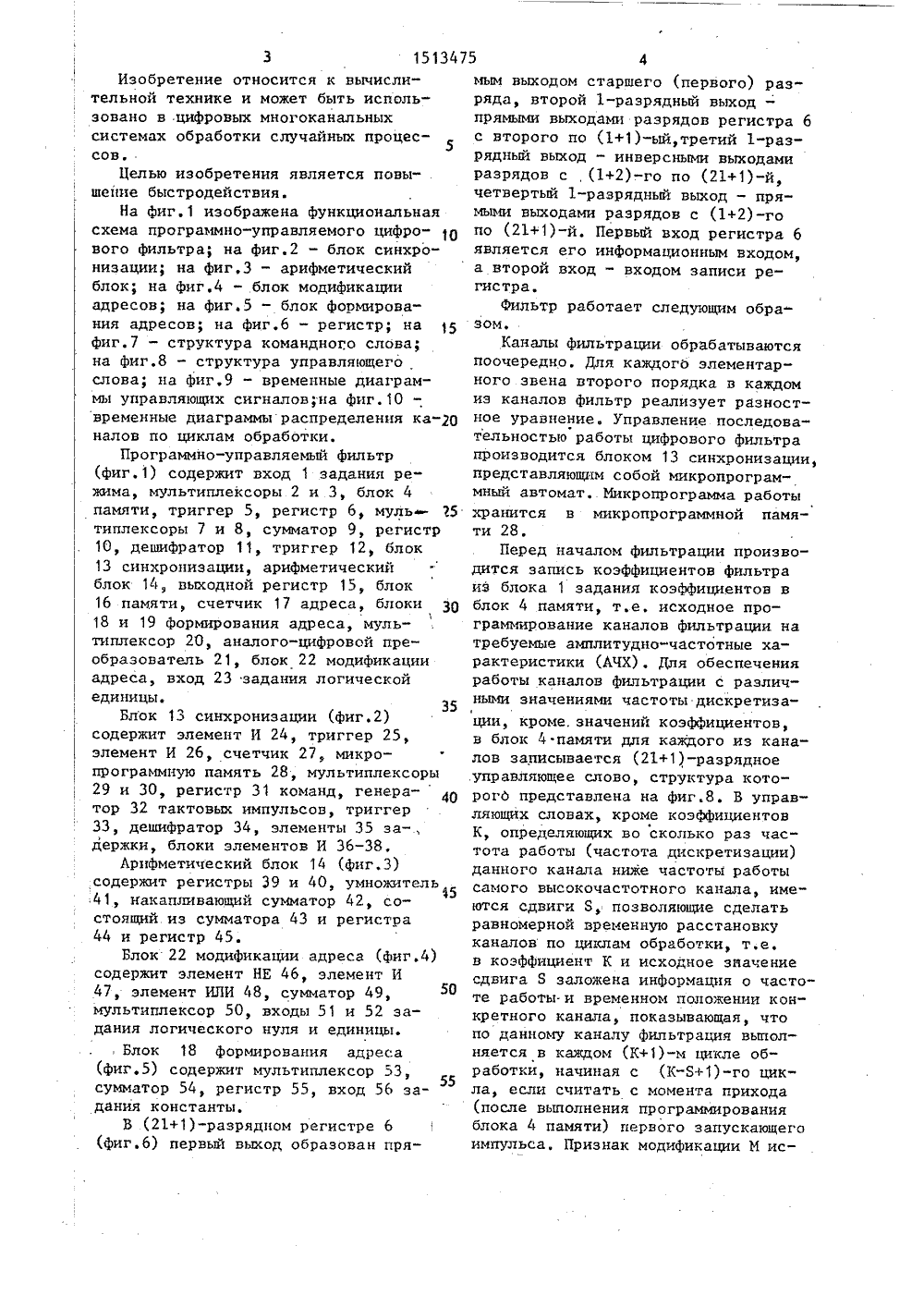

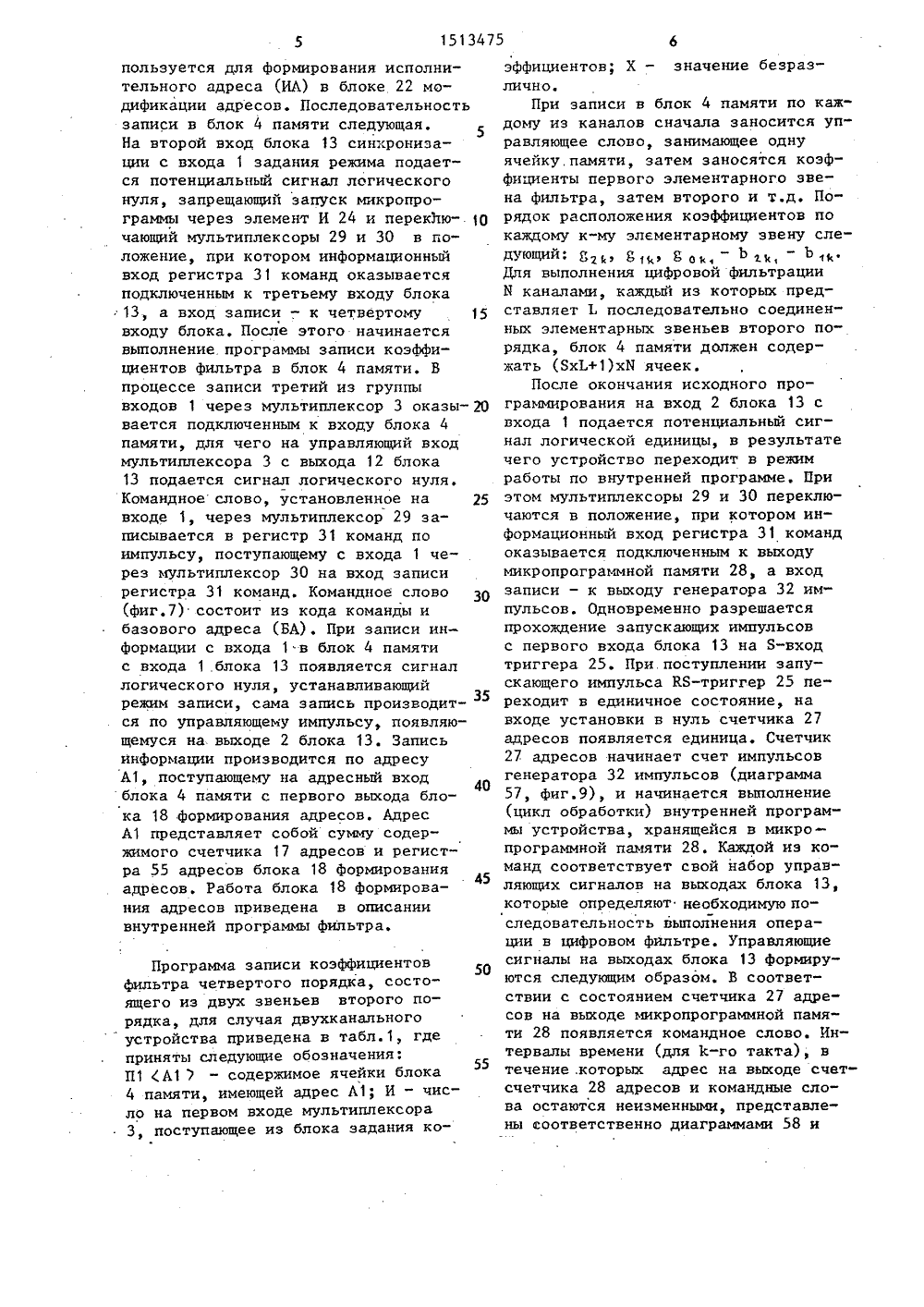

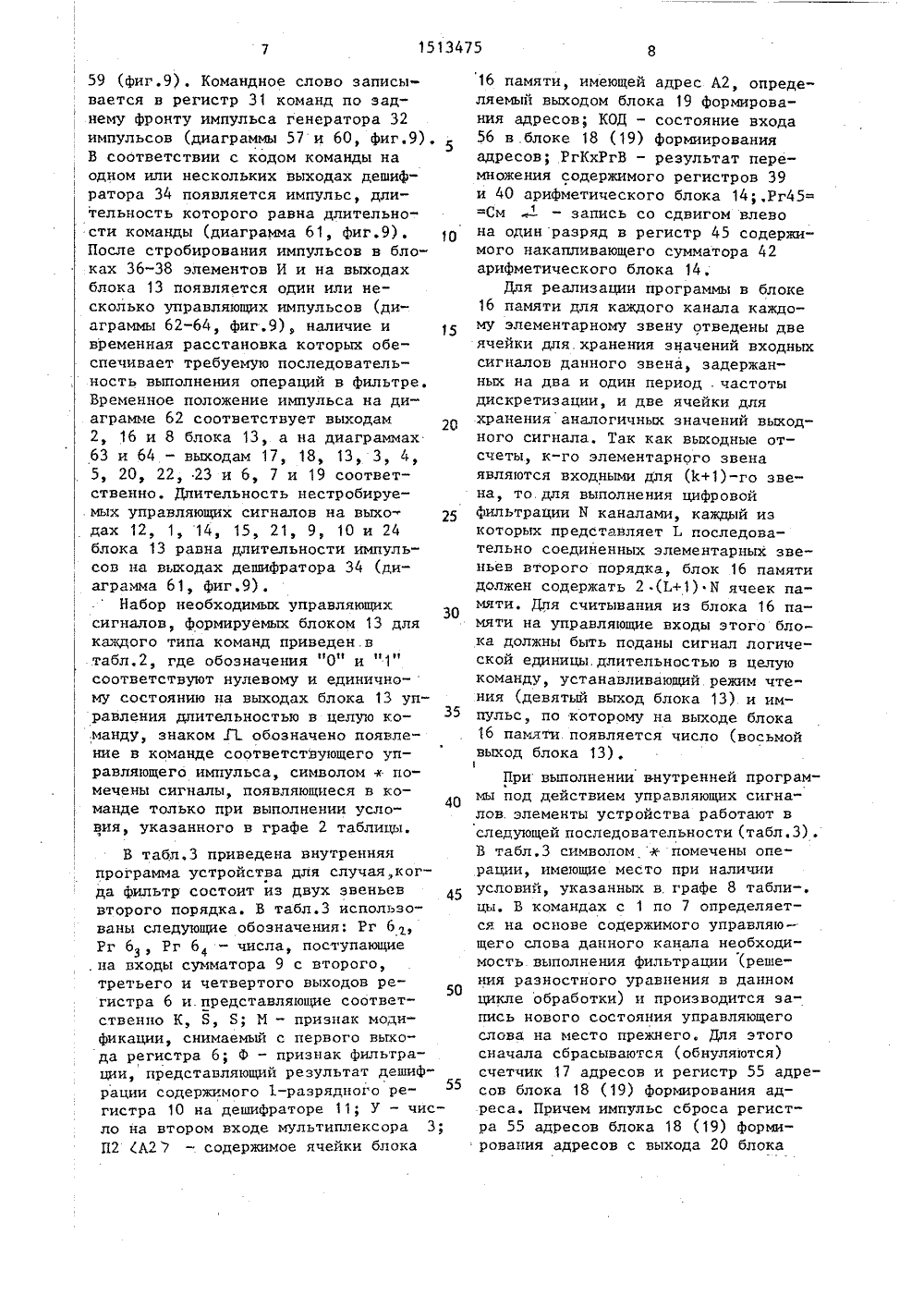

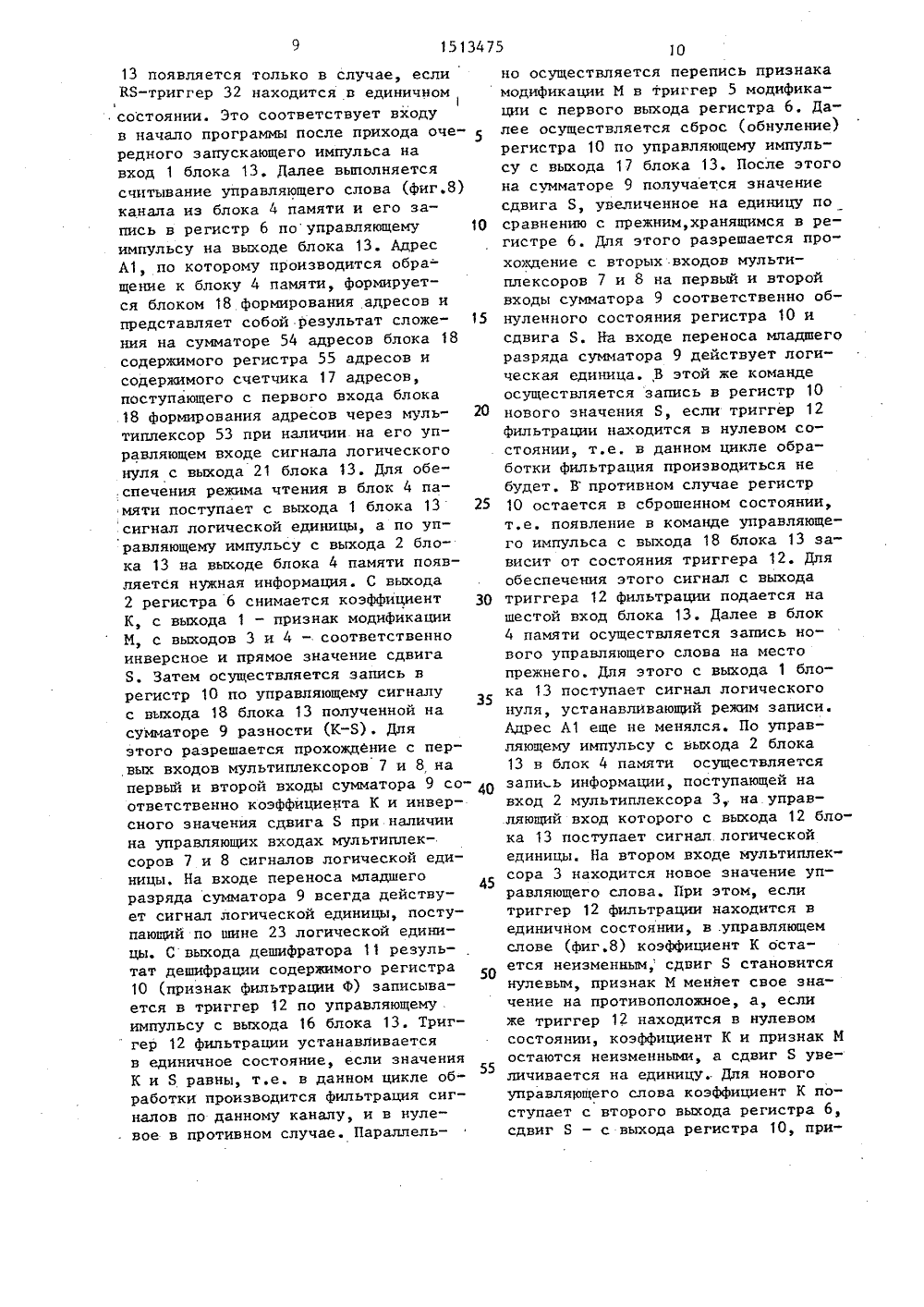

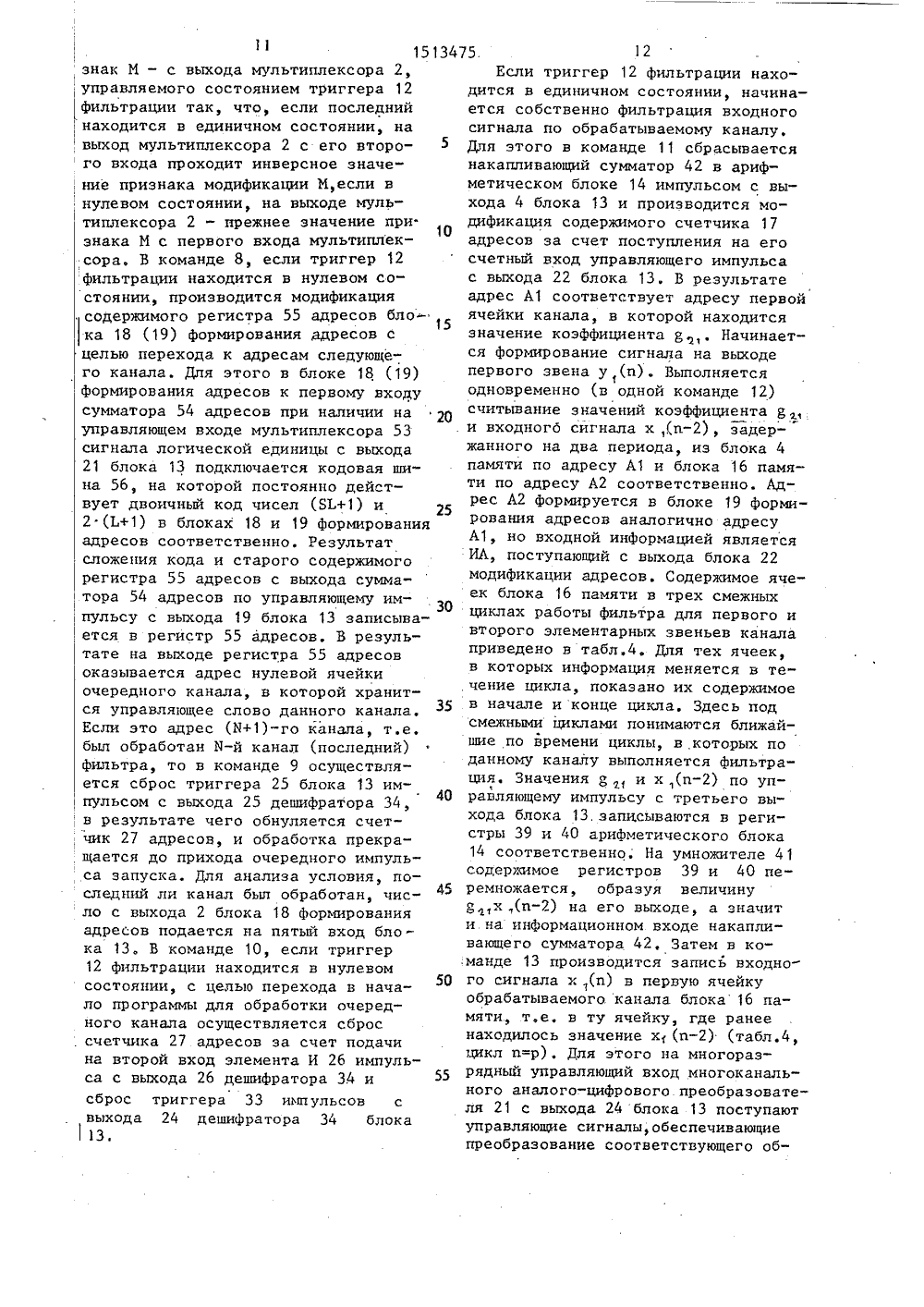

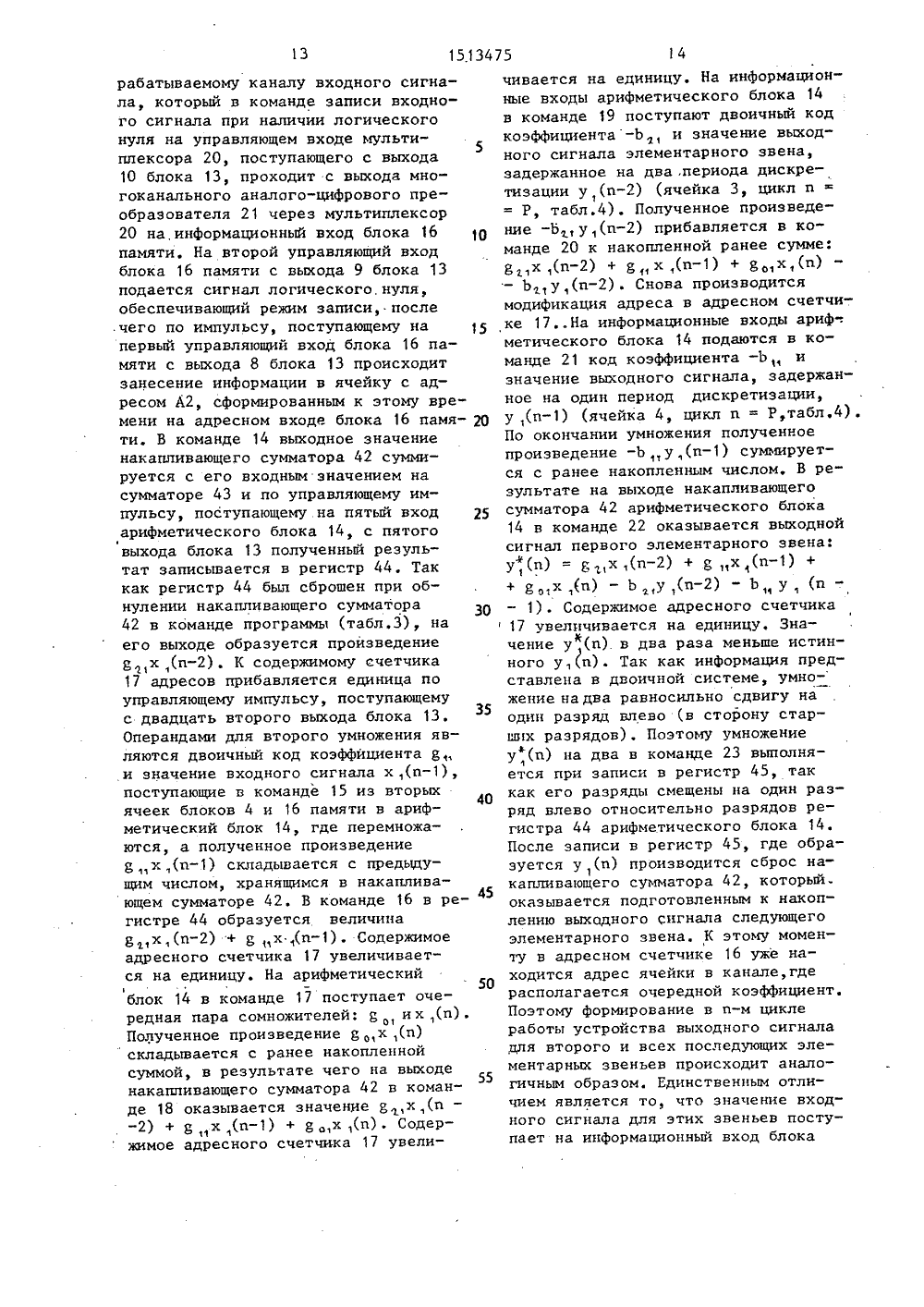

1 13475 20 19 ка формирования адреса и подключенк второму входу сумматора, первый ин-1 формационный вход мультиплексора является адресным входом блока формирования адреса, первым, вторым итретьим тактовыми входами которогоявляются соответственно управляющийвход мультиплексора, установочный 10 вход и вход записи регистра, а второй информационный вход мультиплексора соединен с входом задания константы,блока формирования адреса, который является входом задания кон станты фильтра, при этом блок модификации адреса содержит сумматор,мультиплексор, элемент НЕ, элементИЛИ и элемент И, выход которого подключен к первому входу, сумматора 20 и первому входу элемента ИЛИ, выходкоторого подключен к управляющему входу мультиплексора, выход которого подключен к второму входусумматора, выход которого является 25 выходом блока модификации адреса,адресным входом которого являетсятретий вход сумматора, первым и вторым тактовыми входами блока модификации адреса являются первый вход З 0 элемента И и второй вход элементаИЛИ, второй вход элемента И подключен к выходу элемента НЕ, вход которого подключен к входу младшего разряда адресного входа блока модификации адреса, первй и торой информационные входы мультиплексора соединены соответственно с шиной логической единицы и логического нуляустройства.40 Табл дами группы фильтра, вход переноса . сумматора соединен с шиной логической единицы устройства, выход первого блока памяти подключен к информационному входу первого регистра, первый выход которого подключен к информационному входу первого триггера, прямой и инверсный выходы которого подключены соответственно к первому.и второму информационным входам пятого мультиплексора и соответственно первому и второму тактовому входам блока модификации адреса, выход которого подключен к адресному входу второго блока формирования адреса, выход которого подключен к адресно,му входу второго блока памяти, вто,рой выход первого регистра подключен к второму информационному входу тре,тьего мультиплексора, объединен с выходом пятого мультиплексора и подключен к первому информационному входу второго мультиплексора, второйформационный вход которого подключен к входам кода режима группы филь 1 тра, третий и четвертый выходы первого регистра подключены соответствено к первому и второму информационым входам четвертого мультиплексоа, выход дешифратора подключен к инормационнаму входу второго триггера,ичем блок формирования адреса соержит регистр, сумматор и мультицтексор, выход которого подключЕн К первому входу сумматора, выход коорого является первым выходом блока ормирования адреса и подключен к инормационному входу регистра, выход соторого является вторым выходом блоца 1 тарии и РгА 55 СчА: 0РгА;=0П (АСчА: =СчА Обнуление СчАв БФА 18Запись управляпервого каналаувеличение содСчА 17 на 1 000 001 Х 00000001 его слова БП 4 кимого1 (А ):=ИСчА: =СчА+ 1П 1 (А ) ИСчА:=СчА+1 001 010 001 010 ента 3, вканалу, увеого СчА 17 Запись коэффици БП 4 по первому личение содервим на3 ци апись коэффи П 4 по нерво ичение содер 0010 0011 0010 0011 нта 3, в каналу, увеого СчА 17. 0011 0100 на 1Запись коэффициБП 4 по первомУличение содерэина 1 П (А ):ИСчА: СчА+1 0011 0100 нта 8 овканалу увеого СчА 1721 1513475 Адрес БП 4 Выполняемые операции в команде Командноесловоп/и остоя- АиечА 17 Обозначение Вазов адрес од П (А 1); ИСчА фСчА+ 00100 00101 0100 О 01 1(А)щчА; ффСчА+ 0101 0110 0100110 0110 " П (А ) И0111 СчА=СчА+ Х 011 01101100 01101 5 8 0010 0011 01101 01110 П 1 (А ):=И СчА: СчА+1 ициента му кан могоП 1 (А);= СчА: СчА+1 19 1 А); ИчА: фСчА+1 Запись БП 4 п Бгг валу, увеСчА 17 оэффицивтором)содержим кан личениена 1ЗаписьБП 4 поличениена 1 го П (А 1 ): СчА: фСчА+ 0111 1000 0010 0011 21 8 Х 1001 0100 010 0101 0101 10000110 1001 Х 0110 10001 0111 10010 22Продолжение табл, 1 Содержание и комментарии Запись коэффициента -Ьг, вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Запись коэффициента -ЬБП 4 по первому каналу,личение содержимого СчАна 1Запись коэффициента 8 вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Запись коэффициента 8, вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Запись коэффициента Бог вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Запись коэффициента -Ьгг вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Запись коэффициента -Ь, вБП 4 по первому каналу, увеличение содержимого СчА 17на 1Модификация РгА 55 в БФА 18и обнуление СчА 17 с цельюперехода к адресам второгоканалаЗапись управляющего словавторого канала в БП 4, увеличение содержимого СчА 17на 1Запись коэффициента 8 , вБП 4 по второму каналу, увеличение содержимого СчА 17на 1 Запись коэффБП 4 по второ алличение содерзпна 1Запись коэффициентаБП 4 по второму каналуличение содержимогона 1Запись коэффициентаБП 4 по второму канличенне содержимогона 1 Запись коэффициента -ЬвБП 4 по второму каналу,уве"личение содержимого СчА 17 эффициента 8 в торому каналу, увеодержимого СчА 171513475 23 24 Продолжение табл.1 Адрес БП 4 Командноеслово 9п/и Выполняемые операции в команде остоя- АиечА 17 Обозначение дерзание и комментарии Код ко- Вазов манды адрес 1000 1001 001 010 П (А 1);ИСчА: щСчА+1 оэффициента евторому каналу,содерзимого СчА 001 10100 ОИ 1 0101 П 1 (АгИСчА: фСчА+ 1 1010101 Х 1 О 10о о о о О О О О О ОООО О о о о о ООС,О о оо о о о о о о о о о о О (ОО. О оо о о о о о о о о о о оо.С о ос о о о ОООО О о о о о о оооо о оооо о С о о оооо о о о о о о о О О Ь О О о о о о о о о ( о о о о о о О О О О О о о,оо о о о ое оо ОООО О о о о о о о о ОООО О ОО О о о о о о о о 1 х ООЭЗх Ефво сч о1а 1х ао хЭоооос 1 о хО сд ХфСР ф о х В о Й х х л л о хи х в о Е о о Э Э х х х х Эа Э хю х % х х ОР ОЬО ф сч ф а 1 А ф У Э с х О Э х м х х ф О о1 ЭсЧ а А ф А ц ц х э х ЭЭЩ м хм сО Оъ л 1 11 % Х м .з сс о л ф в с сч м Х щ 1х 1Э Г Чэа г --1 Х м1 с1мфЭ 1- --хО л1о1 - -ЧсСсчГю1 - Л 1ф х х оа Е И о ож1 о Е х л ао СРх фЩ х х х х В э х с й ЭЭАъэ аахсйАс чххЭМ Ра Э Юь о оЩь х од сч хЦоэ ах ЕР,Э Е фСР О.Д АЭЮ Э Эх х хх х иЭЭЭЭфРю цм 11 Ф сф хЭ ИаА ХаО ЭР Х ф- о оии о сСРХ аоф А а Ас э сх хХ 6 хххО 3 Ю х эхм цм юЭхфОЦ Раей ааа мЭ Э РсРе РсР СХСРСА ХХОХахйййхэфа тхххЕЕЭЭХХЭХ0 х хввхвххххххсхээссхОХ ООООХ хРХК ЭХ 1 03 ф а оо РюРе Э х ф х Э А х ох х Ю Э О м фхх ох ьЭ ФЭ вх х61о офь м лсч Р, О Э Ф Хх х Эфо 35 о лхххф ф х моф мосху а ф сч хэо ххфф х а эл эо цсчхо о 1 о х о а оик30 29 15 1 345 Таблица 3 1 ИА (дв.система Командное слово СостояниеСчА 17 Код БА (дв, ко- система) нанды Обозначение Четный Нечетцикл ныйцикл 18 0000 СчА;ОРгА:О " 2 9 3 15 4 21 5 14 6 16 7 7 8 13 Рг 6: П 1 СА) 0000 Рг 1 ОРг 6 +.26 011 011 010 См: См+РгКх+РгВ СчА: СчА+ 0111 27 10 011 011 РгКП (А 1)РгВ:П 2 СА 2 ) 0111 010 См: Им+РгКхРгВСчА:СчЛ+1РгК:П СА 1)РгВ П 2 СЛ 2) 010 010 1000 28 129 10 011 1000 010 011 010 Х Х 000 Тг:ОЯ Выполняемые операции в конвнде Содерхвнке и комментарии Обнуление СчА 17 и РгА 55 в БФА 18 (БФА 19) РгА 55 обнуляется в тон случае, если Тг 331Чтение управляющего слова из БП 4, запись в Рг 6Реализация ка См 9 разности (К-Б). запись в Рг 1 ОЗапись в ТГ 5 признака модификации М н в ТГ 12 признака фильтрации Ф Обнуление Рг 10Запись в Рг 1 О сдвига 8 увеличенного ка 1, если Тг 120 Запись нового управляющего слова в БП 4 нв место прехнего Иодификвция РгА 55 в БФА 18 (БФА 19) в том случае, если Тг 12О, т,е, осуществляется переход к адресам следующего каналаОбнуление Тг 25 в БУ 13, если обра" ботаны все Н каналов,вызывающее прекращение обработки до очередного запускаОбнуление Тг 33 и СЧа 27 в БУ 13, если Тг 120 с целью перехода в начало программы для обработки следующего каналаМодификация СчА 17, обнуление СмНк 42 в БАр 14Чтение 8 из Бп 4, х (и) нэ БП 16 запись в РгК 39 н РгВ 40 Запись входного сигнала х,(п) в БП 16 на место х,(п)Накоплечне в СмНк 42 8 х,(п) модификация СчА 17Чтение 8 иэ БП 4 х,(п) из БП 16, запись в РгК 39 н РгВ 40 Накопление в СмНк 42 уэ,х,(п) + + 8х,(п), модификация СчА 17 Чтение 8 , из БП 4, х (и) иэ БП 16 запись в РгК н РгВ 40 Накопление в СмНк 42 8 э,х(п) + + Вх,(п 1) + 8 х,(п) модифика- ция СчА 17Чтенке -Ьиэ БП 4, у,(п) нз БП 16, запись в РгК 39 н РгВ 40 Накопление в СмНк 42 8 х,(п) + + 8 х (п) + 8 ех (и) - Ъ эУ (и) нодификация СчА 17Чтение "Ъ , иэ БП 4, у,(п) нз БП 16 запись в РгК 39 н РгВ 40 Накопление в СнНк 42 у(п)8 х,(п) + я х,(п) +31 Продолвение табл.З Коман- Командное слова ИА (дв,систе"ма) СостояниеСчА 17 Выполняемые операции в команде да БА (дв.система) Содерхание и комментарии Код коОбозначение Четный НечетШ 1 кл ныйцикл манды Накопление в СмНК 42 В ззх з(п)++ В х (и) + В хз(п), моди"фикация СчА 17Чтение -Ь вз из ВП 4, у т(п) изБП 16, вались в РгК 39 и РгВ 40Накопление в СмНк 42 В хз(п"2)+(БФА 19) для перехода к адресамследующего каналаОбнуление Тг 33 и СчА 17 в ВУ 13с целью перехода в начало программы рля обработки следующего канала, если не все Й каналов обработаныОбнуление Тг 25 в БУ 13 вызывающее прекращение обработки до очередного запуска 100 100 101 ЗО 1001 См: См+РгКхРгВСчА:СчА+ 100 101 101 101 3 10 32 1 100 1001 РгКгвП 1 (АРгВ; П 2 (А 27См;См+РгК+РгВСчА: СчА+1 101 1010 33 10 34 1 101 101Х , Х 101 1010 РгК 1 П (А 1РгВ 5 П 2 (Л 2См:См+РгКхргВСчЛ: СчЛ+1 1011 100 101 1 ОО 101 Х Х Рг 45; См1РгВых 1 Рг 45П 2 А 2 1 Рг 45РгА: РгА+КОД 35 3 36 5 37 1 100 100 1011 1011 1011 Тг 33 ;" 0СчА 27: Оф 38 20 1011 Х Х Х Х 1011 Тг; О 39 22 Таблица 4 Нечетный цикл п=ш=р+1 Четный цикл п=г=ш+1 ИА Четный цикл п=р Содержимое ячейки БП 1 б БА Содержимое ячейки БП 16 БА Содержимое ячейки БП 16 БА 001 хч(г"2); х(г)000 х, (г)011 у,(г) щх (г);У,(г) = хз(г)010 у,(г) х, (г) 000 х,(ш) 001 х 1(ш); х,(ш) 010 у,(ш)х (ш) 000 х,(р); х, (Р)001 х 1(р 1)010 у,(р) =х 1(р);У, Р)=х т(Р011 у, (р) = х (р) 000 001 010 у, (ш) =х з(ш);у,(ш) =х т(ш)у, (ш)Ут(ш 2)Ут(ш) 011 011 100 101 101 у (г); у. (г) 100 У з(г151347Изобретение относится к вычислительной технике и может быть использовано в цифровых многоканальныхсистемах обработки случайных процес 5сов.Целью изобретения является повы- .шейие быстродействия.На Фиг.1 изображена функциональнаясхема программно-управляемого цифрового фильтра; на фиг.2 - блок синхронизации; на фиг.З - арифметическийблок; на Фиг.4 - блок модификацииадресов; на фиг.5 - блок формирования адресов; на фиг.б - регистр; на 15фиг.7 - структура командного слова;на Фиг.8 - структура управляющегослова; на Фиг,9 - временные диаграммы управляющих сигналов;на фиг.10- временные диаграммы распределения ка налов по циклам обработки.Программно-управляемый фильтр. 10, дешифратор 11, триггер 12, блок13 синхронизации, арифметическийблок 14, выходной регистр 15, блок16 памяти, счетчик 17 адреса, блоки 3018 и 19 Формирования адреса, мультиплексор 20, аналого-цифровой преобразователь 2 1, блок 22 модификацииадреса, вход 23 задания логическойединицы,35Блок 13 синхронизации (Фиг.2)содержит элемент И 24, триггер 25,элемент И 26, счетчик 27, микропрограммную память 28, мультиплексоры29 и 30, регистр 31 команд, генератор 32 тактовых импульсов, триггер33, дешиФратор 34, элементы 35 за-.,держки, блоки элементов И 36-38,Арифметический блок 14 (Фиг.З)содержит регистры 39 и 40, умножитель41, накапливающий сумматор 42, состоящий из сумматора 43 и регистра44 и регистр 45.Блок 22 модификации адреса (Фиг.4)содержит элемент НЕ 46, элемент И47, элемент ИЛИ 48, сумматор 49мультиплексор 50, входы 51 и 52 задания логического нуля и единицы.(фиг.б) первый выход образован пря 5 4мым выходом старшего (первого) разряда, второй 1-разрядный выход -прямыми выходами разрядов регистра 6с второго по (1+1)-ый,третий 1"разрядный выход - инверсными выходамиразрядов с ,(1+2)-го по (21+1)-й,четвертый 1-разрядный выход - прямыми выходами разрядов с (1+2)-гопо (21+1)-й. Первый вход регистра 6является его информационным входом,а второй вход - входом записи регистра,Фильтр работает следующим образом,Каналы фильтрации обрабатываютсяпоочередно, Для каждого элементарного звена второго порядка в каждомиз каналов фильтр реализует разностное уравнение. Управление последовательностью работы цифрового фильтрапроизводится блоком 13 синхронизации,представляющим собой микропрограммный автомат. Микропрограмма работыхранится в микропрограммной памяти 28.Перед началом фильтрации производится запись коэффициентов фильтраиз блока 1 задания коэффициентов вблок 4 памяти, т,е, исходное программирование каналов Фильтрации натребуемые амплитудно-частотные характеристики (АЧХ) . Для обеспеченияработы каналов фильтрации с различными значениями частоты дискретизации, кроме, значений коэффициентов,в блок 4 памяти для каждого из каналов записывается (21+1)-разрядноеуправляющее слово, структура которогО представлена на фиг.8. В управляющих словах, кроме коэффициентовК, определяющих во сколько раз частота работы (частота дискретизации)данного канала ниже частоты работысамого высокочастотного канала, имеются сдвиги Я, позволяющие сделатьравномерной временную расстановкуканалов по циклам обработки, т,е,в коэффициент К и исходное значениесдвига Я заложена информация о частоте работы-и временном положении конкретного канала, показывающая, чтопо данному каналу Фильтрация выполняется в каждом (К+1)-м цикле обработки, начиная с (К-Я+1)-го цикла, если считать с момента прихода1513475 оставитель А.Барановехред М,Дидык Коррек Бескид Н.Рогулич едак изводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 10 Заказ б 081(49 Тираж б 68 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раущская наб д. 4/5Программа записи коэффициентов Фильтра четвертого порядка, состоящего из двух звеньев второго порядка, для случая двухканального устройства приведена в табл.1, где приняты следующие обозначения: П 1 (А ) - содержимое ячейки блока 4 памяти, имеющей адрес А 1; И - число на первом входе мультиплексора 3, поступающее из блока задания ко 50 55 пользуется для формирования исполнительного адреса (ИЛ) в блоке 22 модификации адресов, Последовательностьзаписи в блок 4 памяти следующая.На второй вход блока 13 синхронизации с входа 1 задания режима подается потенциальный сигнал логическогонуля, запрещающий запуск микропрограммы через элемент И 24 и переключающий мультиплексоры 29 и 30 в положение, при котором информационныйвход регистра 31 команд оказываетсяподключенным к третьему входу блока13, а вход записи - к четвертому 5входу блока, После этого начинаетсявыполнение. программы записи коэффициентов фильтра в блок 4 памяти. Впроцессе записи третий из группывходов 1 через мультиплексор 3 оказывается подключенным к входу блока 4памяти, для чего на управляющий входмультиплексора 3 с выхода 12 блока13 подается сигнал логического нуля,Командное слово, установленное на 25входе 1, через мультиплексор 29 записывается в регистр 31 команд поимпульсу, поступающему с входа 1 через мультиплексор 30 на вход записирегистра 31 команд. Командное слово(фиг,7) состоит из кода команды ибазового адреса (БА). При записи информации с входа 1 в блок 4 памятис входа 1 блока 13 появляется сигналлогического нуля, устанавливающийрежим записи, сама запись производится по управляющему импульсу, появляющемуся на выходе 2 блока 13. Записьинформации производится по адресуА 1, поступающему на адресный входблока 4 памяти с первого выхода блока 18 формирования адресов. АдресА 1 представляет собой сумму содержимого счетчика 17 адресов и регистра 55 адресов блока 18 формированияадресов. Работа блока 18 Формирования адресов приведена в описаниивнутренней программы фильтра. эффициентов; Х - значение безразлично,При записи в блок 4 памяти по каждому из каналов сначала заносится управляющее слово, занимающее однуячейку, памяти, затем заносятся коэффициенты первого элементарного звена фильтра, затем второго и т,д. Порядок расположения коэффициентов покалдому к-му элементарному звену следующии. г. , сц , ЬЬ ,Для выполнения цифровой фильтрацииБ каналами, каждый из которых представляет Ь последовательно соединенных элементарных звеньев второго порядка, блок 4 памяти должен содержать (ЯхЬ+1)хМ ячеек.После окончания исходного программирования на вход 2 блока 13 свхода 1 подается потенциальный сигнал логической единицы, в результатечего устройство переходит в режимработы по внутренней программе, Приэтом мультиплексоры 29 и 30 переключаются в положение, при котором информационный вход регистра 31 командоказывается подключенным к выходумикропрограммной памяти 28, а входзаписи - к выходу генератора 32 импульсов. Одновременно разрешаетсяпрохождение запускающих импульсовс первого входа блока 13 на Б-входтриггера 25. При.поступлении запускающего импульса КЯ-триггер 25 переходит в единичное состояние, навходе установки в нуль счетчика 27адресов появляется единица. Счетчик27 адресов начинает счет импульсовгенератора 32 импульсов (диаграмма57, фиг,9), и начинается выполнение(цикл обработки) внутренней программы устройства, хранящейся в микропрограммной памяти 28, Каждой из команд соответствует свой набор управляющих сигналов на выходах блока 3,которые определяют необходимую последовательность выполнения операции в цифровом фильтре. Управляющиесигналы на выходах блока 13 формируются следующим образом. В соответствии с состоянием счетчика 27 адресов на выходе микропрограммной памяти 28 появляется командное слово. Интервалы времени (для 1-го такта), втечение .которых адрес на выходе счвтсчетчика 28 адресов и командные слова остаются неизменными, представлены соответственно диаграммами 58 и10 59 (фиг.9) . Командное слово записывается в регистр 31 команд по заднему фронту импульса генератора 32 импульсов (диаграммы 57 и 60, фиг.9), В соответствии с кодом команды на одном или нескольких выходах дешифратора 34 появляется импульс, длительность которого равна длительности команды (диаграмма 61, фиг.9). После стробирования импульсов в блоках 36-38 элементов И и на выходах блока 13 появляется один или несколько управляющих импульсов (диаграммы 62-64, Фиг.9), наличие и временная расстановка которых обеспечивает требуемую последовательность выполнения операций в ФильтреВременное положение импульса на диаграмме 62 соответствует выходам 2, 16 и 8 блока 13, а на диаграммах 63 и 64 - выходам 17, 18, 13, 3, 4, 5, 20, 22, 23 и 6, 7 и 19 соответственно, Длительность нестробируемых управляющих сигналов на выходах 12, 1, 14, 15, 21, 9 10 и 24 блока 13 равна длительности импульсов на выходах дешифратора 34 (диаграмма 61, Фиг,9).Набор необходимых управляющих сигналов, формируемых блоком 13 для каждого типа команд приведен.вутабл,2 где обозначения "0" и "1" соответствуют нулевому и единичному состоянию на выходах блока 13 управления длительностью в целую команду, знаком П. обозначено появление в команде соответствующего управляющего импульса символом + по%мечены сигналы появляющиеся в коУманде только при выполнении условия, указанного в графе 2 таблицы,В табл,З приведена внутренняя программа устройства для случаякогда фильтр состоит из двух звеньев второго порядка. В табл.З использованы следующие обозначения; Рг 6, Рг 6, Рг 6 - числа, поступающие , на входы сумматора 9 с второго, третьего и четвертого выходов регистра 6 и.представляющие соответственно К, Я, Я; М - признак модификации, снимаемый с первого выхода регистра 6; Ф - признак фильтрации, представляющий результат дешифрации содержимого 1-разрядного регистра 10 на дешифраторе 11; У - чис ло на втором входе мультиплексора 3 П 2 (А 27 - содержимое ячейки блока 20 25 30 35 40 45 50 55 16 памяти, имеющей адрес А 2, определяемый выходом блока 19 формирования адресов; КОД - состояние входа56 в блоке 18 (19) формиированияадресов; РгКхРгВ - результат перемножения содержимого регистров 39и 40 арифметического блока 14;,Рг 45"=См в- запись со сдвигом влевона один разряд в регистр 45 содержимого накапливающего сумматора 42арифметического блока 14,Для реализации программы в блоке16 памяти для каждого канала каждому элементарному звену отведены двеячейки для.хранения значений входныхсигналов данного звена, задержанных на два и один период .частотыдискретизации, и две ячейки дляхранения аналогичных значений выходного сигнала, Так как выходные отсчеты, к-го элементарного звенаявляются входными для Ь+1)-го звена, то для выполнения цифровойФильтрации М каналами, каждый изкоторых представляетпоследовательно соединенных элементарных звеньев второго порядка, блок 16 памятидолжен содержать 2 (1.+1)И ячеек памяти. Для считывания из блока 16 памяти на управляющие входы этого блока должны быть поданы сигнал логической единицы. длительностью в целуюкоманду, устанавливающий режим чтения (девятый выход блока 13) и импульс, по которому на выходе блока16 памяти появляется число (восьмойвыход блока 13),1При выполнении внутренней программы под действием управляющих сигналов. элементы устройства работают вследующей последовательности (табл.З).В табл.З символом + помечены операции, имеющие место при наличииусловий, указанных в. графе 8 табли-.цы. В командах с 1 по 7 определяется на основе содержимого управляющего слова данного канала необходимость выполнения фильтрации (решения разностного уравнения в данномцикле обработки) и производится запись нового состояния управляющегослова на место прежнего. Для этогосначала сбрасываются (обнуляются)счетчик 17 адресов и регистр 55 адресов блока 18 (19) формирования адреса. Причем импульс сброса регистра 55 адресов блока 18 (19) Формирования адресов с выхода 20 блока5 10 13 появляется только в случае, если КБ-триггер 32 находится в единичном1 состоянии. Это соответствует входу в начало программы после прихода очередного запускающего импульса на вход 1 блока 13. Далее выполняется считывание управляющего слова (фиг.8) канала из блока 4 памяти и его запись в регистр 6 поуправляющему импульсу на выходе блока 13. Адрес А 1, по которому производится обра- щение к блоку 4 памяти, формируется блоком 18 Формирования адресов и представляет собой результат сложения на сумматоре 54 адресов блока 18 содержимого регистра 55 адресов и содержимого счетчика 17 адресов, поступающего с первого входа блока 18 формирования адресов через мультиплексор 53 при наличии на его управляющем входе сигнала логического нуля с выхода 21 блока 13. Для обе,спечения режима чтения в блок 4 памяти поступает с выхода 1 блока 13 сигнал логической единицы, а по унравляющему импульсу с выхода 2 блока 13 на выходе блока 4 памяти появляется нужная информация. С выхода 2 регистра 6 снимается коэффициент К, с выхода 1 - признак модификации М, с выходов 3 и 4 - соответственно инверсное и прямое значение сдвига Б. Затем осуществляется запись в регистр 10 по управляющему сигналу с выхода 18 блока 13 полученной на сумматоре 9 разности (К-Б) . Для этого разрешается прохождЕние с первых входов мультиплексорови 8 на первый и второй входы сумматора 9 соответственно коэффициента К и инверсного значения сдвига Б при наличии на управляющих входах мультиплексоров 7 и 8 сигналов логической единицы, На входе переноса младшего разряда сумматора 9 всегда действует сигнал логической единицы, поступающий по шине 23 логической единицы. С выхода дешифратора 11 результат дешифрации содержимого регистра 10 (признак фильтрации Ф) записывается в триггер 12 по управляющему . импульсу с выхода 16 блока 13. Триггер 12 фильтрации устанавливается в единичное состояние, если значения К и Б равны, т,е. в данном цикле обработки производится фильтрация сигналов по данному каналу, и в нулевое в противном случае. Параллель 15 20 25 30 35 40 45 50 55 но осуществляется перепись признакамодификации М в триггер 5 модификации с первого выхода регистра б. Далее осуществляется сброс (обнуление)регистра 10 по управляющему импульсу с выхода 17 блока 13, После этогона сумматоре 9 получается значениесдвига Б, увеличенное на единицу посравнению с прежним, хранящимся в регистре бДля этого разрешается про" хождение с вторых входов мультиплексоров 7 и 8 на первый и второйвходы сумматора 9 соответственно обнуленного состояния регистра 10 исдвига Б. На входе переноса младшегоразряда сумматора 9 действует логическая единица, В этой же командеосуществляется запись в регистр 10нового значения Б, если триггер 12фильтрации находится в нулевом состоянии, т,е. в данном цикле обработки фильтрация производиться небудет. В противном случае регистр10 остается в сброшенном состоянии,т,е. появление в команде управляющего импульса с выхода 18 блока 13 зависит от состояния триггера 12. Дляобеспечения этого сигнал с выходатриггера 12 фильтрации подается нашестой вход блока 13. Далее в блок4 памяти осуществляется запись нового управляющего слова на местопрежнего. Для этого с выхода 1 блока 13 поступает сигнал логическогонуля, устанавливающий режим записи.Адрес Л 1 еще не менялся. По управляющему импульсу с выхода 2 блока13 в блок 4 памяти осуществляетсязапиь информации, поступающей навход 2 мультиплексора 3,. на управляющий вход которого с выхода 12 блока 13 поступает сигнал логическойединицы, На втором входе мультиплексора 3 находится новое значение управляющего слова. При этом, еслитриггер 12 фильтрации находится вединичном состоянии, в .управляющемслове (Фиг.8) коэффициент К остается неизменным, сдвиг Б становитсянулевым, признак М меняет свое значение на противоположное, а, еслиже триггер 12 находится в нулевомсостоянии, коэффициент К и признак Мостаются неизменными, а сдвиг Б увеличивается на единицу,. Для новогоуправляющего слова коэффициент К поступает с второго выхода регистра 6,сдвиг Б - с выхода регистра 10, при 1115134 знак М - с выхода мультиплексора 2, управляемого состоянием триггера 12фильтрации так, что, если последнийнаходится в единичном состоянии, навыход мультиплексора 2 с его второго входа проходит инверсное значение признака модификации М,если в нулевом состоянии, на выходе мультиплексора 2 - прежнее значение при.10 знака М с первого входа мультиплексора. В команде 8, если триггер 12 фильтрации находится в нулевом состоянии, производится модификация содержимого регистра 55 адресов блока 18 (19) формирования адресов сцелью перехода к адресам следующего канала. Для этого в блоке 18 (19) формирования адресов к первому входу сумматора 54 адресов при наличии на управляющем входе мультиплексора 53 сигнала логической единицы с выхода 21 блока 13 подключается кодовая шина 56, на которой постоянно действует двоичный код чисел (БЬ+1) и 2 (Ь+1) в блоках 18 и 19 Формирования адресов соответственно. Результат сложения кода и старого содержимого регистра 55 адресов с выхода сумма тора 54 адресов по управляющему импульсу с выхода 19 блока 13 записыва ется в регистр 55 адресов. В результате на выходе регистра 55 адресов оказывается адрес нулевой ячейки очередного канала, в которой хранится управляющее слово данного канала.Если это адрес (И+1)-го канала, т.е, был обработан И-й канал (последний) фильтра, то в команде 9 осуществляется сброс триггера 25 блока 13 импульсом с выхода 25 дешифратора 34,40 в результате чего обнуляется счет, чик 27 адресов, и обработка прекращается до прихода очередного импульса запуска. Для анализа условия, послсдний ли канал был обработан, число с выхода 2 блока 18 Формирования адресов подается на пятый вход блока 13, В команде 10, если триггер 12 фильтрации находится в нулевом состоянии, с целью перехода в нача 50 ло программы для обработки очередного канала осуществляется сброс . счетчика 27 адресов за счет подачи нг второй вход элемента И 26 импульса с выхода 26 дешифратора 34 исброс триггера 33 импульсов с выхода 24 дешифратора 34 блока1375 12Если триггер 12 фильтрации находится в единичном состоянии, начинается собственно фильтрация входного сигнала по обрабатываемому каналу. Для этого в команде 11 сбрасывается накапливающий сумматор 42 в арифметическом блоке 14 импульсом с выхода 4 блока 13 и производится модификация содержимого счетчика 17 адресов за счет поступления на его счетный вход управляющего импульса с выхода 22 блока 13. В результатеадрес А 1 соответствует адресу первойячейки канала, в которой находится значение коэффициента в Начинается формирование сигнала на выходе первого звена у,(п). Выполняется одновременно (в одной команде 12)считывание значений коэффициента ц ,и входного сигнала х,(п), задержанного на два периода, из блока 4памяти по адресу А 1 и блока 16 памяти по адресу А 2 соответственно. Адрес А 2 формируется в блоке 19 формирования адресов аналогично адресу А 1, но входной информацией являетсяИА, поступающий с выхода блока 22 модификации адресов, Содержимое ячеек блока 16 памяти в трех смежных циклах работы фильтра для первого ивторого элементарных звеньев каналаприведено в табл.4. Для тех ячеек, в которых информация меняется в течение цикла, показано их содержимое в начале и конце цикла, Здесь под смежными циклами понимаются ближайашие по времени циклы, в которых по данному каналу выполняется фильтрация. Значения 8 , и х (п) по управляющему импульсу с третьего выхода блока 13, записываются в регистры 39 и 40 арифметического блока 14 соответственно. На умножителе 4 1 содержимое регистров 39 и 40 перемножается, образуя величину д,х (и) на его выходе, а значит и на информационном входе накапливающего сумматора 42, Затем в команде 13 производится запись входного сигнала х (и) в первую ячейку обрабатываемого канала блока 16 памяти, т,е. в ту ячейку, где ранеенаходилось значение х(п) (табл,4, цикл п=р), Для этого на многоразрядный управляющий вход многоканального аналого-цифрового.преобразователя 21 с выхода 24 блока 13 поступают управляющие сигналы, обеспечивающие преобразование соответствующего об 1513475 4рабатываемому каналу входного сигнала, который в команде записи входного сигнала при наличии логического нуля на управляющем входе мультиплексора 20, поступающего с выхода5 10 блока 13, проходит с выхода многоканального аналого-цифрового преобразователя 21 через мультиплексор 20 на,информационный вход блока 16 1 О памяти, На второй управляющий вход блока 16 памяти с выхода 9 блока 13 подается сигнал логического. нуля, обеспечивающий режим записи, после .чего по импульсу, поступающему на 15 первый управляющий вход блока 16 памяти с выхода 8 блока 13 происходит занесение информации в ячейку с адресом А 2, сформированным к этому времени на адресном входе блока 16 памя ти. В команде 14 выходное значение накапливающего сумматора 42 суммируется с его входным значением на сумматоре 43 и по управляющему импульсу, поступающему на пятый вход 25 арифметического блока 14, с пятого выхода блока 13 полученный результат записывается в регистр 44. Так как регистр 44 был сброшен при обнулении накапливающего сумматора 42 в команде программы (табл.3), на его выходе образуется произведение я,х (и). К содержимому счетчика 17 адресов прибавляется единица по управляющему импульсу, поступающему с двадцать второго выхода блока 13.Операндами для второго умножения являются двоичный код коэффициента я и значение входного сигнала х,(п), поступающие в команде 15 из вторых ячеек блоков 4 и 16 памяти в ариф 40 метический блок 14, где перемножаются, а полученное произведениец ,х (и) складывается с предыдущим числом, хранящимся в накапливающем сумматоре 42. В команде 16 в ре гистре 44 образуется величиная ,х (и) + ц ц,х (и). Содержимое адресного счетчика 17 увеличивается на единицу, На арифметический50 блок 14 в команде 17 поступает очередная пара сомножителей: дих (и), Полученное произведение а х,(п) складывается с ранее накопленнойсуммой, в результате чего на выходе накапливающего сумматора 42 в команде 18 оказывается значение 8 ,х,(п - -2) + я,х (и) + я ,х,(п) . Содержимое адресного счетчика 17 увеличивается на единицу, На информационные входы арифметического блока 14 в команде 19 поступают двоичный код коэффициента-Ъ , и значение выходного сигнала элементарного звена, задержанное на два,периода дискретизации у,(п) (ячейка 3, цикл и= Р, табл.4), Полученное произведение -Ь, у(п) прибавляется в команде 20 к накопленной ранее сумме: 8.,х,(п) + х,(п) + 8,х,(п) - Ь, у,(п). Снова производится модификация адреса в адресном счетчике 17 На информационные входы ариф-, метического блока 14 подаются в команде 21 код коэффициента -Ь и значение выходного сигнала, задержанное на один период дискретизации, у,(п) (ячейка 4, цикл п = Р,табл.4). По окончании умножения полученное произведение -Ьу (и) суммируется с ранее накопленным числом, В результате на выходе накапливающего сумматора 42 арифметического блока 14 в команде 22 оказывается выходной сигнал первого элементарного звена: у (и) = 8, х, (и) + 8 х (и) + + 8 х,(п) - Ь у,(п) - Ь у (и - .1). Содержимое адресного счетчика17 увеличивается на единицу, Значение у (и). в два раза меньше истинХного у(п). Так как информация представлена в двоичной системе, умно- жение надва равносильно сдвигу на один разряд влево (в сторону старших разрядов), Поэтому умножение у (и) на два в команде 23 выполняется при записи в регистр 45, так как его разряды смещены на один разряд влево относительно разрядов регистра 44 арифметического блока 14, После записи в регистр 45, где образуется у,(п) производится сброс накапливающего сумматора 42, который. оказывается подготовленным к накоплению выходного сигнала следующего элементарного звена. К этому моменту в адресном счетчике 16 уже находится адрес ячейки в канале,где располагается очередной коэффициент. Поэтому формирование в и-м цикле работы устройства выходного сигнала для второго и всех последующих элементарных звеньев происходит аналогичным образом. Единственным отличием является то, что значение входного сигнала для этих звеньев поступает на информационный вход блока16 памяти с выхода арифметического блока 14 через второй вход мультиплексора 20, а не с входов фильтра, т.е, для второго и всех последующих звеньев входным сигналом является выходной сигнал предыдущего звена х (и) = у ,(и), При этом на управляюший вход мультиплексора 20 поступает сигнал логической единицы 1 О разрешающий прохождение сигнала с второго входа мультиплексора 20 на его выход, После того, как в регистр 45 арифметического блока 14 поступает значение выходного сигнала последнего элементарного звена у (и) ка - нала (команда 35, табл, 3), производитсяего перезапись в выходной регистр , . 15 по управляющему импульсу с выхода 7 блока 13 (команда 36,табл.З) 20Одновременно с этим через второйвход мультиплексора 20 значение у (и)с выхода арифметического блока 14 заносится в блок, 16 памяти на место у (и), Далее производится модификация содержимого регистра 55 адресов в блоке 18 (19) формированияадресов с целью перехода к адресамследующего канала (команда 37,табл,З).Если еще не все М каналов Фильтраобработаны, осуществляется переходв начало программы (команда 38,Уабл,З), для чего производится сброссчетчика 27 адресов и триггера 33при условии, что в результате мо-.дификации регистра 55 адресов получа 35ется адрес нулевой ячейки 1-го канала, причем Х 4 Б. В противном случае выполняется завершающая программу команда (команда 39, табл,З), щв которой осуществляется сброс ЕБтриггера 25 импульсом с выхода 25дешифратора 34, в результате чегоустанавливается в нуль счетчик 27адресов, и прекращается обработка до прихода очередного импульсазапуска. На этом цикл обработкизаканчивается.Работа фильтра в следующем цикле(цикл ш = р + 1) выполняется по той 50же программе, однако ячейки блока16 памяти, в которых хранятся значения задержанных на один и двапериода дискретизации входных (выходных) сигчалов для каналов, покоторым выполняется Фильтрация, поменялись местами по сравнению с предыдущим циклом, в котором выполнялась фильтрация (циклы ш и р,табл.4). Для получения нужного исполнительного адреса (ИА) на первый и второй входы блока 22 модификацииадресов поступает соответственнопрямое и инверсное значение признакаМ с выходов триггера 5 модификации,на третий вход - базовый адрес (БА)с одиннадцатого адресного выхода блока 13. Для получения требуемого ИАв блоке 22 модификации адресов производится преобразование БА по следующему правилу:-ИА = БА + 1, если М = 1, а младший разряд БА равен нулю;-ИА = БА - 1, если М= 1 и младшийразряд БА равен единице;- ИА = БА, если М = О,Признак М меняет свое значение на противоположное в управляющем слове какала в цикле, в котором производится фильтрация по данному каналу. В остальных циклах значение М не меняетсяЕсли признак М равен единице, а младший разряд БА и, следовательно, вход элемента НЕ 46 равны нулю, выходы элементов И 47 и ИЛИ 48 равны единице. Сигнал с выхода элемента И 47 поступает на вход переноса младшего разряда сумматора 49, к первому входу которого подключен БА, а к второму входу в этом случае оказывается подключенной шина 51 логического нуля, т.е. код 000, что достигается подачей сигнала логической единицы с выхода элемента ИЛИ 48 на управляющий вхрд мультиплексора 50, В итоге на выходе сумматора 49 Формируется ИА = БА + 1Если М = 1 и младший разряд БА равен единице, выходы элементов НЕ 46, 1 47 и ИЛИ 48 равны нулю, В этом случае на входе переноса младшего разряда сумматора 49 действует нуль, а к его второму входу подключается шина 52 логической единицы, т.е, код 111, вто время, как на первом входе сумматора 49 по прежнему БА. СуммированиеБА с кодом 11 1 равносильно вычитанию из БА единицы, так как -1 вдополнительном коде представляетсяединицами во всех разрядах. В результате на выходе блока 22 модификацииадресов имеется ИА = БА - 1, В томслучае, когда М = Онезависимо оттого, чему равен младший разряд БА,на выходе элемента И 47 устанавливается нуль, а выход элемента ИЛИ48 равен единице, При этом на входепереноса младшего разряда сумматора49 действует нуль, а к второму входу подключается шина 5 1 логического нуля. В результате на выходе блока 22 модификации адресов присутствует ИА = БЛ. Указанная последовательность работы обеспечивает необходимыйпорядок смены адресов смежных ячеекблока 1 б памяти в каждом цикле рабо Оты канала, в котором по данному каналу выполняется фильтоация. Формула изобретения15Программно-управляемый цифровой фильтр, содержащий первый и второй блоки памяти, арифметический блок, блок модификации адресов, первый мультиплексор, .выходной регистр и 20 блок. синхронизации, первый и второй выходы которого подключены к входам управления соответственно записью и считыванием первого блока памяти, выход которого подключен к входу 25 коэффициента арифметического блока, выход которого подключен к первому информационному входу первого мультиплексора и информационному входу выходного регистра, выход которого О является информационным выходом Фильтра, входом запуска которого является первый вход блока синхронизации, третий, четвертый, пятый и шестой выходы которого подключены соответственно к входу синхронизации приема, входу синхронизации вычислений, установочному входу и входу синхронизации выдачи арифметического блока, вход операнда которого подключен к выходу второго блока памяти, информационный вход которого подключен к выходу первого мультиплексора, вход записи выходного регистра подключен к седьмому выходу блока синхронизации, восьмой и девятый выходы которого подключены к входам управления соответственно записью и считыванием второго блока памяти, управляющий вход первого мультиплексора подключен к десятому выходу блока синхронизации, одиннадцатый выход которого подключен к адресному входу блока модификации адресов, первый, второй и третий входы кода режима блока синхронизации явля 55 ются входами разрядов кода режима группы фильтра, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены счетчик адреса, первый и второй блокиформирования адреса, второй, третий,четвертый и пятый мультиплексоры,первый и второй триггеры, первый ивторой регистры, сумматор, дешифратори аналого-цифровой преобразователь,выход которого подключен к второмуинформационному входу первого мультиплексора, двенадцатый, тринадцатый,четырнадцатый и пятнадцатый выходыблока синхронизации подключены соответственно к управляющему входу второго мультиплексора тактовому входупервого регистра, управляющим входамтретьего и четвертого мультиплексоров, выходы которых подключены соответственно к первому и второму информационным входам сумматора, выходкоторого подключен к информационномувходу второго регистра, выход которого подключен к входу дешифратора, пепервому информационному входу третьего мультиплексора и первому информационному входу второго мультиплексора, выход которого подключен к информационному входу первого блока памяти, адресный вход которого подключенк первому выходу первого блока фор -мирования адреса,.второй выход которого подключен к входу окончания обработки блока синхронизации, шестнадцатый выход которого подключен к тактовому входу первого триггера и тактовому входу второго триггера, выходкоторого подключен к управляющемувходу пятого мультиплексора и четвертому входу кода режима блока синхронизации, семнадцатый и восемнадцатыйвыходы которого подключены соответ"ственно к входу обнуления и входу записи второго регистра., девятнадцатый,двадцатый и двадцать первый выходыблока синхронизации подключены соответственно к первому, второму и третьему тактовым входам первого и второго блоков формирования адреса,.двадцать второй и двадцать третий выходы блока синхронизации подключенысоответственно к входу обнуления исчетному входу счетчика адреса, выход которого подключен к адресномувходу первого блока Формирования адреса, двадцать четвертый выход блокасинхронизации. подключен к тактовомувходу аналого-цифрового преобразователя, информационные входы группы которого являются информационными вхо

СмотретьЗаявка

4279101, 06.07.1987

ПРЕДПРИЯТИЕ ПЯ Г-4152

ПАРИЖСКИЙ ЮРИЙ СЕМЕНОВИЧ, ПЕТРОВА ИРИНА КОНСТАНТИНОВНА, ШПОЛЯНСКИЙ АЛЕКСАНДР НАУМОВИЧ

МПК / Метки

МПК: G06F 17/17, H03H 17/04

Метки: программно-управляемый, фильтр, цифровой

Опубликовано: 07.10.1989

Код ссылки

<a href="https://patents.su/20-1513475-programmno-upravlyaemyjj-cifrovojj-filtr.html" target="_blank" rel="follow" title="База патентов СССР">Программно-управляемый цифровой фильтр</a>

Предыдущий патент: Устройство для спектрального анализа сигналов

Следующий патент: Устройство для определения моментов распределения случайных величин

Случайный патент: Образец для испытаний на растяжение