Устройство для исправления одиночных и обнаружения мяоюкратных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

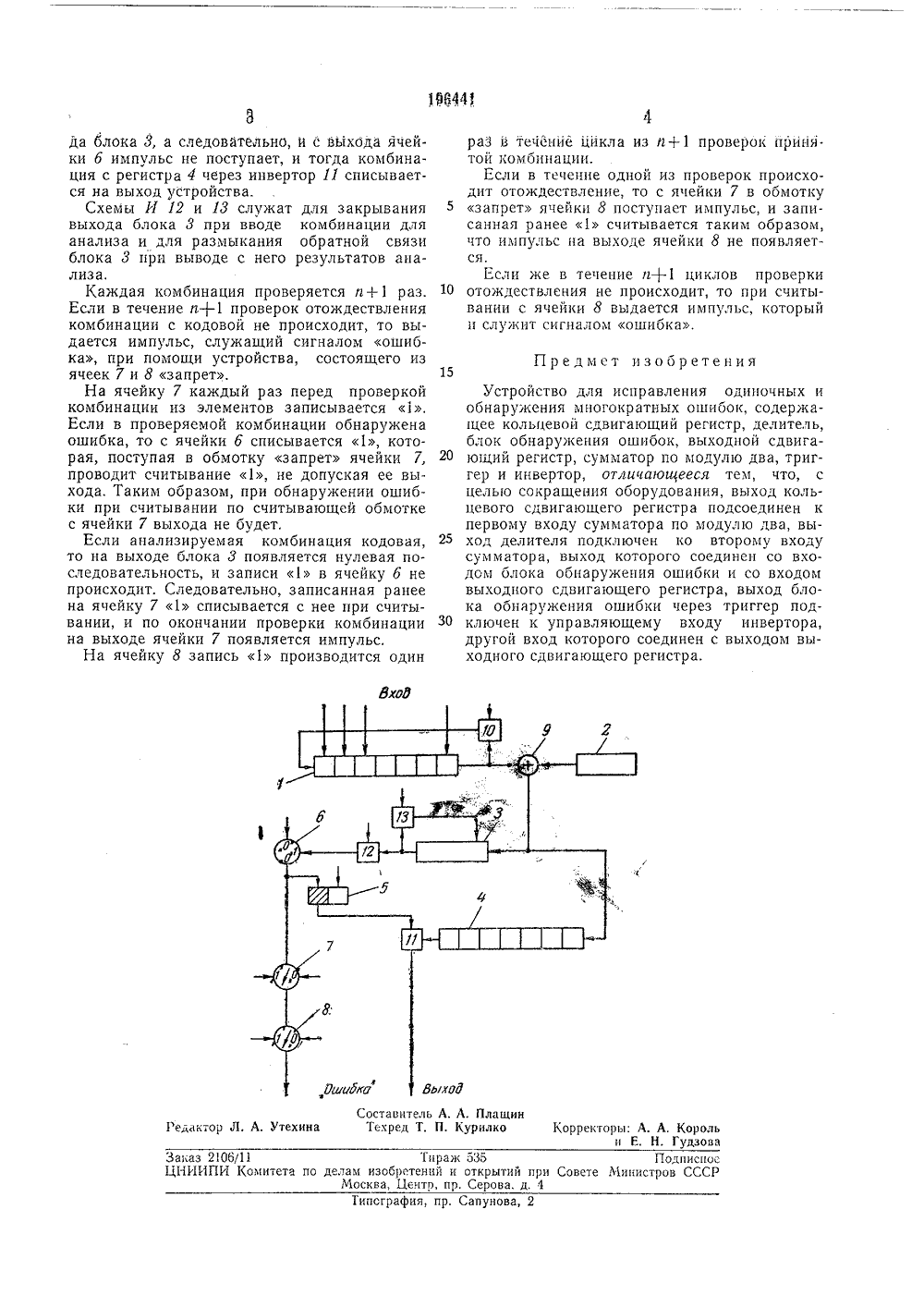

В 6441 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Сова Соеетссиа Социалистичесииа респуалиивт, свидетельстваависимое о л. 42 пт Заявлено 19.111.1966 ( 1061734/26-2 заявкис присоедпнеш МПО б 0 Комитет по делам иэооретений и сткрыти ори Совете Министре СССР.ата опублик ДО 681,142.07(088.8 6.7.1967, Бюллетень М 11аиия описания 18.И 1.1967 вторимбрстения А. И. Захаров енная краснознаменная академия свяЗаявител СТРОЙСТВО ДЛОБНАРУЖЕН ИСПРАВЛЕНИЯ ОДИНОЧНЫХ МН 01 ООРАТНЫХ ОШИБОКИзвестны устройства для испарения одиночных и обнаружения многократных ошибок, содержащие регистры сдвига, сумматоры по модулю два, запоминающие элементы и умно- жители на постоянный коэффициент,Предложенное устройство отличается тем, что выход кольцевого сдвигающего регистра подсоединен к первому входу сумматора по модулю два, выход делителя подключен ко второму входу сумматора, выход которого соединен со входом блока обнаружения ошибки и со входом выходного сдвигающего регистра; выход блока обнаружения ошибки через триггер подключен к управляющему входу инвертора, другой вход которого соединен с выходом выходного сдвигающего регистра,Это позволяет сократить оборудование.На чертеже приведена функциональная схема устройства для исправления одиночных и обнаружения многократных ошибок для корректирующего кода с кодовой комбинацией длины гг.Опа содержит регистр 1 с обратной связью на гг разрядов, делитель 2 на гг+1, блок 3 обнаружения ошибки, регистр 4 на и разрядов, триггер 5, ячейку б памяти, ячейки 7, 8 запрет, сумматор 9 по модулю два, схемы И 10, инвертор 11, схемы О 12, 13.В устройстве для получения последовательности из и+1 комбинаций, в которой первая комоинация нс изменена, а в остальных поочередно инвертировано по одному элементу, используется сложение по модулю два последовательности из и+1 неизмененных принятых комбинаций, полученных с регистра с обратной связью, и последовательности, получаемой с делителя на (и+ 1) .Инвертирование производится с помощьюсумматора по модулю два.10 Схема И 10 в цепи обратной связи регистраслужит для размыкания обратной связи на и+ 1 цикле, что необходимо для очистки регистра 1 и приема новой комбинации. Полученная после сумматора 9 комбинация записывается на регистр 4 и одновременно анализируется с помощью блока 3.Если анализируемая комбинация не является кодовой, с выхода блока 3 выдается хотя бы одна единица (так как, например, для ли нейных кодов синдром в этом случае всегдабудет не нулевым) и записывается в ячейку б памяти, с которой при считывании выдается импульс, опрокидывающий триггер б в такое состояние, при котором инвертор 11 закрыт и 25 комбинация, записанная в регистре 4, на выход устройства не попадет. Перед проверкоп каждой комбинации триггер 5 возвращается в состояние, при котором инвертор 11 оказывается открытым. Поэтому, если прп анализе 30 комбинации она окажется кодовой, то с выхоеда ь аказ 210 б/11 1 прак 535 Поднисно НИИПИ Комитета по делам изобретений и открытий при Совете Министров ССС Москва, Центр, пр. Серова, д, 4 Т 2ипсграфия, пр, Сапунова,да блока 3, а следовательно, и с выхода ячейки б импульс не поступает, и тогда комбинация с регистра 4 через инвертор 11 списывается на выход устройства.Схемы И 12 и 13 служат для закрывания выхода блока 3 при вводе комбинации для анализа и для размыкания обратной связи блока 3 при выводе с него результатов анализа.Каждая комбинация проверяется а+1 раз. Если в течение а+1 проверок отождествления комбинации с кодовой не происходит, то выдается импульс, служащий сигналом ошибка, при помощи устройства, состоящего из ячеек 7 и 8 запрет.На ячейку 7 каждый раз перед проверкой комбинации из элементов записывается 1. Если в проверяемой комбинации обнаружена ошибка, то с ячейки б списывается 1, которая, поступая в обмотку запрет ячейки 7, проводит считывание 1, не допуская ее выхода. Таким образом, при обнаружении ошибки при считывании по считывающей обмотке с ячейки 7 выхода не будет,Если анализируемая комбинация кодовая, то на выходе блока 3 появляется нулевая последовательность, и записи 1 в ячейку б не происходит. Следовательно, записанная ранее на ячейку 7 1 списывается с нее при считывании, и по окончании проверки комбинации на выходе ячейки 7 появляется импульс.На ячейку 8 запись 1 производится один раз в течение цикла из и+1 проверок йриня.той комбинации.Если в течение одной из проверок происходит отождествление, то с ячейки 7 в обмотку5 запрет ячейки 8 поступает импульс, и записанная ранее 1 считывается таким образом,что импульс па выходе ячейки 8 не появляется,Если же в течение и+1 циклов проверки10 отождествления не происходит, то при считывании с ячейки 8 выдается импульс, которыйи служит сигналом ошибка. Устройство для исправления одиночных иобнаружения многократных ошибок, содержащее кольцевой сдвигающий регистр, делитель, блок обнарукения ошибок, выходной сдвига югций регистр, сумматор по модулю два, триггер и инвертор, отличающееся тем, что, с целью сокращения оборудования, выход кольцевого сдвигающего регистра подсоединен к первому входу сумматора по модулю два, вы ход делителя подключен ко второму входусумматора, выход которого соединен со входом блока обнаружения ошибки и со входом выходного сдвигающего регистра, выход блока обнаружения ошибки через триггер подЗ 0 ключен к управляющему входу инвертора,другой вход которого соединен с выходом выходного сдвигающего регистра.

СмотретьЗаявка

1061734

А. И. Захаров, Военна краснознаменна академи

МПК / Метки

МПК: G06F 11/08, H03M 13/51

Метки: исправления, мяоюкратных, обнаружения, одиночных, ошибок

Опубликовано: 01.01.1967

Код ссылки

<a href="https://patents.su/2-196441-ustrojjstvo-dlya-ispravleniya-odinochnykh-i-obnaruzheniya-myaoyukratnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления одиночных и обнаружения мяоюкратных ошибок</a>

Предыдущий патент: Г. а. блинов и ж. к. корзо

Следующий патент: Аналого-дискретное устройство передачи приращений преобразованного сигнала

Случайный патент: Способ крепления ножей к фрезерному барабану почвообрабатывающей машины