Устройство контроля ошибок линейных регенераторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1385302

Авторы: Гуревич, Дурец, Непомнящий, Паламарчук

Текст

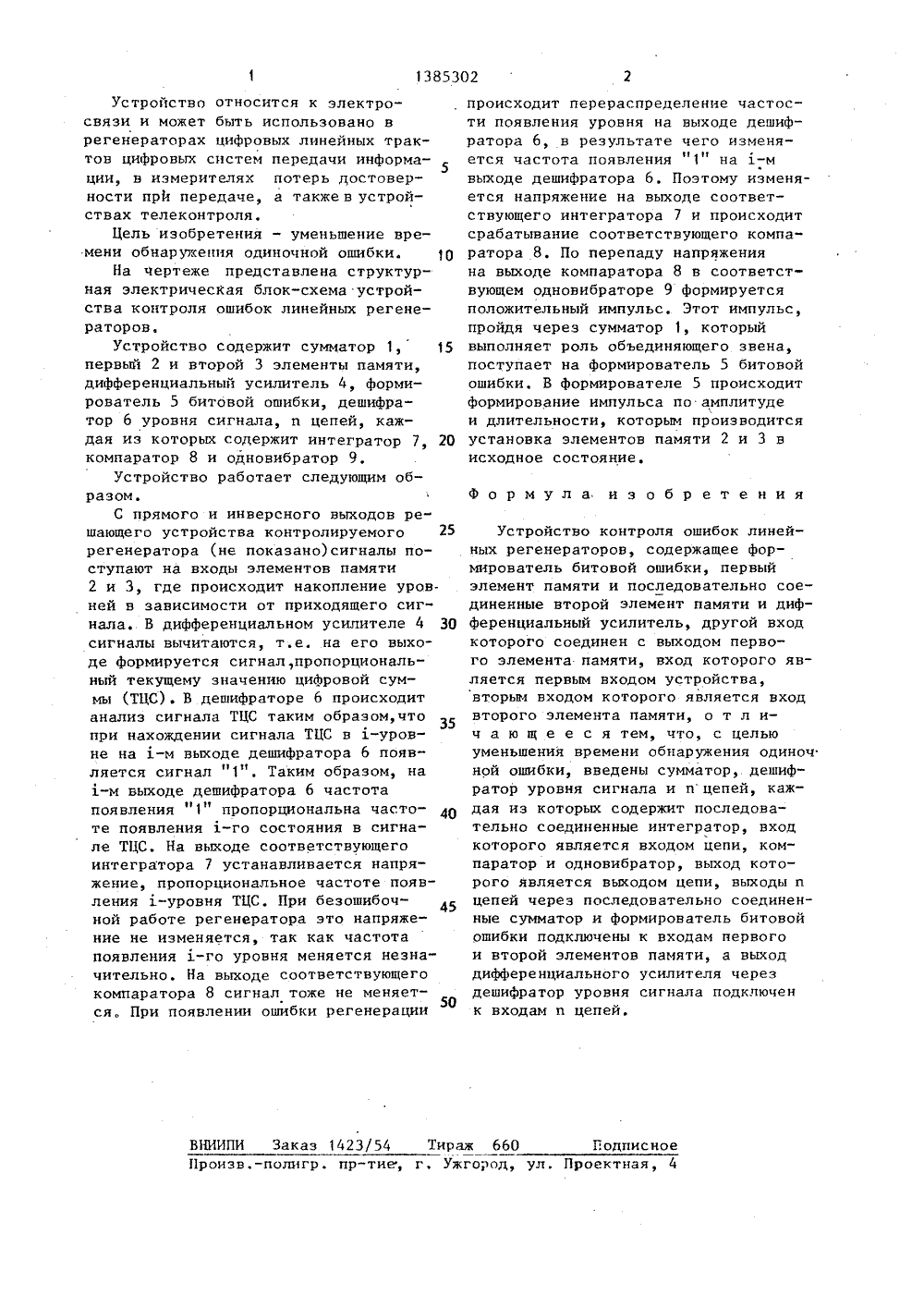

(54) УСТРОЙС ЛИНЕЙНЫХ РЕГ (57) Изобрет связи. Цель ние времени 0ЕРА ОНТРОЛЯ ОШИБОКОРОВ тносится к элект тения - уменьшежения одиночной и зобр ГОСУДАРСТВЕННЫИ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(22) 15. 12,86 (46) 30.03.88 (71) Ленингр кий институт евича(72) Е.Я.Дуре В.А.Паламарчу (53) 62 1.395. (56) Техничес РСМ3219, МасЬгдсЬепе 1 ябрь 1984, с. ошибки, Устр-во содержит эл-ты 2и 3 памяти, диф, усилитель 4, формирователь (Ф) 5 битовой ошибки. Введены сумматор 1, дешифратор 6 уровня сигнала, и цепей, каждая из к-рыхсодержит интегратор 7, компаратор 8и одновибратор 9. В эл-тах 2 и 3 происходит накопление уровней в зависимости от приходящего сигнала.По перепаду напряжения на выходе компаратора 8 и соответствующем одновибраторе 9 будет сформирован полож. импульс. Этот импульс, пройдя черезсумматор 1, к-рый выполняет рольобъединяющего звена, поступит на Ф 5.В Ф 5 происходит формирование импульса по амплитуде и длительности, к-рымпроизводится установка эл-тов 2 и 3в исходное состояние. 1 ил.1385302 ВНИИПИ Заказ 1423/54 Тираж 660 Подписное 11 роизв.-палигр. пр-тие, г, Ужгород, ул, Проектная, 4 Устройство относится к электросвязи и может быть использовано врегенератарах цифровых линейных трактов цифровых систем передачи информа 5ции, в измерителях потерь достоверности прй передаче, а также в устройствах телеконтроля.Цель изобретения " уменьшение времени обнаружения одиночной ошибки.На чертеже представлена структурная электрическая блок-схема устройства контроля ошибок линейных регенераторов.Устройство содержит сумматор 1, 15первый 2 и второй 3 элементы памяти,дифференциальный усилитель 4, формирователь 5 битовой ошибки, дешифратор 6 уровня сигнала, и цепей, каждая из которых содержит интегратор 7, 20компаратор 8 и одновибратор 9,Устройство работает следующим образом.С прямого и инверсного выходов решающего устройства контролируемого 25регенератора (не показано)сигналы поступают на входы элементов памяти2 и 3, где происходит накопление уровней в зависимости от приходящего сигнала. В дифференциальном усилителе 4 30сигналы вычитаются, т.е. на его выходе формируется сигнал,пропорциональный текущему значению цифровой суммы (ТЦС). В дешифраторе 6 происходитанализ сигнала ТЦС таким образом,чтопри нахождении сигнала ТЦС в д-уровне на -м выходе дешифратора 6 появляется сигнал "1". Таким образом, на-м выходе дешифратора 6 частотапоявления " 1" пропорциональна частоте появления -го состояния в сигнале ТЦС. На выходе соответствующегоинтегратора 7 устанавливается напряжение, пропорциональное частоте появления -уровня ТЦС. При безошибачной работе регенератора это напряжение не изменяется, так как частотапоявления х-го уровня меняется незначительно. На выходе соответствующегокомпаратара 8 сигнал тоже не меняет 50ся. При появлении ошибки регенерации происходит перераспределение частости появления уровня на выходе дешифратора 6, в результате чего изменяется частота появления "1" на -мвыходе дешифратора 6. Поэтому изменяется напряжение на выходе соответствующего интегратора 7 и происходитсрабатывание соответствующего компаратора 8. По перепаду напряженияна выходе компаратора 8 в соответствующем одновибраторе 9 формируетсяположительный импульс, Этот импульс,пройдя через сумматор 1, которыйвыполняет роль объединяющего звена,поступает на формирователь 5 битовойошибки. В формирователе 5 происходитформирование импульса по амплитудеи длительности, которым производитсяустановка элементов памяти 2 и 3 висходное состояние,Формула изобретения Устройство контроля ошибок линейных регенераторов, содержащее формирователь битовой ошибки, первый элемент памяти и последовательно соединенные второй элемент памяти и дифференциальный усилитель, другой вход которого соединен с выходом первого элемента памяти, вход которого является первым входом устройства, вторым входом которого является вход второго элемента памяти, о т л ич а ю щ е е с я тем, что, с целью уменьшения времени обнаружения адиноч ной ошибки, введены сумматор, дешифратор уровня сигнала и пцепей, каждая из которых содержит последовательна соединенные интегратор, вход которого является входом цепи, компаратор и одновибратор, выход которого является выходом цепи, выходы п цепей через последовательно соединенные сумматор и формирователь битовой ошибки подключены к входам первого и второй элементов памяти, а выход дифференциального усилителя через дешифратор уровня сигнала подключен к входам и цепей.

СмотретьЗаявка

4161047, 15.12.1986

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

ДУРЕЦ ЕВГЕНИЙ ЯНКЕЛЕВИЧ, НЕПОМНЯЩИЙ КОНСТАНТИН АЛЕКСАНДРОВИЧ, ПАЛАМАРЧУК ВАДИМ АЛЕКСЕЕВИЧ, ГУРЕВИЧ ВИКТОР ЭЛИЗАРОВИЧ

МПК / Метки

МПК: H04B 3/46

Метки: линейных, ошибок, регенераторов

Опубликовано: 30.03.1988

Код ссылки

<a href="https://patents.su/2-1385302-ustrojjstvo-kontrolya-oshibok-linejjnykh-regeneratorov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство контроля ошибок линейных регенераторов</a>

Предыдущий патент: Устройство дистанционного контроля диаграммы уровней на необслуживаемых усилительных пунктах кабельной линии связи

Следующий патент: Устройство телеконтроля линейных трактов цифровых систем передачи

Случайный патент: 160544