Система для сопряжения терминалов с вычислительной машиной

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1529232

Авторы: Братенникова, Быков, Самойлова, Толмач

Текст

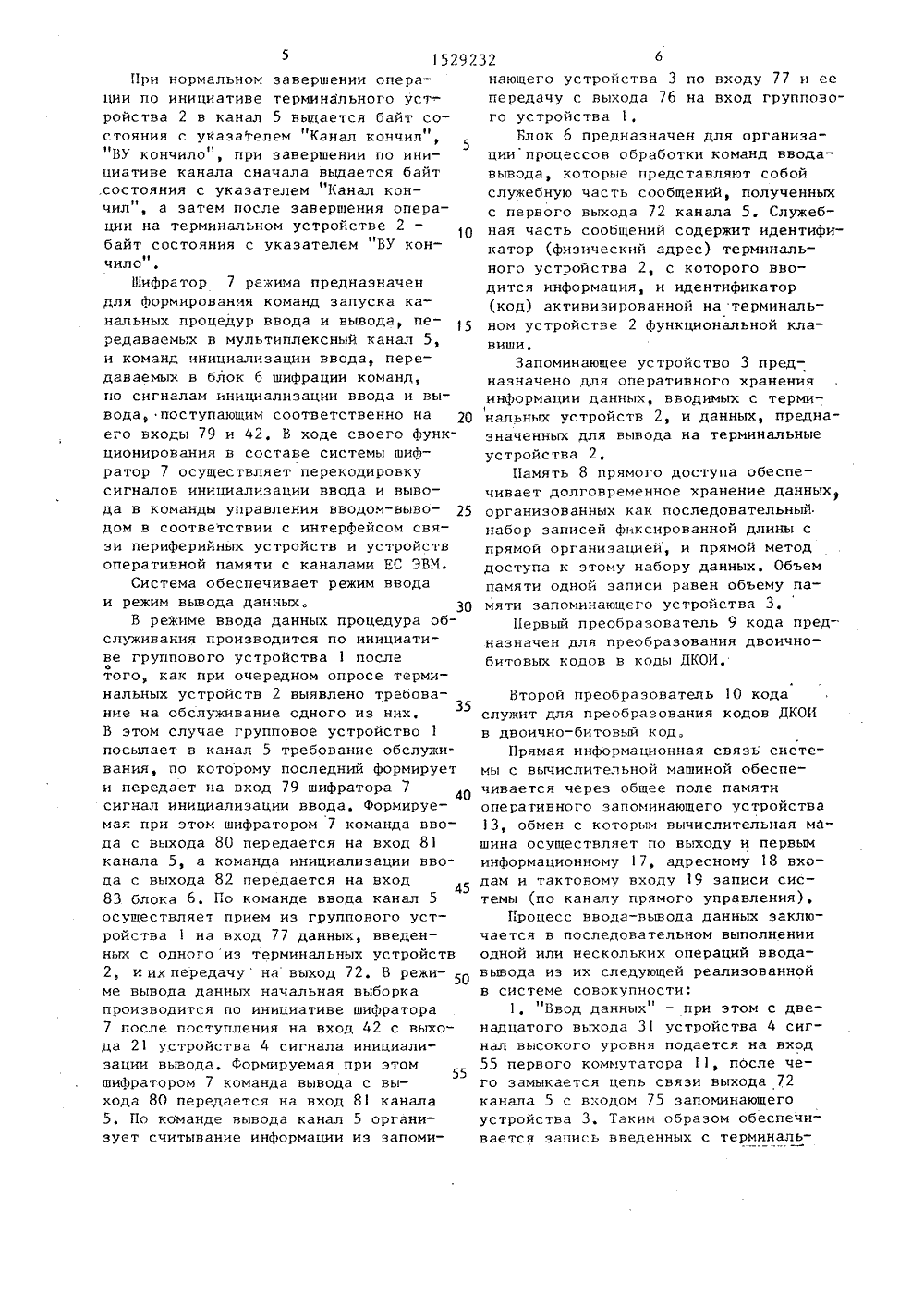

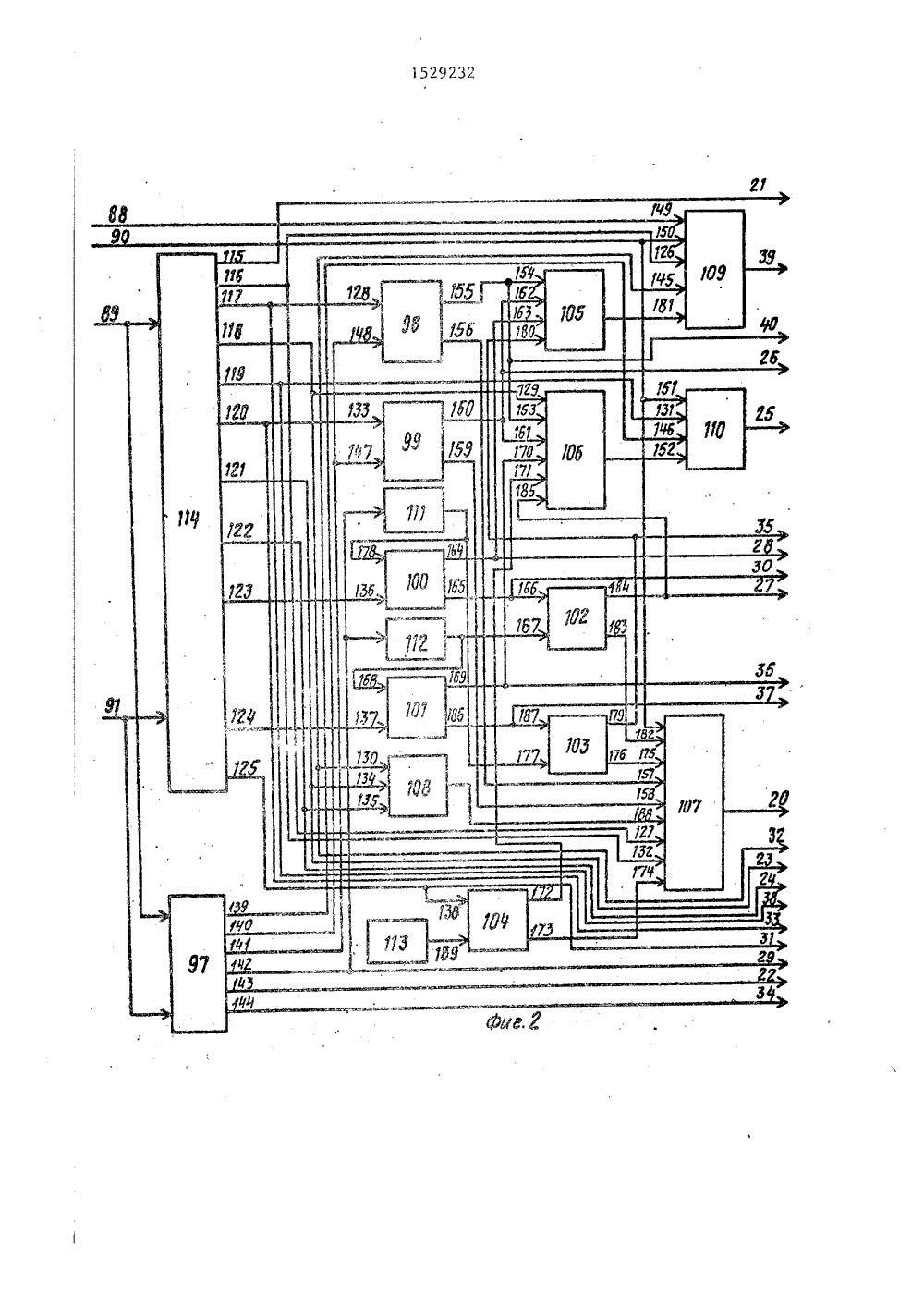

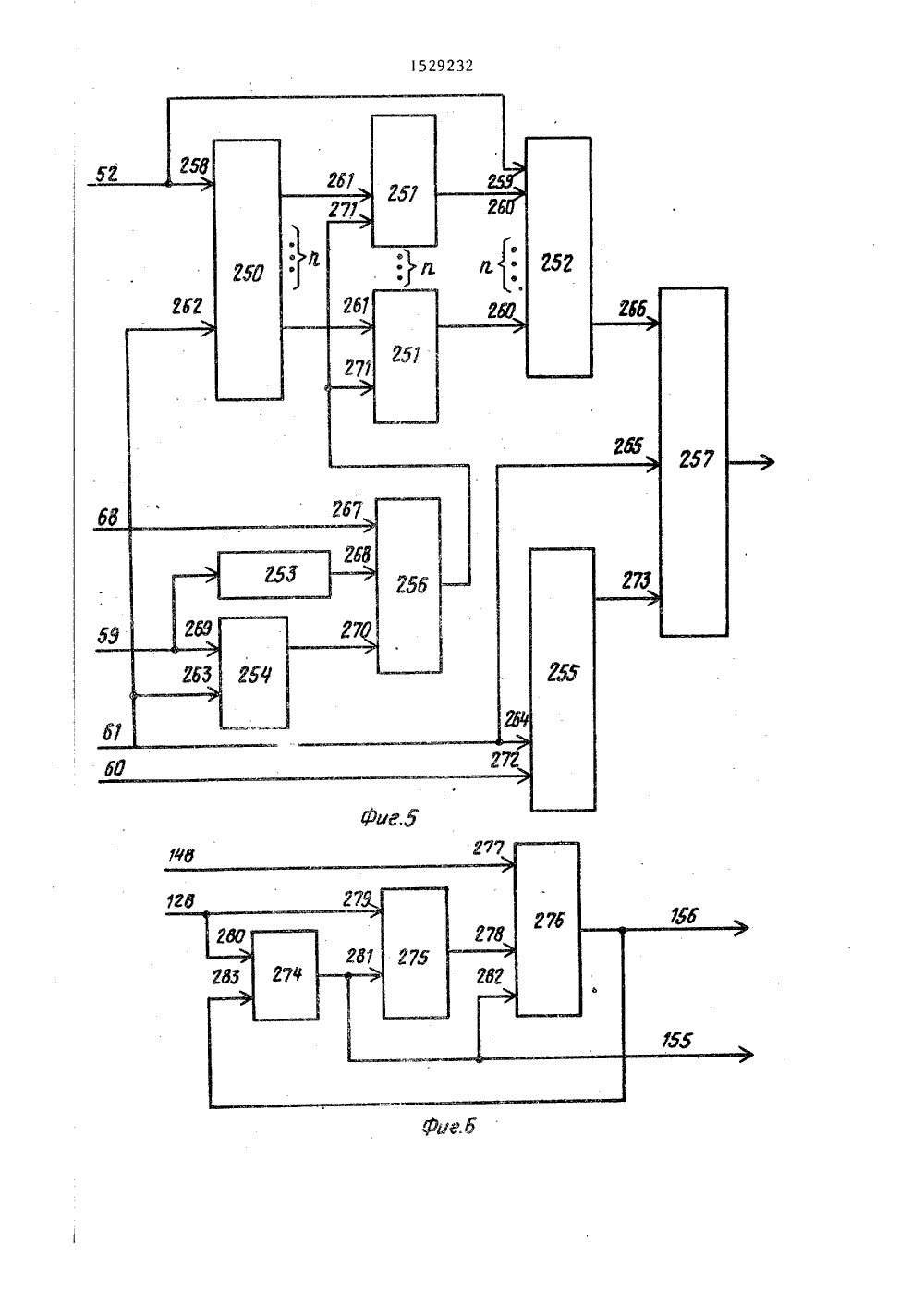

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 594 С 06 Е ГОСУДАРСТВЕННЫПО ИЗОБРЕТЕНИЯПРИ ГКНТ СССР КОМИТЕТ ОТКРЫТИЯ САНИЕ ИЗ ЕТЕНИЯ ТЕЛЬСТ Н АВТОРСКОМУ С 24-24(21 (22 л, например дисежиме диалога в Бюл. 9 46 О,Н,Самойлова(72) ия заклюе устрой- интерак(53) (56) Ф 51 свидетельствоС Об Р 13/00, 1видетельство СС С 06 Р 13/10,7 ввода-в транза 983 де ит те е(54) СИСТЕМАЛОВ С ВЫЧИСЛИ ДЛЯ СОПРЯЖЕНИЯ Т ЕЛБНОй МАШИНОЙМИНА два преое запоми 7 Изобретени утат йств шифр ома ти. осится ает,ке и вычисли быть использ ных системах льнои технике п циимого доступа, блок шифратор режима. 2 вано в автоматизирован т водаправления дляс использовани команд вода данн я к автомати нике и может Изобретение относи ке и вычислительной т быть использовано в а оматизированны ввода-вывода системах управления д данных с использовани терминалов имер дисплеиных иалога в реальном вывода, нап ежи анц еме Цель изобр а решаемых з нтерактивног о управления шаблонами ранзакций ввода-вывода раметрамнных,руктур я терм ной; н авлена с сопряжен а иг предсты дляслителктурна систе с выч хем и ма н ало фиг. т стро3 я схема на фи стрления рук мен уп 4308293/ 20.07,87 15.2.89 В,К,Быков олмач и С 681; 3 (08 Авторско 952, кл, торское 7428, кл ия - расширение класпутем обеспечения миналов ввода-выводплейных станций, в рреальном времени. Цельюявляется расширение класзадач, Сущность изобретенчается в том, что введенньства позволяют обеспечитьтивное управление шаблонамвода данных и параметрамиций ввода-вывода, Системагрупповое устройство управминалами, мультиплексный кройство управления обменомразователя кодов, оперативн ющее устроиство, два ком ферное запоминающее устр турная схема блока шифрации команд; на фиг,4 - структурная схема первого преобразователя кода; на фиг,5 структурная схема второго преобразователя кодл; на фиг.б - структурная .схема узла синхронизации; на фиг,7 структурнля схема первого формирователя адреса; нл фиг,8 - структурная схема второго формирователя адреса,Система для сопряжения терминалов с вычислительной машиной (фиг,.1) соЪдержит групповое устройство 1 управления.терминалами, соединенное с терминальными устройствами 2, буферное запоминающее устройство 3, устройство 4 управления обменом, мультиплексный канал 5, блок б шифрации команд, шифратор 7 режима, память 8 прямогодоступа, первый 9 и второй 10 преоб 1 разователи кодов, первый 11 и второй12 коммутаторы и оперативное запоминающее устройство 13, первьпл инфор,мационный 14 и первый адресный 15входы и первый тактовый вход 16 записи которого являются соответственноинформационным 17 и адресным 18 входами и тактовым входом 19 записи системы, с первого по двадцать первыйвыходы 20-40 устройства 4 управленияобменом, входы и выходы 41-96 блоковсистемы,Устройство 4 управления обменом(Фиг,.5) содержит демультиплексор 250,преобразователи 251 кодов, мультиплек сор 252, элемент 253 задержки, первый254 и второй 255 регистры адреса, первый 256 и второй 257 регистры и входыи выходы 258-273 узлов преобразователяУзел синхронизации (Фиг.6) образуют генератор 274.тактов счетчик 275и компаратор 276, а также входы и выходы 277-283 элементов узла.Первый Формирователь 109 адреса55(Фиг.7) включает коммутатор 284, элемент И 1 П 1 285 с задержкой, накапливающий сумматор 286 и регистр 287, а также входы и выходы 288-299. Второй Формирователь адреса (фиг.8)еодержит первый 300 и второй 301 регистры, элемент ИЛИ 302 с задержкой,накапливающий сумматор 303 и коммутатор 304, а также входы и выходы 305316 узлов формирователя,Сйстема работает слепующим образом.Система для сопряжения терминалов свычислительной машиной предназначенадля обеспечения обмена данными междутерминалами пользователей и ЭВМ иинтерактивного управления шаблонамиввода-вывода и параметрами процессовввода-вывода данных.В качестве терминальных устройств2, сопряжение которых с ЭВМ обеспечивает система, могут быть использованы телевизионные таблично-знаковыеиндикаторы.Мультиплексный канал может быть выполнеч согласно известному (Каган Б.МКаневский М.М. Цифровые вычислительные машины и системы, М,: Энергия,1975, с, 510, рис. 9.2).Групповое устройство 1 управлениятерминалами в составе системы обеспечивает интерфейс терминальных устройств 1с каналом 5 и может быть выполненокак аппаратное групповое устройствоуправления, которое в этом случае совместно с ТЗИ образует непрограммируемый модуль отображения,Групповое устройство 1 обеспечивает обмен с шестнадцатью терминальными устройствами 2. Сопряжение с каналом 5 осуществляется в соответствиис требованиями интерфейса ввода-вывода ОСТ 4.ГО.304.000 и ОСТ 4,Г 0,304001, Обмен с каналом 5 осуществляетсякак в монопольном, так и в мультиплексном режимах, причем считывание -всегда в монопольном,Выбор терминального устройства 2осуществляется по адресу, поступающему из канала в процессе начальной выборки в соответствии с требованиямиинтерфейса ввода-вывода, В процессе;своего функционирования групповоеустройство 1 обеспечивает выполнеггние следующих канальных команд: Про 1 11 11верить ввод-выводЗаписать"СЧИтатЬ 1, "ОСНОВНОЕ утОЧНЕНИЕгг,Стереть/Записать", "Считать ручнойввод и др,Кроме укаэанных команд расшифровываются приказы, передаваемые для терминальных устройств 2 в данных,5 15292При нормальном завершении операции по инициативе терминального устройства 2 в канал 5 выдается байт состояния с указателем Канал кончил "ВУ кончило , при завершении по инициативе канала сначала выдается байт .состояния с указателем пКанал кончил , а затем после завершения операции на терминальном устройстве 2 байт состояния с указателем "ВУ кончилоШифратор 7 режима предназначен для формирования команд запуска канальных процедур ввода и вывода, передаваемых в мультиплексный канал 5, и команд инициализации ввода, передаваемых в блок 6 шифрации команд, по сигналам инициализации ввода и выВторой преобразователь 10 кодаслужит для преобразования кодов ДКОИв двоично-битовый код,Прямая информационная связь системы с вычислительной машиной обеспечивается через общее поле памятиоперативного запоминающего устройства13, обмен с которым вычислительная машина осуществляет по выходу и первыминформационному 17, адресному 18 входам и тактовому входу 19 записи системы (по каналу прямого управления),Процесс ввода-вывода данных заключается в последовательном выполненииодной или нескольких операций вводавьвода из их следующей реализованнойв системе совокупности:1, "Ввод данных" - при этом с двенадцатого выхода 31 устройства 4 сигнал высокого уровня подается на вход55 первого коммутатора 11, пОсле чего замыкается цепь связи выхода 72канала 5 с в:.одом 75 запоминающегоустройства 3. Таким образом обеспечивается запись введенных с терминальвода, поступающим соответственно на 20 его входы 79 и 42, В ходе своего функционирования в составе системы шифратор 7 осуществляет перекодировку сигналов инициализации ввода и вывода в команды управления вводом-выво дом в соответствии с интерфейсом связи периферийных устройств и устройств оперативной памяти с каналами ЕС ЭВМ.Система обеспечивает режим ввода и режим вьвода данных, 30В режиме ввода данных процедура обслуживания производится по инициативе группового устройства 1 после того, как при очередном опросе терминальных устройств 2 выявлено требование на обслуживание одного из них, В этом случае групповое устройство 1 посылает в канал 5 требование обслуживания, по которому последний формирует и передает на вход 79 шифратора 7 сигнал инициализации ввода, Формируемая при этом шифратором 7 команда ввода с выхода 80 передается на вход 81 канала 5, а команда инициализации ввода с выхода 82 передается на вход 83 блока 6, По команде ввода канал 5 осуществляет прием из группового устройства 1 на вход 77 данных, введенных с одного из терминальных устройств 2, и их передачуна выход 72. В режи ме вывода данных начальная выборка производится по инициативе шифратора 7 после поступления на вход 42 с выхода 21 устройства 4 сигнала инициализации вывода, формируемая при этом шифратором 7 команда вывода с выхода 80 передается на вход 8 канала 5, По команде вывода канал 5 организует считывание информации из запоми 32 6нающего устройства 3 по входу 77 и ее передачу с выхода 76 на вход группового устройства 1,Блок 6 предназначен для организации процессов обработки команд вводавьвода, которые представляют собой служебную часть сообщений, полученных с первого выхода 72 канала 5. Служебная часть сообщений содержит идентификатор (физический адрес) терминального устройства 2, с которого вводится информация и идентификатор (код) активизированной на терминальном устройстве 2 функциональной клавиши,Запоминающее устройство 3 предназначено для оперативного храненияинформации данных, вводимых с терминальных устройств 2, и данных, предназначенных для вывода на терминальныеустройства 2,11 амять 8 прямого доступа обеспечивает долговременное хранение данныхорганизованных как последовательньп 1набор записей Фиксированной длины спрямой организацией, и прямой методдоступа к этому набору данных, Объемпамяти одной записи равен объему памяти запоминающего устройства 3,Первый преобразователь 9 кода предназначен для преобразования двоичнобитовых кодов в коды ДКОИ, 1529232ного устройства 2 данных в запоминающее устройство 3;2, "Ввод шаблона" - запись кодов символов, составляющих кадр изобра5 жения данных, введенных с терминального устройства 2 и считанных в запоминающее устройство 3, в память 8.1 ри этом с четвертого выхода 23 устройства 4 сигнал высокого уровня подается на вход 44 записи памяти 8, после чего в последнюю по входу 70 считывается содержимое запоминающего , устройства 3 и записывается в набор , данных в запись, адрес которой заданн кодом адреса, считанного с треть" его выхода 22 устройства 4 на адресный вход памяти 8;3. "Вывод шаблона" . - чтение кодов символов, составляющих запись набора данных памяти 8, в запоминающее устройство 3. При этом с пятого выхода 24 устройства 4 сигнал высокого уровня подается на вход 45 чтения памяти 8 и на вход 46 первого коммутатора 25 11, после чего замыкается цепь связи выхода памяти 8 с входом 75 запоминающего устройства 3 и содержимое записи на.бора данных, адрес которой задан кодом адреса считанного с третьего выхода 22 устройства 4 на адресный вход памяти 8, переписывается в за- поминающее устройство 3:4, "Ввод символов" - перепись группы кодов ДКОИ символов из запоминаю 35 щего устройства в о; еративное запоминающее устройство 13,. при этом с девятнадцатого выхода 38 устройства 4 сигнал высокого уровня годается на " вход 63 второго коммутатора 12, после чего замыкается цепь связи выхода запоминающего устройства 3 с инфор-. мационным входом оперативного запоминающего устройстьа 13. В соответствии с вырабатываемой на двадцать пер.вом выходе 40 устройства 4 последовательностью тактовых импульсов, пода-. ваемых на вход 65 записи оперативного запоминающего устройства 13 в последний по адресу, зацанному кодом50 адреса, считанного с двадцатого. выхода 39 устройства 4, на адресный вход 64 оперативного запоминающего устройства 13 переписывается иэ запоминающего устройства 3 информация,55 записанная в нем по адресу, заданному кодом адреса, считанного на адресный вход 47 запоминающего устройства 3 с шестого выхода 25 устройства 4: 5, "Вывод. символов" - перепись группы кодов ДКОИ символов из оперативного запоминающего устройства 13в запоминающее устройство 3. При этомс четырнадцатого выхода 33 устройства 4 сигнал высокого уровня подается на вход 57 первого коммутатора 1после чего замыкается цепь связи выхода оперативного запоминающего устройства с информационным входом 75 запоминающего устройства 3. В соответствии с вырабатываемой на седьмом выходе 26 устройства 4 последовательностью тактовых импульсов, подаваемых на вход 48 записи запоминающе"го устройства 3, в последний по адресу, заданному кодом адреса, считанного с шестого выхода 25 устройства 4, на адресный вход 47 запоминающегоустройства 3 переписывается иэ оперативного запоминающего устройства 13 информации, записанная в нем по ад -ресу, заданному кодом адреса, считанного на адресный вход 64 устройства 13 с двадцатого выхода 39 устройства 4;6, "Ввод чисел" - преобразование кодов ДКОИ цифровых групп данных в двоичнобитовые коды в соответствии с их форматом представления в памяти оперативного запоминающего устройства 13, При этом в соответствии с последовательностью тактовых импуль" сов, вырабатываемых на шестнадцатом выходе 35 устройства 4 и подаваемых на вход 59 записи преобразователя 10, в последний по его информационному входу 68 считывается иэ запоминающего устройства 3 информации, записанная в нем по адресу, заданному кодом адреса, считанного на адресный вход 47 запоминающего устройства 3 с шестого выхода 25 устройства 4.11 осле того, как в преобразователь10 будут переписаны коды ДКОИ подлежащей преобразованию группы цифровых данных, с восемнадцатого выхода 37 устройства 4 сигнал высокого уровня подается на вход 61 преобразователя 10 и вход 62 второго коммутатора 12,Замыкается цепь связи выхода преобразователя 10 с входом 66 оперативногозапоминающего устройства 13, В соответствии с последовательностью тактовых импульсов, вырабатываемых насемнадцатом выходе 36 устройства 4 иподаваемых на вход 60 чтения преобразователя 10, и аналогичной после 1529232 10довательностью тактовых импульсов, вырабатываемых на двадцать первом выходе 40 устройства 4 и подаваемых на вход 65 записи оперативного запоминаю" щего устройства 13, в последний по входу 66 считывается иэ преобразователя 10 информация, полученная в результате преобразования кодов ДКОИ цифровых групп данных в двоично-бито 1 О вый код представления этих данных, которая записывается в оперативное запоминающее устройство 13 по адресу, заданному кодом адреса, который считывается на адресный вход 64оперативного запоминающего устройства 13 с двадцатого выходами 39 устройства 4;7, "Вывод чисел" - преобразование двоично-битовых кодов чисел в группу кодов ДКОИ в соответствии с форматом представления чисел в памяти оперативного запоминающего устройства 13 и их шаблонами изображения на терминальном устройстве 2, При этом в соответствии с последовательностью тактовых импульсов, вырабатываемых на восьмом выходе 27 устройства 4 и подаваемых на вход 49 записи преобразователя 9 в последний по его информацион ному входу 94 считывается из оперативного запоминающего устройства 13 информация, записанная в нем по адресу, заданному кодом адреса, который считывается на адресный вход 64 опе - ративного запоминающего устройства 1335 с двадцатого выхода 39 устройства 4.После того, как в преобразователь 9 будут переписаны двоично-битовые коЬы,подлежащие преобразованию в коды ДКОИ, с одиннадцатого выхода 30 устройства 4,сигнал высокого уровня подается навход 53 преобразователя 9 и на вход 54 первого коммутатора 11, Замыкается цепь связи выхода преобра зователя 9 с информационным входом 75 запоминающего устройства 3, Далее в соответствии. с последовательностью тактовых импульсов, вырабатываемых на девятом выходе 28 устройства 4 и подаваемых на вход 50 чтения преобразо О вателя 9, и аналогичной последовательностью тактовых импульсов, вырабаты- - ваемых на седьмом выходе 26 устройства 4 и подаваемых на вход 48 записи запоминающего устройства 3, в последний по его информационному входу 75 считывается из преобразователя 9 информация, полученная в результате преобразования дноично-битовых чиселв коды ДКОИ их изображения, котораязаписывается в запоминающее устройство 3 по адресу, заданному кодом адреса, который считывается на адресньпвход 47 запоминающего устройства 3 сшестого выхода 25 устройства 4;8, "Запись кода" - запись специального кода по текущему адресу в запоминающее устройство .,3. При этом стринадцатого выхода 32 устройства 4сигнал высокого уровня подается навход 56 первого коммутатора 11, после чего замыкается цепь связи пятнадцатого выхода 34 устройства 4, По импульсу такта, поданному с седьмоговыхода 26 устройства 4 на вход 48 записи запоминающего устройства 3, впоследнее по его информационному входу 75 считывается с пятнадцатого выхода 34 устройства 4 специальный код,который записывается в запоминающееустройство 3 по адресу, заданному кодом адреса, который считывается наадресный вход 47 запоминающего устройства 3 с шестого выхода 25 устройства 4;9. "Вывод данных" - вывод содержимого памяти запоминающего устройства 3 общим потоком через канал 5 игрупповое устройство 1 на терминальное устройство 2, При этом с второговыхода 21 устройства 4 сигнал высокого уровня подается на вход 42 шифратора 7, являясь для последнего сигналом инициализации вывода, по которому командой вывода, переданной с выхода 80 на вход 81 канала 5, запускается канальная процедура вывода иинформация, записанная в запоминающееустройство 3, передается на терминальное устройство 2 в соответствии сего физическим адресом, записаннымвслужебной части общего потока выводимых данных,Каждой из перечисленных операцийввода-вывода поставлена в соответствие команда ввода в выво, Командыввода-вывода задают равномерными кодами и записывают в режиме интерактивного диалога с использованием терминального устройства 2 в оперативное запоминающее устройство 13, Изоперативного запоминающего устройства 13 коды команд ввода-вывода могутбыть считаны в память блока 6 подополнительной команде "Выборка команд", Команда "Выборка команд" ис1 115292йолняется по инициативе блока б, всеостальные команды передаются дляисполнения с выхода 85 блока б в уст,ройство 4 по его выходу и инициализи-руются к исполнению по сигналу такта,5поступившему на вход 91 устройства 4выхода 87 блока 6, Тактовый сигналисполнения команды ввода-вывода передается с первого выхода 20 устройства 4 на вход 41 блока 6,Формула изобретения 1, Система для сопряжения термина лов с вычислительной машиной, содержащая групповое устройство управления терминалами, мультиплексный канал оперативное запоминающее устройство, устройство управления обменом, 20 блок шифрации команд, первый коммутатор о т л и ч а ю щ а я с я тем, что, с целью расширения класса решае" мых задач, она содержит шифратор ре- ,жима, буферное запоминающее устройство, второй коммутатор, первый и второй преобразователи кодов и память прямого доступа, причем группа инфор. мационно-управляющих входов-выходов группового устройства управления тер п миналамИФувляется группой входов-высиходов системы для подклочения к терминалам, информационные вход и выход группового устройства управления терминалами соединены соответственно35 с первыми инфор. з.,онными выходом и входом мультиплексно 1 канала, второй информационный выход которого со"- единен с первыми информационными вхо" цами блока шифрации команд и перво 40 го коммутатора, второй и третий информационные входы которого соединены соответственно с выходами памяти прямого доступа и первого преобразователя кода, информационный вход которого соединен с выходом оперативного запоминающего устройства, четвертым информационным входом первого комму-татора вторым информационным входом блока шифрации команд и выходом системы для подключеиия к информационной шине вычислительной машины, первый и второй выходы шифратора режима соединены соответственно с режимными входами блока шифрации команд и муль-. ) типлексного канала, управляющий выход которого соединен с первым входом шифратора режима, выход буферного запоминающего устройства соединен с 32 12вторым информационным входом мультиплексного канала, информационнымивходами памяти прямого доступа и второго преобразователя кода и первыминформапионным входом второго коммутатора, второй информационный входкоторого соединен с выходом второгопреооразователя кода, выход второгокоммутатора соединен с первым информационным входом оперативного запоминающего устройства, выход первогокоммутатора соединен с информационным входом буферного запоминающегоустройства, первый выход устройства управления обменом соединен с тактовым входом блока шифрации команд,группа выходов которого соединена сгруппой командных входов устройствауправления обменом, второй выход которого соединен с вторым входом шифратора режима, третий четвертый ипятый выходы устройства управленияобменом соединены соответственно садресным, тактовым входами памятипрямого доступа и объединенными входом чтения памяти прямого доступа ипятым информационным входом первогокоммутатора, шестой и седьмой выходы соединены с входами адреса и записи буферного запоминающего устройства, восьмой и девятый выходы - свходами записи и чтения первого преобразователя кода, десятый выход - свходами управления первого и второго преобразователей кодов, одиннадцатый выход - с тактовыми входами первого преобразователя кода и первогокоммутатора, управляющие входы которого соединены с двенадцатого попятнадцатый выходами устройства управления обменом, шестнадцатый и семнадцатый выходы которого соединеныс входами записи и чтения второгопреобразователя кода,. восемнадцатыйвыход - с тактовыми входами второгопреобразователя кода,и второго коммутатора, с девятнадцатого по двадцатьпервый выходы соединены соответственно с управляющим входом второгокоммутатора, первым адресным и тактовым входами оперативного запоминающего устройства, вторые информационный, адресный входы и вход записи которого являются входами системы дляподключения к одноименным выходамвычислительной машины,2, Система по и, 1, о т л и ч а ющ а я с. я тем, что устройство управ 159232ления обменом содержит дешифратор,шифратор, семь узлов синхронизации, три регистра, четыре элемента ИЛИ и два формирователя адреса причем информаФ5 ционные входы дешифратора и шифратора объединены и являются первым входом группы командных входов устройства, тактовые входы дешифратора и шифратора объединены и являются вторым вхо- О дом группы командных входов устройства, первый выход дешифратора является вторым выходом устройства, с второго по одиннадцатый выходы дешифратора соединены соответственно: второй - с первым тактовым входом первого формирователя адреса и с первым входом первого элемента ИЛИ, третий - с входом запуска первого узла синхронизации и является девятнадцатым выходом 20 устройства, четвертый - с первыми входами второго и третьего элементов ИЛИ и является тринадцатым выходом устройства, пятый - с первым тактовым входом второго формирователя адреса и 2 с вторым входом первого элемента ИЛИ, шестой - с входом запуска второго узла синхронизации и является.четырнадцатым выходом устройства, седьмой - с вторым входом третьего элемента ИЛИ и является четвертым выходом устройства, восьмой - с третьим входом третьего элемента ИЛИ и является пятым выходом устройства, девятый - с входом запуска третьего узла синхронизации, десятый - с входом запуска четвертого узла синхронизации, одиннадцатый - с входом запуска пятого узла синхронизации и является двенадцатым выхо - дом устройства, с первого по шестой выходы шифратора соединены соответственно: первый - с первым информационным входом первого формирователя адреса, второй - с информационным входом второго формирователя адреса, тре" тий - с входами режима первого и второго узлов синхронизации, четвертый - с информационными входами первого и второго регистров и является десятым выходом устройства, пятый является третьим выходом устройства и шестой является пятнадцатым выходом устройства, второй информационный вход первого формирователя адреса является третьим входом группы командных входов устройства, управляющий вход первого формирователя адреса является четвертым входом группы командных входов устройства, соединен с третьим входом первого элсмен - та ИЛИ и с входом начальной установки второго формирователя адреса, второй тактовый вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с первым выходом первого узла синхронизации, с первым входом четвертого элемента ИЛИ и является двадцать первым выходом устройства, второй выход первого узла синхронизации соединен с четвертым входом первого элемента ИЛИ, пятый вход которого соединен с первым выходом второго узла синхронизации, второй выход которого является седьмым выходом устройства и соединен с вторым входом четвертого элемента ИЛИ и с третьим входом второго элемента ИЛИ, третий вход четвертого эле-. мента ИЛИ соединен с первым выходом третьего узла синхронизации и является девятым выходом устройства, второй выход третьего узла синхронизации является одиннадцатым выходом устройства и соединен с входом запуска шестого узла синхронизации, вход режима которого соединен с выходом второго регистра и с входом режима,четвертого узла синхронизации, первый выход которого является семнадцатым выходом устройства и соединен с четвертым входом второго элемента ИЛИ, пятый вход которого соединен с первымвыходом пятого узла синхронизации, второй выход которого соединен с шестым входом первого элемента ИЛИ, седьмой вход которого соединен с первым выходом седьмого узла синхронизации, вход режима которого соединен с входомрежима третьего узла синхронизации и с выходом первого регистра, второй выход седьмого узла синхронизации является шестнадцатым выходом устройства и соединен с четвертым входом четвертого элемента ИЛИ, выход кото - рого соединен с вторым тактовым входом первого формирователя адреса, выход которого является двадцатым выходом устройства, восьмой вход первого элемента ИЛИ соединен с первым вы" ходом шестого узла синхронизации, второй выход которого является восьмым выходом устройства и соединен с шестым входом второго элемента ИЛИ, второй выход четвертого узла синхронизации соединен с входом запуска седьмого узла синхронизации и являетсявосемнадцатым выходом устройства, вы1529232 15Йод третьего элемента ИЛИ соединен с девятым входом первого элемента ИЛИ, выход которого является первым выходом устройства выход третьего регист 15 ра соединен с входом режима пятого узла синхронизации, выход второго формирователя адреса являеТся шестым выходом устройства. 3, Система о п. 1, о т л и ч а юш а я с я тем, что блок шифрации команд содержит узел синхронизации, три регистра, схему сравнения, ре 15 гистр сдвига, два узла ассоциативной па,ятиэлемент задержки, регистр ад" ре;.а и узел пам;ли, информационный вх.д которого является. вторым информационным входом блока, а вход чтения является тактовым входом блока и соединен с входом записи третьего регистра и с входом элемента задержки, выход которого является первым выходом группы выходов блока и соединен с тактовым входом регистра адреса, выход которого соединен с адресным входом узла памяти, вход записи которого соединен с выходом "Равно" схе" мы сравнения, выход "Неравно" которой соединен с тактовым входом второго узла ассоциативной памяти и с входом записи регистра адреса, информационный вход которого соединен с выходомвторого узла ассоциативной памяти,информационный вход которого соеди,нен с выходом регистра сдвига, с ин-,формационным входом первого узла ассоциативной памяти и с первым информационйым входом схемы сравнения, тактовый вход которой соединен с первымвыходом узла синхронизации, с тактовым входом первого узла ассоциативнойпамяти и является вторым выходом груп"пы выходов блока, второй информацион"ный вход схемы сравнения. соединен свыходом второго регистра, выход первого регистра соединен с входом режимаузла синхронизации, вход запуска которого является режимным входом блокаи соединен с входом установки нуля регистра сдвига, информационный вход которого является первым информационнымвходом блока, а тактовый вход соединен с вторым выходом узла синхронизации, выход узЛа памяти соединен с информационным входом.третьего регистра, выход которого является третьим выходом группывыходов блока, выход первого узлаассоциативной памяти является четвертым выходом группы выходов блока.

СмотретьЗаявка

4308293, 20.07.1987

ПРЕДПРИЯТИЕ ПЯ В-2655

БЫКОВ ВАЛЕРИЙ КОНСТАНТИНОВИЧ, САМОЙЛОВА ОЛЬГА НИКОЛАЕВНА, ТОЛМАЧ АЛЛА ВЛАДИМИРОВНА, БРАТЕННИКОВА СВЕТЛАНА НИКОЛАЕВНА

МПК / Метки

МПК: G06F 13/00

Метки: вычислительной, машиной, сопряжения, терминалов

Опубликовано: 15.12.1989

Код ссылки

<a href="https://patents.su/13-1529232-sistema-dlya-sopryazheniya-terminalov-s-vychislitelnojj-mashinojj.html" target="_blank" rel="follow" title="База патентов СССР">Система для сопряжения терминалов с вычислительной машиной</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Канал связи для одновременной передачи напряжения питания, синхроимпульсов и информации

Случайный патент: Способ биохимической очистки сточных вод