Формирователь кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1145469

Автор: Ярмолик

Текст

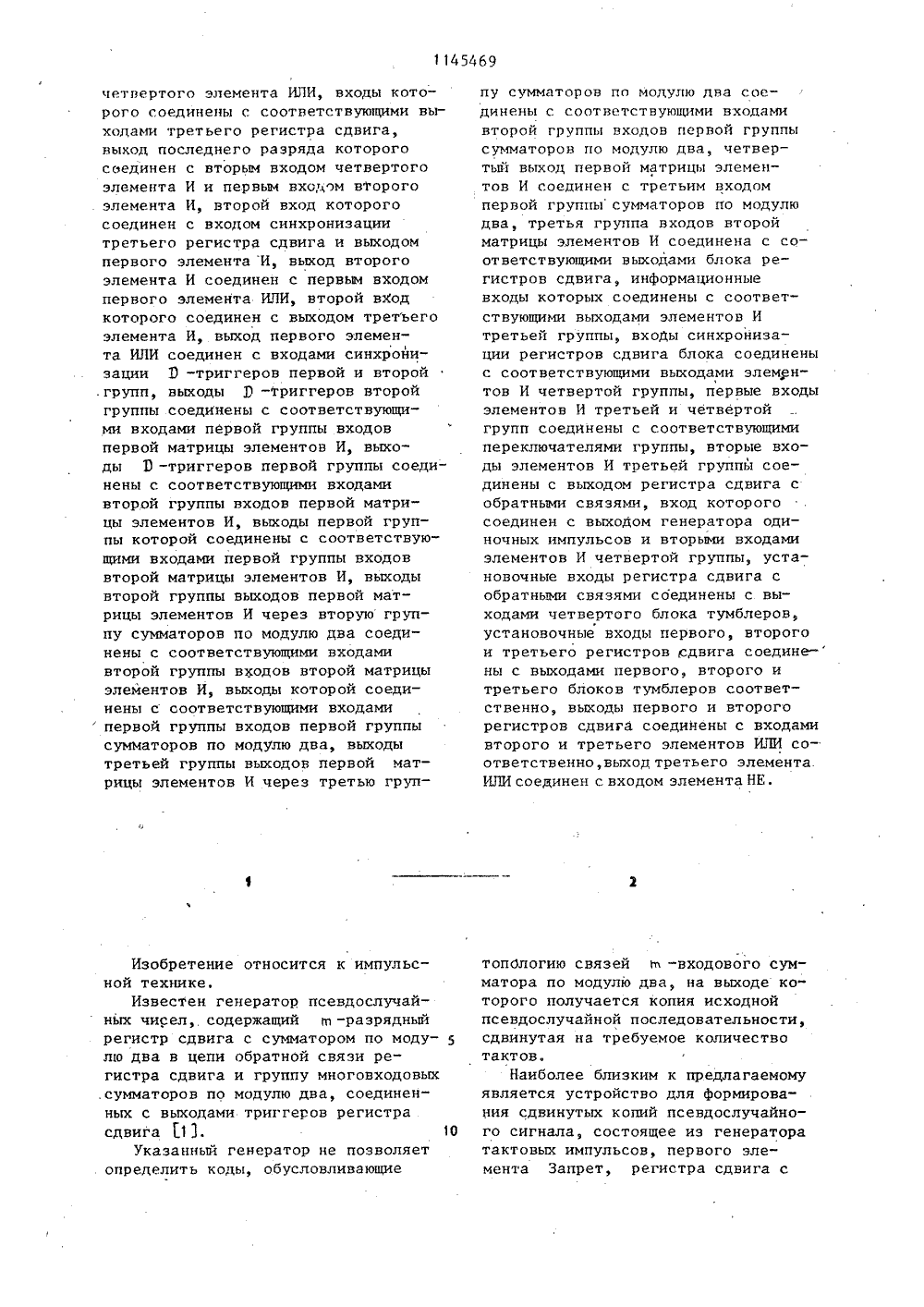

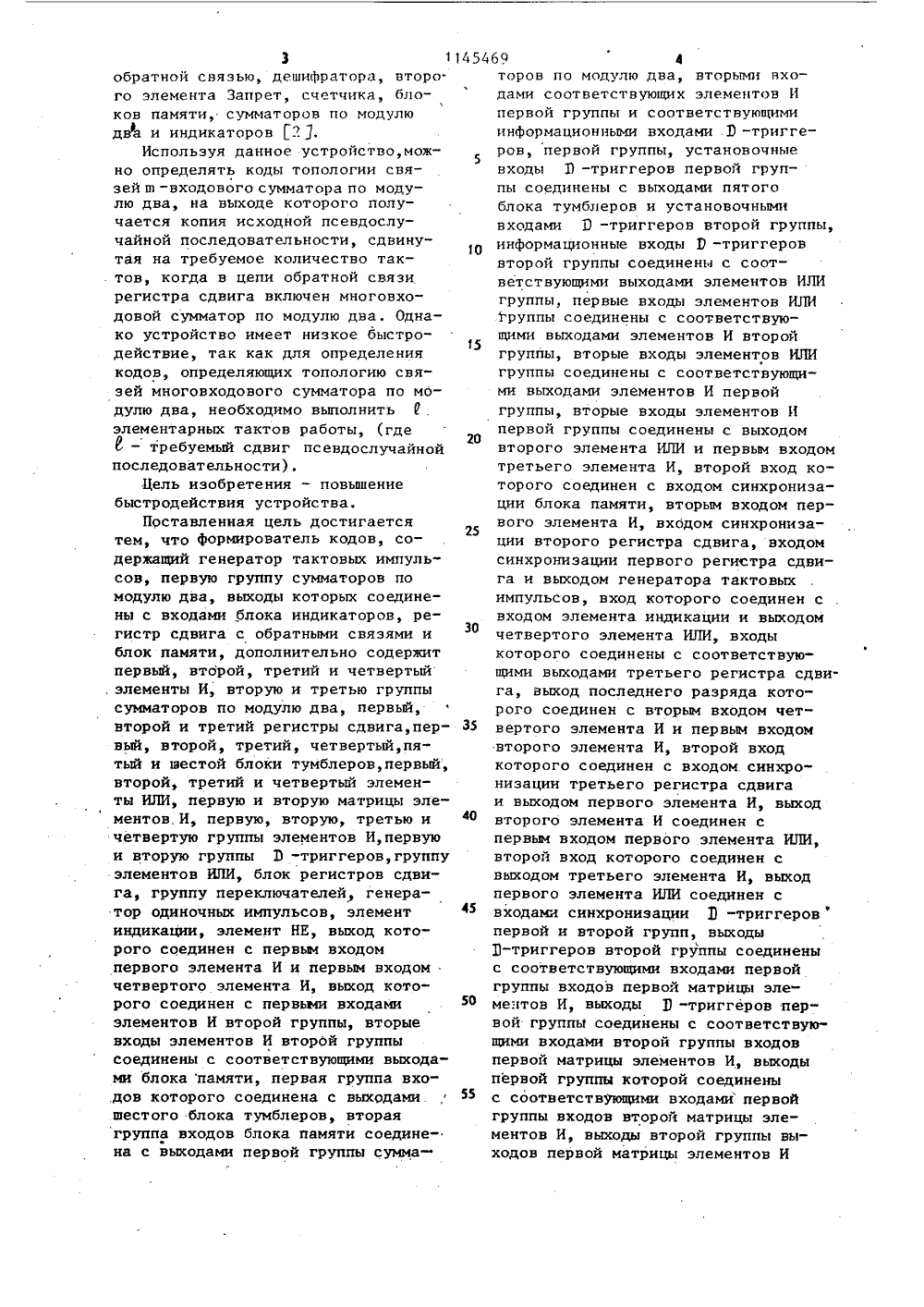

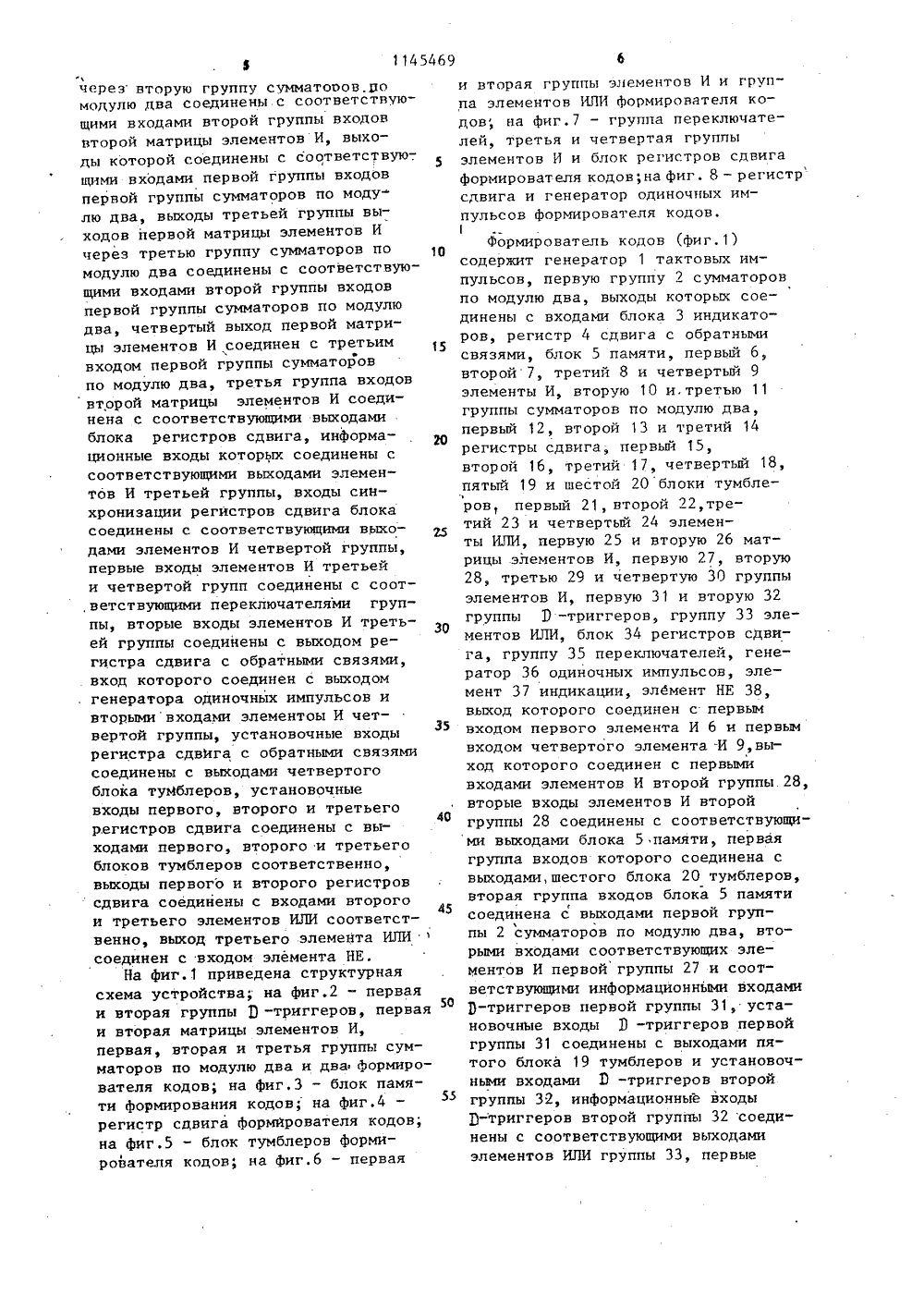

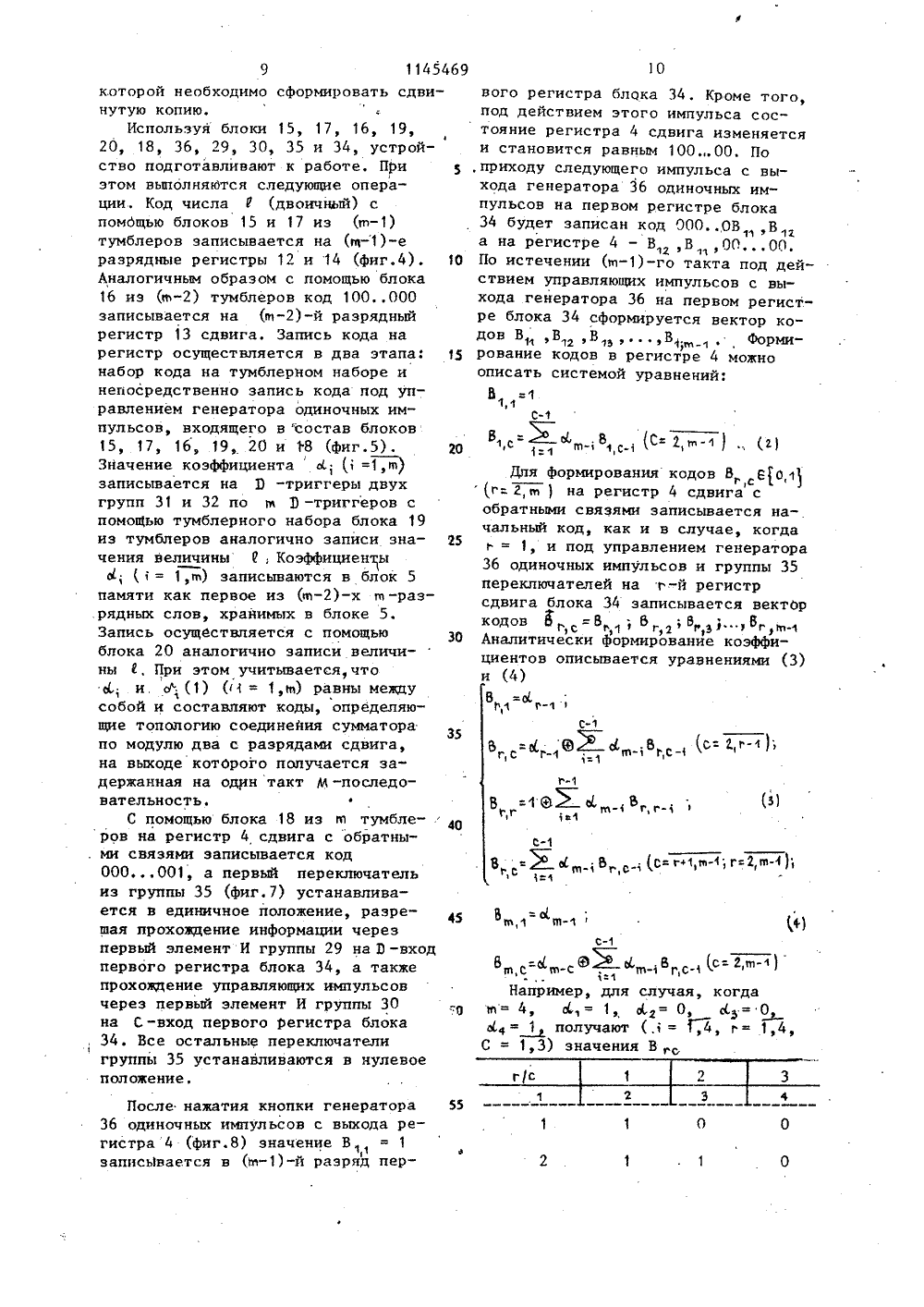

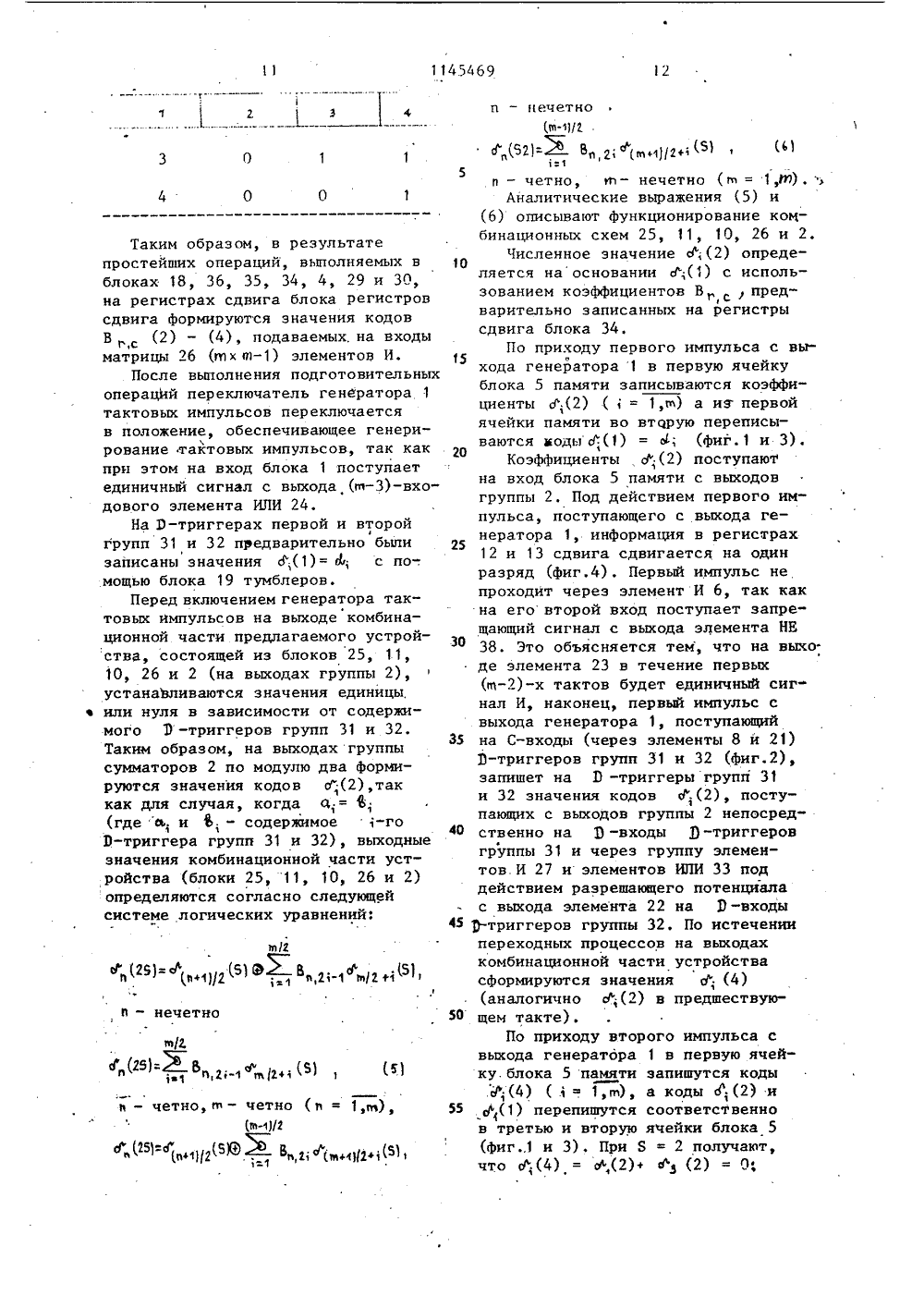

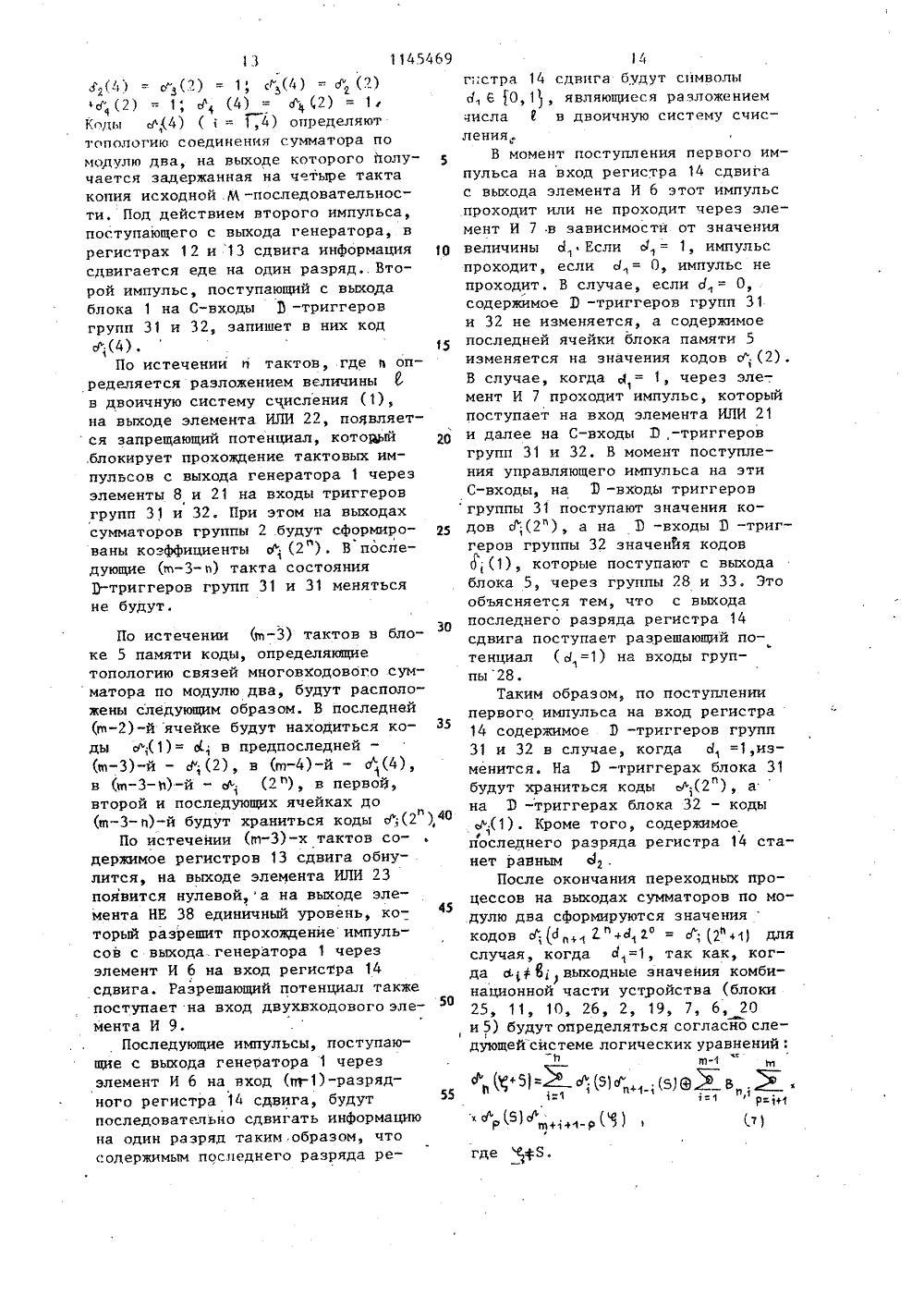

ОЮЗ СОВЕТСНИХ ОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 546 119) 51) НОЗ К 38 ТЕ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ПИСАНИЕ ИЭОБРЕВТОРСНОМУ СВИДЕТЕЛЬСТВ(71) Минский радиотехнический институт(56) 1. Яковлев В.В., Федоров Р.Ф.Вероятностные вычислительные машины.Л., "Машиностроение", 1974, с, 54,рис, 118,2. Авторское свидетельство СССРВ 527012, кл. Н 03 К 3/00, 1974.(54)(57) ФОРМИРОВАТЕЛЬ КОДОВ, содержащий генератор тактовых импульсов,первую группу сумматоров по модулюдва, выходы которых соединены с входами блока индикаторов, регистрсдвига с обратными связями и блокпамяти, о т л и ч а ю щ и й с ятем, что, с целью повышения быстродействия формирователя кодов, ондополнительно содержит первый, второй, третий и четвертый элементы И,вторую и третью группы сумматоровпо модулю два, первый, второй и третий регистры сдвига, первый, второй,третий, четвертый, пятый и шестойблоки тумблеров, первый, второй,третий и четвертый элементы ИЛИ,первую и вторую матрицы элементов И,первую, вторую, третью и четвертуюгруппы элементов И, первую ивторую группы 3 -триггеров, группуэлементов ИЛИ, блок регистров сдвига, группу переключателей, генератор одиночных импульсов, элементиндикации, элемент НЕ, выход которого соединен с первьм входом первогоэлемента И и первьм входом четвертого элемента И, выход которогосоединен с первыми входами элементов И второй группы, вторые входыэлементов И второй группы соединеныс соответствующими выходами блокапамяти, первая группа входов которого соединена с выходами шестогоблока тумблеров, вторая группавходов блока памяти соединена с выходами первой группы сумматоров помодулю два, вторыми входами соответствующих элементов И первой группыи соответствующими информационнымивходами 2 -триггеров первой группы, установочные входы 3 -триггеровпервой группы соединены с выходамипятого блока тумблеров )1 установочными входами 1) -триггеров второйгруппы, информационные входы 3 -триггеров второй группы соединены ссоответствующими выходами элементов ИЛИ группы, первые входы элементов ИЛИ группы соединены с соответствующими выходами элементов И второй группы, вторые входы.элементов ИЛИ группы соединены ссоответствующими выходами элементов И первой группы, вторые входыэлементов И первой группы соединеныс выходом второго элемента ИЛИ ипервым входом третьего элемента И,второй вход которого соединен свходом синхронизации блока памяти,вторым входом первого элемента И,входом синхронизации второго регистра сдвига, входом синхронизации первого регистра сдвига и выходом генератора тактовых импульсов, вход которого соединен с входом элемента индикации и выходомВНЧНПИ . Заказ 1187/4ЪфРаа 872 ПодасаоеШй ффПатевтфюДр Яфе Пфое11454 б 9 четвертого элемента ИЛИ, входы которого соединены с соответствующими выходами третьего регистра сдвига, выход последнего разряда которого соединен с вторым входом четвертого элемента И и первым входом второго элемента И, второй вход которого соединен с входом синхронизации третьего регистра сдвига и выходом первого элемента И, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход первого элемента ИЛИ соединен с входами синхронизации Э -триггеров первой и второй .групп, выходы 3 -триггеров второй группы соединены с соответствующими входами первой группы входов первой матрицы элементов И, выходы Ю -триггеров первой группы соединены с соответствующими входами второй группы входов первой матрицы элементов И, выходы первой группы которой соединены с соответствующими входами первой группы входов второй матрицы элементов И, выходы второй группы выходов первой матрицы элементов И через вторую группу сумматоров по модулю два соединены с соответствующими входами второй группы входов второй матрицы элементов И, выходы которой соединены с соответствующими входамипервой группы входов первой группы сумматоров по модулю два, выходы третьей группы выходов первой матрицы элементов И через третью групИзобретение относится к импульсной технике,Известен генератор псевдослучайных чисел, содержащий в -разрядный регистр сдвига с сумматором по моду лю два в цепи обратной связи регистра сдвига и группу многовходовых .сумматоров по модулю два, соединенных с выходами триггеров регистрасдвига 13. 1 ОУказанный генератор не позволяет определить коды, обусловливающие пу сумматоров по модулю два соединены с соответствующими входамивторой группы входов первой группысумматоров по модулю два, четвертый выход первой матрицы элементов И соединен с третьим входомпервой группы сумматоров по модулюдва, третья группа входов второйматрицы элементов И соединена с соответствующими выходами блока регистров сдвига, информационныевходы которых соединены с соответствующими выходами элементов Итретьей группы, входы синхронизации регистров сдвига блока соединеныс соответствующими выходами элементов И четвертой группы, первые входыэлементов И третьей и четвертойгрупп соедннены с соответствующимипереключателями группы, вторые входы элементов И третьей группы соединены с выходом регистра сдвига собратными связями, вход которогосоединен с выхоДом генератора одиночных импульсов и вторыми входамиэлементов И четвертой группы, установочные входы регистра сдвига собратными связями соединены с выходами четвертого блока тумблеров,установочные входы первого, второгои третьего регистров сдвига соедине-ны с выходами первого, второго итретьего блоков тумблеров соответственно, выходы первого и второгорегистров сдвига соединены с входамивторого и третьего элементов ИЛИ соответственно, выход третьего элемента.ИЛИ соединен с входом элемента НЕ. топОлогию связей ь -входового сумматора по модулю два, на выходе которого получается копия исходной псевдослучайной последовательности, сдвинутая на требуемое количество тактов.Наиболее близким к предлагаемому является устройство для формирования сдвинутых копий псевдослучайного сигнала, состоящее из генератора тактовых импульсов, первого элемента Запрет, регистра сдвига с3 1обратной связью, дешифратора, второ.го элемента Запрет, счетчика, блоков памяти, сумматоров по модулюдва и индикаторов1,Используя данное устройство,можно определять коды топологии связей ш -входового сумматора по модулю два, на выходе которого получается копия исходной псевдослучайной последовательности, сдвинутая на требуемое количество так. тов, когда в цепи обратной связирегистра сдвига включен многовходовой сумматор по модулю два. Однако устройство имеет низкое быстродействие, так как для определениякодов, определяющих топологию связей многовходового сумматора по модулю два, необходимо выполнитьэлементарных тактов работы, (где0 - требуемый сдвиг псевдослучайнойпоследовательности).Цель изобретения - повьпненнебыстродействия устройства.Поставленная цель достигаетсятем, что Формирователь кодов, содержащий генератор тактовых импульсов, первую группу сумматоров помодулю два, выходы которых соединены с входами блока индикаторов, регистр сдвига с обратными связями иблок памяти, дополнительно содержитпервый, второй, третий и четвертыйэлементы И, вторую и третью группысумматоров по модулю два, первый,второй и третий регистры сдвига,первый, второй, третий, четвертый,пятый и шестой блоки тумблеров, первый,второй, третий и четвертый элементы ИЛИ, первую и вторую матрицы элементов И, первую, вторую, третью ичетвертую группы элементов И,первуюи вторую группы Э -триггеров, группуэлементов ИЛИ, блок регистров сдвига, группу переключателей, генератор одиночных импульсов, элементиндикации, элемент НЕ, выход которого соединен с первым входомпервого элемента И и первым входомчетвертого элемента И, выход которого соединен с первьии входамиэлементов И второй группы, вторыевходы элементов И вторбй группысоединены с соответствующими выходами блока памяти, первая группа входов которого соединена с выходами.шестого блока тумблеров, втораягруппа входов блока памяти соединена с выходами первой группы сумма 145469 4 5 1 О 15 20 25 30 35 40 45 50 торов по модулю два, вторыми входами соответствующих элементов Ипервой группы и соответствующимиинформационными входами Э -триггеров, первой группы, установочныевходы 3 -триггеров первой группы соединены с выходами пятогоблока тумблеров и установочнымивходами 0 -триггеров второй группы,информационные входы Р -триггероввторой группы соединены с соответствующими выходами элементов ИЛИгруппы, первые входы элементов ИЛИгруппы соединены с соответствующими выходами элементов И второйгруппы, вторые входы элементов ИЛИгруппы соединены с соответствующими выходами элементов И первойгруппы, вторые входы элементов Ипервой группы соединены с выходомвторого элемента ИЛИ и первым входомтретьего элемента И, второй вход которого соединен с входом синхронизации блока памяти, вторым входом первого элемента И, входом синхронизации второго регистра сдвига, входомсинхронизации первого регистра сдвига н выходом генератора тактовыхимпульсов, вход которого соединен свходом элемента индикации и выходомчетвертого элемента ИЛИ, входыкоторого соединены с соответствующими выходами третьего регистра сдвига, выход последнего разряда которого соединен с вторым входом четвертого элемента И и первым входомвторого элемента И, второй входкоторого соединен с входом синхронизации третьего регистра сдвигаи выходом первого элемента И, выходвторого элемента И соединен спервым входом первого элемента ИЛИ,второй вход которого соединен свыходом третьего элемента И, выходпервого элемента ИЛИ соединен свходаж синхронизации 3 -триггеровпервой и второй групп, выходы3-триггеров второй группы соединеныс соответствующими входами первойгруппы входов первой матрицы элементов И, выходы Р -триггеров первой группы соединены с соответствующими входами второй группы входовпервой матрицы элементов И, выходыпервой группы которой соединеныс соответствующими входами первойгруппы входов второй матрицы элементов И, выходы второй группы выходов первой матрицы элементов И1145469 через вторую группу сумматоров.помодулю два соединены.с соответствующими входами второй группы входоввторой матрицы элементов И, выходы которой соединены с соответствую-,щими входами первой группы входовпервой группы сумматоров по модулю два, выходы третьей группы выходов первой матрицы элементов Ичерез третью группу сумматоров помодулю два соединены с соответствующими входами второй группы входовпервой группы сумматоров по модулюдва, четвертый выход первой матрицы элементов И соединен с третьимвходом первой группы сумматоровпо модулю два, третья группа входоввторой матрицы элементов И соединена с соответствующими выходамиблока регистров сдвига, информационные входы которых соединены ссоответствующими выходами элементов И третьей группы, входы синхронизации регистров сдвига блокасоединены с соответствующими выходами элементов И четвертой группы,первые входы элементов И третьейи четвертой групп соединены с соот,ветствующими переключателями группы, вторые входы элементов И третьей группы соединены с выходом ре"гистра сдвига с обратными связями,вход которого соединен с выходомгенератора одиночных импульсов ивторымивходами злементоы И четвертой группы, установочные входырегистра сдвига с обратными связямисоединены с выходами четвертогоблока тумблеров, установочныевходы первого, второго и третьего40регистров сдвига соединены с выходами первого, второго и третьегоблоков тумблеров соответственно,выходы первого и второго регистровсдвига соединены с входами второгои третьего элементов ИЛИ соответственно, выход третьего элемента ИЛИсоединен с входом элемента НЕ.На фиг.1 приведена структурнаясхема устройства; на фиг.2 - перваяи вторая группы 3 -триггеров, первая50и вторая матрицы элементов И,первая, вторая и третья группы сумматоров по модулю два и два 1 Формирователя кодов; на фиг,З - блок памяти Формирования кодов на фиг.455регистр сдвига формирователя кодов;на фиг.5 - блок тумблеров Формирователя кодов; на Фиг.6 - первая и вторая группы элементов И и группа элементов ИЛИ Формирователя кодов, на фиг.7 - группа переключателей, третья и четвертая группыэлементов И и блок регистров сдвигаформирователя кодов;на фиг. 8 - регистрсдвига и генератор одиночных импульсов формирователя кодов.1Формирователь кодов (фиг. 1)содержит генератор 1 тактовых импульсов, первую группу 2 сумматоровпо модулю два, выходы которых соединены с входами блока 3 индикаторов, регистр 4 сдвига с обратнымисвязями, блок 5 памяти, первый 6,второй 7, третий 8 и четвертый 9элементы И, вторую 10 и,третью 11группы сумматоров по модулю два,первый 12, второй 13 и третий 14регистры сдвига, первый 15,второй 16, третий 17, четвертый 18,пятый 19 и шестой 20 блоки тумбле 1ров, первый 21, второй 22,третий 23 и четвертый 24 элементы ИЛИ, первую 25 и вторую 26 матрицы элементов И, первую 27, вторую28, третью 29 и четвертую ЗО группыэлементов И, первую 31 и вторую 32группы В -триггеров, группу 33 элементов ИЛИ, блок 34 регистров сдвига, группу 35 переключателей, генератор 36 одиночных импульсов, элемент 37 индикации, элемент НЕ 38,выход которого соединен с первымвходом первого элемента И 6 и первымвходом четвертого элемента -И 9,выход которого соединен с первымивходами элементов И второй группы 28,вторые входы элементов И второйгруппы 28 соединены с соответствующими выходами блока 5 памяти, перваягруппа входов которого соединена свыходами, шестого блока 20 тумблеров,вторая группа входов блока 5 памятигсоединена с выходами первой группы 2 сумматоров по модулю два, вторыми входами соответствующих элементов И первой группы 27 и соответствующими информационными входами3-триггеров первой группы 31, установочные входы 3 -триггеров первойгруппы 31 соединены с выходами пятого блока 19 тумблеров и установочными входами 2 -триггеров второйгруппы 32, информационные входы-триггеров второй группь 1 32 соединены с соответствующими выходамиэлементов ИЛИ группы 33, первые:1,щ) определяющих вид полинома,для входы элементов ИЛИ группы 33 соелицены с соответствующими выходами эпемецтов И второй группы 28, вторые входы элементов ИЛИ группы 33 соединены с соответствующими выходами 5 элементов И первой группы 27, вторые входы элементов И первой группы 27 соединены с выходом второго элемента ИЛИ 22 н первым входом третьего элемента И 8, второй вход которого 10 соединен с входом синхронизации бло. ка 5 памяти, вторым входом первого элемента И б,входом синхронизации второго регистра 13 сдвигавходом синхро - низации первого регистра 12 сдвига и 15 выходом генератора 1 тактовых имс пульсов, вход которого соединен с входом элемента 37 индикации и выходом четвертого элемента ИЛИ 24, входы которого соединены с соответствующими выходами третьего регистра 14 сдвига, выход последнего разряда которого соединен с вторым входом четвертого элемента И 9 и первым входом второго элемента И 7, 25 второй вход которого соединен с входом синхронизации третьего регистра 14 сдвига с выходом первого элемента И 6, выход второго элемента И 7 соединен с первым входом ЗО первого элемента ИЛИ 21, второй вход которрго соединен с выходом третьего элемента И 8, выход первого элемента ИЛИ 21 соединен с входами синхронизации 2 в .триггеров первой 31 и второй 32 групп, выходы Р -триггеров второй .группы 32 соединены с соответствующими входами первой группы входов первой матрицы 25 элементов И, выходы Р -триггеров 4 О первой группы 31 соединены с соответствующими входами второй группы входов первой матрицы 25 элементов И, выходы первой группы которой соединены с соответствующими входа ми первой группы входов второй матрицы 26 элементов И, выходы второй группы выходов первой матрицы 25 .элементов И через вторую группу 10 сумматоров по модулю два соединены с,соответствующими входами второй группы входов второй матрицы 26 элементов И, выходы которой соединены с соответствующими входами первой группы входов первой группы 2 сумматоров по модулю два, выходы третьей группы выходов первой мат-. рицы 25 элементов И через третью группу 11 сумматоров по модулю два соединены с соответствующими входами второй группы входов первой группы 2 сумматоров по модулю два, четвертый выход первой матрицы 25 элементов И соединен с третьим входом первой группы 2 сумматоров по модулю два, третья группа входов второй матрицы 26 элементов И соединена с. соответствующими выходами блока 34 регистров сдвига, информационные входы которых соединены с соответствующими выходами элементов И третьей группы 29, входы синхронизации регистров сдвига блока 34 соединены с соответствующими выходами элементов И четвертой группы 30, первые входы элементов И третьей 29 и четвертой 30 групп соединены с соответствующими переключателями группы 35,вторые вхо-. ды элементов И третьей группы 29 соединены с выходом регистра 4 сдвига с обратными связями, вход которого соединен с выходом генератора 36 одиночных импульсов и вторыми входами элементов И четвертой группы 30, установочные входы регистра 4 сдвига с обратными связями соединены с выходами четвертого блока 18 тумблеров, установочные входы первого 12, второго 13 и третьего 14 регистров сдвига соединены с выходами первого 15, второго 16 и третьего 17 блоков тумблеров соответственно, выходы первого 12 и второго 13 регистров сдвига соединены с входами второго 22 и третьего 23 элементов ИЛИ соот- ветственно, выход третьего элемента ИЛИ 23 соединен с входом элемен-та НЕ 38.формирователь кодов работает следующим образом. Исходной информацией для получе-. ния кодов, определяющих топологию связей многовходового сумматора по модулю два, является величина сдвиЬ Ъ2 1=О 2+а . +. ,2 аг+а,Ъ,где ф 1;, =11 д;60,1(: 1,п- двоичные цифры числа 1 и, кроме того,Ю-последовательность в виде значения в и коэффициентов 6 в 1 0,11145469 10 которой необходимо сформировать сдвинутую копию.Используя блоки 15, 17, 16, 19,20, 18, 36, 29, 30, 35 и 34, устройство подготавливают к работе. Приэтом выполняются следующие операции. Код числа 0 (двоичньпЪ) спомОщью блоков 15 и 17 из (п)тумблеров записывается на (ы)-еразрядные регистры 12 и 14 (фиг.4). 1 ОАналогичным образом с помощью блока16 из (в) тумблеров код 100000записывается на (в)-й разрядныйрегистр 13 сдвига. Запись кода нарегистр осуществляется в два этапа: 15набор кода на тумблериом наборе инепосредственно запись кода под управлением генератора одиночных импульсов, входящего в состав блоков15, 17, 16, 19, 20 и 18 (фиг.5). 20Значение коэффициентао; (1 =1,в)записывается на П -триггеры двухгрупп 31 и 32 по ю 1) -триггеров спомощью тумблерного набора блока 19из тумблеров аналогично записи значения величины 1, КоэффициентыЫ; ( 1 = 1,в) записываются в блок 5памяти как первое из (а)-х щ -раз.рядных слов, храйимых в блоке 5.Запись осуществляется с помощьюблока 20 аналогично записи величины 2, При этом учитываетея,чтоеС; и. У,(1) (1 = 1,в) равны междусобой и составляют коды, определяющие топологию соединения сумматорапо модулю два с разрядами сдвига,на выходе которого получается задержанная на один такт И -последовательность.С помощью блока 18 из ю тумбле- . 40ров на регистр 4 сдвига с обратны. ми связями записывается код000001, а первый переключательиз группы 35 (фиг.7) устанавливается в единичное положение, разрешая прохождение информации черезпервый элемент И группы 29 на 2 -входпервого регистра блока 34, а такжепрохождение управляющих импульсовчерез первый элемент И группы 30на С -вход первого регистра блока34. Все остальные переключателигруппы 35 устанавливаются в нулевоеположение,30 с8 в с фв-с-фтЬгс- (с Например, для случая, когда-.О в= 4, с,= 1, 01= О, с 5= О ь= 1 получают (,1= 7,4, г= 1,4,С = 1,3) значения В , ра 5рене а выходаВ,=11зряд пер 1 1 После нажатия кнопки 36 одиночных импульсов с гистра 4 (фиг.8) значенн записьвается в (М)-й р вого регистра блока 34. Кроме того, под действием этого импульса состояние регистра 4 сдвига изменяется и становится равным 10000. По приходу следующего импульса с выхода генератора 36 одиночных импульсов на первом регистре блока 34 будет записан код ООООВ В111 а а на регистре 4 - В ,В,ОООО По истечении (ю)-го такта под действием управляющих импульсов с выхода генератора 36 на первом регистре блока 34 сформируется вектор код в В ,В,ВВ. , Формидов Врование кодов в регистре 4 можно описать системой уравнений:с В, вХс,В, (С 1,п.1 ), (11Для формирования кодов Ь,Еа,13 (г"- 2,в ) на регистр 4 сдвига с обратными связями записывается начальный код, как и в случае, когда1, и под управлением генератора 36 одиночных импульсов и группы 35 переключателей на г-й регистр сдвига блока 34 записывается вектОр кодовЬ, 1 Ь3 у, 6 р,с, г 2, " э Аналитически формирование коэффициентов описывается уравнениями (3) и (4)Ь =ссс1234Таким образом, в результатепростейших операций, выполняемых вблоках 18, 36, 35, 34, 4, 29 и 30,на регистрах сдвига блока регистровсдвига Формируются значения кодовВс (2) - (4), подаваемых, на входыматрицы 26 (щх ш) элементов И.После выполнения подготовительныхопераций переключатель генератора 1тактовых импульсов переключаетсяв положение, обеспечивающее генерирование тактовых импульсов, так какпри этом на вход блока 1 поступаетединичный сигнал с выхода (щ)-входового элемента ИЛИ 24.На Р-триггерах первой и второйгрупп 31 и 32 предварительно былизаписаны значения д,(1) = А; с помощью блока 19 тумблеров.Перед включением генератора тактовых импульсов на выходе комбинационной части предлагаемого устройства, состоящей из блоков 25, 11,10, 26 и 2 (на выходах группы 2),устанавливаются значения единицы,или нуля в зависимости от содержимого Э -триггеров групп 31 и 32.Такии образом, на выходах группысумматоров 2 по модулю два формируются значения кодов К(2),таккак для случая, когда О;= Ф(где сь и В,. - содержимое -гоР-триггера групп 31 и 32), выходныезначения комбинационной части устройства (блоки 25, 11, 10, 26 и 2)определяются согласно следующейсистеме логических уравнений::1и - четно, в - нечетно ( = 1,Ю). ,Аналитические выражения (5) и (6) описывают функционирование комбинационных схем 25, 11, 10, 26 и 2.Численное значение У,(2) определяется на основании д;(1) с использованием коэффициентов Вспредварительно записанных на регистры сдвига блока 34.По приходу первого импульса с выхода генератора 1 в первую ячейку блока 5 памяти записываются коэффициенты д;.(2) (= 1,о) а иэ первой ячейки памяти во вторую переписываются моды д", = д; (Фиг. 1 и 3).КоэфФициенты д";(2) поступают на вход блока 5 памяти с выходов группы 2. Под действием первого импульса, поступающего с выхода генератора 1, информация в регистрах 12 и 13 сдвига сдвигается на один разряд (фиг.4). Первый импульс не проходит через элемент И 6, так как на его второй вход поступает запрещающий сигнал с выхода элемента НЕ 38. Это объясняется тем, что на выхо. де элемента 23 в течение первых (1-)-х тактов будет единичный сигнал И, наконец, первый импульс с выхода генератора 1, поступающий на С-входы (через элементы 8 и 21) 2-триггеров групп 31 и 32 (фиг.2), запишет на Р -триггеры групп 31 и 32 значения кодов д,.(2), поступающих с выходов группы 2 непосредственно на 3 -входы Д -триггеров группы 31 и через группу элементов И 27 и элементов ИЛИ 33 поддействием разрешающего потенциала с выхода элемента 22 на Р-входы переходных процессов на выходахкомбинационной части устройствасформируются значения д"; (4)(аналогично сР;(2) в предшествующем такте),По приходу второго импульса свыхода генератора 1 в первую ячейку. блока 5 памяти запишутся кодыУ;(4) (. 1,т), а коды д,. (2) ид"(1) перепишутся соответственнов третью и вторую ячейки блока 51145469У(4) = (2) = 1, (4) = д (2)фс (2) =- 1; д (4) = У 2) = 1 Коды с(4) (= 1,4) определяюттс 1 пологию соединения сумматора по модулю два, на выходе которого получается задержанная на четыре такта копия исходной .М -последовательности, Под действием второго импульса, поступающего с выхода генератора, в регистрах 12 и 13 сдвига информация 10 сдвигается еде на один разряд Второй импульс, поступающий с выхода блока 1 на С-входы Э -триггеров групп 31 и 32, запишет в них код д" (4) . 15По истечении 6 тактов, где ь определяется разложением величины 6 в двоичную систему счисления (1), на выходе элемента ИЛИ 22, появляется запрещающий потенциал, котощый 2 О .блокирует прохождение тактовых импульсов с выхода генератора 1 через элементы 8 и 21 на входы триггеров групп 3 1 и 32. При этом на выходах сумматоров группы 2 будут сформиро ваны коэффициенты о;(2"). В последующие (в- о) такта состояния3-триггеров групп 31 и 31 меняться не будут.По истечении (в) тактов в блоке 5 памяти коды, определяющие топологию связей многовходового сумматора по модулю два, будут расположены следующим образом. В последней (в)-й ячейке будут находиться ко- З 5 ды о(1) = Ы.; в предпоследней - (ю)-й - Р;(2), в 6 п)-й - с(4), в (в-И)-й - сР(2"), в первой, второй и последующих ячейках до (в- и)-й будут храниться коды с/";(2 ),фПо истечении (в"3)-х тактов содержимое регистров 13 сдвига обнулится, на выходе элемента ИЛИ 23 появится нулевой,а на выходе элемента НЕ 38 единичный уровень, который разрешит прохождение импульсов с выхода генератора 1 через элемент И 6 на вход регисТра 14 сдвига. Разрешающий потенциал также поступает на вход двухвходового элемента И 9.Последующие импульсы, поступающие с выхода генератора 1 через элемент И 6 на вход (пт) -разрядного регистра 14 сдвига, будут55 последовательно сдвигать информацию на один разряд таким, образом, что содержимым последнего разряда ре Iгстра 14 сдвига будут символыИ 6 О, 1, являющиеся разложениемчисла с в двоичную систему счисленияВ момент поступления первого импульса на вход регистра 14 сдвигас выхода элемента И 6 этот импульспроходит или не проходит через элемент И 7 в зависимости от значениявеличины Ы Если Ы = 1, импульспроходит, если д= О, импульс непроходит. В случае, если д = О,содержимое 2 -триггеров групп 31и 32 не изменяется, а содержимоепоследней ячейки блока памяти 5изменяется на значения кодов с" (2).В случае, когда д,= 1, через элемент И 7 проходит импульс, которыйпоступает на вход элемента ИЛИ 21и далее на С-входы З,-триггеровгрупп 31 и 32. В момент поступления управляющего импульса на этиС-входы, на 2 -входы триггеровгруппы 31 поступают значения кодов с(2"), а на 2 -входы 2 в триггеров группы 32 значенйя кодов;(1), которые поступают с выходаблока 5, через группы 28 и 33. Этообъясняется тем, что с выходапоследнего разряда регистра 14сдвига поступает разрешающий поЬтенциал (Ы =1) на входы группы 28.Таким образом, по поступлениипервого импульса на вход регистра14 содержимое 3 -триггеров групп31 и 32 в случае, когда с, =1,изменится. На Э -триггерах блока 31будут храниться коды ок(2"), ана 3 -триггерах блока 32 - кодысР.(1). Кроме того, содержимоепоследнего разряда регистра 14 станет равным д 1.После окончания переходных процессов на выходах сумматоров по модулю два сформируются значениякодов Ы:,(р+1 2."+12. = "(2"Ф 1) дляслучая, когда Ы=1, так как, когда юФ 6 выходные значения комби)национной части устройства (блоки25, 11, 1 О, 26, 2, 19, 7, 6, 20и 5) будут определяться согласно следующейсистеме логических уравнений:П с + Я =ХФ с" ; (я Ж Ж Ь , Х1-1р 1+1в"Ф ( ) где ЧЯ.5469 6 15 11Числовые значения кодов с,(2 +1)определяются на основании сР;(2")и д;(1) с использованием кодовВ г предварительно записанных на1регистры блока 34,Под действием второго импульса,поступающего на вход регистра 14,в последнем разряде регистра 14сдвига изменяется информация.Вместо значения о 2 хранится значение д . Кроме того, в случаекогда Ы 2= 1, на выходах сумматоров группы 2 формируются значениякода ,д";(2"+1+Р), в случае, когдаЫ 2 ь О, на этих выходах формируются значения У (2"+1).По истечении определенного количества тактовых импульсов, когдасимвол с/,1+ = 1 будет находитьсяв предпоследнем разряде регистра 14,на выходах сумматоров группы 2 будутсформированы значения кодов Одновременно с моментом получения значений И;(Г) на выходе элемента 24 появится нулевой уровень,который отключит генератор 1 тактовых импульсов и, кроме того, погасит элемент 37 индикации. Гашение 1 О элемента 37 индикации означает,чтотребуемые коды получены, приемчисловое их значение определяетсяв блоке 3, ю индикаторов которогоопределяют значения кодов .У;(Ф).15 Если о; (1) = 1 для конкретногото 1 -й индикатор блока 3 светитсяи, наоборот, в случае, если д; И)=0,1-й индикатор блока 3 не светится.Таким образом, быстродействие 2 О предлагаемого устройства по сравнению с известным повышается практически в 2/ К раз.

СмотретьЗаявка

3561797, 09.03.1983

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЯРМОЛИК ВЯЧЕСЛАВ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: кодов, формирователь

Опубликовано: 15.03.1985

Код ссылки

<a href="https://patents.su/13-1145469-formirovatel-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь кодов</a>

Предыдущий патент: Устройство фиксации временного положения случайного сигнала

Следующий патент: Дискретная линия задержки

Случайный патент: Устройство для моделирования аэроупругих авиационных конструкций