Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

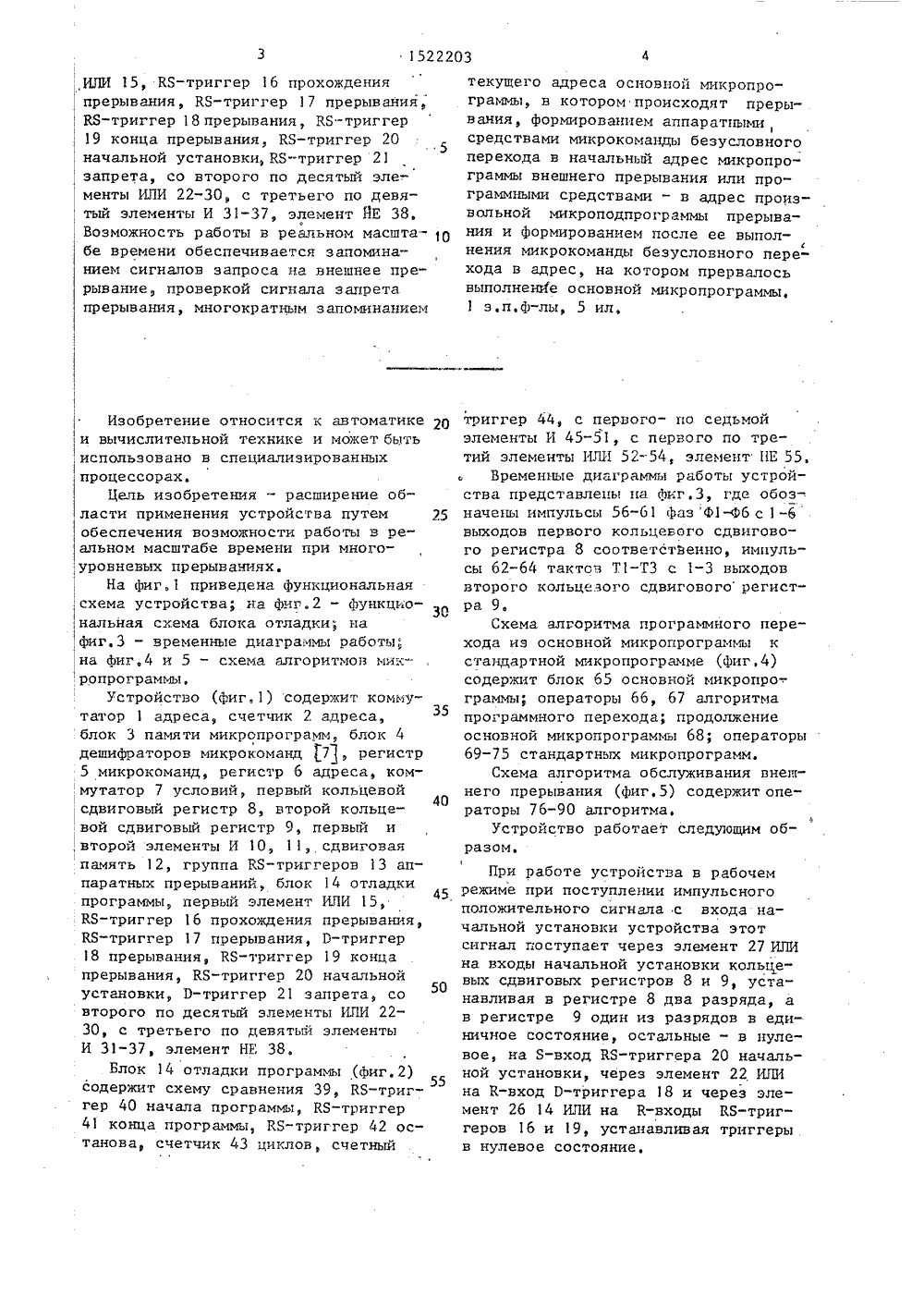

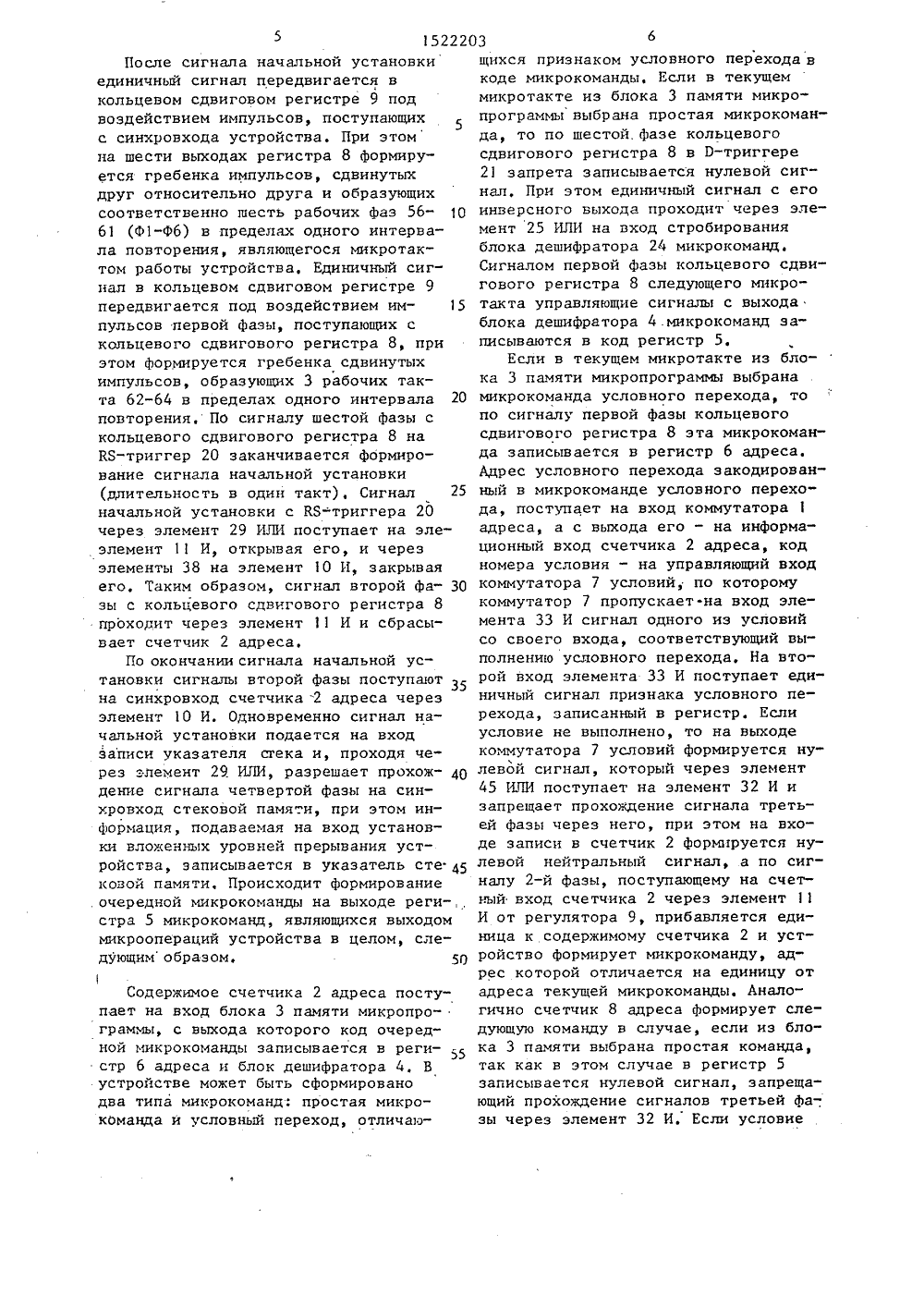

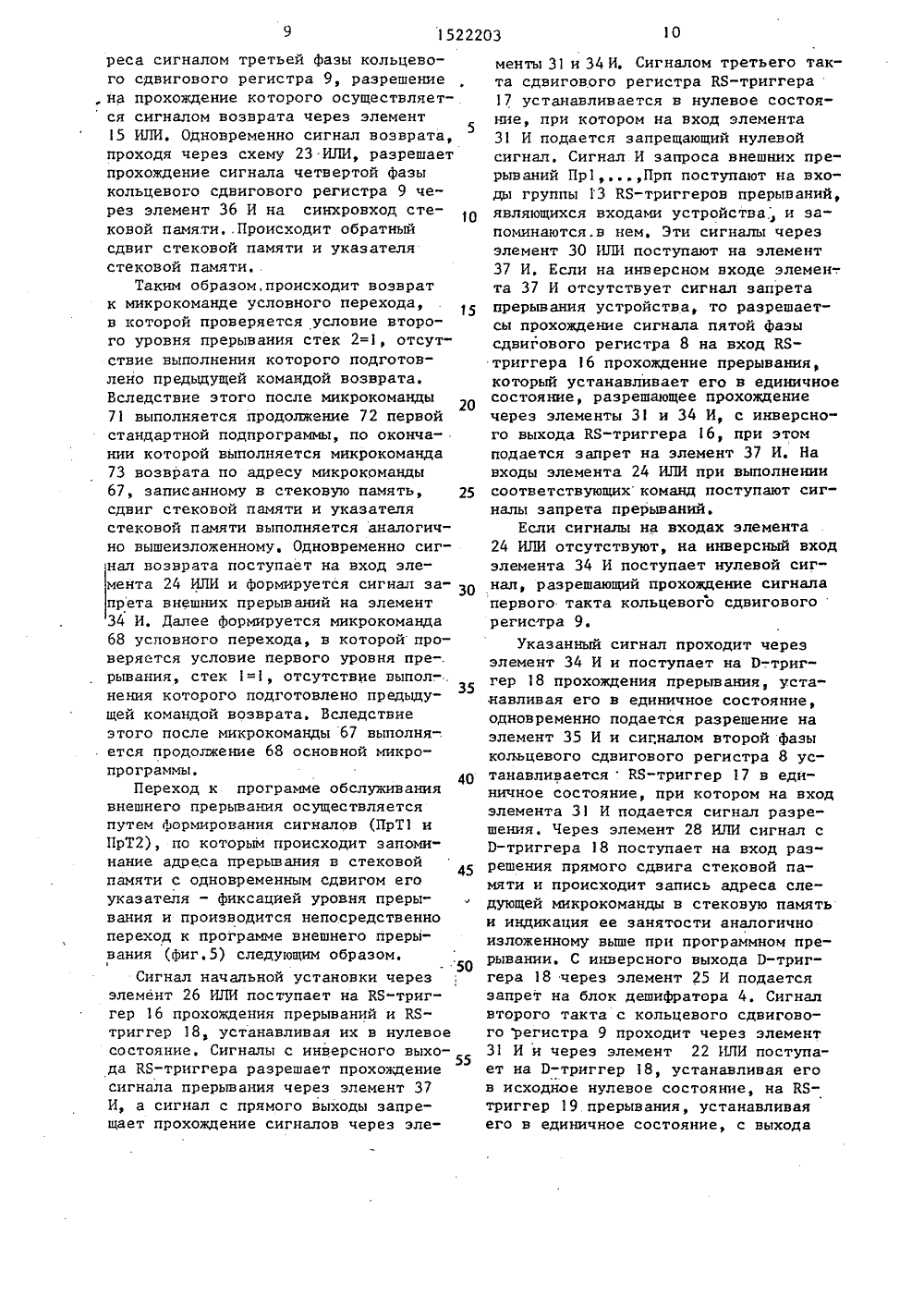

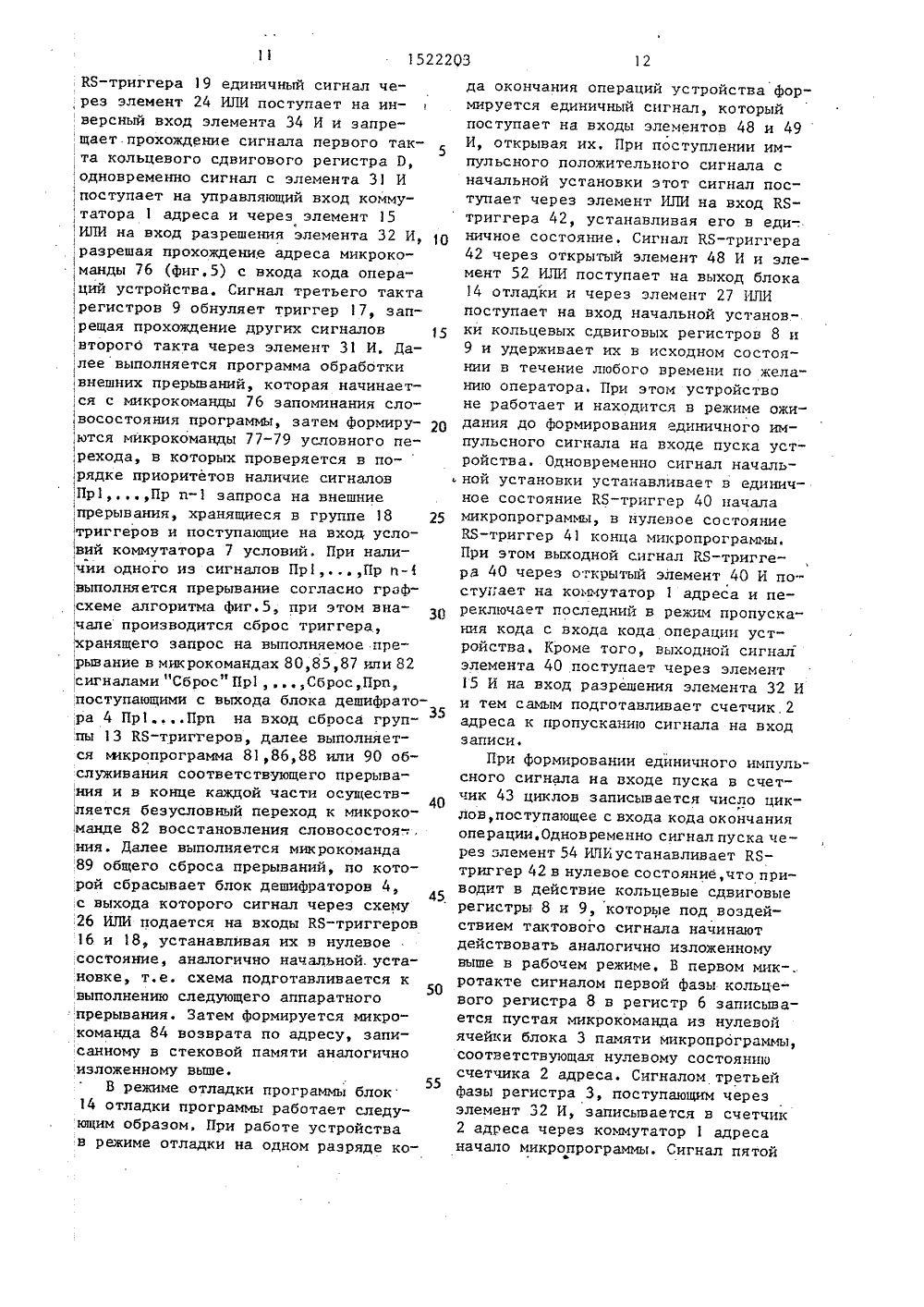

(50 4 ОАНИЕ ИЗОБРЕТЕНИЯ П.Храмцов во СССР 1982. СССР 1983. ЙСТВО УП ельст 9/22, ство 11/28 УСТРО относится к автомаьной технике, Цельширение области приокт ОСУДАРСТВЕННЫЙ НОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретениетике и вычислителизобретения - рас 2менения устройства путем обеспечения возможности работы в реальном масштабе времени при многоуровневых прерываниях. Устройство содержит коммутатор 1 адреса, счетчик 2 адреса, блок 3 памяти микропрограмм, блок 4 дешифраторов микрокоманд, регистр 6 адреса, коммутатор 7 условий, первый кольцевой сдвиговый регистр 8второй кольцевой сдвиговый регистр 9, первый 10 и второй 11 элементы И, стековую память 12, группу 13 КЯ- триггеров аппаратных прерываний, бл 14 отладки программы, первый элеменсчетчик циклов, счетный триггер, КБ- триггер начала и КБ-триггер конца программы, КБ-триггер останова, спервого по седьмой элементы И, с первого по третий элементы ИЛИ, элемент , НЕ, причем первый и второй входы схемы сравнения подключены соответственно к младшим разрядам входа . кон-. ца программы и входу текущего адреса0 программы, блока отладки программы, ,выход схемы сравнения подключен к первому входу первого элемента И, второйвход которого подключен к первому син;хровходу. блока отладки программы, а выход первого элемента И подключен кБ-входу КБ-триггера конца программы, К-вход которого соединен с Б-входомКБ-триггера начала программы, с пер-дым входом второго элемента И, вхо. - .дом элемента НЕ и выходом признака рабочего режима блока отладки про-граммы и подключен к выходу первого , элемента ИЛИ, а прямой выход КБ-триггера конца программы соединен с выхо дом признака конца программы блока отладки программы и подключен к первому входу третьего элемента И, второй вход которого соединен с К-входом КБ-триггера. начала программы и подключен к второму синхровходу блока отладки. программы, а выход третьего элемента И подключен к первому входу второго элемента ИЛИ второй вход которого соединен с вторым входом первого элемента ИЛИ и подключен к входу З начальной установки блока отладки программ., а выход второго элемента ИПИ подключен к Б-входу КБ-триггера останова прямой выход которого подФ40 ключен к первому входу четвертого элемента И, второй вход которого соединен с первым входом пятого элементаИ и подключен к первому старшему разряду входа конца программы блока отладки программ,. а выход четвертогоэлемента И подключен к первому входупервого элемента ИДИ, К-вход КБ-триггера останова подключен к выходутретьего элемента ИЛИ, первый входкоторого соединен с входом записисчетчика циклов и подключен к входупуска блока отладки программ, а второй вход элемента ИЛИ подключен к выходу элемента И, первый вход которого подключен к второму старшему разряду входа конца программы блока отладки программ, второй вход элементаИ соединен с входом "-1" счетчикациклов и подключен к прямому выходусчетного. триггера, а третий входшестого элемента И подключен к выходу седьмого элемента И, первый входкоторого подключен к третьему старшему разряду входа конца программы блока отладки программ, а второй входседьмого элемента И подключен к выходу счетчика циклов, вход сброса исчетный вход счетного триггера подключены соответственно к выходам элемента НЕ блока и второго элемента И,второй вход которого подключен ктретьему синхровходу блока отладкипрограмм, прямой выход КБ-триггераначала программы подключен к второмувходу пятого элемента И, а выход пятого элемента И соединен с выходомпризнака начала программы блока отладки программ, с четвертого по последний старшие разряды входа концапрограммы соединены с информа -ционными входами счетчика циклов.комитета по изобрете Москва, Ж, Раушск Подписноеям и открытиям при ГКНТ СССРнаб., д, 4/51522203 ИЛИ 15, КЯ-триггер 16 прохождения прерывания, КБ-триггер 17 прерывания, КЯ-триггер 18 прерывания, КБ-триггер 19 конца прерывания, КБ-триггер 20 начальной установки, КБ-триггер 21 запрета, со второго по десятый элементы ИЛИ 22-30, с третьего по девя тый элементы И 31-37, элемент НЕ 38.еВозможность работы в реальном масшта бе времени обеспечивается запоминанием сигналов запроса на внешнее прерывание, проверкой сигнала запрета прерывания, многократным запоминанием Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано в специализированныхпроцессорах,Цель изобретения - расширение области применения устройства путемобеспечения возможности работы в реальном масштабе времени при многоуровневых прерываниях.На Фиг.1 приведена Функциональнаясхема устройства; на Фиг.2 - Функциональная схема блока отладки; наФиг.З - временные диаграммы работы 1на Фиг.4 и 5 - схема алгоритмов микропрограммы,Устройство (Фиг,1) содержит коммутатор 1 адреса, счетчик 2 адреса,блок 3 памяти микропрограмм, блок 4дешифраторов микрокоманд 7, регистр5 микрокоманд, регистр б адреса, коммутатор 7 условий, первый кольцевойсдвиговый регистр 8, второй кольце,вой сдвиговый регистр 9, первый и,второй элементы И 10, 11, сдвиговаяпамять 12, группа КЯ-триггеров 13 аппаратных прерываний, блок 14 отладкипрограммы, первый элемент ИЛИ 15,КБ-триггер 1 б прохождения прерывания,КБ-триггер 17 прерывания, Р-триггер18 прерывания, КБ-триггер 19 концапрерывания, КБ-триггер 20 начальнойустановки, Э-триггер 21 запрета, совторого по десятый элементы ИЛИ 2230, с третьего по девятый элементыИ 31-37, элемент НЕ 38.Блок 14 отладки программы (Фиг.2)содержит схему сравнения 39, КБ-триггер 40 начала программы, КЯ-триггер41 конца программы, КБ-триггер 42 останова, счетчик 43 циклов счетный 2 г ЗО 35 40 45 50 55 текущего адреса основной микропрограммы, в котором происходят прерывания, формированием аппаратными1средствами микрокоманды безусловногоперехода в начальный адрес микропрограммы внешнего прерывания или программными средствами - в адрес произвольной микроподпрограммы прерывания и Формированием после ее выполснения микрокоманды безусловного перехода в адрес, на котором прервалосьвыполнение основной микропрограммы,1 з.п.ф-лы, 5 ил,триггер 44, с первого- по седьмойэлементы И 45-51, с первого по третий элементы ИЛИ 52-54, элемент НЕ 55,Временные диаграммы работы устройства представлены на Фиг.З, где обозначены импульсы 56-61 Фаз Ф 1-Фб с 1 -бвыходов первого кольцевого сдвигового регистра 8 соответственно, импульсы 62-64 тактсв Т 1-ТЗ с 1-3 выходоввторого кольцевого сдвигового регист"ра 9.Схема алгоритма программного перехода из основной микропрограммы кстандартной ьикропрограмме (Фиг,4)содержит блок 65 основной микропрограммы; операторы бб, 67 алгоритмапрограммного перехода; продолжениеосновной микропрограммы 68; операторы69-75 стандартных микропрограмм.Схема алгоритма обслуживания внешнего прерывания (Фиг, 5) содержит операторы 76-90 алгоритма,Устройство работает следующим образом.При работе устройства в рабочемрежиме при поступлении импульсногоположительного сигнала с входа начальной установки устройства этотсигнал поступает через элемент 2 ИЛИна входы начальной установки кольце"вых сдвиговых регистров 8 и 9, уста"навливая в регистре 8 два разряда, ав регистре 9 один из разрядов в единичное состояние, остальные - в нулевое, на Я-вход КЯ-триггера 20 начальной установки, через элемент 22 ИЛИна К-вход Р-триггера 18 и через эле"мент 26 14 ИЛИ на К-входы КБ-триггеров 16 и 19, устанавливая триггерыв нулевое состояние,03 5 15222После сигнала начальной установкиединичный сигнал передвигается вкольцевом сдвиговом регистре 9 подвоздействием импульсов, поступающихс синхровхода устройства. При этомна шести выходах регистра 8 Формируется гребенка импульсов, сдвинутыхдруг относительно друга и образующихсоответственно шесть рабочих Фаз 56- 1061 (Ф 1-Ф 6) в пределах одного интервала повторения, являющегося микротактом работы устройства. Единичный сигнал в кольцевом сдвиговом регистре 9передвигается под воздействием импульсов первой Фазы, поступающих скольцевого сдвигового регистра 8, приэтом формируется гребенка сдвинутыхимпульсов, образующих 3 рабочих такта 62-64 в пределах одного интервала 20повторения, По сигналу шестой фазы скольцевого сдвигового регистра 8 наКБ-триггер 20 заканчивается фбрмирование сигнала начальной установки(длительность в один такт), Сигнал 25начальной установки с КЯ-триггера 20через элемент 29 ИЛИ поступает на элеэлемент 11 И, открывая его, и черезэлементы 38 на элемент 1 О И, закрываяего, Таким образом, сигнал второй Фазы с кольцевого сдвигового регистра 8проходит через элемент 11 И и сбрасывает счетчик 2 адреса.По окончании сигнала начальной установки сигналы второй фазы поступают 35на синхровход счетчика .2 адреса черезэлемент 10 И. Одновременно сигнал начальной установки подается на входзаписи указателя стека и, проходя через элемент 29 ИЛИ, разрешает прохождение сигнала четвертой фазы на синхровход стековой памяти, при этом инФормация, подаваемая на вход установки вложенных уровней прерывания устройства, записывается в указатель сте 45ковой памяти Происходит Формированиеочередной микрокоманды на выходе реги-стра 5 микрокоманд, являющихся выходоммикроопераций устройства в целом, следующим образом, 501 Содержимое счетчика 2 адреса поступает на вход блока 3 памяти микропрограммы, с выхода которого код очередной микрокоманды записывается в реги 55 стр 6 адреса и блок дешифратора 4, В устройстве может быть сформировано два типа микрокоманд: простая микро- команда и условный переход, отличающихся признаком условного перехода вкоде микрокоманды, Если в текущеммикротакте из блока 3 памяти микропрограммы выбрана простая микрокоманда, то по шестой. фазе кольцевогосдвигового регистра 8 в Р-триггере2 запрета записывается нулевой сигнал, При этом единичный сигнал с егоинверсного выхода проходит через элемент 25 ИЛИ на вход стробированияблока дешифратора 24 микрокоманд.Сигналом первой фазы кольцевого сдвигового регистра 8 следующего микро"такта управляющие сигналы с выходаблока дешифргтора 4.микрокоманд записываются в код регистр 5,Если в текущем микротакте из блока 3 памяти микропрограммы выбранамикрокоманда условного перехода, топо сигналу первой фазы кольцевогосдвигового регистра 8 эта микрокоманда записывается в регистр 6 адреса.Адрес условного перехода закодированный в микрокоманде условного перехода, поступает на вход коммутатора 1адреса, а с выхода его - на информационный вход счетчика 2 адреса, кодномера условия - на управляющий входкоммутатора 7 условий; по которомукоммутатор 7 пропускает-на вход элемента 33 И сигнал одного из условийсо своего входа, соответствующий выполнению условного перехода, На второй вход элемента 33 И поступает единичный сигнал признака условного перехода, записанный в регистр. Еслиусловие не выполнено, то на выходекоммутатора 7 условий Формируется нулевой сигнал, который через элемент45 ИЛИ поступает на элемент 32 И изапрещает прохождение сигнала третьей фазы через него, при этом на входе записи в счетчик 2 формируется нулевой нейтральный сигнал, а по сигналу 2-й фазы, поступающему на счетный вход счетчика 2 через элемент 11И от регулятора 9, прибавляется единица к содержимому счетчика 2 и устройство формирует микрокоманду, адрес которой отличается на единицу отадреса текущей микрокоманды. Аналогично счетчик 8 адреса Формирует следующую команду в случае, если из блока 3 памяти выбрана простая команда,так как в этом случае в регистр 5записывается нулевой сигнал, запрещающий прохождение сигналов третьей фазы через элемент 32 И. Если условиевыполнено то на выходе коммутатора 7 усноьий формируется единичный сигнал котооый разрешает прохождение сигнах 1 а третьей фазь через элементы 32 И на зхтд записи числа в счетчик 2 аде;,=, и производитя запись адреСа У; ИОВ 1 О 1 О тЗР=ХОДа, ПОСтУПаЮЩЕГО на информационный вход счетчика 2адреса из регистра 6, ,через коммута- .О :. :,Цреса чт Обеспечивает перед Оойс:.ва в адрес 1 ь 1 кропрограмК: ЗР 11 О 1 у:, ТЕКУЩЕЙ УГКРОКОМННДЕ,СьОт:;ГО ПЕРЕХОДа ПРИ ЭТОМ СОСТОЯвие на синхровходе счетчика безразтично%:1 та 11 да безусттовного перехода выи;,-.аналогичнО. КОманде услов, ;, т:; - ;к, та 1,"ТЕ КОДИООВання Б НЕЙ11 О):".: ,,;:. В ": аПРИОНО ВЬПОтНЕННОГО 2 ООгукг 1 ЭН-й .ОТВЕТСТВЮЩЕГО ВХОДакотут гоа / на едттничный потенциалисточ 1 н.т пи ения Оцноврет:енно приВЫ 11 ОЛтта.,И УСЛОВНОГО ПЕРЕХОДа В 01 ритч Г3 ат ета 111 тои фаз ои кольцевого :дв 11 гового регистра 9 записы" ваетс-. признак услогного переходаа нулевой сигнал с инверсного выходат 1-трт 1 Г" Ера 1 Етт-З -ЛЕ 1 ЕНТ 5 1 Щ 1поступает на б 11; детгиоргоров 4 мик- ороко;.анд и запрещает его работу,ПеОх-,.д из ОС 11 ов;:,Ой микропро Гр ат-,мы к стандартной 1 ик 1.оподпрогт .з.я;(фи -1 ттрОИЗВОт 1-"Ся Ст 1 ЕдуштуКт Образом, Постэ зьтт О 111 етт 1 О с.Овной 1 тикРОПР, Гтта,м 6 Гто Т т О 1,1 РС та;-11,Обходимо вьи 1 олнит,: переход к стан, -11 ар т 1 Ой . Гик попд;1 тО гр аЯ 1, 1 тот) 1, руе т"гся иОстен микгОрОГрамма 00 записиадттеса поерь 1 в анин в стековую пяуя 7 ь,чПО этой командс по сьтгнатгу первой фазы кольцевого сцвигового регттстра 9 с1 выхопа регистра сигнал записи в сте,ковую память поступает через элемент 38 ИПИ на входы разрешения прямогосЦвттга и т рез элемент 29 ИЛИ на Перьый вход элемента Зб И открывая его.По сттг 11 атту второй фазы кольцевого.,т 1счетчика 2 адреса а сигнап четвертой"фазы кольцевого сцвигового регистра8 птоход 1 1 ереэ элеме;.1 го И Нос 1 упает на синхровход стековой памяти.На 11 ЯфООта 11 ИОНЬЬЕ тХОД 1 КОТОРСГО Г 1 Зцается сигнал со счетчика 2 адреса ипроисходи запись адреса следующей 1 о,;андь 1 б 7 в птрвутр 1 тейку с арековойи;.мятиП 1 дт пртмо. сдв:тге коттичество единичных разрядов в указателе стековой памяти увеличивается, а при Обратном сдвиге уменьшается.Сигнал с выхода признака занятости стековой памяти поступает черезэлемент 24 ИЛИ на инверсный вход элемента 34 И, запрещая прохождение прерывания по сигналам запроса на внешнее прерывание,Зтот же сигнал с первого выходауказателя стековой памяти поступаетна вход условия-стек 1 коммутатора 7,аналогично сигнал со второго выходауказателя стековой памяти поступаетна вход условия - стек 2 коммутатора7 условий и т,д, Эти условия в дальнейшем называются условиями прерывания соответствующего уровня. В следующем микротакте формируется кома 11 да67 условного перехода, в которой проверяется условие первого уровня прерывания стек 1 = 1 выполнение которого подготовпено предыдущей микрокомандой, и выполняется переход к стандартной подпрограмме б 9, При ее выполнении в случае необходимости производится обращение к другой стандартной подпрограт ме, при этом выполняется микрокоманд 70 записи в стековуюпамять:, по сигналу записи в стековуюпамять производится запись в адресамикрокоманды 71, одновременно произво;.,Нтся сдвиг указателя стековой памя"п 1, вследствие чего по второй разряд указателя стековой памяти записывается единичный сигнал, В следующем микротакте формируется микрокоманда 71 условного перехода, в котором проверяется условие второго уровня прерывания (стек 2=1), выполнение котороГо подготовлено предыдущей микрокомандой, и выполняется условный переход к стандартной подпрограмме. После выполнения стандартной подпрограммы 74 формируется микрокоманда 75 возврата по адресу микрокоманды 71, записанному в стендовую память. 12 пос" ледним и одновременный обратный сдвиг стековой памяти и указа.теля стековой памяти следующим образом. При формировании в блоке 3 памяти микрокоманды75 единичный сигнал возврата с выхода регистра 3 поступает на входы обратного сдвига стековой памяти 12 и на соответствующий вход коммутатора 1 адреса. Адрес, записанный последним в стековую память через коммутатор 1 адреса, записывается в счетчик 2 ад 1522203 Ореса сигналом третьей фазы кольцевого сдвигового регистра 9, разрешениена прохождение которого осуществляется сигналом возврата через элемент15 ИЛИ. Одновременно сигнал возврата,5проходя через схему 23.ИЛИ, разрешаетпрохождение сигнала четвертой фазыкольцевого сдвигового регистра 9 че"рез элемент 36 И на синхровход стековой памяти.,Происходит обратныйсдвиг стековой памяти и указателястековой памятиТаким образом. происходит возвратк микрокоманде условного переходарв которой проверяется условие второго уровня прерывания стек 2=1, отсутствие выполнения которого подготов"лено предыдущей командой возврата,Вследствие этого после микрокоманды71 выполняется продолжение 72 первойстандартной подпрограммы, по окончании которой выполняется микрокоманда73 возврата по адресу микрокоманды67, записанному в стековую память, 25сдвиг стековой памяти и указателястековой памяти выполняется аналогично вышеизложенному. Одновременно сигнал возврата поступает на вход элемента 24 ИЛИ и формируется сигнал за 3прета внешних прерываний на элемент34 И. Далее формируется микрокоманда68 условного перехода, в которой проверяется условие первого уровня пре-.рывания, стек 1=1, отсутствие выпол-.нения которого подготовлено предыдущей командой возврата. Вследствиеэтого после микрокоманды 67 выполня-.. ется продолжение 68 основной микропрограммы,Переход к программе обслуживаниявнешнего прерывания осуществляетсяпутем формирования сигналов (ПрТ иПрТ 2), по которым происходит запоминание адреса прерывания в стековойпамяти с одновременным сдвигом егоуказателя - фиксацией уровня прерывания и производится непосредственнопереход к программе внешнего прерывания (фиг.5) следующим образом.. 50Сигнал начальной установки черезэлемент 26 ИЛИ поступает на КЯ"триггер 16 прохождения прерываний и КЯтриггер 18, устанавливая их в нулевоесостояние. Сигналы с инверсного выхода КЯ-триггера разрешает прохождениесигнала прерывания через элемент 37И, а сигнал с прямого выходы запрещает прохождение сигналов через элементы 31 и 34 И, Сигналом третьего такта сдвигового регистра КЯ-триггера17 устанавливается в нулевое состояние, при котором на вход элемента31 И подается запрещающий нулевойсигнал. Сигнал И запроса внешних прерываний Пр 1 .,Прп поступают на входы группы 13 КЯ-триггеров прерываний,являющихся входами устройства и запоминаются,в нем, Эти сигналы черезэлемент 30 ИЛИ поступают на элемент37 И. Если на инверсном входе элемен-.та 37 И отсутствует сигнал запретапрерывания устройства, то разрешаетсы прохождение сигнала пятой фазысдвигового регистра 8 на вход КЯтриггера 16 прохождение прерывания,который устанавливает его в единичноесостояние, разрешающее прохождениечерез элементы 31 и 34 И, с инверсного выхода КЯ-триггера 6, при этомподается запрет на элемент 37 И. Навходы элемента 24 ИЛИ при выполнениисоответствующих команд поступают сигналы запрета прерываний,Если сигналы на входах элемента24 ИЛИ отсутствуют, на инверсный входэлемента 34 И поступает нулевой сигнал, разрешающий прохождение сигналапервого такта кольцевого сдвиговогорегистра 9,Указанный сигнал проходит черезэлемент 34 И и поступает на Р-.триггер 18 прохождения прерывания, уста.навливая его в единичное состояние,одновременно подается разрешение наэлемент 35 И и сигналом второй фазыкольцевого сдвигового регистра 8 устанавливаетсяКЯ-триггер 17 в единичное состояние, при котором на входэлемента 31 И подается сигнал разрешения. Через элемент 28 ИЛИ сигнал с0-триггера 18 поступает на вход раз"решения прямого сдвига стековой памяти и происходит запись адреса следующей микрокоманды в стековую памятьи индикация ее занятости аналогичноизложенному выше при программном прерывании. С инверсного выхода Р"триггера 18 через элемент 25 И подаетсязапрет на блок дешифратора 4. Сигналвторого такта с кольцевого сдвигового регистра 9 проходит через элемент31 И и через элемент 22 ИЛИ поступает на 0-триггер 18, устанавливая егов исходное нулевое состояние, на КЯтриггер 19 прерывания, устанавливаяего в единичное состояние, с выходаКЯ-триггера 19 единичный сигнал че,рез элемент 24 ИЛИ поступает на инверсный вход элемента 34 И и запрещает прохождение сигнала первого так 5 та кольцевого сдвигового регистра О, одновременно сигнал с элемента 31 И поступает на управляющий вход коммутатора 1 адреса и через элемент 15 ИЛИ на вход разрешения элемента 32 И, О разрешая прохождение адреса микрокоманды 76 (фиг,5) с входа кода операций устройства. Сигнал третьего такта регистров 9 обнуляет триггер 7, запрещая прохождение других сигналов второго такта через элемент 31 И. Далее выполняется программа обработки внешних прерываний, которая начинается с микрокоманды 76 запоминания словосостояния программы, затем формиру ются микрокоманды 77-79 условного пе" рехода, в которых проверяется в порядке приоритетов наличие сигналов Пр 1Пр пзапроса на внешние прерывания, хранящиеся в группе 18 25 триггеров и поступающие на вход условий коммутатора 7 условий. При наличии одного из сигналов Пр 1Пр и- выполняется прерывание согласно графсхеме алгоритма фиг.5, при этом вначале производится сброс триггера, хранящего запрос на выполняемое прерывание в микрокомандах 80,85,87 или 82 сигналами "Сброс" Пр 1, Сброс,Прппоступающими с выхода блока дешифратора 4 ПрПрп на вход сброса груп 35 пы 13 КЯ-триггеров, далее выполняется икропрограмма 81,86,88 или 90 обслуживания соответствующего прерывания и в конце каждой части осуществ;ляется безусловный переход к микрокоманде 82 восстановления словосостоя- ния. Далее выполняется микрокоманда 89 общего сброса прерываний, по которой сбрасывает блок дешифраторов 4, с выхода которого сигнал через схему 26 ИЛИ подается на входы КЯ-триггеров 16 и 18, устанавливая их в нулевое состояние, аналогично начальной. установке, т,е. схема подготавливается к выполнению следующего аппаратного прерывания, Затем формируется микро" команда 84 возврата по адресу, записанному в стековой памяти аналогично изложенному выше.55В режиме отладки программы блок14 отладки программы работает следующим образом. При работе устройствав режиме отладки на одном разряде кода окончания операций устройства формируется единичный сигнал, который поступает на входы элементов 48 и 49 И, открывая их, При поступлении импульсного положительного сигнала с начальной установки этот сигнал поступает через элемент ИЛИ на вход КЯ- триггера 42, устанавливая его в еди-.ничное состояние, Сигнал КЯ-триггера42 через открытый элемент 48 И и элемент 52 ИЛИ поступает на выход блока14 отладки и через элемент 27 ИЛИ поступает на вход начальной установки кольцевых сдвиговых регистров 8 и 9 и удерживает их в исходном состоянии в течение любого времени по желанию оператора, При этом устройствоне работает и находится в режиме ожидания до формирования единичного импульсного сигнала на входе пуска устройства. Одновременно сигнал началь.ной установки устанавливает в единичное состояние КЯ-триггер 40 началамикропрограммы, в нулевое состояниеКЯ-триггер 41 конца микропрограммы.При этом выходной сигнал КЯ-триггера 40 через открытый элемент 40 И по.ступает на коммутатор 1 адреса и переключает последний в режим пропускания кода с входа кода операции устройства. Кроме того, выходной сигналэлемента 40 поступает через элемент15 И на вход разрешения элемента 32и тем самым подготавливает счетчик.2 адреса к пропусканию сигнала на вход записи.При формировании единичного импульсного сигнала на входе пуска в счетчик 43 циклов записывается число циклов,поступающее с входа кода окончанияоперации, Одновременно сигнал пуска через элемент 54 ИПИустанавливает КЯтриггер 42 в нулевое состояние,что приводит в действие кольцевые сдвиговыерегистры 8 и 9, которые под воздействием тактового сигнала начинаютдействовать аналогично изложенному выше в рабочем режиме, В первом мик-.ротакте сигналом первой фазы кольцевого регистра 8 в регистр 6 записывается пустая микрокоманда из нулевойячейки блока 3 памяти микропрограммы,соответствующая нулевому состояниюсчетчика 2 адреса. Счгналом третьейфазы регистра 3, поступающим черезэлемент 32 И, записывается в счетчик2 адреса через коммутатор 1 адресаначало микропрограммы. Сигнал пятойФоРмула изобретения фазы кольцевого сдвигового регистра 8 сбрасывает КЯ-триггер 40 начала микропрограммы в нулевое состояние и переводит к коммутатору 1 адреса в рабочий режим, обеспечивая замыкание цепей для выполнения условных переходов устройством, аналогично изложенному, выше.Во втором и последующих микрокомандах устройство формирует микрокоманды аналогично рабочему режиму, изложенному выше, начиная с микрокоманды, установленной на входе кода операции устройства 1. При этом адрес исполняемой микрокоманды со счетчика 2 поступает на схему 39 сравнения, на второй вход которого поступает конечный адрес микрокоманды, установленный на входе кода окончания операции,Когда микропрограмма, формируемая устройством, достигает адреса, равного конечному адресу, на выходе схемы сравнения формируется единичный сигнал, поступающий на элемент 45 И, При 25 этом при прохождении последней микро- команды сигнал шестой фазы кольцевого сдвигового регистра 8 через элемен 1 45 И поступает на КЯ-триггер 41 конца микропрограммы и устанавливает его в единичное состояние, Выходной сигнал БЯ-триггера 41 открывает элемент 47 И и одновременно через элемент 49 ИЛИ бткрывает элемент 11 И. После выполнения конечной микрокоманды в следующем микротакте сигнал вто 35 рой фазы кольцевого сдвигового регистра проходит через элемент 11 Ии сбрасывает счетчик адреса, сигналпятой фазы проходит через элементы 4047 И и 53 ИЛИ и устанавливает КЯ-триггер 42 в единичное состояние,Единичный сигнал КЯ-триггера 42 проходит через элементы 48 И и 52 ИЛИи устанавливает ВЯ-триггер 41 конца . 45программы в нулевое состояние, приэтом заканчивается формирование сигнала конца программы и устройство устанавливается в исходное положение.Если на втором синхровходе блока14 не установлен единичныи сигнал,то чередование команд на выходе устРойства на этом заканчивается, послечего работа устройства может бытьповторена аналогично изложенному выше, однако с другими значениями начала и конца микропрограммы, установленными на соответствующих входах устройства. Если на втором синхровходе блока 14 установлен единичный сигнал, то после первого цикла исполнения микропрограммы от начального до конечного адреса, как изложено выше, сигнал с выхода элемента 52 ИЛИ открывает элемент 46 И, через который тактовый сигнал поступает на счетный вход триггера 44 и переводит его в единичное состояние. Выходной сигнал триггера 44 через элементы 50 И и 54 ИЛИ сбрасывает ЕЯ-триггер 42 в нулевое состояние. Затем работа устройства повторяется от начального адреса до конечного аналогично изложенному вьппе циклу работы. Нулевой сигнал с выхода элемента 52 ИЛИ через элемент НЕ 55 устанавливает счетный триггер 44 в нулевое состояние, Таким образом, на выходе триггера 44 формируется в кон-. це каждого цикла работы микропрограммный импульс, поступающий кроме элемента 50 И также на счетный вход счетчика 48 циклов, который работает в режиме обратного счета и после каждого цикла уменьшает свое содержимое на единицу.Повторение циклов формирования отлаживаемой части микропрограммы от начального адреса до конечного происходит до тех пор, пока содержимое счетчика 43 не достигнет нуля, В этом случае сигнал с его выхода поступает на элемент 51 И и при наличии единичного сигнала на другом входе элемента 51 И запрещает прохождение сигналов через элемент 50 И, вследствие чего новый цикл не начинается и работа устройства заканчивается, Далее работа устройства может быть повторе" на с другими значениями адресов микропрограммы и числа циклов, установленных на соответствующих входах устройства.Если на разряде признака ограничения циклов входа кода окончания операций устройства установлен нулевой сигнал, то сигнал с выхода счетчика 43 циклов никогда не пройдет через элемент 51 И, вследствие чего циклы повторения отлаживаемой части микропрограммы выполняются беспредельно. 1. Микропрограммное устройство управления, содержащее регистр адреса, коммутатор адреса, счетчик адреса,онных входов коммутатора условий, управляющий вход которого соединен с выходом кода условия регистра адреса, выход кодов адреса и условия блока памяти микрокоманд соединен с информационным входом регистра адреса., о т л и ч а ю щ е е с я тем, что, с целью расширения области применения путем обеспечения возможности работы в реальном масштабе времени при мно 35 гоуровневых прерываниях, в него вве. - . дены стековая память, второй кольце-. вой сдвиговый регистр, группа КБ- триггеров аппаратных прерываний, КБ- триггеры прохождения прерывания, КБ- триггер. прерывания, КБ"триггер конца прерывания, КБ-триггер начальной установки, Э-триггер прерывания, 0- триггер запрета, с пятого по десятый элементы ИЛИ, причем третий информа"ционный вход коммутатора адреса соединен с информационным выходом стековой памяти, первый управляющий вход коммутатора адреса соединен с пер= вым входом первого элемента ИЛИ и подключен к выходу признака начала программы блока отладки программы, второй управляющий вход коммутатора. адреса соединен с входом КБ-триггера55 конца прерывания, первым входом второго и вторым входом первого элемен" та ИЛИ и поДключен к выходу третьего элемента И, третий управляющий вход 5 О блок памяти микропрограмм, блок дешифраторов микрокоманд, регистр микрокоманд, коммутатор условий, первый кольцевой сдвиговый регистр, блок от-.5 ладки программы, с первого по девятый элементы И, с первого по четвертый элементы ИЛИ, элемент НЕ, причем вход кода операции устройства соединен с первым информационным входом коммута тора адреса, выход которого соединен с информационным входом счетчика адре са, информационный выход которого соединен с адресным входом блока памяти микропрограмм, выход кода микроопера ций которого соединен. с информационным входом блока дешифраторов микро- команд, первый выход которого. соединен с информационным входом регистра микрокоманд, выход кода микроопераций которого является выходом микроопераций устройства, выход кода адреса регистра адреса соединен с вторым инфор. мационным входом коммутатора адреса, входы логических условий устройства 25 соединены с первой группой информацикоммутатора адреса соединен с входомразрешения обратного сдвига стековойпамяти с первыми входами третьего ичетвертого элементов ИЛИ и третьимвходом первого элемента ИЛИ и подключен к выходу признака возврата реги-.,стра микрокоманд, счетный вход счетчика адреса подключен к выходу первого элемента И, вход установки в0 счетчика адреса соединен с выходом второго элемента И, вход управления режимом записи счетчика адресаподключен к выходу четвертого элемен". та И, а выход счетчика адреса соеди-, нен с входом текущего адреса блокаотладки программы с информационнымвходом стековой памяти, вход записирегистра адреса соединен с входамизаписи регистра микрокомапд второгокольцевого сдвигового регистра и спервым выходом первого кольцевогосдвигового регистра, выход признака типа команды блока памяти микрокоманд соединен с П-входом П-триггера запрета, синхровход которого соединен с первым синхровходом блока отладкипрограммы и с 0-входом .КБ-триггераначальной установки, а инверсный выход 0-триггера запрета подключен кпервому входу пятого элемента ИЛИ, второй вход которого подключен к инверсному выходу Р-триггера прерыванияпятого элемента ИЛИ., выход подключенк входу стробирования блока дешнфраторов микрокоманд, второй выход блокадешифраторов микрокоманд подключен к входам К КБ-триггеров групп аппаратных триггеров прерываний, третий выход блока дешнфраторов микрокомандподключен к первому входу шестого элемента ИЛИ, второй вход которого соединен с вторыми входами второго ипервым входом седьмого элементов ИЛИ, Б-входом ВЯ-триггера начальной установки, входом начальной установки блока отладки программы и подключенк входу начальной установки устройства, а выход шестого элемента ИЛИ подключен к К-входу КБ"триггеров прохождения прерывания и конца прерывания, выход признака условного перехода регистра микрокоманд соединен спервым входом пятого элемента И иподключен к второму входу четвертогоэлемента ИЛИ, третий вход которогоподключен к выходу признака занятости стековой памяти, четвертый входчетвертого элемента ИЛИ соединен свыходом признака запрета прерываний регистра микрокоманд, а пятый вход четвертого элемента ИЛИ соединен с прямым выходом КБ-триггера конца пре 5 рывания, выход четвертого элемента ИЛИ подключен к первому входу шестого элемента И, второй вход которого подключен к первому выходу второго кольцевого сдвигового регистра, а третий вход шестого элемента И соединен с входом третьего элемента И и подключен к прямому выходу КБ-триггера прохождения прерываний, 1 выход шестого элемента И соединен с первым входом седьмого элемента И и подключен к Р-входу Р-триггера прерывания, синхровход которого соединен с вторыми входами первого, второго и седьмо-. го элементов И и подключен к второму выходу первого кольцевого сдвигового регистра, а вход сброса Р-триггера прерывания подключен к выходу второго элемента ИЛИ, прямой выход П-триггера прерывания подключен к первому 25 входу восьмого элемента ИЛИ, второй вход которого подключен к выходу признака записи в стековую память.регистра микрокоманд, а выход восьмого эле-. мента ИЛИ соединен с входом разрешения прямого сдвига стековой памяти и подключен к второму входу третьего элемента ИЛИ, третий вход которого соединен с входом записи указателя . стековой памяти, первым входом девятого элемента ИЛИ и подключен к прямому выходу КБ-триггера начальной установки, выход третьего элемента ИЛИ соединен с первым входом восьмого элемента И, выход восьмого элемента И 4 О подключен к входу записи стековой памяти, третий выход первого кольцевого сдвигового регистра подключен к первому входу четвертого элемента И, второй вход которого подключен к вы ходу первого элемента ИЛИ, четвертый вход которого подключен к выходу пятого элемента И, второй вход которого подключен к выходу коммутатора условий, второй вход восьмого элемента И подключен к четвертому выходу первого кольцевого сдвигового регистра, вторая группа информационных входов коммутатора условий соединена с выхода-. ми указателя стековой памяти, вход указателя стековой памяти соединен с входом установки вложенных уровней прерывания устройства, третья группа информационных входов коммутатора условий соединена с прямыми выходами КБ-триггеров группы КБ-триггеров аппаратных прерываний, Б-входы которых являются входами внешних прерываний устройства, прямые выходы КБ- триггеров группы КБ-.триггеров аппаратных прерываний соединены входами десятого элемента ИЛИ, выход которого подключен к первому входу девятого элемента И, второй вход которого подключен к входу запрета прерываний устройства, третий вход девятого элемента И подключен к инверсному выхо; ду КБ-триггера прохождения прерывания, четвертый вход девятого элемента И подключен к пятому выходу первого кольцевого сдвигового регистра и соединен с вторым синхровходом блока ,отладки программы, а выход девятого элемента И соединен с Б-входом КБ- триггера прохождения прерывания, синхровход первого кольцевого сдвигового регистра подключен к синхровходу устройства и соединен с третьим синровходом блока отладки программы, вход начальной установки первого кольевого сдвигового регистра и второго кольцевого сдвигового регистра подключен к выходу седьмого элемента ИЛИ, второй вход которого подключен к выходу признака рабочего режима блока отладки программы, выход признака конца программы которого подключен к второму входу девятого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И и входом элемента НЕ, выход которого подключен,к второму входу первого элемента И, шестой выход первого кольцевого сдвигового регистра соединен с К-входом КБ-триггера начальной установки, вход конца программы блока отладки программы соединен с входом кода окончания операции устройства, вход пуска устройства соединен с входом пуска блока отладки программы, второй выход второго кольцевого сдвигового регистра подключен к второму входу третьего элемента И, а третий выход второго кольцевого сдвигового регистра подключен к К-входу КБ-триггера прерывания Б-вход которого подключен к выходу седьмого элемента И, прямой выход КБ-триггера прерывания соединен с третьим входом третьего элемента И.2. Устройство по п. 1, о т л и ч а - ю щ е е с я тем, что блок отладки программы содержит схему сравнения,

СмотретьЗаявка

4261393, 15.06.1987

ПРЕДПРИЯТИЕ ПЯ Г-4152

ИЦКОВИЧ ЮРИЙ СОЛОМОНОВИЧ, ХРАМЦОВА ЛЮБОВЬ ПЕТРОВНА

МПК / Метки

МПК: G06F 11/28, G06F 9/22

Метки: микропрограммное

Опубликовано: 15.11.1989

Код ссылки

<a href="https://patents.su/12-1522203-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для умножения частоты на код

Следующий патент: Устройство для организации очереди к общему ресурсу

Случайный патент: Устройство временного компандирования для систем связи с многостанционным доступом