Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

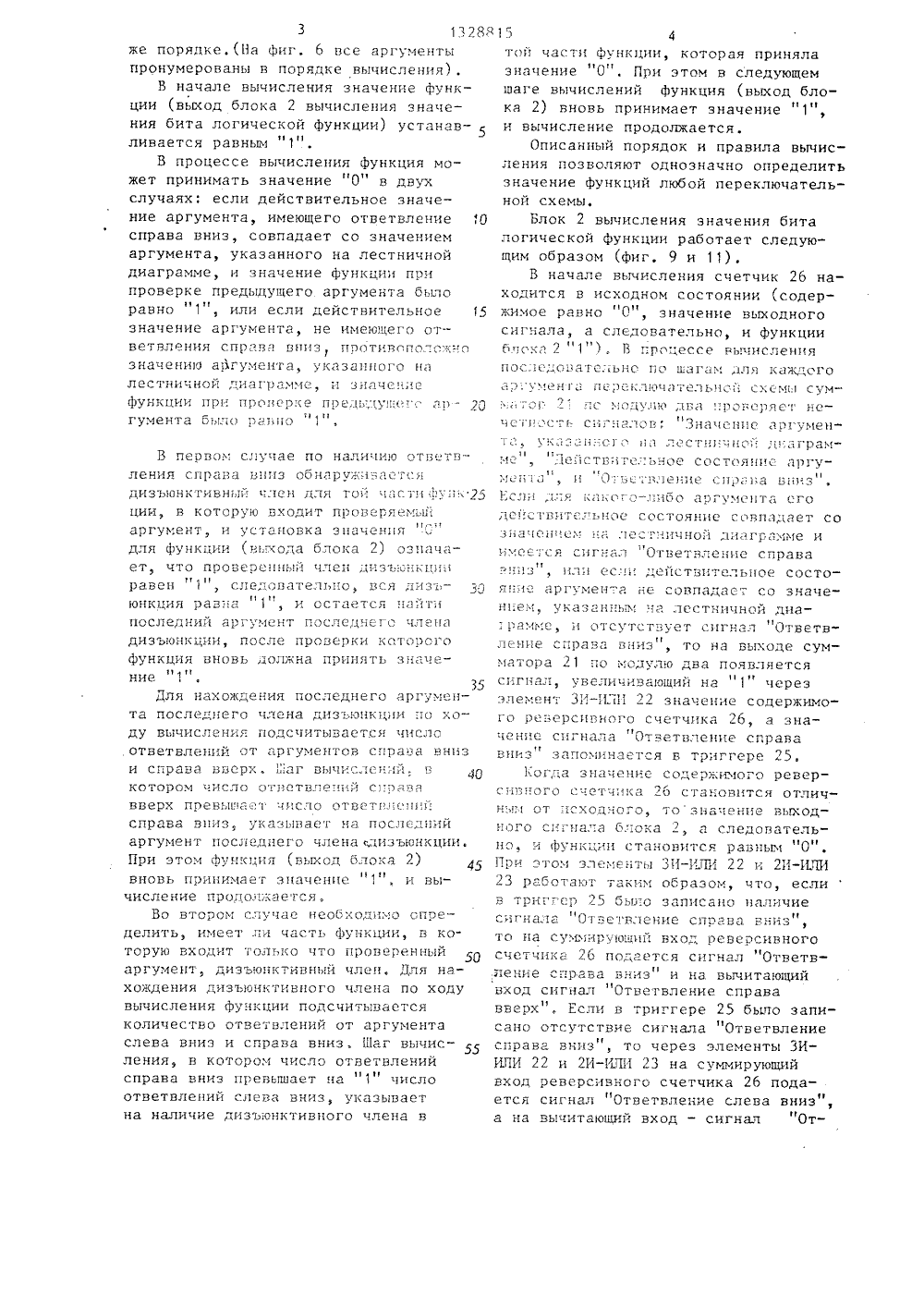

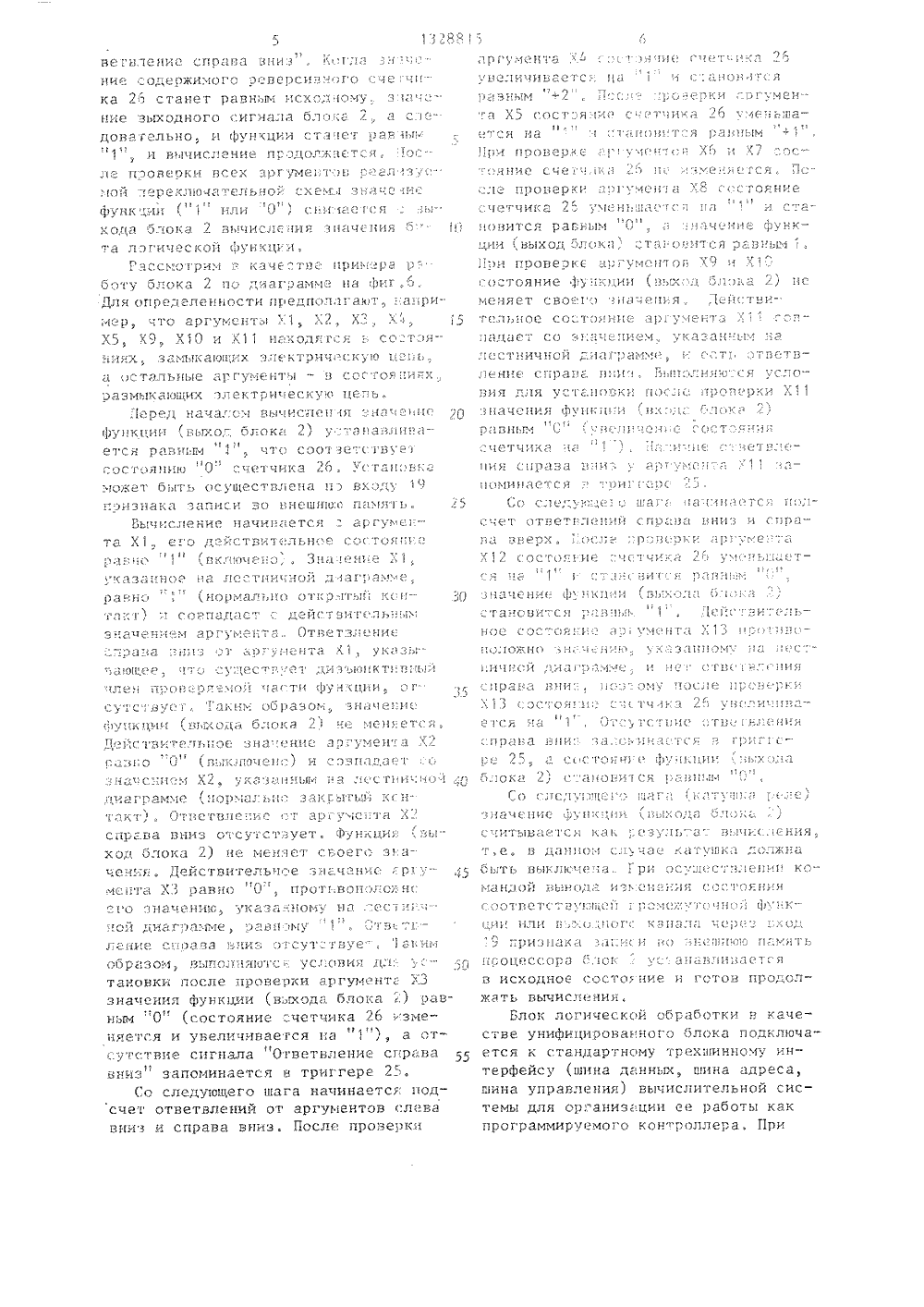

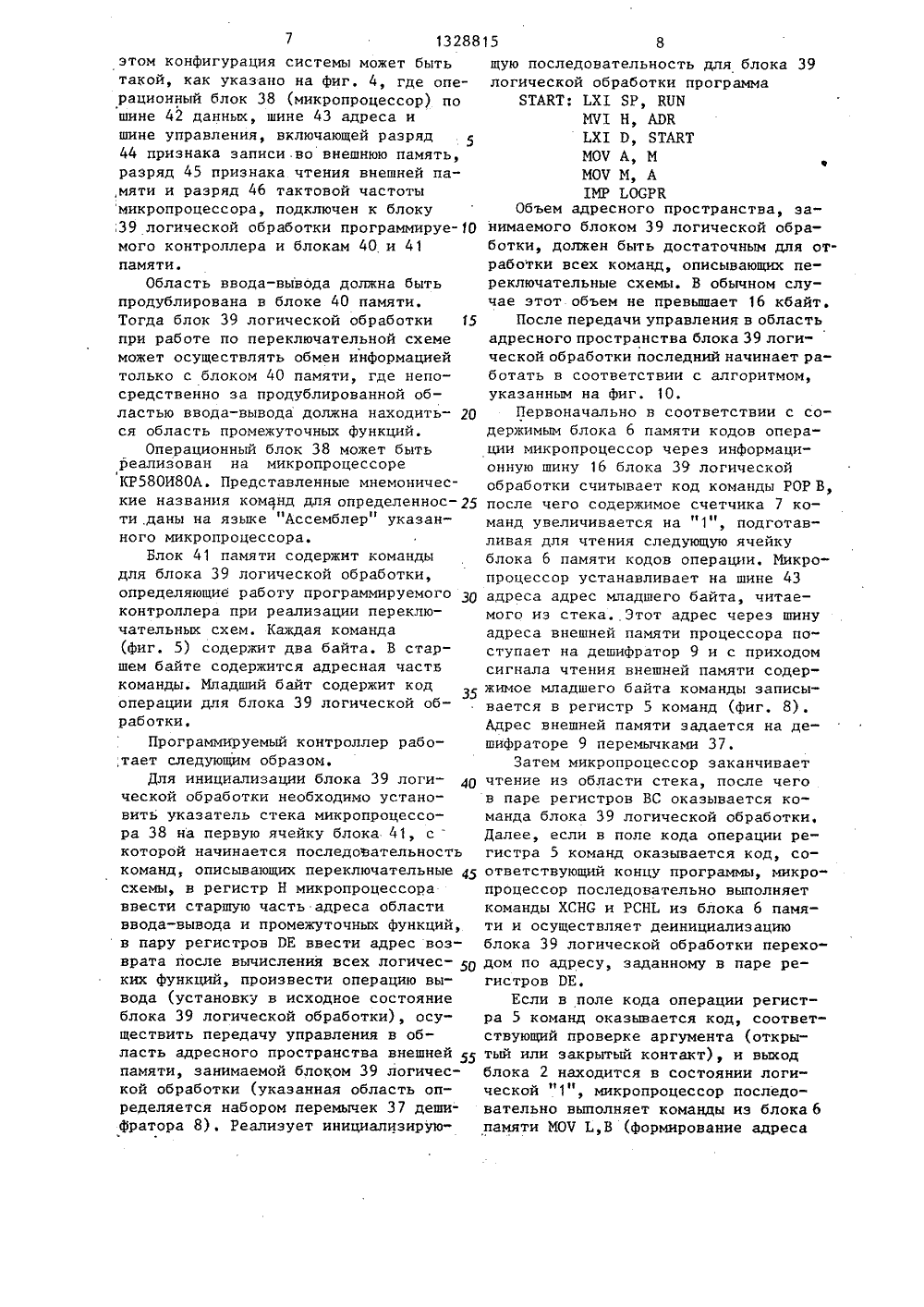

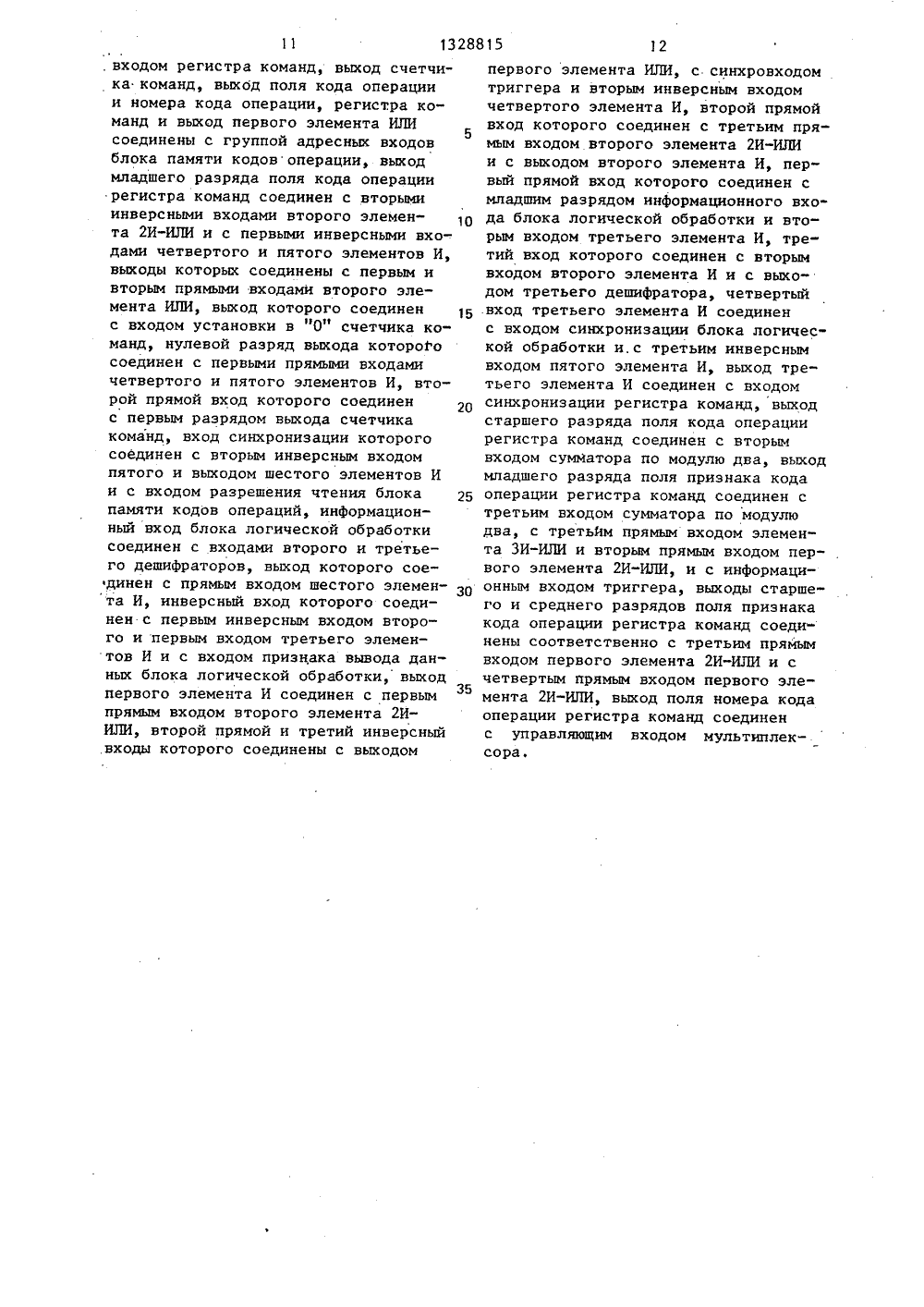

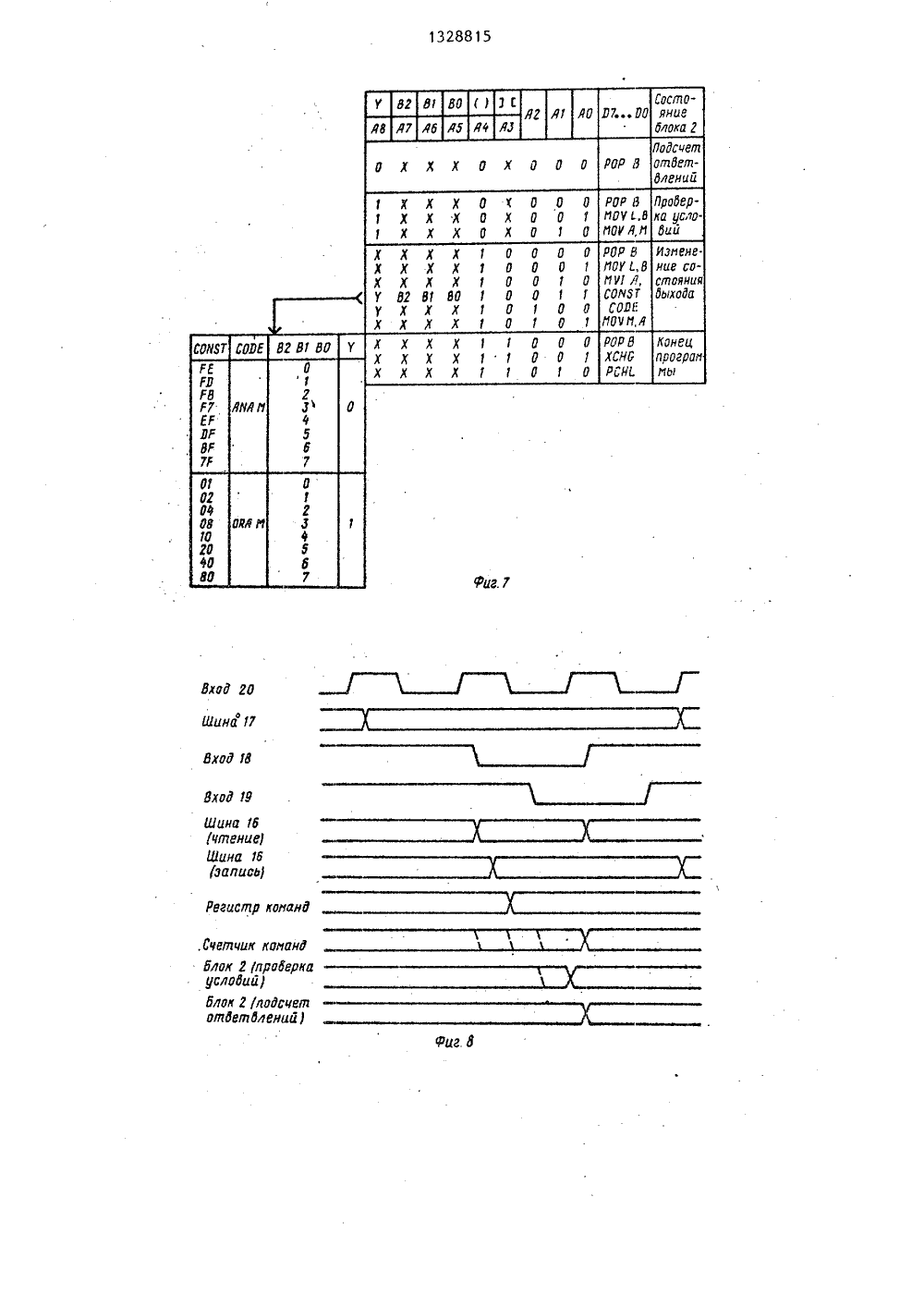

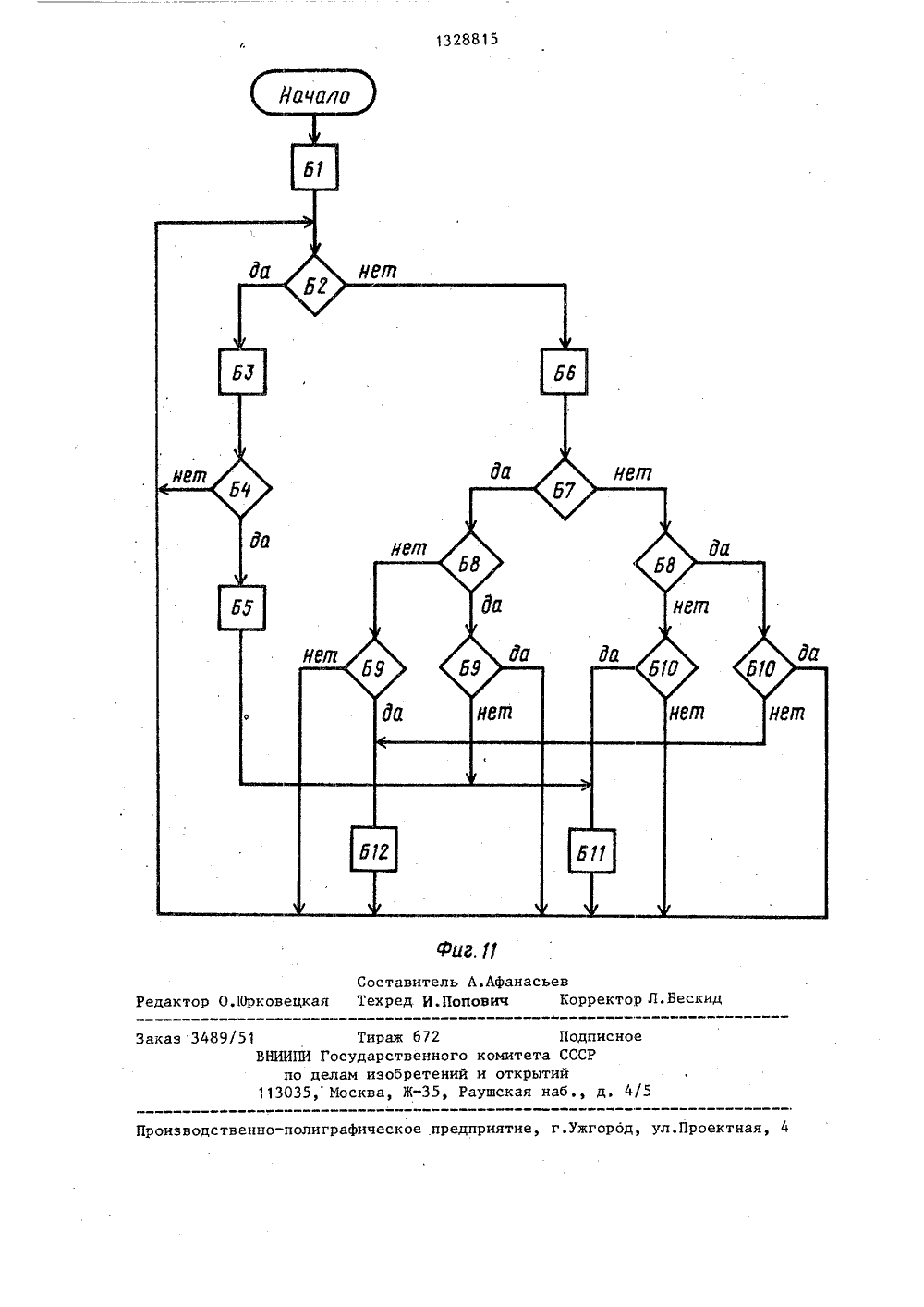

СО 1 ОЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 19) (11 00 ОПИСАНИЕ ИЗОБРЕТЕНИ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(57) Изобретение относится к областивычислительной техники и может бытьиспользовано в системах контроля,Цель изобретения - сокрап 1 ение объемаблока памяти программируемого контроллера. Программируемый контроллерсодержит операционный блок, блок логической обработки и блок памяти.Введение в блок логической обработкидвух дещифраторов, регистра команд,счетчика команд, блока памяти кодовопераций, пяти элементов И, элементаИЛИ и элемента 2 И-ИЛИ приводит к достижению пели, 11 ил.1328815 У Вг ВУ ВО 1 ) 1 Сяг я яа ЯВ Я 7 ЯЮ ЯХ ЯФ Я 5 7 0 Х Х Х 0 Х К О 0 О РОР В Х а Олоус х ио лоуя 1 Х Х Х 1 Х Х Х 1 Х Х Х а о о о 1 О О Оо оо 1 О 0 1 У0 1 О а 1 О 1 Оарв сна Сн). к х х Х Х Х х х х СОЕ О)У а а1 1 а 1 о РЕ Ш Гв мял О Ри Вход га Шина 7 Вход ход У стр коианд Счетчик кокандбяок г 1 пробернаусяобий)блок г йодсчетощбещбяений)Фиг. б Шина УВ чтение) Шина В запись) Х Х Х Х Х Х Х Х Х Х Х Х у вг в 1 во У Х Х Х Х Х Х Х ОРВ ЛОУ ЛУУ Я СОУчз СОВУ ОУл1328815 Инрвриацисиный оход Входы кода операции и признака кода операции Выход дюка Я 1 Вытд прийгера О Восход эюеюееоа Г Вьасб змненаа О Выонг зелена1328815 А,Афанапович Составите Техред И,ор 0,10 рковецка е д, 4/ роизводственно-полиграфическое предприятие, г.ужгород, ул.Проектная,каз 3489/51 Тираж 67 ВНИИПИ Государствен по делам изобрет 113035, Москва, ЖвКорректор Л Бески Подписноеого комитета СССРний и открытийРаушская наб.,.ель изабр(-тенин - сос,р,:.1 ени: )б ема блокапамяти пзогряммс 1)уемога КаптРОЛЛЕРЯ 1 трЕт;С гав.т(ЕНя ГЗСЕ:.,": О.:О, Обр)ООТСИНа фтг - :уятО.ТОК,т 3 ЫЧ С 7 ЕцЯ ЭЯг ло ическай функ(ии иа ровНа нг Л )ГитЕС.1(от" и "а пазЬПЯЯч И. т Ии: стандартных яунсцианяль ь:.х элеент ЭВта фиф /КтО .7 Ьп Я Я С ЕМЯ д щифраторо ня уровне ста .пар сныс с)ункционя.пьпых эле."1(.н.в;:,а фиг, с грук "ура зрограьрируз.101-0 канз ро;1- 5 л "ра; па фиГ, э - ООрмат сс:манд б 10.0,.10 т(ОИ ОЭОЯС 01,И т 1 т. ф 5)С ."( энс ре; ня я песеключяте 1 ьн(15" схсмаС 1 З П.СТНИЧПОй ДиаГРЯттзЬ );, -На ф; Г, . Табп 11 т 1 я Про Г" Ртран Н я б:ока памяти тсадов операци: ,1 - .:Огя-. Ч ".эя - ПО.ЧдтсСИЙ О" . Х т Ремс н ЯЯ ДиагРамма Работы алака ори :;,с;,ай (;бряб Оть ипа фиг - вре;ев пяя дтягряммя раооты блока вычисления э зачепия бита лсгическай 1)т нкцпи; ня г -. 1 " яГортм рас)аты с:лака л" .ЕССОЙ С)Ь ОЯЬОТ 1(;.1 " - СЧИ "ЯТЬ,1 ВП Яйта ;0 тан,ть;. А п,-)авс 1:)5 ь л.1 ОЛ ЯС 0 1"са ВьКада;г 3 " 1" равсриь ) ЕСТЬ Лт. КЭ,:ЕЦ ПРЭГРЯМСЬ- ПРОПЕ-. р 1 ть (.сст япие вьхсда блок;: на рапепт"ВО ЧУЮУ(: -" ЧИ" а ТЬ СО( ТОЯ ПИЕ Вадя нли п 1:оме;ут; т-.В К ЮтИГ Капапнял А "- 1 с.тя:-:овит.:ссояние19 " к(;.алэори 1 работзначения бита ло -".1 - устапсвит с, с05 тПЗьМ 1 .", )ПОРТЯ ;Вада -. Вьт;.;01 фУтКЦИИТс)(тнс С тЕ гЧ 5 Са.,п(,"овс рить саста 5 тние счетчика па р("т )тт, -1 потна : Б - устссновиз ь зЯчэ -н)е,сртпктщи разное1)1- - с 00,е-.т, тт,Рт ъ,Е)С 5 ГЗИТЕ 515 ПО ЛИ ЗНЯЧСП 1 ИЕ сРУ" теВИТЯ СОВПЯЦЯЕТ СС) ЗНтЕНСИУКЯ: Я". 1")В Па 71 т( ТНИЧНОЙ тиаРЯМ:тС., И Р" ,и отпе,пление справя внизт илс;зпацяе и нст Отсз твлз 51;,5 сравс тз, 55 - запомнить наличие или стУт" т СПв ( т;т ЦЯЛЯТВ(:, 1 ВЛЕ тИЕ ГРЯ ВЯ вниз г, триггере; Бб установить : пачс 1 П 1 Е (уцСЦИИров)ЫМ С т тэГ 1)ОВЕр(ТЬ,. ЗафИКСИраВЯНО ЛИ В трн;. - (тс . . - ,.е ответвсеняе справя в)-."из БЗ П)ОНЕРЯТЬ НЯткЧ 1 Е ОТВЗТВЛЕНИЯ СПРЯВЯ Впиэ; 9 - проверить наличке ответвления справа вверх Б 10 - В.раверкь 1В;-Птп.-1 т, (д. р,",С ). тг. птттСя2 -. уменьи:и ь .;,;,тое счетчика.Я 1 т.Блок лагичес: ои обраЬотки прсграмтРУЕМОГО КОНРС пп )РЯ ,СЗИГ. :, СЭДЕРит му.ьтипл "ксар 1 бт.ок 2 вьчисле -:,я ЗНЯЧЕНИЯ ОИТЯ,10 ГЧ(СКОЙ фувСции.- .ЗВВЬ ДЕШИтРЯТСО 3ЭЛСЗМЕН: И "Фрегистр э коман;(. блок с памяти кодовОПЕЗЯЦИИ, СЧЕТЧИ:( т КОМЯНД, ВТОЭОИ иТЭЕТИЙ 7,ЕИС 01) С)пЬ 8 И .,", ЭЛЕМЕ ТЫ т3 -. 14 и И 1 т )т ьНсрормацианныйз ход Вьход 1 э,тн(1(р(Я ционны зха ;,з ход 18 Риз Яака вывода данных т входПРИЗНЯСЯ 3тИС 1""1 СШПЮС т 1 ЯМЯТЬи вход 20 синхропизя.Нт,Блок 2 вьь 1 спе;и я зпате 5 ия биталэгической сзпк,ии Сфь 1, 2, содержитсумматор 21 .7(. мэд;лю ,ва элемент ) ) И-ЮЪ 1 2 с. н т) 11 с 2 : 1( 2-:, Три Гве 17 25, сче чнк 26 э.те енз ц1 2;,нформационныс входы 2 т - 30 пха;.1 3тпРСЯ ВХ)СЬ ), И 50 З; ПЯ тт 5: )ЕЕИмэв и выход 3-с)СдИ ИЕт 1,Ь, , С))с .тарьР 13 яэа иня Олае - . .ая:и;1 еитвитс.з:ьиых з я, нпй ягуента( иб 1 ок -И 1 ч 5 т., с;1013.Сан.я ат-.1.Эврусмой сх е.ь пиу 2,1 Я -.Ньх т н ФЗ".(емы для дия.эря:г.ь: ня фи . э зтояЗгумент .л. ),7 гсм сСверяются па=сеповятельн , все с 1)г умент:., ясполо;ЕПНЫЕ На Этс 1 жЕ С -уПЕт (7 ЕСТ;15 Ч - ой даграмрь, д(, " КижзйС(дгс Отьетвения яргуме г; я справя гппз 1 ри на. -личин ответвления с.праза вниз опускаются на следующую ступень лестничной диаграммыпредал)яют вычисление по этой ступенс(, ньчиная с крайнего ,гевога аргумента, )х т.д. После проверки аргумента, имеющего только ответвление справа вверх поднк(заются ня верхнюю ступень лес"пичной диагр(ммы и продолжают вычисление в том3 1328 гВ же порядке.(На Фиг, 6 Бсе аргумецть пронумерованы в порядке вычисления).В начале вычисления значение Функции (выход блока 2 вычисления значения бита логической функции) устанав ливается равным "1",В процессе вычисления Функция может принимать значение "О" в двух случаях: если действительное значение аргумента, имеющего ответвление 1 О справа вниз, совпадает со значением аргумента, указанного на лестничной диаграмме, и значение функции при проверке предыдущего аргумента было равно "1, или если действительное 15 значение аргумента, не имеющего ответвления справя в 11 э прлтивапалсжна значению абгумецта, указанного ня лестничной диаграмме, и знячеие ФУНКЦИИ ПРК ПРОтСРКР ГОЕГЬгтУ.етц Я - 2 О гумента сылс 1 я но1 В первом с.цучае по наличию атветвлениЙ справя Вцкз обняруж:вяетсядизъюнктивный ч:ец для тай яс.ги Фуц:ции, в которую входит проверяемый1аргумент, и установка зцячец:ядля Функции (вьгода блока 2) озцачяЕТ ЧТО ПРОБЕРЕЦНЫЙ Ч.ЕЦ;.ИЗЬОЦК 1111равен "1", спедсвательно. Бся дизь 11юнкция равна 1, и сстаегся:яйтцпаследнгй аргумент паследцегс членадизъюнкции пОсле прсверки катарсГОФУНКЦИЯ ВНОВЬ ДОЛжца ПРИНЯТЬ ЗцатЕние 111ЗгДля нахождения последнего аргумента последнего члена дизъюцкц;и по хо -ду вычисления подсчитывается чтслсответвлений от аргументов справа внизи справя ББерх . 11,яг Вычислен:1 ЙБкОтОРОм число стнетвлетий с 1 явявверх превышает числа атветцлоП-,Йсправа вниз. указывает на последнийаргумент последнего членадизъюцкции,При этом функция (выход блока 2)1111вновь принимает эцачение 1 , и вычисление продотжяется,Ва втором случае цеабхсдмо определить, имеет ли часть функции, Б которую входит только что проверенныйаргумент, дизъюнктивный член. Для нахождения дизъюнктивного члена по ходувычисления Функции подсчитываетсяколичество ответвлений от аргументаслева вниз и справа вниз, Шаг вычисления, в катарам числа ответвленийсправа вниз превьппяет на "1" числаответвлений слева Вниз, указываетна наличие дизъюнктивнага члена в 5 4тсй части функции, которая приняла значение О . При этом в следующем шаге вычислений функция (выход блока 2) вновь принимает значение "1", и вычисление продолжается.Описанный порядок и правила вычиспения позволяют однозначно определить значение функций любой переключательной схемы,Блок 2 вычисления значения бита логической функции работает следующим образом (фиг. 9 и 11).В начале вычисления счетчик 26 находится в исходном состоянии (содержимое равно 0 , значение выходного сигнала, а следовательно, и функции блока" 1" 1, В процесс Р 11 ьтисл енияпсс;1.:дацятс:ьца пс гпяГям дл каждогояс Г.Рн г я пе реключ 1 те;ьс Й схем. сумчетцас Гь сиНаОБ: Значение яргумецГС ,.1:,а -, ".Ц 1;,1 т ЦЯ ЛЕСТНт:тнст; т -,1 Раы 1ме, Дейсть:ГРьцае состояние ярГу,1м.ц" я, и оте "1 Б;РгпР сп,.дяца БцИзЕс 11 51.я КК ага ",1100 я 1 Г1 ц 1 г ,г Одействггс:.Ьнае состояние совпадает соЗЦЯ 1 ЕЦЕМ Нг ЛЕС Гцичцат,1 ГЯГРЯММЕ И1 Укестся сигналОтветвление справац;з , цл: Рс.ц: "ействительцае состоян:е аргумента це савпадаст со значе- ЦтРМ, УкаЗЯЦЦЫМ Я ЛЕСтЦИЧЦай Дцарамт"е и ОтсутствуРГ ЕИГнял ОТВстВ ленке спраза внизто на Выходе сумматора 21 по ",одулю два появляется сигца:1, увеличиваОщий ня 1 через элемент ЗИ-И.11 22 значение содержимого реверсивного счетчика 26, а зна- тЕНИЕ СИГНаЛа "ОТВЕтБЛЕНИР Сгравя Вниз" запоминается в триггере 25.1:огда значение ссдержпаго реверси нага счетч;ка 26 стят оьится отличНЬ;1 ОТ:1 СХОД 10 ГС 1 Та 3 Ц ат 1 Р НИР ВЫХОД ного сгца.я блока 2, а следовательно, и функции стгнсВится рявньы О11 При этом элемецть ЗИВ 1 т 22 и 2 И-ИЛИ3 работают таким образам, что, если Б триггср 5 бы;:а записано наличиез т ъ с 11 на 1 я Ответв 1 Рние справя Вниз та на суььируОгИ 1 вход реверсивного счетчика 26 падгется сигнал "Ответв;ение срава Вниз" и ня Вычитающий вход сигнал "Ответвление справа вверх", Если в триггере 25 было записано отсутствие сигнапа 1 Ответвление СпряВя ВНИЗ , То ЧЕреэ ЭЛЕМЕНТЫ тИ- ИПИ 22 и 2 И-ИГП 1 23 на суьпирующий Вход реверсивного счетчика 26 пода 11 11 ется сигнал Ответвление слева вниз а На БЫЧИтаЮщий ВХад - СИГНат 1 От" д) гРгсс" О У 1(И Я. С С 1,".ОТ Р И: 3 К Д Ч Е " Т)3 с) 1 РИ:1 Я 3ОС)ТУ ОЗОКД. ПС ДИЯГР ЯМЫЯ НД фРО, Для определенности пседпогпгат Га:рр- ;ЕР, ЧТО ЯРГУСТЬ ." Л,) Х.: Ряхза)а ка ш Рх з.:е ктрическуВ иТД ЬНЫЕ Я 13 ( ) МЕ НТЫ 3 (., ОЯ рязмцкдкших )з-.ектр 1-еску( епь,ЕГССГД ЧД "Гс ГЗГ 111 5 =С)Гф 1 КВ,1 Ь Г 0 ГТ О, Д)д.1ЕТСЯ РЯРЫМ -: 1 Т СООТ ЗЕТС 113 УЕ 10.)с тоя 1 ю ИО счетчика сО д .( тян;)г: д1)0 КЕТ б:П Ь ОСУЕС 3 ВЛЕПЯ П Э Вх ) 1 1: ЭИЗНЯкс ЗДПИСИ ВО ВНЕ 1 О:(3 Пс Я Ь д БЬд 1 С в ни, ПЯЧнпаЕсТСЯЯ) Г 3 ЬЕ 1 "ГДЗД;НгЕЯ гготи) Цй - дЗГ)Я;дсдР Я ВН , ( НО 3 МДЛ ,НО ОТК 0.1 Тэй К(. -ТД К Г):; С(дд 3 гЯ )сСГ С "ЕЙ(Т ЯИ( П)Нд3 ДсЕНЕМ ЯОГукЕ:Т-: ОтЗЕТ 33 . НИ; 1 ВЕЕ1 : СУ (СГН Е ";: Зс)1 Г т 1с;в ПООН . Г ЗЗР:; 11 Я ТИ У: (ПИИГЦЕгВ);ТЕ ".,Посс Н . и.Г ГдЕ 1"-р 11 О О ( ыкск)ге по и "0 Зп(дд 1. т, 0Д,;С-;И, дсУ(сс 3;.1 Цс; Я 1:С Гдс;1, ,1,гПИЯЯМЕНогЧД- Ч Я, 1.1".,Спрс";.ВЯ ЗНИЗ 0 ссу СТзуЕТЭуддп.Рдд ВЫ хоД блока д) не мениет своего з д- .С;П(5, ДЕйетВИТЕЛЬ ОЕ ЗЯЯНИС;:р11 " 11ъЕ Ясс,),. ЯВНО О с ПРО1 ВОПОНОЯ 1( 1( НачвнВ г -д, ,рОМ Н Д Ег 3 11 ;гй;)Д Г:-)Д ПЕ .) Г,В, )ыд, 1 образом) Зьпоп 53 озг( ус 3 опия д:1 Т ДНОВКР ПОСЛЕ ПВОРЕ Ки Я р Гуио ЕТс.,(. ) значения функнии вьдхода блока ) рдвм "01 ,состояне счетчика 2 б:зме 1 цястся и увеличивается на "), а от- .-3 ТСТВИЕ СИГНада "ОТВЕТВЛЕНИЕ Спрана Вниз зяпомин 3 ется 3 т 1)игГере 2Со следусего шага начинаетс подсчет ответвлений от аргументов 1 лева вни 3 и справа Вниз. Паслс. проверки)К ДЬ В ЫЧ И С1 3 Н и Я,Блок логическсй обработки в качестве унифидироьанного блока подключается к стандартному трехшиннсму ин- ТЕРфЕйСУ (Ш 3 НЯ ДспНЬП(. ШИНа аДРЕСа, пина управлеия) вычислительной системы для ор днизщии ее работы как программируемого контроллера. При7 13288этом конфигурация системы может бытьтакой, как указано на фиг, 4, где операционный блок 38 (микропроцессор) пошине 42 данных, шине 43 адреса ишине управления, включающей разряд44 признака записи во внешнюю память,разряд 45 признака чтения внешней па,мяти и разряд 46 тактовой частотымикропроцессора, подключен к блоку,39 логической обработки программируе мого контроллера и блокам 40 и 41памяти.Область ввода-вывода должна бытьпродублирована в блоке 40 памяти.Тогда блок 39 логической обработки 15при работе по переключательной схемеможет осуществлять обмен информациейтолько с блоком 40 памяти, где непосредственно за продублированной областью ввода-вывода должна находиться область промежуточных функций.Операционный блок 38 может бытьреализован на микропроцессореКР 580 И 80 А. Представленные мнемонические названия команд для определенности .даны на языке "Ассемблер" указанного микропроцессора,Блок 41 памяти содержит командыдля блока 39 логической обработки,определяющие работу программируемого 30контроллера при реализации переключательных схем, Каждая команда(фиг. 5) содержит два байта. В старшем байте содержится адресная частвкоманды, Младший байт содержит кодоперации для блока 39 логической обработки.Программируемый контроллер рабо,тает следующим образом.Для инициализации блока 39 логической обработки необходимо установить указатель стека микропроцессора 38 на первую ячейку блока 41, скоторой начинается последовательностькоманд, описывающих переключательные 45схемы, в регистр Н микропроцессораввести старшую часть адреса областиввода-вывода и промежуточных функций,в пару регистров ПЕ ввести адрес возврата после вычисления всех логических функций, произвести операцию вывода (установку в исходное состояниеблока 39 логической обработки), осуществить передачу управления в область адресного пространства внешней 55памяти, занимаемой блоком 39 логической обработки (указанная область определяется набором перемычек 37 дешифратора 8). Реализует инициализирую 15 8щую последовательность для блока 39логической обработки программаЯТАКТ: 1,Х 1 ЯР, ИЦЧМЧ 1 Н, АЭК1 Х 1 О, БТАКТМОЧ А, ММОЧ М, А1 МР 1.ОСРКОбъем адресного пространства, занимаемого блоком 39 логической обработки, должен быть достаточным для отработки всех команд, описывающих переключательные схемы. В обычном случае этот объем не превышает 16 кбайт.После передачи управления в областьадресного пространства блока 39 логической обработки последний начинает работать в соответствии с алгоритмом,указанным на фиг. 10,Первоначально в соответствии с содержимым блока 6 памяти кодов операции микропроцессор через информационную шину 16 блока 39 логическойобработки считывает код команды РОР В,после чего содержимое счетчика 7 команд увеличивается на "1", подготавливая для чтения следующую ячейкублока 6 памяти кодов операции. Микропроцессор устанавливает на шине 43адреса адрес младшего байта, читаемого из стека. Этот адрес через шинуадреса внешней памяти процессора поступает на дешифратор 9 и с приходомсигнала чтения внешней памяти содержимое младшего байта команды записывается в регистр 5 команд (фиг. 8).Адрес внешней памяти задается на дешифраторе 9 перемычками 37,Затем микропроцессор заканчиваетчтение из области стека, после чегов паре регистров ВС оказывается команда блока 39 логической обработки.Далее, если в поле кода операции регистра 5 команд оказывается код, соответствующий концу программы, микропроцессор последовательно выполняеткоманды ХСНС и РСН 1. из блока 6 памяти и осуществляет деинициализациюблока 39 логической обработки переходом по адресу, заданному в паре регистров РЕ,Если в поле кода операции регистра 5 команд оказывается код, соответствующий проверке аргумента (открытый или закрытый контакт), и выходблока 2 находится в состоянии логической "1", микропроцессор последовательно выполняет команды иэ блока 6памяти МОЧ Ь,В (формирование адреса9 132881анализируемого логического условия)и МОЧ А, М (проверка логического условия).При выполнении микропроцессоромоперации чтения анализируемого байтаосуществляется переключение (при необходимости) реверсивного счетчика 26по сигналу с дешифратора 3 ввода-вывода, Адрес ввода-вывода задаетсяна дешифраторе 3 перемычками 37. Затем счетчик 7 команд обнуляется, иуказанный цикл повторяется,Если н поле кода операции регистра 5 команд оказывается код, соответствующий проверке аргумента, и выход 15блока 2 находится в состоянии логического "0" при чтении микропроцессором старшего байта команды из стека,осуществляются сначала сброс счетчика 7 команд, а затем йереключение ре нерсивного счетчика 26.Если в поле кода операции регистра 5 команд оказывается код, соотнетствующий обработке выхода (катушкареле), микропроцессор последовательно выполняет команды ИОЧ Т.,В и И 71А, СОИБТ.Причем значение СОМЯТ выбираетсяв зависимости от состояния выходаблока 2 вычисления значения бита логи.ЗОческой функции и состояния поля номера кода операции регистра 5 команд,Затем, если состояние выхода блока 2соответствует логическому 0, микропроцессор выполняет команду АМА М,н противном случае - ОБА М, После это.го результат вычислений оказываетсяВ аккумуляторе микропроцессора, ицикл заканчивается выполнением команды МОУ М,А. На,фиг. 7 в таблице для 10константы СОйЯТ ее значение указанов шестнадцатеричной системе счисления.Формула изобретенияПрограммируемый контроллер, содер.жащий операционный блок, блок логической обработки и блок памяти, информационный ВхОд-ВыхОд которого соединен 50 с информационными входами-выходами сперационного блока и блока логической обработки, информационный вход которого соединен с информационным ныхо. Дом операционного блока и адресным входом блока памяти, вход упранления чтением которого соединен с выходом признака ввода данных операционного блока и с входомпризнака вывода дан 5 10ных блока логической обработки, входпризнака ввода данных которого соединен с входом управления записью блокапамяти и входом признака вывода данных операционного блока, выход синхронизации которого соединен с входами синхронизации блока логической обработки и блока памяти, причем блоклогической обработки содержит мультиплексор, первый дешифратор, первыйэлемент И, сумматор по модулю два,триггер, первый элемент 2 И-ИЛИ и элемент ЗИ-ИЛИ, счетчик и первый элементИЛИ-НЕ, выход которого соединен ссинхровходом триггера, с первым инторым инверсными входами первогоэлемента 2 И-ИЛИ и с первым и вторыминверсными, с первым прямым входамиэлемента ЗИ-ИЛИ, выходы элемента ЗИИЛИ и первого элемента 2 И-ИЛИ соединены соответственно с суммирующим ивычитающим входами счетчика, выходкоторого соединен с входом первогоэлемента ИЛИ, выход триггера соединенс третьим инверсным и первым прямымвходами первого элемента 2 И-ИЛИ и стретьим инверсным и вторым прямымвходами элемента ЗИ-ИЛИ, первый входи выход сумматора по модулю два соединены соответственно с выходом мультиплексора и третьим прямым входомэлемента ЗИ-ИЛИ, информационный входвыход блока логической обработки соединен с информационным входом мультиплексора, входы признака вывода ипризнака ввода данных блока логической обработки соединены соответственно с первым и вторым инверсными входами первого элемента И, вход блока логической обработки соединен с входомпервого дешифратора, выход которогосоединен с прямым входом первого элемента И, о т л и ч а ю щ и й с я тем,что, с целью сокращения объема блокапамяти программируемого контроллера,блок логической обработки содержитс второго по шестой элементы И, второй дешифратор, третий дешифратор,регистр команд, счетчик команд, блокпамяти кодов операций, второй элементИЛИ, второй элемент 2 И-ИЛИ, выходкоторого соединен с синхровходомсчетчика, вход установки в "0" которого соединен с инверсный нходом второго элемента ИЛИ и входом признакаввода данных блока логической обработки, информационный вход-выход которого соединен с выходом блока памяти кодов операций и с информационным, входом регистра команд, выход счетчика команд, выход поля кода операции и номера кода операции, регистра команд и выход первого элемента ИЛИ соединены с группой адресных входов блока памяти кодовоперации, выход младшего разряда поля кода операции регистра команд соединен с вторыми инверсными входами второго элемента 2 И-ИЛИ и с первыми инверсными входами четвертого и пятого элементов И, выходы которых соединены с первым и вторым прямыми входами второго элемента ИЛИ, выход которого соединен с входом установки в "О" счетчика команд, нулевой разряд выхода которого соединен с первыми прямыми входами четвертого и пятого элементов И, второй прямой вход которого соединен с первым разрядом выхода счетчика команд, вход синхронизации которого соединен с вторым инверсным входом пятого и выходом шестого элементов И и с входом разрешения чтения блока памяти кодов операций, информационный вход блока логической обработки соединен с входами второго и третьего дешифраторов, выход которого соединен с прямым входом шестого элемента И, инверсный вход которого соединен с первым инверсным входом второго и первым входом третьего элементов И и с входом признака вывода данных блока логической обработки, выход первого элемента И соединен с первым прямым входом второго элемента 2 ИИЛИ, второй прямой и третий инверсный ,входы которого соединены с выходом первого элемента ИЛИ, с синхровходомтриггера и вторым инверсным входомчетвертого элемента И, второй прямой 5вход которого соединен с третьим прямым входом второго элемента 2 И-ИЛИи с выходом второго элемента И, первый прямой вход которого соединен смладшим разрядом информационного вхо О да блока логической обработки и вторым входом третьего элемента И, третий вход которого соединен с вторымвходом второго элемента И и с выходом третьего дешифратора, четвертый 15 .вход третьего элемента И соединенс входом синхронизации блока логической обработки и,с третьим инверснымвходом пятого элемента И, выход третьего элемента И соединен с входом 20 синхронизации регистра командф выходстаршего разряда поля кода операциирегистра команд соединен с вторымвходом сумматора по модулю два, выходмладшего разряда поля признака кода 25 операции регистра команд соединен стретьим входом сумматора по модулюдва, с третьйм прямым входом элемента ЗИ-ИЛИ и вторым прямым входом первого элемента 2 И-ИЛИ, и с информационным входом триггера, выходы старшего и среднего разрядов поля признакакода операции регистра команд соединены соответственно с третьим прямымвходом первого элемента 2 И-ИЛИ и счетвертым прямым входом первого элемента 2 И-ИЛИ, выход поля номера кодаоперации регистра команд соединенс управляющим входом мультиплексора.1328815 фиг, Ф Юабаий байт Норсер коба опе- Поде признака раиии Поде кода Р 7 Р 6 Р 6 РФ РУ Р 2 Р Р 0 а Оиарший РайтР 6 Р 5 Р 1 Р 5 Р 2 Р

СмотретьЗаявка

4034019, 07.03.1986

МОСКОВСКИЙ АВТОМОБИЛЬНЫЙ ЗАВОД ИМ. И. А. ЛИХАЧЕВА

АНДЕРСОН АЛЕКСАНДР ИОСИФОВИЧ, ХОХЛОВ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: контроллер, программируемый

Опубликовано: 07.08.1987

Код ссылки

<a href="https://patents.su/12-1328815-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Вероятностный интегратор

Следующий патент: Устройство для загрузки групповых данных

Случайный патент: Устройство для сварки и отделения пакетов к упаковочным машинам