Устройство управления загрузкой микропрограмм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

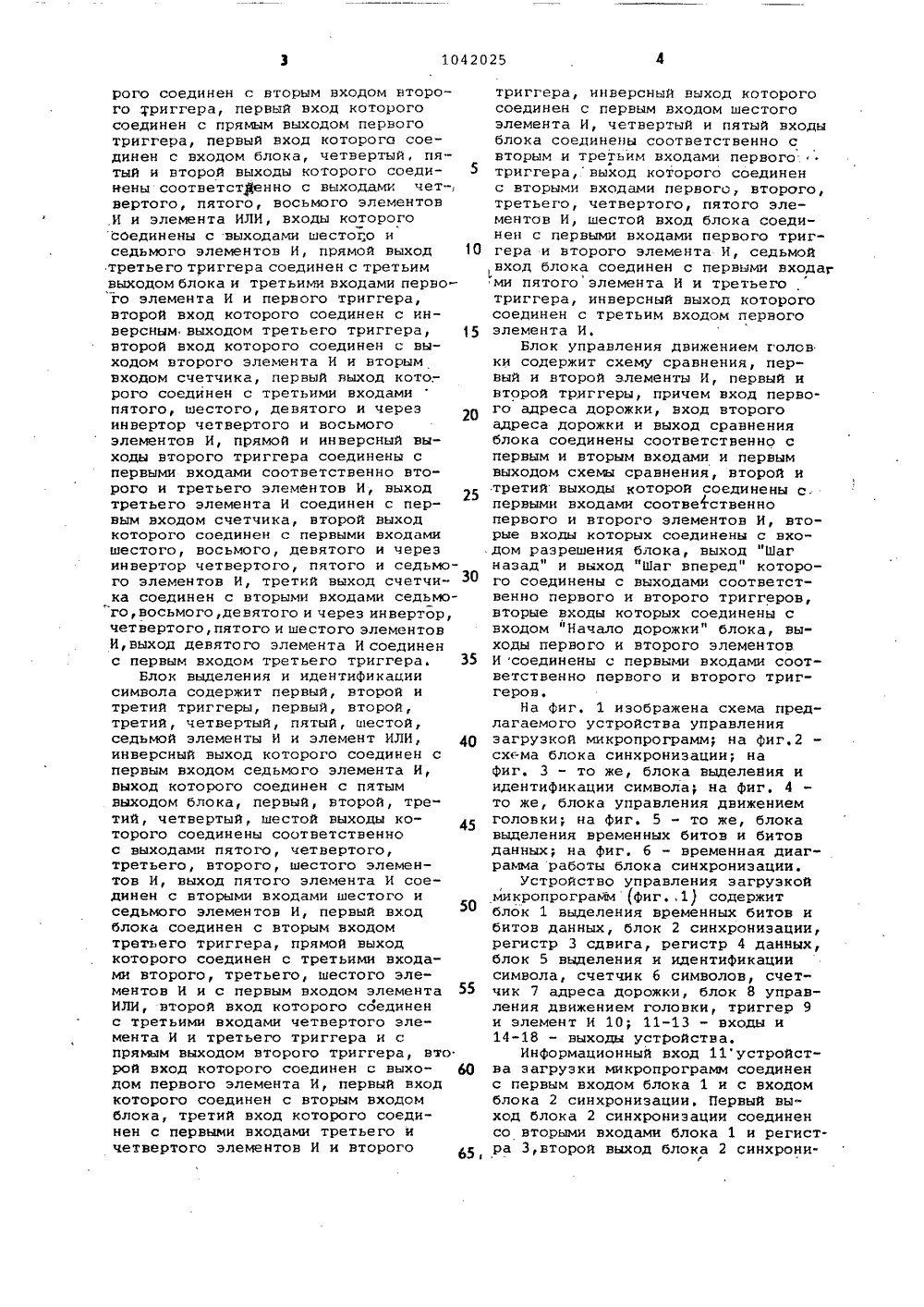

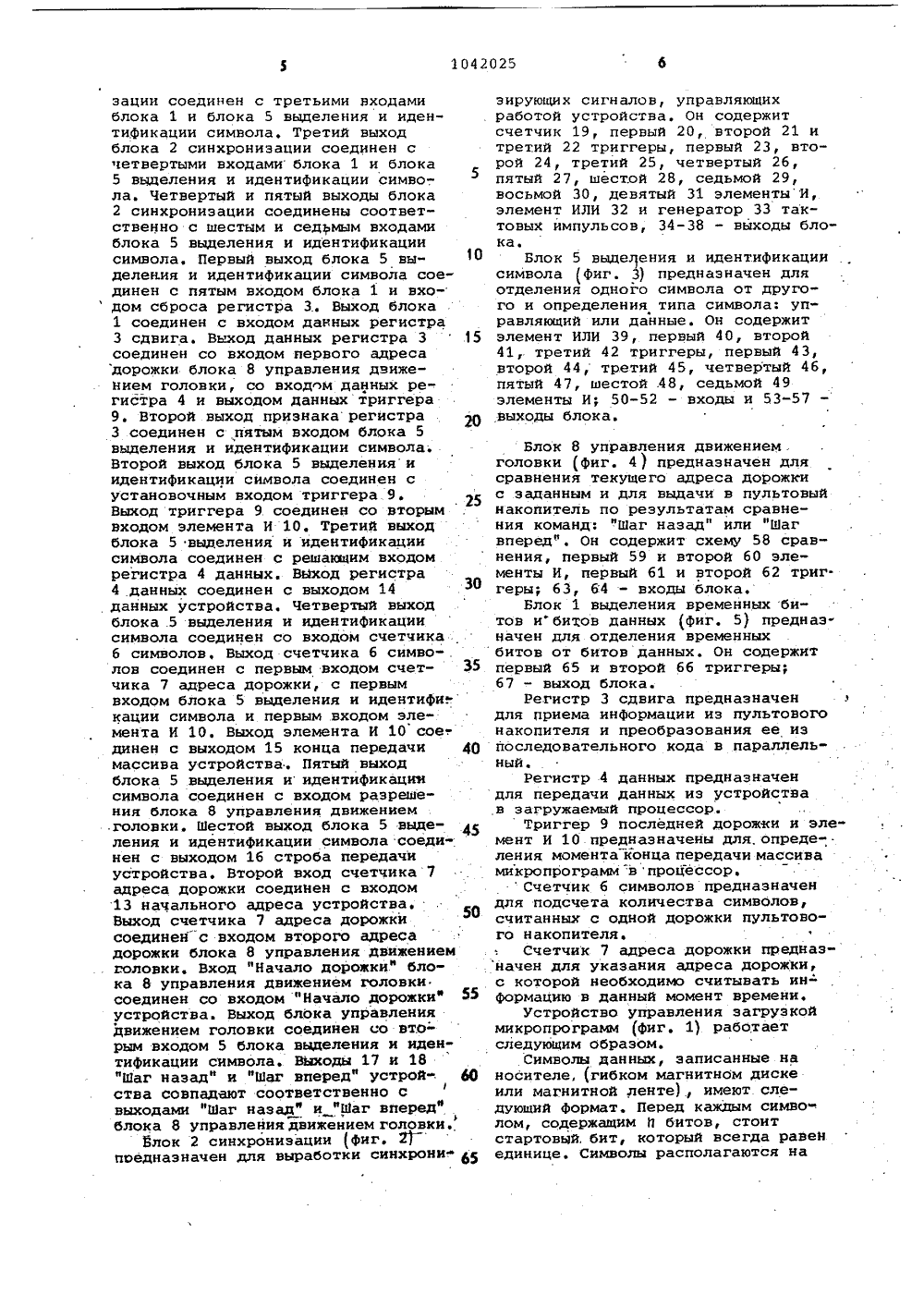

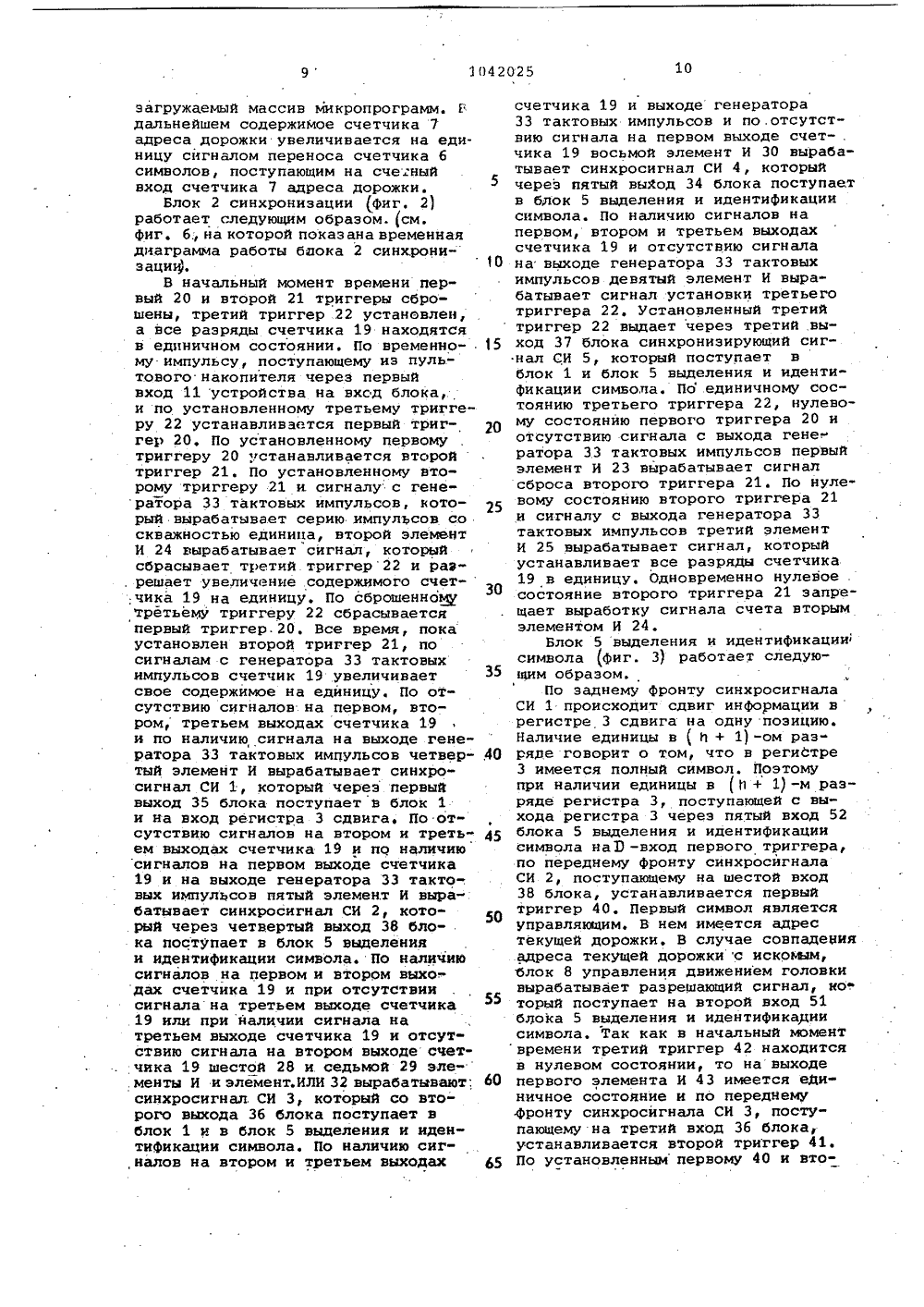

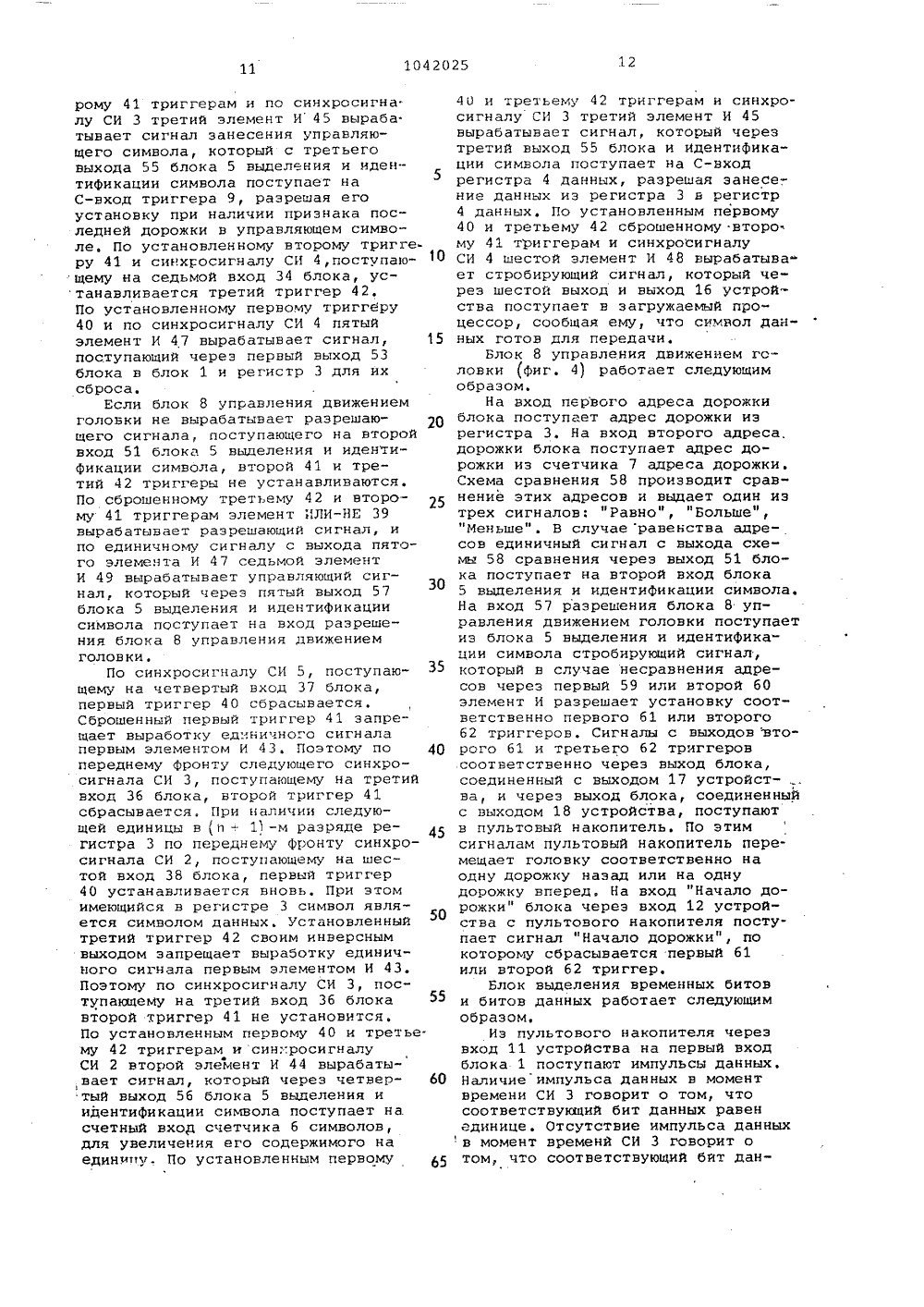

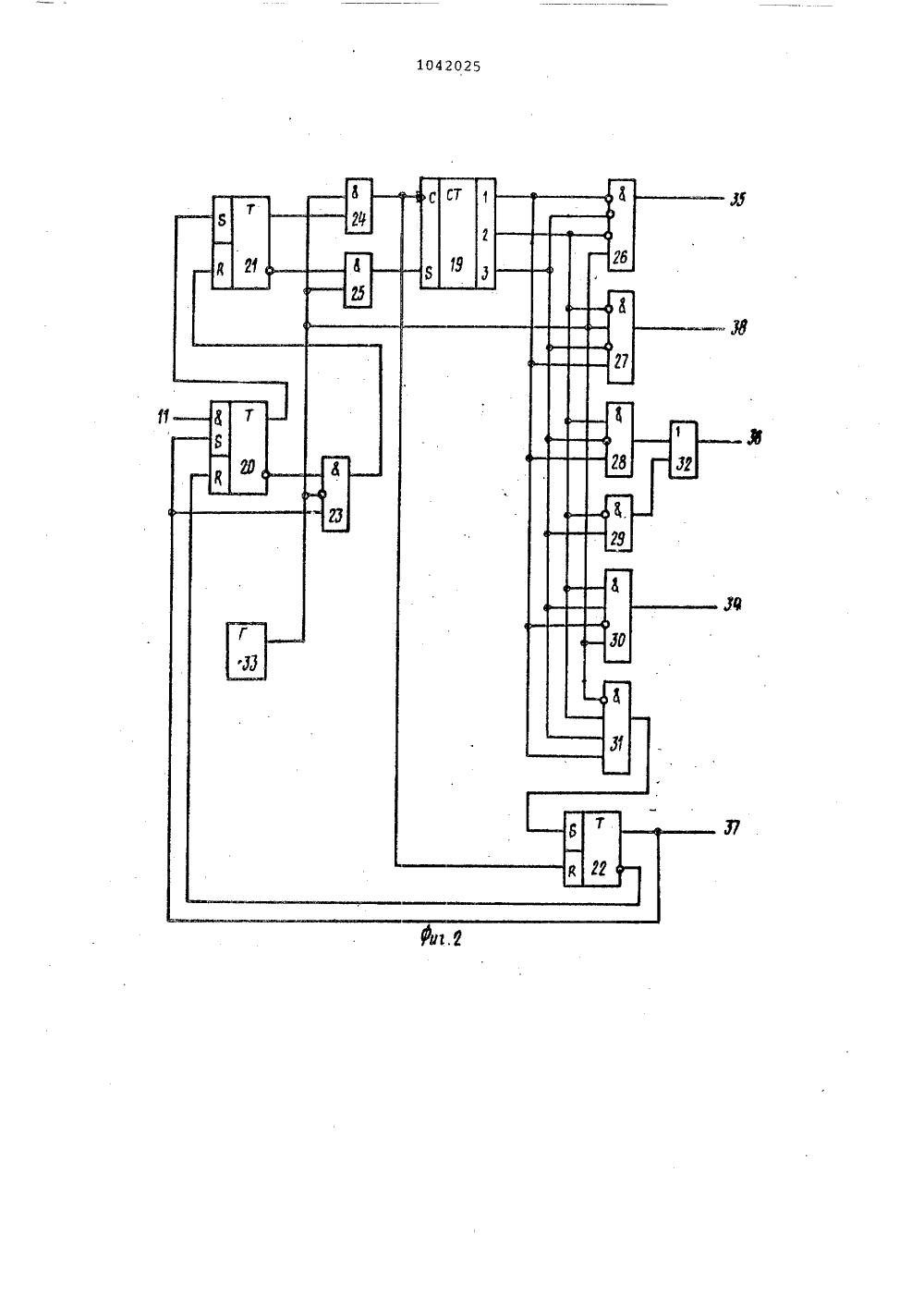

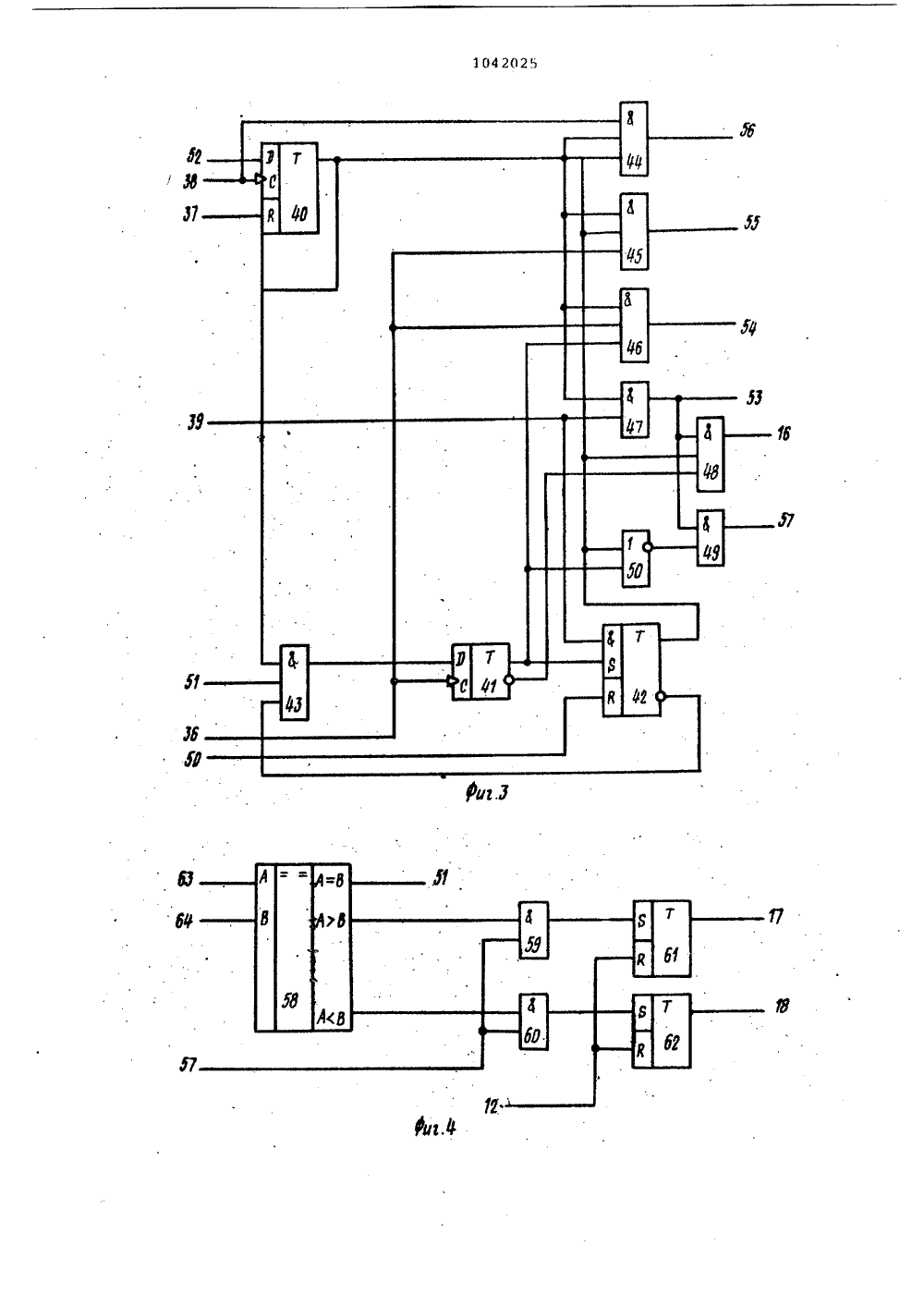

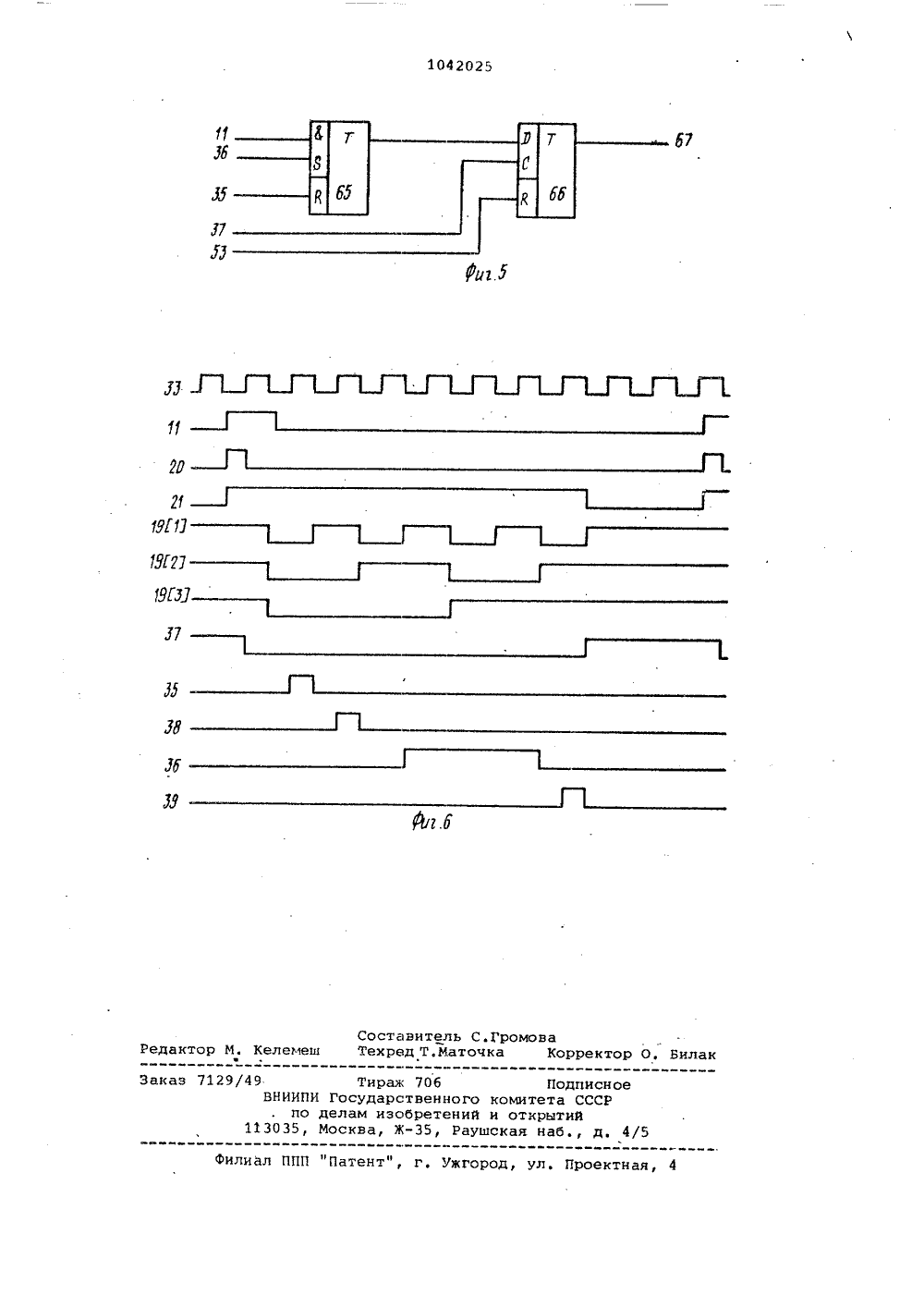

(50 0 06 Р 13/04 Я ::-:;.,ОПИСАНИЕ ИЗОБРЕТЕМ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 2, Устройс а ю щ е е с инхронизации торой и трет о по п. 1, о т л итем, что блок одержит первый,триггеры, счетчик, ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ,(54)(57) 1, устройство упРАВлениЯЗАГруЗОЙ МИКРОПРОГРАММ, содержащее регистр сдвига, счетчик символов, регистр данных и блок выделения временных битов и битов данных, первый вход которого подключен к информационному входу устройства, а первый выход - к информационному входу регистра сдвига, выход данных которого соединен с входом данных регистра данных, выход которого подключен к выходу данных устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, в него введены блок синхронизации, блок выделения и идентификации символов, счетчик адреса дорожки, блок управления движением головки, триггер и элемент И, причем выход счетчика символов подключен к первому входу блока выделения и идентификации символов, к первому входу счетчика адреса дорожки и первому входу элемента И, выход которого соединен с выходом конца передачи массива устройства, а второй вход - с выходом триггера, вход блока синхронизации подключен к информационному входу устройства, первый выход - к второму входу блока выделения временных битов и к управляющему входу регистра сдвига, второй выход - к третьему входу блока выделения временных битов ибитов данных, третий выход - к четвертому входу блока выделения временных битов и битов данных, пятыйвход которого соединен с входомсброса регистра сдвига и первымвыходом блока выделения и идентификации символа, второй выход которого подключен к установочному входутриггера, вход данных которого соединен с входом первого адреса дорожки блока управления движениемголовки и выходом регистра с,вига,третий выход блока выделения иидентификации символа подключен кразрешающему входу регистра данных,четвертый выход - к входу счетчикасимволов, пятый выход - к входуразрешения блока управления движением головки, шестой выход -"к выходу строба передачи устройства,второй вход - к выходу сравненияблока-управления движением головки,третий вход - к второму выходублока синхронизации, четвертыйвход - к третьему выходу блокасинхронизации, пятый вход -к вы-ходу признака регистра сдвига,шестой вход - к четвертому выходублока синхронизации, седьмой входк пятому выходу блока синхронизации, второй вход счетчика адресадорожки подключен к входу начально.Го адреса устройства, а выход -. свходом второго адреса дорожки бло-.ка управления движением головки,вход фНачало дорожки" которого соединен с входом "Начало дорожки"устройства, а,выходы "Шаг назад"и "Шаг впередп - с выходами "Шагназад" и "Шаг впереди соответственно устройства.1042025Фиг 521 1 Ю 3 Составитель С.ГромоваТехред Т,Маточка Корректор О, БилакРедактор М. КелемешЗаказ 7129/49 Тираж 706 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5ее е е ефилиал ППП "Патент", г. Ужгород, ул, Проектная, 4первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с четвер,тыми входами четвертого, пятого и восьмого элементов И, с вторыми входами второго и третьего элементов И и через инвертор с четвертымвходом девятого элемента И и с вторым входом первого элемента И, выход которого соединен с вторым входом второго триггера, первый вход которого соединен с прямым выходом первого триггера, первый вход которого соединен с входом блока, первый, четвертый, пятый и.второй выходы которого соединены соответственно с выходами четвертого, пятого, восьмого элементов И и элемента ИЛИ, входы которого соединены о выходами шестого и седьмого элементов И, прямой выход треТьего триггера соединен с третьим выходом блока и третьими входами первого элемента И и первого триггера,второй вход которого соединен с инверсным выходом третьего триггера, второй вход которого соединен с выходом второго элемента И и вторым входом счетчика, первый выход которого соединен с третьими входами пятого, шестого, .девятого и через инвертор четвертого и восьмого элементов И, прямой и инверсный выходы второго триггера соединены с первыми входами соответственно второго и третьего элементов И, выход третьего элемента И соединен с первым входом счетчика, второй выход которого соединен с первыми входами шестого, восьмого, девятого и через инвертор четвертого, пятого и седьмого элементов И, третий выход счетчика соединен с вторыми входами седьмого, восьмого, девятого и через инвертор четвертого, пятого и шестого элементов И, выход девятого элемента И соединен с первым входом третьего триггера.3, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок выделения и идентификации символа содержит первый, второй и третий триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы,Й и элемент ИЛИ, инверсный выход которого соединен с первым вХодом седьмого элемента И, выход которого соединен с пятым выходом блока, первый, второй, третий, четвертый, шестой выходы которого соединены соответственно с выходами пятого, четвертого, третьего, второго, шестого элементов И, выход пятого .элемента И соединен с вторыми входами шестого и седьмого элементов И, первый вход блока соединен с вторым входом третьего триггера, прямой выход которого соединен с третьими входами второго, третьего, шестого элементов И и с первым входом элемента ИЛИ, второй вход которого соединен с третьими входами четвертого элемента И и третьего триггера и с прямым выходом второго триггера, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с вторым входом блока, третий вход которого соединен с первыми входами третьего и четвертдго элементов И и второго триггера, инверсный выход которого соединен с первым входом шестого элемента И, четвертый и пятый входы блока соединены соответственно с вторым и третьим входами первого триггера, выход которого соединен с вторыми входами первого, второго, третьего, четвертого, пятого элементов И, шестой вход блока соединен с первыми входами первого триггера и второго элемента И, седьмой вход блока соединен с первыми , входами пятого элемента И и третьего триггера, инверсный выход которого соединен с третьим входом первого элемента И. 4. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок управ. ления движением головки содержит схему сравнения, первый и второй элементы И, первый и второй триггеры, вход первого адреса дорожки, вход второго адреса дорожки и выход сравнения блока соединены соответственно с первым и вторым входами и первым выходом схемы сравнения, второй и третий выходы которого соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с входом разрешения блока, выход "Шаг назад" и выход "Шаг вперед" которого соеди-, нены с выходами соответственно первого и второго триггеров, вторые входы которых соединены с входом "Начало дорожки" блока, выходы первого и второго элементов И соединены с первыми входами соответственно первого и второго триггеров.30 Изобретение относится к вычислительной технике и может. быть применено н ЭВМ с перезагружаемой памятьюмикропрограмм,Известно устройство, содержащеесдвигающий регистр, сепаратор, счетчик байтов 1 .Недостатком устройства являетсяотсутстние возможности его использования для загрузки микропрограммв процессор, так как информация,считанная с пультового накопителя,может использоваться только длядиагностических и сервисных функций.Известно также устройство упранления для аппаратуры хранения последонательной информации, содержащеесепаратор, счетчик байтов, регистрданных накопителя, коммутатор, регистр данных 21 .Недостатком этого устройства 20являются большие затраты оборудования.Наиболее близким к изобретениюявляется устройство, содержащеерегистр данных накопителя, регистрданных, счетчик симнолон и сепара-.тор, первый вход и выход которогосоединены соответственно с первымвходом устройства и с перным входомрегистра данных накопителя, первыйвыход которого соединен со вторымвходом регистра данных, выход которого соединен с первым выходомустройства 33 .Недостатком данного устройстваявляются избыточные затраты оборудования, связанные с реализациейвоэможности модификации адреса дорожки на произвольную величину, атакже с наличием сложного оборудова"ния для определения конца массива, 40данных и окончания процесса загруз"ки, Кроме того, избыточные затратыоборудования требуются для идентификации. считываемой с носителя информации и для реализации довольно 45сложного алгоритма связи этого устройства с процессором.Цель изобретения - сокращение,аппаратурных затрат.Поставленная цель достигаетсятем, что в устройство управлениязагрузкой микропрограмм, содержащеерегистр сдвига, счетчик символов,регистр данных и блок выделениявременных битов и битов данных, первый вход которого подключен к инФормационному входу устройства, апервый выход - к информационному вхот.ду регистра сдвига, выход данныхкоторого соединен с входом данных,регистра данных, выход которого подключен к выходу данных устройства,в него введены блок синхронизации,блок выделения и идентификациисимволов, счетчик адреса дорожки,блок управления движением головки, 65 триггер и элемент И, причем выходсчетчика еимнолон подключен к перно-му входу блока выделения и идентификации символов, к перному входу счетчика адреса дорожки и первОму входу элемента И, выход которого соединен с выходом конца передачи массива устройства, а второй вход с выходом триггера, вход блока синхронизации подключен к информационному входу устройства, первый выход - к второму входу блока выделения временных битов и, к управляющему входу регистра сдвига, второй выход - к третьему входу блока выделения временных битов и битовданных, третий выход - к четвертомувходу блока выделения временных битон и- битов данных, пятый вход которого соединен с входом сброса регистра сдвига и первым выходом блокавыделения и идентификации данных, второй выход которого подключен к установочному входу триггера, вход данных которого соединен с входом первого адреса дорожки блока управления движением голонки и выходом регистра сдвига, третий выход блока выделения и идентификации символа подключен к разрешающему входу ре гистра данных, четвертый выход -к входу счетчика символов, пятый выход - к входу разрешения блокауправления движением головки, шестойвыход - к выходу строба передачи устройства, второй вход - к выходу сравнения блока управления движени- ем головки, третий вход - к второму выходу блока синхронизации, пятый вход - к выходу признака регистра сдвига, шестой вход - к четвертому выходу блока синхронизации, седьмойвход - к пятому выходу блока синхронизации, второй вход счетчика адреса дорожки подключен к входу начального адреса устройства, а выход - с входом второго адреса дорожки блока управления движением головки, вход "Начало дорожки" которого соединен с входом "Начало дорожки" устройства, а выходы "Шаг назад" и "Шаг вперед" - с выходами "Шаг назад" и "Шаг вперед" устройства соответственно. Блок синхронизации содержитсчетчик, первый, второй .и третийтриггеры; первый, второй, третий,четвергый, пятый, шестой, седьмой,восьмой, девятый элементы И, элемент ИЛИ й генератор тактовых импульсов, выход которого соединен с четвертыми входами, четвертого, пятого и восьмого элементов И, с вторыми входами второго и третьего элементов И и че-. рез инвертор с четвертым входомдевятого элемента И и с вторым вхо- дом первого элемента И, выход кото 1042025рого соединен с вторым входом второго триггера, первый вход которогосоединен с прямым выходом первоготриггера, первый вход которого соединен с входом блока, четвертый, пятый и нторой выходы которого соедивены соответственно с ныходамк чет-,вертого, пятого, восьмого элементовИ и элемента ИЛИ, входы которогосОединены с выходами шестого иседьмого элементов И, прямой выход 1 Отретьего триггера соединен с третьимвыходом блока и третьими входами перного элемента И и первого триггера,второй вход которого соединен с инверсным выходом третьего триггера,нторой вход которого соединен с выходом второго элемента И и вторымвходом счетчика, первый выход кото;рого соединен с третьими входамипятого, шестого, девятого и черезинвертор четвертого и восьмогоэлементон И, прямой и инверсный выходы второго триггера соединены спервыми входами соответстненно втоРОГО и третьеГО элементов и, выход 25третьего элемента И соединен с первым входом счетчика, второй выходкоторого соединен с первыми входамишестого, восьмого, девятого и черезинвертор четвертого, пятого и седьмого элементов И, треткй выход счетчика соединен с вторыми входами седьмого,восьмого, девятого и через инвертор,четвертого, пятого и шестого элементовИ,выход девятого элемента И соединенс первым входом третьего триггера. 35Блок выделения и идентификациисимвола содержит первый, второй итретий триггеры, первый, второй,третий, четвертый, пятый, шестой,седьмой элементы Й к элемент ИЛИ, 4 Оинверсный выход которого соединен спервым входом седьмого элемента И,выход которого соединен с пятымвыходом блока, первый, второй, тре"тий, четвертый, шестой выходы которого соединены соответстненнос выходами пятого, четвертого,третьего, второго, шестого элементов И, выход пятого элемента И соединен с вторыми входами шестого иседьмого элементов И, первый входблока соединен с вторым входомтретьего триггера, прямой выходкоторого соединен с третьими входами второго, третьего, шестого элементов И и с первым входом элемента 55ИЛИ, второй вход которого соединенс третьими входами четвертого элемента И и третьего триггера и спрямым выходом второго триггера, второй вход которого соединен с выходом первого элемента И, первый входкоторого соединен с вторым входомблока, третий вход которого соединен с первыми входами третьего ичетвертого элементов И и второго1 триггера, инверсный ныход которогосоединен с первым входом шестогоэлемента И, четвертый и пятый входыблока соединены соответственно свторым и третьим входами первоготриггера,выход которого соединенс вторыми нходами первого, второго,третьего, четвертого, пятого элементов И, шестой вход блока соединен с первыми входами первого триггера и второго элемента И, седьмойвход блока соединен с первыми входагми пятого элемента И и третьеготриггера, инверсный выход которогосоединен с третьим входом первогоэлемента И.Блок управления движением головки содержит схему сравнения, первый и второй элементы И, первый ивторой триггеры, причем вход первого адреса дорожки, вход второгоадреса дорожки и выход сравненияблока соединены соответственно спервым и вторым входами и первымвыходом схемы сраннения, второй итретий выходы которой соединены с.первыми входами соответственнопервого и второго элементов И, вторые входы которых соединены с входом разрешения блока, выход "Шагназад" и выход "Шаг вперед" которого соединены с выходами соотнетственно первого и второго триггеров,вторые входы которых соединены свходом "Начало дорожки" блока, выходы перного и второго элементовИ соединены с первыми входами соответственно первого и второго триггеров.На фиг, 1 изображена схема предлагаемого устройства управлениязагрузкой микропрограмм; на фиг.2схема блока синхронизации; нафиг. 3 - то же, блока выделеНия иидентификации символа; на фиг. 4то же, блока управления движениемголовки; на фиг. 5 - то же, блокавыделения временных битов и битовданных; на фиг. б - временная диаграмма работы блока синхронизации.Устройство управления загрузкоймикропрограмм фиг.,1) содержитблок 1 выделения временных битов ибитов данных, блок 2 синхронизации,регистр 3 сдвига, регистр 4 данных,блок 5 выделения и идентификациисимвола, счетчик б символов, счетчик 7 адреса дорожки, блок 8 управления движением головки, триггер 9и элемент И 10; 11-13 - нходы и14-18 - выходы устройства,Информационный вход 11 устройства загрузки микропрограмм соединенс первым входом блока 1 и с входомблока 2 синхронизации. Первый выход блока 2 синхронизации соединенсо вторыми входами блока 1 и регистра З,второй выход блока 2 синхрони50 зации соединен с третьими входами блока 1 и блока 5 выделения и идентификации символа. Третий выход блока 2 синхронизации соединен с четвертыми входами блока 1 и блока 5 выделения и идентификации символа. Четвертый и пятый выходы блока 2 синхронизации соединены соответственно с шестым и седьмым входами блока 5 выделения и идентификации символа. Первый выход блока 5 выделения и идентификации символа соединен с пятым входом блока 1 и вхо дом сброса регистра 3 Выход блока 1 соединен с входом данных регистра 3 сдвига. Выход данных регистра 315 соединен со входом первого адреса дорожки блока 8 управления движением головки, со вход м данных регистра 4 и выходом данных триггера 9. Второй выход признака регистра 3 соединен с пятым входом блока 5 выделения и идентификации символа, Второй выход блока 5 выделенияи идентификации символа соединен с установочным входом триггера 9. Выход триггера 9 соединен со вторым входом элемента И 10. Третий выход блока 5 выделения и идентификации символа соединен с решающим входом регистра 4 данных. Вйход регистра 4 данных соединен с выходом 14 данных устройства. Четвертый выход блока .5 выделения и идентификации символа соединен со входом счетчика б символов, Выход счетчика б симво- . лов соединен с первым входом счет чика 7 адреса дорожки, с первым входом блока 5 вьщеления и идентифи. кации символа и первым входом элемента И 10. Выход элемента И 10 сое; динен с выходом 15 конца передачи 40 массива устройства. Пятый выход блока 5 вьщеления иидентификации символа соединен с входом разрешения блоха 8 управления движением головки. Шестой выход блока 5 виде ления и идентификации символа соединен с выходом 16 строба передачи устройства. Второй вход счетчика 7 адреса дорожки соединен с входом 13 начального адреса устройства. Выход счетчика 7 адреса дорожки соединен с входом второго адреса дорожки блока 8 управления движением головки. Вход фНачало дорожки" блока 8 управления движением головки соединен со входом "Начало дорожки" 55 устройства. Выход блока управления движением головки соединен со вто- рым входом 5 блока вьщеления и идентификации символа. Выходы 17 и 18 "Шаг назад" и "Шаг вперед" устрой" 60 ства совпадают соответственно с выходами фШаг назад" и фШаг вперед" блока 8 управлений движением головки.Блок 2 синхронизации (фиг. 2) предназначен для выработки синхронизирующих сигналов, управляющих работой устройства, Он содержит счетчик 19, первый 20, второй 21 и третий 22 триггеры, первый 23, второй 24, третий 25, четвертый 26, пятый 27, шестой 28, седьмой 29, восьмой 30, девятый 31 элементыИ, элемент ИЛИ 32 и генератор 33 тактовых импульсов, 34-38 - выходы блока.Блок 5 вьщет)ения и идентификации символа (фиг. 3) предназначен для отделения одного символа от другого и определения типа символа: управляющий или данные. Он содержит элемент ИЛИ 39, первый 40, второй 41, третий 42 триггеры, первый 43, второй 44, третий 45, четвертый 46, пятый 47, шестой .48, седьмой 49 элементы И; 50-52 - входы и 53-57- выходы блока. Блок 8 управления движением . головки (фиг. 4) предназначен для сравнения текущего адреса дорожки с заданным и для выдачи в пультовый накопитель по результатам сравнения команд: "Шаг назад" или "Шаг вперед". Он содержит схему 58 сравнения, первый 59 и второй 60 элементы И, первый 61 и второй 62 триггеры; 63, 64 - входы блока.Блок 1 выделения временных битов и битов данных (фиг. 5) преднаэ. начен для отделения временных битов от битов данных. Он содержит первый 65 и второй 66 триггеры;67 - выход блока.Регистр 3 сдвига предназначендля приема информации из пультового накопителя и преобразования ее из последовательного кода в параллельный.Регистр 4 данных предназначен для передачи данных из устройства в загружаемый процессор.Триггер 9 последней дорожки и элемент И 10 предназначены для,опреде-. ления момента конца передачи массива микропрограмм в процессор.Счетчик 6 символов предназначен для подсчета количества символов, считанных с одной дорожки пультового накопителя.Счетчик 7 адреса дорожки предназначен для указания адреса дорожки, с которой необходимо считывать ин- формацию в данный момент времени.Устройство управления загрузкой микропрограмм (Фиг. 1) работает следующим образом.Символы данных, записанные на носителе, (гибком магнитном диске или магнитной ленте)., имеют следующий Формат, Перед каждым символом, содержащим И битов, стоит стартовый. бит, который всегда равен единице. Символы располагаются на40 Блок 2 синхронизации вырабатывает синхросигналы, которые поступают на блок 1, регистр 3 сдвига и блок 5 выделения и идентификации символа. Блок 5 выделения и идентификации символа определяет момент, когда в регистре 3 сдвига имеется полный символ, а также тип символа- управляющий или данные. В зависимости от типа символа блок 5 выделения и идентификации символа разрешает занесение символа в регистр 4 данных или установку триггера 9, который устанавливается, если в управляющем символе имеется соответ ствующий признак. После выделения символа блок 5 выделения и идентификации символа со своего первого выхода 53 выдает в блок 1 и регистр 3 сдвига сигнал сброса, который 60 служит для отделения одного символа от другОгоКроме того, выделив управляющий симнол, блок 5 ныделения и идентификации символа со своего пятого выхода 57 выдает в блок 8 дорожке носителя друг за другомбез промежутков. Всего на дорожкеимеется 2 п + 1 символовВ началеи н конце дорожки записаны нули,поэтому первый единичный бит, расположенный в начале дорожки, является стартовым. Следующие за нимб битов являются информационными,после них записан стартовый бит ии информационных битов и т,д, Поинформационному входу 11 устройства 10в блок 1 и блок 2 синхронизациипоступают временные импульсы, которые запускают блок 2 синхронизации.По этому же входу 11 в промежуткемежду временными импульсами поступают импульсы данных. Наличие импульса после временного бита говорито том, что соответстнующий бит данных равен единице, отсутствие импульса гонорит о том, что соответствующий бит данных ранен нулю.Блок 1 отделяет импульсы данных отвременных. Биты данных поступаютс выхода 67 блока 1 на вход данныхрегистра 3 сднига, На управляющийвход регйстра 3 подается с первоговыхода 35 блока 2 синхронизациисинхросигнал СИ 1, по прохождениикоторого происходит сдвиг информации на одну позицию. Регистр 3 сдвига состоит из Ц + 1 разрядов. В Празрядов вдвигаются биты данных, в(й + 1) -й разряд вдвигается стартовый бит, Наличие единицы н ( и + 1) -мразряде означает то, что в регистре3 сдвига имеется полный символ, 35Первый символ является управляющим. Он содержит адрес дорожки ипризнак последней дорожки массива.Следующие 2 щ символов являются данными,управления днижением головки разрешающий сигнал на сравнение адреса дорожки из счетчика 7 адреса дорожки с адресом дорожки из регист. ра 3 сдвига. В зависимости от результата сравнения блок 8 управления движением головки выдает один иэ сигналов: "Шаг назад", "Шаг вперед", которые поступают соответственно с 17 или 18 выходов устройства в пультовой накопитель, или вырабатывает сигнал сравнения, который с ныхода 51 блока 8 управления движением головки поступает на второй вход блока 5 выделения и идентификации симнола, Выделив символ данных, блок 5 выделения и идентификации символа со своего четвертого выхода 56 выдает сигнал в счетчик б символов на увеличение содержимого счетчика б символов на единицу, со своего третьего выхода 55 ныцает сигнал в регистр 4 данных, разрешающий занесение данных из регистра 3 в регистр 4 данных, и своего шестого выхода выдает на выход 16 устройства строб передачи, который поступает н загружаемый процессор и служит признаком того, что символ данных подготовлен устройством уп-равления загрузкой микропрограмм для передачи в процессор. При этом содержимое регистра 4 данных через выход 14 данных устройства передается н загружаемый процессор.Счетчик б сймволон считает приня" тые символы данных, Он содержит п разрядов. В начальном состоянии содержимое счетчика б символов равно нулю. После приема 2 щ символов данных счетчик б символов снова сбра. сывается в нулевое состояние и вырабатывает сигнал переноса, который поступает в счетчик 7 адреса дорожки для увеличения адреса дорожки на единицу, на первый вход элемента И 10 для разрешения выработки сигнала "Конец передачи", в блок 5 выделения и идентификации символа; для сброса его в исходное состояние. Элемент И 10 вырабатывает сигнал "Конец передачи" при наличии двух условий: установленного триггера 9 и наличия сигнала переноса из счетчика 6 символов. Сигнал с выхода элемента И 10 поступает через выход 15 устройства в загружаемый процессор и сообщает ему, что весь массив микропрограмм передач загружен.Счетчик 7 адреса дорожки служит для указания адреса дорожки, с которой необходимо считывать информацию в данный момент времени. В начале загрузки микропрограмм с входа 13 н счетчик 7 адреса дорожки заносится начальный адрес дорожки, начиная с которого располагается510 65 загружаемый массив микропрограмм. Е дальнейшем содержимое счетчика 7 адреса дорожки увеличивается на единицу сигналом переноса счетчика б символов, поступающим на сче ный вход счетчика 7 адреса дорожки.Блок 2 синхронизации (фиг. 2) работает следующим образом. см. фиг. б;, на которой показана временная диаграмма работы баока 2 синхронизации).В начальный момент времени первый 20 и второй 21 триггеры сброшены, третий триггер 22 установлен, а все разряды счетчика 19 находятся в единичном состоянии, По временному импульсу, поступающему из пультового накопителя через первый вход 11 устройства на вход блока, и по установленному третьему триггеру 22 устанавливается первый триггер 20. По установленному первому триггеру 20 устанавливается второй триггер 21. По установленному второму триггеру 21 и. сигналу с генератора 33 тактовых импульсов, который вырабатывает серию импульсов со скважностью единица, второй элемент И 24 вырабатывает сигнал, который сбрасывает третий триггер 22 и раз. решает увеличение содержимого счет,чика 19 на единицу. По сброшенному третьему триггеру 22 сбрасывается первый триггер.20. Все время, пока установлен второй триггер 21, по сигналам с генератора 33 тактовых импульсов счетчик 19 увеличивает свое содержимое на единицу. По отсутствию сигналов на первом, втором, третьем выходах счетчика 19 и по наличию сигнала на выходе генератора 33 тактовых импульсов четвертый элемент И вырабатывает синхросигнал СИ 1, который через первый выход 35 блока поступает в блок 1 и на вход регистра 3 сдвига. По отсутствию сигналов на втором и треть" ем выходах счетчика 19 и по наличию сигналов на первом выходе счетчика 19 и на выходе генератора 33 такто-. вых иМпулЬсов пятый элемент И вырабатывает синхросигнал СИ 2, который через четвертый выход 38 блока поступает в блок 5 выделения и идентификации символа. По наличию сигналов на первом и втором выхо-. дах счетчика 19 и при отсутствии сигнала на третьем выходе счетчика 19 или при наличии сигнала на третьем выходе счетчика 19 и отсутствию сигнала на втором выходе счетчика 19 шестой 28 и седьмой 29 эле. менты И и элемент.ИЛИ 32 вырабатывают: синхросигнал. СИ 3, который со второго выхода Зб блока поступает в блок 1 и в блок 5 выделения и идентификации символа. По наличию сиг,налов на втором и третьем выходах счетчика 19 и выходе генератора33 тактовых импульсов и по .отсутствию сигнала на первом выходе счет- .чика 19 восьмой элемент И 30 вырабатывает синхросигнал СИ 4, которыйчерез пятый выход 34 блока поступаетв блок 5 выделения и идентификациисимвола. По наличию сигналов напервом, втором и третьем выходахсчетчика 19 и отсутствию сигналана выходе генератора 33 тактовых импульсов девятый элемент И вырабатывает сигнал установки третьеготриггера 22. Установленный третийтриггер 22 выдает через третий вы 15 ход 37 блока синхронизирующий сигнал СИ 5, который поступает вблок 1 и блок 5 выделения и иденти"фикации символа. По единичному состоянию третьего триггера 22, нулевому состоянию первого триггера 20 иотсутствию сигнала с выхода гене-.ратора 33 тактовых импульсов первыйэлемент И 23 вырабатывает сигналсброса второго триггера 21. По нулевому состоянию второго триггера 21и сигналу с выхода генератора 33тактовых импульсов третий элементИ 25 вырабатывает сигнал, которыйустанавливает все разряды счетчика19 в единицу, Одновременно нулевоесостояние второго триггера 21 запрещает выработку сигнала счета вторымэлементом И 24,Блок 5 выделения и идентификациисимвола (Фиг. 3) работает следую 35 щим образом.По заднему Фронту синхросигналаСИ 1 происходит сдвиг информации врегистре 3 сдвига на одну позицию.Наличие единицы в ( и + 1) -ом раз,40 ряде говорит о том, что в регистре3 имеется полный символ. Поэтомупри наличии единицы в ( П + 1) -м разряде регистра 3, поступающей с выхода регистра 3 через пятый вход 5245 блока 5 выделения и идентификациисимвола на 2 -вход первого триггера,по переднему фронту синхросигналаСИ 2, поступающему на шестой вход38 блока, устанавливается первыйтриггер 40, Первый символ являетсяуправляющим. В нем имеется адрестекущей дорожки. В случае совпаденияадреса текущей дорожки с исковым,блок 8 управления движением головкивырабатывает разрешающий сигнал, ко.торый поступает на второй вход 51блока 5 выделения и идентификациисимвола. так как в начальный моментвремени третий триггер 42 находитсяв нулевом состоянии, то на выходе60 первого элемента И 43 имеется единичное состояние и по переднему фронту синхросигнала СИ 3, поступающему на третий вход 36 блока,устанавливается второй триггер 41.По установленнымпервому 40 и вто 1042025 12рому 41 триггерам и по синхросигналу СИ 3 третий элемент И 45 выраба.тывает сигнал занесения управляющего символа, который с третьеговыхода 55 блока 5 выделения и идентификации символа поступает наС-вход триггера 9, разрешая егоустановку при наличии признака последней дорожки в управляющем символе, По установленному второму триггеру 41 и синхросигналу СИ 4,поступающему на седьмой вход 34 блока, устанавливается третий триггер 42.По установленному первому триггеру40 и по синхросигналу СИ 4 пятыйэлемент И 47 вырабатывает сигнал, 15поступающий через первый выход 53блока в блок 1 и регистр 3 для ихсброса.Если блок 8 управления движениемголовки не вырабатывает разрешаю- рОщего сигнала, поступающего на второйвход 51 блока 5 выделения и идентификации символа, второй 41 и третий 42 триггеры не устанавливаются,По сброшенному третьему 42 и второму 41 триггерам элемент ИЛИ-НЕ 39вырабатывает разрешающий сигнал, ипо единичному сигналу с выхода пятого элемента И 47 седьмой элементИ 49 вырабатывает управляющий сигнал, который через пятый выход 57блока 5 выделения и идентификациисимвола поступает на вход разрешения блока 8 управления движениемголовки,По синхросигналу СИ 5, поступаю- З 5щему на четвертый вход 37 блока,первый триггер 40 сбрасывается,Сброшенный первый триггер 41 запрещает выработку ед.;ничного сигналапервым элементом И 43. Поэтому по 4 Опереднему фронту следующего синхросигнала СИ 3, поступающему на третийвход 36 блока, второй триггер 41сбрасывается. При наличии следующей единицы в (и + 11 -м разряде регистра 3 по переднему фронту синхросигнала СИ 2, поступающему на шестой вход 38 блока, первый триггер40 устанавливается вновь. При этомимеющийся в регистре 3 символ является символом данных, Установленныйтретий триггер 42 своим инверснымвыходом запрещает выработку единичного сигнала первым элементом И 43,Поэтому по синхросигналу СИ 3, поступающему на третий вход 36 блока 55второй триггер 41 не установится,По установленным первому 40 и третье.му 42 триггерам и синросигналуСИ 2 второй элемент И 44 вырабатывает сигнал, который через четвер- бОтый выход 56 блока 5 выделения иидентификации символа поступает на.счетный вход счетчика 6 символов,для увеличения его содержимого наединипу, По установленным пеРвому б 5 40 и третьему 42 триггерам и синхросигналу СИ 3 третий элемент И 45вырабатывает сигнал, который черезтретий выход 55 блока и идентификации символа поступает на С-входрегистра 4 данных, разрешая занесение данных из регистра 3 в регистр4 данных, По установленным первому40 и третьему 42 сброшенному второму 41 триггерам и синхросигналуСИ 4 шестой элемент И 48 вырабатыва"ет стробирующий сигнал, который через шестой выход и выход 16 устройства поступает в загружаемый процессор, сообщая ему, что символ данных готов для передачи,Блок 8 управления движением головки (фиг. 4) работает следующимобразом.На вход первого адреса дорожкиблока поступает адрес дорожки изрегистра 3. На вход второго адреса,дорожки блока поступает адрес дорожки из счетчика 7 адреса дорожкиСхема сравнения 58 производит сравнение этих адресов и выдает один изтрех сигналов: "Равно", "Больше","Меньше". В случае равенства адресов единичный сигнал с выхода схемы 58 сравнения через выход 51 блока поступает на второй вход блока5 выделения и идентификации символа.На вход 57 разрешения блока 8 управления движением головки поступаетиз блока 5 выделения и идентификации символа стробирующий сигнал,который в случае несравнения адресов через первый 59 или второй 60элемент И разрешает установку соответственно первого 61 или второго62 триггеров, Сигналы с выходов второго 61 и третьего 62 триггеровсоответственно через выход блока,соединенный с выходом 17 устройст-ва, и через выход блока, соединенныйс выходом 18 устройства, поступаютв пультовый накопитель. По этимсигналам пультовый накопитель перемещает головку соответственно наодну дорожку назад или на однудорожку вперед. На вход "Начало дорожки" блока через вход 12 устройства с пультового накопителя поступает сигнал "Начало дорожки", покоторому сбрасывается первый 61или второй 62 триггер.Блок выделения временных битови битов данных работает следующимобразом.Из пультового накопителя черезвход 11 устройства на первый входблока 1 поступают импульсы данных.Наличие импульса данных в моментвремени СИ 3 говорит о том, чтосоответствукщий бит данных равенединице. Отсутствие импульса данныхв момент временй СИ 3 говорит отом, что соответствующий бит данных равен нулю. При наличии импулГ=са данных и синхросигнала СИ 3,который поступает иэ блока 2 синхронизации на третий вход 36, устанавливается первый триггер 65. Посинхросигналу СИ 5, поступающемуна четвертый вход 37 блока 1 иэ блока 2 синхронизации, состояние первого триггера переписывается вовторой триггер бб. Сигнал с выходавторого триггера 66 через выход 67 1 Опоступает на вход данных регистра 3.По следующему синхросигналу СИ 1состояние второго триггера 66 вдвигается в регистр 3. Одновременнопо синхросигналу СИ 1, поступающему на вход 35, сбрасывается первыйтриггер 65. Когда в регистре 3 накопится полный символ, блок 5 выделения.и идентификация символа выдает напятый вход 53 сигнал сброса,который сбрасывает второй триг:гер 66. В предлагаемом устройстве сущест. венно упрощается алгоритм связи с процессором, а также блок управле" ния пультовым накопителем. За счет изменения работы блока синхронизации изменения формата записей на магнитном носителе, .в результате которого изменяется принцип выделения и идентификации символа, добиваются экономии об(Я,-удования. За счет изменения алгоритма связи с процессором сокращается количество шин между процессором и устройством загрузки микропрограмм, а также упрощается оборудование, определяющее момент окончания загрузки микропрограмм.Благодаря сокращенному объему оборудонания предлагаемое устройство потребляет меньше электроэнергии, занимает меньше площади, обладает большей надежностью, требует меньше времени на обслуживанЩ

СмотретьЗаявка

3409698, 16.03.1982

ПРЕДПРИЯТИЕ ПЯ М-5339

ВАЙЗМАН АЛЕКСАНДР ЯКОВЛЕВИЧ, ГУЩЕНСКОВ БОРИС НИКОЛАЕВИЧ, ЕРМОЛОВИЧ ГАЛИНА АЛЕКСАНДРОВНА

МПК / Метки

МПК: G06F 13/04

Метки: загрузкой, микропрограмм

Опубликовано: 15.09.1983

Код ссылки

<a href="https://patents.su/12-1042025-ustrojjstvo-upravleniya-zagruzkojj-mikroprogramm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления загрузкой микропрограмм</a>

Предыдущий патент: Многоканальное резервированное устройство

Следующий патент: Процессор микро-эвм

Случайный патент: Способ контроля содержания капролактама в свежесформованной нити