Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1725224

Авторы: Грездов, Космач, Лещенко, Лобок, Логвиненко

Текст

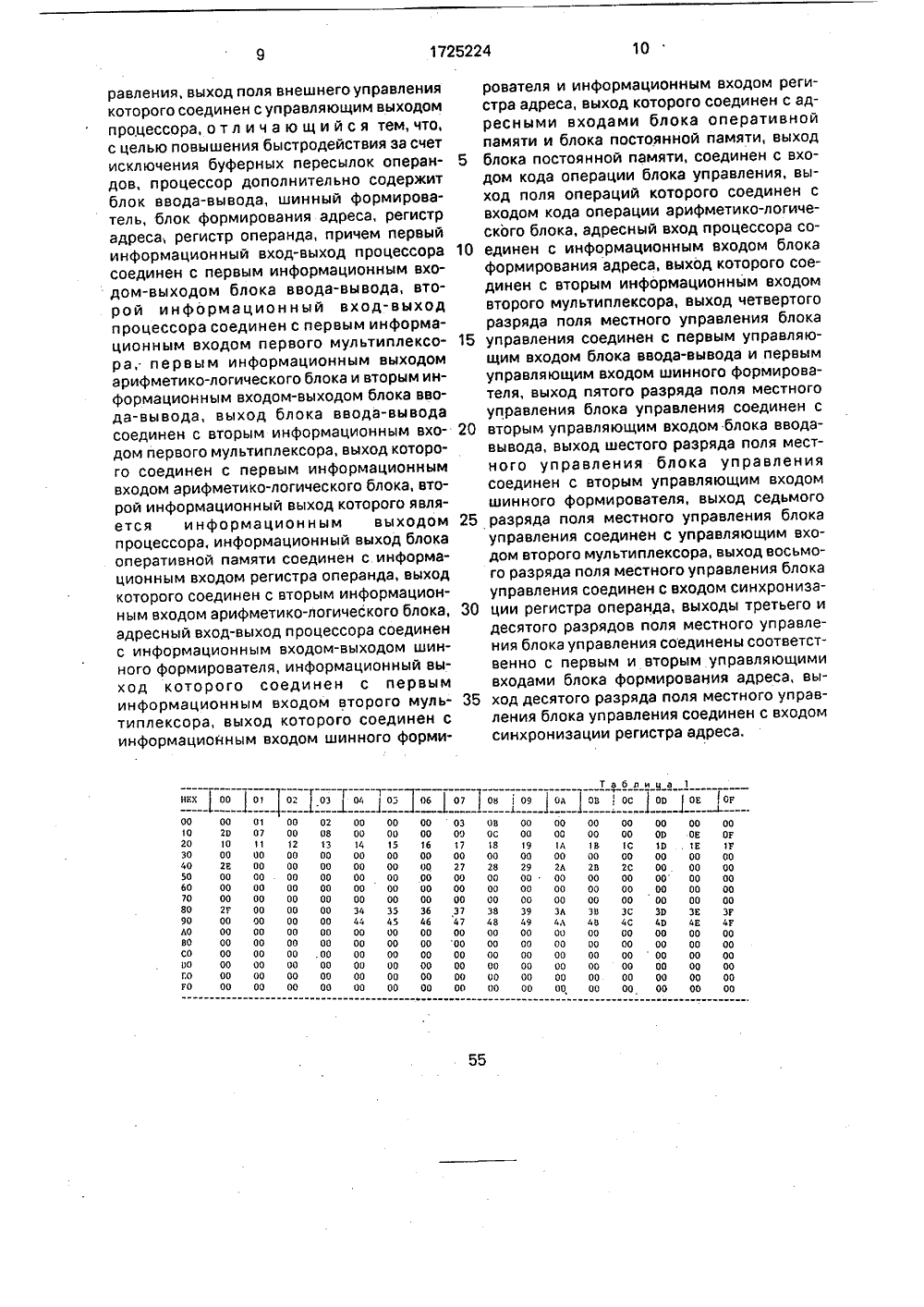

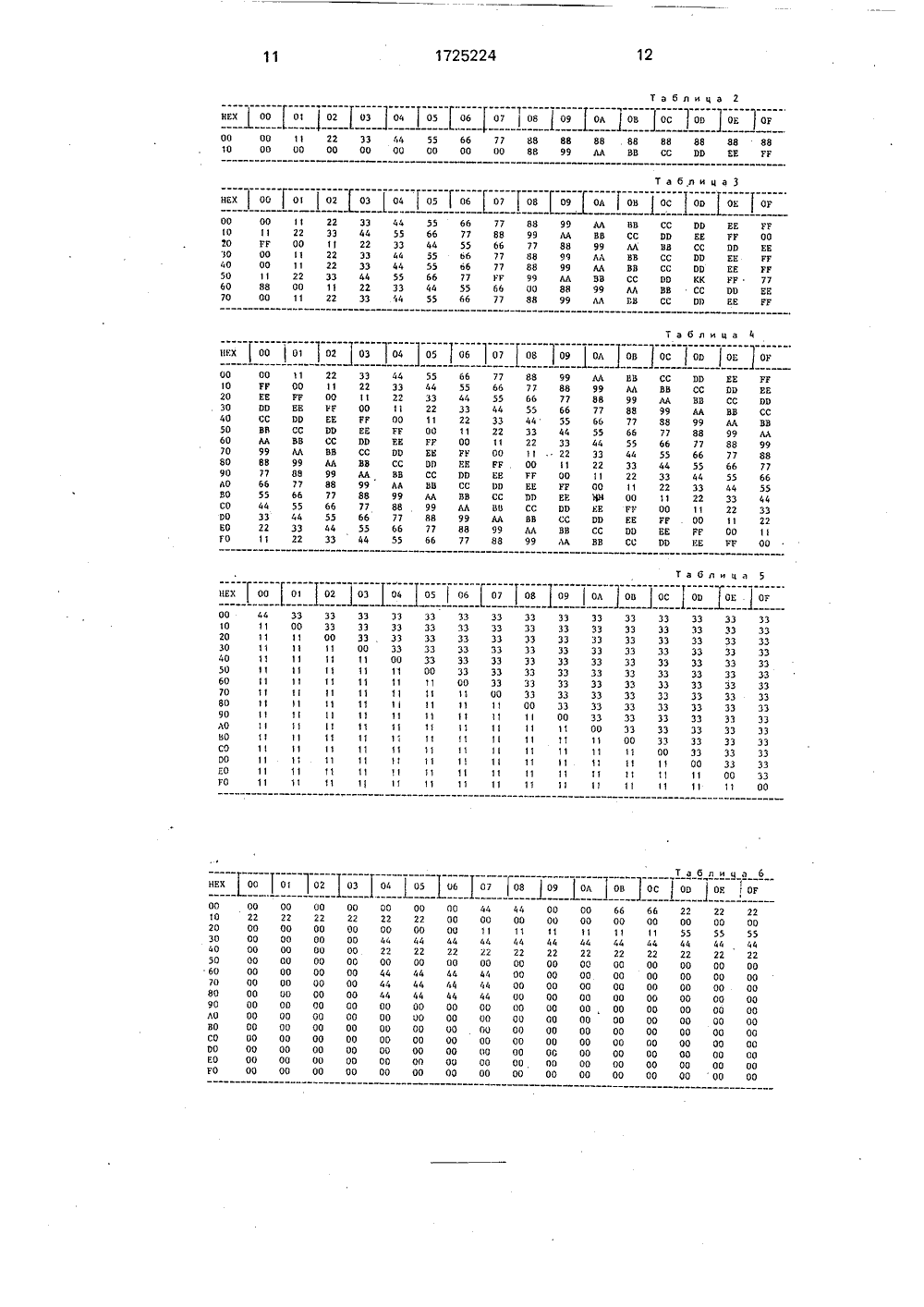

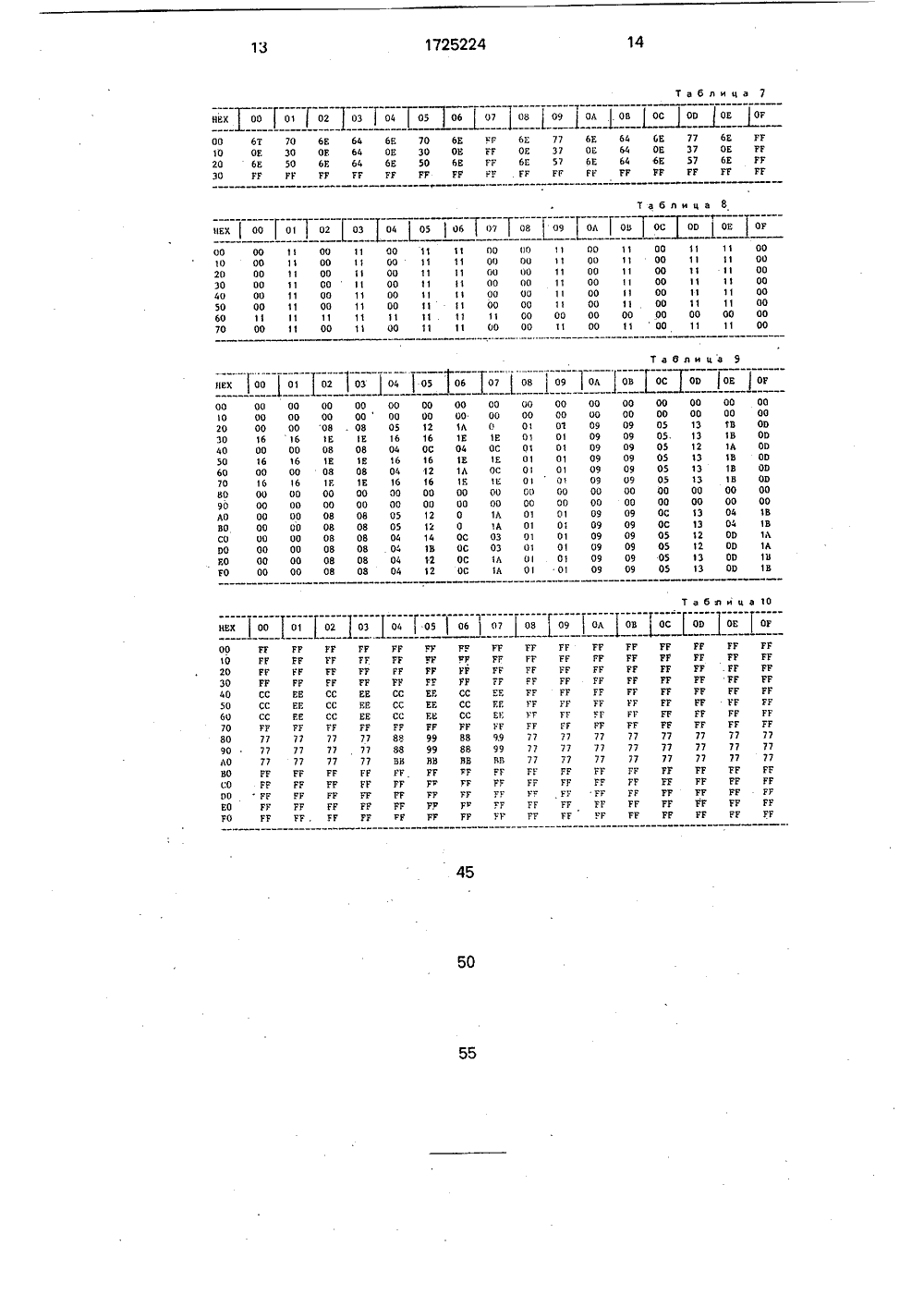

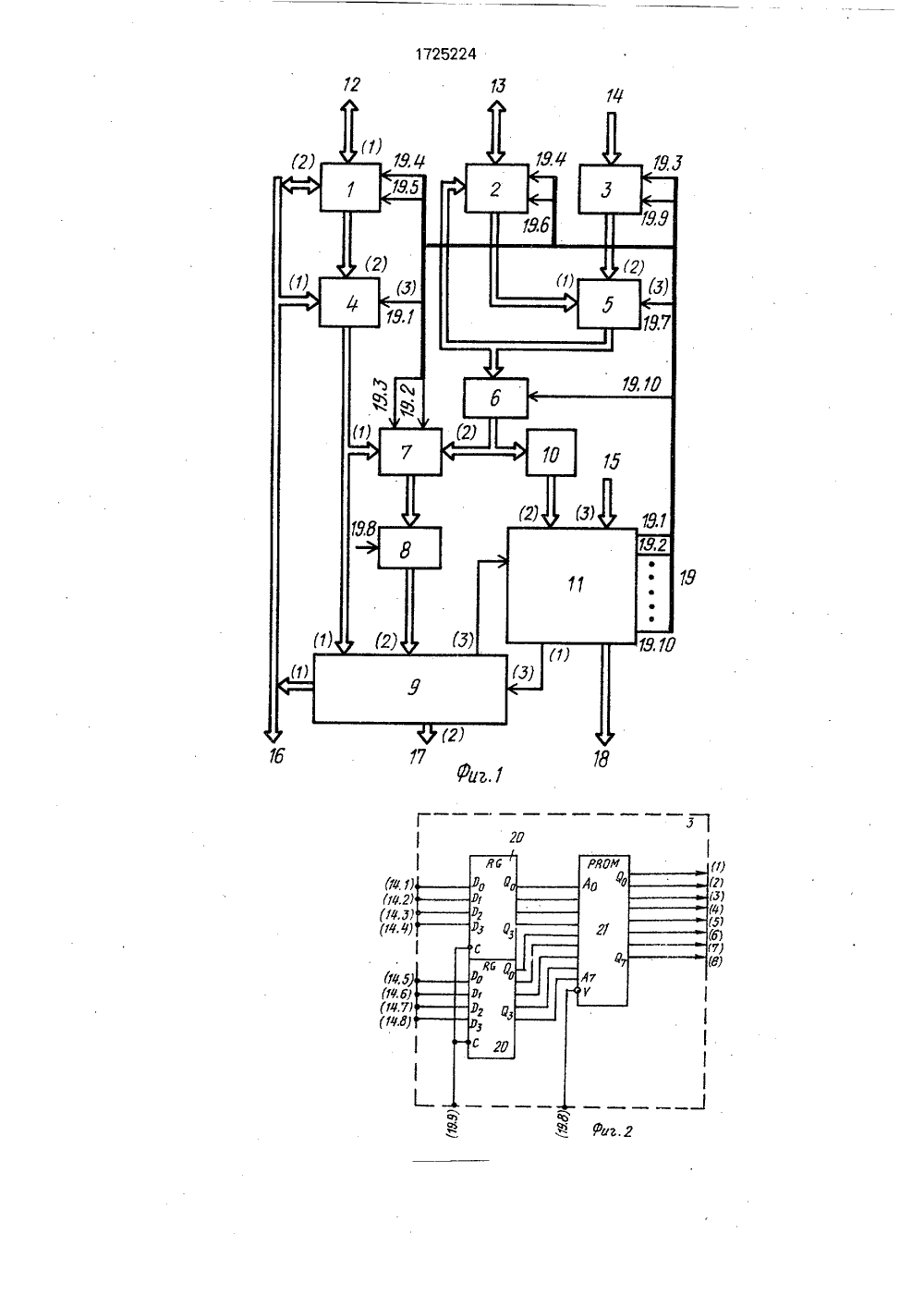

(51) ТЕНИ тел ьноидля об 1 Я ЬЭ иИзобр ной техни обработки быть испо лизирова большого ния динам ления, а работающ Наибо жет быть дчислитель- ссорам для ии, и может нии специаных систем оделировастем управых систем, о времени. эффет моовании прони,ро- перная схема ока формима реализаблока; на а управлеГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР ПИСАНИЕ ИЗО ТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Институт проблем моделирования в энергетике АН УССР(56) Грездов Г,ИКосмач Ю.ПЛогвиненко Ю.П, Модульная организация вычислений в гибридных имитационных моделях. - Электронное моделирование, 1979, М 1, Киев; Наукова думка, с.75 - 80.Авторское свидетельство СССР М 1198532, кл. 0 06 Р 15/00, 1985.Авторское свидетельство СССР М 1352498, кл. 0 06 Р 15/00, 1987.Авторское свидетельство СССР М 1462339, кл, 6 06 Р 15/00, 1989.(57) Устройство относится к вычислтехнике, в частности к процессор етение относится к вь ке, в частности к проце цифровой информац льзовано при пастрое ных многопроцессор быстродействия для м ических объектов и си также измерительн их в режиме реальног льший экономический остигнут при использ работки цифровой информации, и может быть использовано при построении специализированных многопроцессорных систем большого быстродействия для моделирования динамических объектов и систем управления в алигативных вычислительных системах, а также в измерительных системах, работающих в режиме реального времени, Процессор имеет три основных режима функционирования и позволяет обрабатывать операнды, представленные в форме с фиксированной или плавающей точкой, которые изменяю ся в процессе решения динамической зад и. Целью изобретения является повышен е быстродействия за счет исключения буферных пересылок операндов. Процессор содержит первый и второй мультиплексоры, блоки оперативной и постоянной памяти, блок управления, арифметико-логический блок, блок формирования адреса, блок напряжения, шинный формирователь, регистры адреса и операнда, 6 ил 10 табл. цессора в составе алигативной вычис тельной системы при решении задач ди мики объекта в режиме реального времеЦель изобретения - повышение быст действия за счет исключения буферных ресылок операндов,На фиг,1 изображена структу процессора; на фиг,2 - схема бл рования адреса; на фиг.3 - схе ции арифметико-логического фиг.4 - схема реализации блок1725224 1) (2) (Ю) 35 орректор Э.Лончаков озо риз дакт каз 1177 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 Сост Техр итель С.СошкМ,Моргенталния; на фиг,5 - временная диаграмма синхроимпульсов; на фиг.6 - схема реализацииблока ввода-вывода. Процессор (фиг,1) содержит блок 1 ввода-вывода, шинный формирователь 2, блок 3 формирования адреса, первый 4 и второй 5 мультиплексоры, регистр 6 адреса, блок 7 оперативной памяти, регистр 8 операнда, арифметико-логический блок (АЛБ) 9, блок 10 постоянной памяти, блок 11 управления, первый информационный вход-выход 12, адресный вход-выход 13, адресный вход 14, вход 15 режима и синхронизации, второй информационный вход-выход 16, информационный выход 17, выход 18 поля внешнего управления, выход 19 поля местного управления. Цифрами в скобках (фиг,1) обозначены порядковые номера входов и выходов блоков.Блок 3 формирования адреса (фиг.2) предназначен для обеспечения приема адреса переноса из аналоговой части алигативной вычислительной системы и преобразования в адрес обрабатываемого операнда и содержит регистры 20, память 21, пример программирования которой приведен в табл.1. Нагрузочные резисторы на схеме и далее не показаны.Арифметика-логический блок 9 (фиг.3) содержит элементы 22 - 25 памяти, и-разрядный сумматор.26 по модулю 2, элемент ИЛИ 27, элемент И - НЕ 28.Программирование элемента 22 осуществляется в соответствии с табл.2, карта программирования элемента 23 памяти приведена в табл.3; карта программирования элемента 24 памяти - в табл,4; программирование элемента 25 памяти осуществляется согласно табл,5.Блок 11 управления (фиг.4) содержит элементы 29 - 31 памяти, программирование которых осуществляется согласно табл.7 - 9 соответственно, элемент 32 памяти, программирование которого осуществляется согласно табл,10, О-триггер 33.На фиг.5 приведена временная диаграмма синхроимпульсов, поступающих на вход 15 режима работы и синхронизации: т 1 - на вход 15.5;г 2 - на вход 15,6;гз - на вход 15,7. На остальные входы поступают асинхронные сигналы режимов работы; на вход 15.1 - сигнал "Запись", на вход 15.2 - сигнал "Обработка", на вход 15.3 - сигнал "Чтение", на вход 15,4 - сигнал "Знак переноса".Блок 1 вводэ-вывода (фиг,6) содержит магистральные приемопередатчики 34 - 37 и инвертор 38.Процессор работает в трех основных режимах: ввода, обработки и вывода, а также может находиться в режиме ожидания.Работа процессора осуществляется сле дующим образом.Режим ввода устанавливается в исходном состоянии алигативной вычислительной системы для задания нулевых или начальных значений операндов. Этот ре жим имеет высший приоритет и предусматривает задание или смену любого операнда Х, поступающего на адресный и информационный входы-выходы процессора с общих шин АВС.15 При режиме ввода осуществляется замена хранящейся в блоке памяти информации об операнде с фиксированной точкой Хф,=(мф,) Хф =(Мф),20 и с плавающей точкой ФХ,=(Р,М ) Х =(РМ),25где Мф, М - соответственно мантиссы операнда с фиксированной и плавающей точкой,Рн - порядок операнда с плавающей30 точкой,а также осуществляется вычисление приращения порядка ЛР = Рн - Рно35 Новое значение операнда и вычисленное значение приращения порядка выдается для дальнейшего использования в гибридную часть АВС одновременно с уп равляющими сигналами.Режим ввода процессора устанавливается подачей сигнала низкого уровня ("Запись") на вход 15,1 режима работы и синхронизации. При этом в блоке 11 управ ления элементом 29- памяти (фиг.4, табл.7)формируются управляющие сигналы на выходе, а также на О-триггере 33 по приходу синхроимпульса х 1 устанавливается сигнал "Процссор занят", поступающий на выход 50 (18.1) поля внешнего управления.По управляющим сигналам (19.4, 19,5)поля 19 местного управления блок 1 устанавливается на передачу информации с второго входа-выхода на первый, Первый 55 мультиплексор 4 передает информацию свторого входа на выход. Таким образом 16- тиразрядное значение операнда поступает на информационные входы (1) блока 7 оперативной памяти, блока 9 и без измененийпоступает на второй информационный вход-выход 16 процессора.Шинный формирователь 2 устанавливается на передачу с входа-выхода (2) на выход, а второй мультиплексор 5 по сигналам поля местного управления включен на передачу с первого входа на выход. При этом адрес операнда поступает с адресного входа-выхода 13 процессора на вход регистра 6 адреса и фиксируется на период обработки по управляющему сигналу поля местного управления (19.10) при высоком уровне импульса т. По установленному адресу на адресном входе (2) блока 7 оперативной памяти, прежнее значение операнда (по гг ) заносится в регистр 8 операнда. Затем осуществляется запись нового значения, установленного на информационном (1) входе операнда в блоке оперативной памяти.Блок 10 постоянной памяти по установленному на входе адресу анализирует тип операнда и выдает соответствующую команду на вход (2) блока 11 управления. Арифметика-логический блок 9 (фиг.3), сравнивая поступившие на первый информационный вход новое значение и зафиксированное на втором информационном входе старое значение порядка, вычисляет на элементах 24 и 25 величину его изменения и выдает на информационный выход 17 приращения порядка. Одновременно с выдачей информации блокуправления формирует на управляющих выходах поля внешнего управления 18 следующие сигналы; 18.2 - Ь - управляющий сигнал, который выдается синхронно с выдачей приращения порядка операнда; 18,3 - В, - "Знак приращения порядка", 18,4 - д - управляющий сигнал, который выдается синхроннос выдачей порядка операнда; 18.5 - х - управляющий сигнал, который выдается синхронно с выдачей информации о мантиссе операнда,Режим обработки процессора является основным рабочим режимом и предназначен для преобразования цифровой части с учетом переноса из аналоговой части операндов алигативного типа, которые непрерывно изменяются при решении задачи алигативной вычислительной системой в масштабе реального времени.На адресный вход 14 процессора поступает адрес (номер) запрашивающего устройства, который по управляющим сигналам (управляющие входы 19.3 и 19.9) фиксируется по заднему фронту на период обработки на регистрах 20 блока формирования адреса 3 (фиг.2). Режим обработки10 устанавливается подачей сигнала низкого уровня "Обработка" на вход (15.2) режимаработы и синхронизации. После этого блок 11 управления (фиг,4) формирует сигнал на выходе 0-триггера 33 "Процессор занят", который поступает на выход (18.1) поля внешнего управления.Элементом 29 памяти (фиг.4) в соответствии с табл.7 вырабатываются управляющие сигналы, по которым блок 1 и шинный формирователь 2 отключаются соответственно от информационной и адресной шин системы. Сигналы, поступающие на управляющие(3) входы мультиплексора, переклюплексора,Зафиксированному номеру запрашиваемой памяти 21 (фиг.2) согласно табл,1 ставится в соответствие адрес требующего обработки операнда. Этот адрес поступает на регистр 6 адреса и устанавливается на период обработки на адресном (2) входе блока 7 оперативной памяти и входе блока 10 постоянной памяти. Затем происходит считывание с блока оперативной памяти прежнего значения операнда, занесение его (по т 2) в регистр операнда 8 и установка на втором информационном входе арифметико-логического блока 9 для преобразования.В блоке 10 постоянной памяти в соответствии с записанной в ППЗУ программой (табл,6) определяется тип операнда и необходимость выдачи его нового значения на общие шины вычислительной системы и выдается соответствующая команда в блок 11 управления. На элементах 30-32 памяти (фиг.4) анализируются: информация о знаке переноса, поступающая на вход (15.4) процессора, значение старших разрядов мантиссы и порядка, а также знаковые разряды мантиссы и приращения порядка, после чего на первый выход блока управления, а следовательно, и на управляющий вход (3) АЛБ 9 поступают соответствующие сигналы, По этим сигналам в АЛБ элементом 22 памяти (фиг.3) и сумматором 26 осуществляется преобразование мантиссы, а элементом 23 памяти - порядка операнда. Одновременно элементом 25 памяти осуществляется вычисление приращения порядка операнда.Если тип операнда - с фиксированной точкой, то на элементах 22, 26 и 23 АЛБ по командам с блока 11 управления происходит вычисление 16-разрядного значения операнда, причем на элементе 22 вычисля 20 25 30 35 40 45 5055 15 чают их на передачу информации от первоговхода на выход первого 4 мультиплексора и от второго входа на выход второго 5 мульти 172522440 45 50 55 ются младшие разряды операнда, а на элементе 23 - вычисляются старшие разряды, Новое значение операнда поступает на второй информационный вход-выход 16 процессора, а также поступает на информационный вход (1) блока оперативной памяти.Если новое значение операнда необходимо сразу же выдать на общие шины алигативной вычислительной системы, то в соответствии с поступающей на вход кода операции блока управления командой на элементе 29 памяти (фиг.4) формируются сигналы, поступающие на поле местногоуправления, По этим сигналам блок 1 и шинный формирователь 2 включаются на передачу информации с первого входа на второй вход-выход. При этом адрес операнда с блока 3 формирования адреса через второй мультиплексор 5 и шинный формирователь поступает на адресный вход-выход 13 процессора,Новое значение операнда поступает через блок 1 на первый информационный вход-выход 12 процессора. По тактирующему сигналу хз происходит выдача управляющих сигналов на выходы поля внешнего управления 18 процессора, а также производится запись нового значения операнда на место его прежнего значения в блоке 7 оперативной памяти. В дальнейшем при отсутствии сигнала запроса на обработку следующим т снимается сигнал "Процессор занят", и процессор переходит в режим ожидания.Для преобразования операндов неалигативного типа одновременной подачей сигналов "Запись" и "Обработка" на вход 15 режима работы и синхронизации может устанавливаться режим, при котором поступающий с общих шин вычислительной системы операнд перед записью в блок оперативной памяти и выдачей на выходы 16 и 17 процессора преобразуется в блоке 9 аналогично режиму обработки. Тип обрабатываемых операндов, а также виды их преобразования легко изменить без изменения структуры процессора, а лишь перепрограммировав соответствующие элементы памяти.Режим вывода имеет низший приоритет и предназначен для вывода любого из операндов для индикации или анализа на общую информационную шину алигативной вычислительной системы, Адрес выводимого операнда устанавливается на адресном входе-выходе 13 процессора, а сигнал низкого уровня "Чтение", задающий режим, поступает на вход 15 процессора. Блок 11 5 10 15 20 25 30 35 управления вырабатывает сигналы, поступающие на поле местного управления, по которым блок 1 ввода-вывода переключается на передачу информации от первого входа-выхода на второй, а следовательно, на выдачу информации на первый информационный вход-выход 12 процессора. Шинный формирователь 2 включен на передачу информации об адресе операнда от второго входа-выхода на вход блока, а второй мультиплексор 5 - на передачу от первого входа на выход,Таким образом, адрес выводимого операнда поступает с адресного входа-выхода 13 процессора на вход регистра 6, запоминается (по т 1 ) на период вывода и устанавливается на адресном входе (2) блока 7 оперативной памяти.С блока 11 управления выдаются сигналы на поле местного управления, по которым хранящаяся информация об операнде считывается с блока оперативной памяти, фиксируется в регистре 8 операнда (по тг ) и поступает на второй информационный вход блока 9. Без преобразования информация поступает на информационный выход АЛБ 9, а следовательно, через первый блок ввода-вывода - на первый информационный вход-выход 12 процессора,В режиме вывода на выходах поля 18 внешнего управления процессора вырабатывается только сигнал "Процессор занят" (18.1, фиг.4), остальные сигналы не вырабатываются. По окончании сигнала "Чтение" передним фронтом сигнала т 1 процессор устанавливается в исходный режим ожидания,Формула изобретения Процессор, содержащий первый и второй мультиплексоры, блок оперативной памяти, блок постоянной памяти, арифметико-логический блок, блок управления, причем выход первого мультиплексора соединен с информационным входом блока оперативной памяти, выход признаков результата арифметико-логического блока соединен с входом логических условий блока управления, выход первого разряда поля местного управления которого соединен с управляющим входом первого мультиплексора, выходы второго и третьего разрядов поля местного управления блока управления соединены соответственно с входами записи-чтения и выборки блока оперативной памяти, вход режима работы и синхронизации процессора соединен с входом кода операции и синхронизации блока уп-4- 4- 100 10 20 30 40 50 60 70 80 90 ЛО ВО СО 00 ГО ГО 00 01 20 07 1 О 11 00 ОО 2 Е 00 00 00 00 00 00 00 2 Г 00 00 00 00 00 00 00 00 00 00 00 00 0000 00 00 02 00 08 12 13 00 0000 00 00 00 00 0000 00 00 00 00 00 00 0000 00 00 .0000 0000 00 00 00 00 00 14 00 00 00 00 00 34 44 00 00 00 00 00 00 00 00 ОО 00 15 16 00 00 00 00 00 00 00 00 00 00 35 36 45 46 00 00 00 ОООО 00 00 00 00 00 00 00 03 ОВ 00 ОС 17 18 00 00 27 28 00 00 00 00 00 00 Э 7 38 47 48 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 19 1 А 00 ОО 29 2 А 00 00 00 00 00 00 39 ЗА 49 4 А 00 00 00 00 00 0000 00 00 00 00 00,00 00 1 В 00 2 В 00 00 00 ЗВ 48 00 00 00 00 00 00 00 00 00 ОР С 1 О 00 00 2 С 00 .00 00 00 00 00 00 ЭС ЗО 4 С 40 00 00 00 00 0000 00 00 00 00 00 00 00 00 ОЕ ОГ 1 Е 1 Г 00 00 00 00 00 00 00 00 00 00 ЗЕ ЗГ 48 4 Г 00 00 00 00 00 00 00 00 00 00 00 00 55 равления, выход поля внешнего управления которого соединен с управляющим выходом процессора, отл ича ющийся тем, что, с целью повышения быстродействия за счет исключения буферных пересылок операн дов, процессор дополнительно содержит блок ввода-вывода, шинный формирователь, блок формирования адреса, регистр адреса, регистр операнда, причем первый информационный вход-выход процессора 10 соединен с первым информационным входом-выходом блока ввода-вывода, второй информационный вход-выход процессора соединен с первым информационным входом первого мультиплексо ра, первым информационным выходом арифметико-логического блока и вторым информационным входом-выходом блока ввода-вывода, выход блока ввода-вывода соединен с вторым информационным вхо дом первого мультиплексора, выход которого соединен с первым информационным входом арифметико-логического блока, второй информационный выход которого является информационным выходом 25 процессора, информационный выход блока оперативной памяти соединен с информационным входом регистра операнда, выход которого соединен с вторым информационным входом арифметико-логического блока, 30 адресный вход-выход процессора соединен с информационным входом-выходом шинного формирователя, информационный выход которого соединен с первым информационным входом второго муль типлексора, выход которого соединен с информационным входом шинного формирователя и информационным входом регистра адреса, выход которого соединен с адресными входами блока оперативной памяти и блока постоянной памяти, выход блока постоянной памяти, соединен с входом кода операции блока управления, выход поля операций которого соединен с входом кода операции арифметико-логического блока, адресный вход процессора соединен с информационным входом блока формирования адреса, выход которого соединен с вторым информационным входом второго мультиплексора, выход четвертого разряда поля местного управления блока управления соединен с первым управляющим входом блока ввода-вывода и первым управляющим входом шинного формирователя, выход пятого разряда поля местного управления блока управления соединен с вторым управляющим входом блока ввода- вывода, выход шестого разряда поля местного управления блока управления соединен с вторым управляющим входом шинного формирователя, выход седьмого разряда поля местного управления блока управления соединен с управляющим входом второго мультиплексора, выход восьмого разряда поля местного управления блока управления соединен с входом синхронизации регистра операнда, выходы третьего и десятого разрядов поля местного управления блока управления соединены соответственно с первым и вторым управляющими входами блока формирования адреса, выход десятого разряда поля местного управления блока управления соединен с входом синхронизации регистра адреса..".1-1100 00 88 99 Лл ВВ ОЕ 00 00 00 88 ГГ 88 ОО 88 ЕЕ бв 4 55 00 00 00 10 00 00 Таб л и НЕХ ОГ 00 10 20 10 40 50 60 70 00 1 22 ЭЗ 44 55 11 22 33 44 55 66 ГГ 0022 33 44 00 11 22 33 44 55 00 11 22 ЗЗ 44 55 11 22 33 44 55 66 88 00 11 22 33 44 00 11 22 33 Лв 4 55 66 77 77 88 55 66 66 77 66 77 77 ГУ 55 66 66 77 99 ЛЛ ВВ ЛА ВВ СС 88 99 ЛЛ 9999 АА ВВ ЛЛ ВВ СС 88 99 ЛЛ 99 ЛЛ ГВ 88 99 77 88 88 99 00 88 СС ОО ВВ СС СС ОО ВВ СС ОО ЕЕ СС ОО ОО КК СС ОО ЕЕ УГ ОО ЕЕ ГГ . ОО ЕЕ ГГ 00 ЕЕ УГ ГГ 77 ЕЕ ГГ блица Т а вв.цвоооз 1 о 1 ов 1 ов 1 о 1 оа 1 о/ов 1 оосовсов ос 1 оо 11 22 00 11 ГГ ОО ЕЕ ГГ ОО ЕЕ СС ОО ВВ СС ЛЛ ВВ 99 АЛ 88 99 77 88 66 77 55 66 44 55 33 44 22 33 ЗЭ 44 22 33 00 11 ГГ 00 КЕ УГ ОО ЕЕ СС РО ВВ СС АА ВВ 99 АА 88 99 77 88 66 77 55 66 44 55 55 6644 55 33 44 22 33 11 22 00 11 ГГ 00 ЕЕ ГУ ОО ЕЕ СС ОО ВВ СС ЛА ВВ 99 ЛЛ 88 99 77 88 66 77 77 88 66 77 55 66 44 55 33 44 22 33 11 22 00 11 ГГ 00 ЕК УУ ОО КЕ СС ОП ВВ СС АА ВВ 99 Лл 88 99 Таблица1- Х оасвоаовоа 1 ооОЛ ОВ НЕХ 33 33 33 33 ЗЗ 33 33 Зз 33 33 33 33 Зз 33 33 33 00 33 33 33 11 00 33 33 11 11 00 ЗЭ 11 11 11 00 1 11 11 1 11 11 11 11 11 1 11 11 1 11 11 11 11 11 11 1 11 11 11 1 1 11 1111 11 11 11 33 ЗЗ 33 ЗЭ 00 ЭЭ 11 00 11 11 11 11 11 111111 11 1 11 1 11 11 11 11 11 11 11 11 11 11 1 33 ЭЗ 33 33 Зз 33 33 ЭЗ ЭЭ 33 33 33 33 33 33 3300 ЗЗ 1 00 1 11 11 11 11 11 11 11 11 11 1 в 11 а 6 Таб лиц П. 22 22 00 00 00 44 00 22 00 00 ОО 44 00 44 00 44 ОО 00 00 00 00 00 00 00 00 00 00 ОО 00 00 05 ОО 22 00 44 22 00 44 44 44 00 00 00 ОО 00 00 00 оа оооа / ов ов 1 овос 1 ооов , оо НЕХ 00 00 0022 22 22 00 00 00 00 00 00 00 00 00 00 00 0000 00 0000 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 100 00 00 00 11 11 44 44 44 22 22 22 00 00 00 44 44 00 44 44 00 44 44 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ОО 00 00 ОО 00 00 00 00 00 00 00 11 111 44 44 44 22 22 22 00 00 00 00 00 00 00 00 00 00 00 00 ОО 00, 00 00 00 00 00 00 00 00 00 00 00 00 00 ОО 00 ОО 00 00 00 00 10 20 30 40 50 60 70 80 90 ЛО ВО СО ОО ЕО ГО 00 1 О 20 30 40 50 60 70 80 90 ЛО ВО СО ОО ЕО УО 00 1 О 20 30 40 50 60 70 80 90 АО ВО СО 00 ЕО УО 00 ГГ ЕЕ ОО СС ВВ АА 99 88 77 66 55 44 33 22 11 44 11 11 11 11 11 11 11 1 1 1 11 1 111 33 00 11 11 1 11 1 11 11 11 11 11 99 88 77 66 55 44 33 22 11 00 ГГ КК ОО СС ВВ ЛА ЛЛ ВВ 99 АЛ 88 99 77 88 66 77 55 66 44 55 33 44 22 33 11 22 00 11 НН 00 КЕ ГУ ОО ЕЕ СС ОО ВВ СС 33 33 ЭЭ Эз 33 33 33 33 33 3333 33 33 33 33 33 33 33 33 33 00 33 11 00 11 11 11 11 11 11 11 1 66 00 11 44 22 00 00 00 00 00 00 00 00 00 00 00 СС ВВ ЛА 99 88 77 66 55 44 33 22 11 00 ГГ КЕ ОО 33 33 33 33 33 33 33 33 33 33 33 33 00 111 11 22 00 55 44 22 00 00 00 00 00 00 00 00 00 00 00 ОО СС ВВ АА 99 88 77 66 55 44 33 22 11 00 ГГ КЕ 33 33 33 33 33 33 33 33 ЗЗ 33 33 33 33 00 11 11 22 00 55 44 22 00 00 00 ОО 00 00 00 00 00 00 00 ЕК ОО СС ВВ АА 99 88 77 66 55 44 Зз 22 11 00 УГ 33 33 33 ЗЗ 33 33 33 33 33 33 33 33 33 ЗЗ 00 11 22 00 55 44 22 00 00 00 00 00 00 00 00 00 00 00 ГГ ЕЕ ОО СС ВВ Лл 99 88 77 66 55 44 33 22 11 00 33 33 33 33 33 33 33 33 33 33 33 33 33 33 33 00( 1 0304050607 6 Б 70 ОЕ 30 6 Е 50 ГР РР 00 10 20 ЭО ЬЕ 64 СЕ 77 6 Е РР ОЕ 64 ОЕ 37 ОЕ РГ 6 Е 64 6 Е 57 6 Е ГР ГГ ГР РР ГГ РГ РГ 6 Е 77 ОЕ 37 6 Е 57 , ГР РГ 64 64 64 УГ 6 Е ОЕ 6 Е РР 6 Е РР ОЕ ГГ 68 Ур ГР РГ Таб ззнкОо 011 02 оз 106 105 06 01 06 109 106 09 ОсОООЕ ОГ 1 11 00 11 11 00 1 11 00 11 11 00 11 11 00 11 11 00 00 00 00 11 11 00 11 00 11 00 11 00 1 00 1 00 11 00 00 00 1100 11 00 ОО 11 00 11 00 00 1 00 11 00 00 11 00 11 00 00 11 00 11 00 00 11 00 11 00 00 1 00 1 11 00 00 00 11 00 00 11 00 00 11 0011 00 11 00 11 00 11 00 11 11 11 00 11 00 11 00 11 00 1 0011 00 11 00 11 11 11 00 11 00 00 11 1 О 00 11 20 00 11 ЗО 00 11 40 00 11 50 00 11 60 11 1 70 00 11 Т а б л и ц а 9 нккВо 1 01 1 02 1 оз 1 066506 Оз00 / 09 1 06 1 ОВ Ос 00 (ОЕ ( 09 00 0000 00О 01 Е 01ОС 011 Е 01ОС 01К 0100 0000 001 Л 011 А 0103 01ОЗ 01Л 011 А 0 00 00 00 00 00 00 16 16 00 00 16 16 00 00 16 1 Ь 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 Таблица 10 нек Щ оо 1 01 1 02 1 оз 1 66оз06 ц 01 1 ое 1 09 1 оз 1 ов 1 осов 1 он 1 09 00 ГГ 1 О ГГ 20 РГ 30 ГГ 40 СС 50 СС 60 СС 70 УГ 80 77 90 77 ЛО 77 ВО РР СО ГР 00ГР ЕО ГУ УО Рр РГ РГ ГР РГ РР ГР РР .РГ РР РР РГ ГР РР РГ ГГ РР УР РГ ГР ГР ГГ РГ РГ ГР 77 77 77 77 77 77 77 77 77 РР РГ РР РР РР РР РР РР ГУ РГ РР РР ГР РР РГ РР УР РГ ГГРГ РГ ГР ГГРР ГР ГГ 1 ОГУР ГГ ГГ ГРСС ЕЕ РР РРСС ЕЕ ГГ ГРСС ЕЕ УУ УУУР ГГ УУ Гр88 99 77 7788 99 77 77ВВ ВВ 77 77УР РГ ГГ ГРУУУУ УУ УУ ГУУУ УУ УУРР УУ ГГ УГ РР ГР РГ ГГ ГГ ГР ГР РГ ЕЕ СС ЕЕ СС ЕЕ СС УУ УУ 77 77 77 77 77 77 ГГ РГ ГГ ГГ ГГ РР РР РР УР . РР 45 50 55 00 0 20 30 40 50 60 70 80 90 АО ВО СО ОО ЕО РО 00 00 08 1 Е 08 1 Е 08 1 Е 00 00 08 08 08 08 08 08 00 00 08 1 Е 08 1 Е 08 1 Е 00 00 08 08 08 08 08 08 ГР УУ РР РР ЕЕ ЕЕ ЕЕ ГР 77 77 77 ГГ ГГ ГР РР 00 00 00 ОО 05 12 16 16 04 ОС 16 16 04 12 16 16 00 00 00 00 05 12 05 12 04 14 , 04 1 В 04 12 04 12 УР РУ РГ РР РГ Рр РГ РР СС ЕЕ СС ЕЕ СС ЕЕ ГР Рр88 99 88 99 ВВ ВВ ГР РГ Гр УУ ГР РР РР УР УР РУ 00 00 1 Л 1 Е 04 1 Е 1 Л 1 Б 00 ОО 0 0 ОС ОС ОС ОС 00 00 00 00 09 05 09 05 09 05 09 05 09 05 09 05 00 00 00 00 09 ОС 09 ОС 09 05 09 05 09 05 09 05 РР РР РР ГР РР РР РГ РР РР ГР ГГ Рр УГ ГУ РГ УГ ГГ РР РР РР РГ 77 77 77 77 77 77 77 77 77 РГ ГР РГ РР РР ГР РУ РУ РР РГ ГГ РР РУ РГ РГ 00 00 00 00 13 В 13 18 12 1 А 13 1 В 13 18 13 18 00 00 00 00 13 04 1 Э 04 12 ОО 12 ОО 13 ОО 13 ОО 00 00 ОО ОО 00 ОО 00 ОО 00 00 18 18 1 А 1 А 1 В 1 В

СмотретьЗаявка

4756589, 04.11.1989

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ГРЕЗДОВ ГЕННАДИЙ ИВАНОВИЧ, КОСМАЧ ЮЛИЙ ПЕТРОВИЧ, ЛОГВИНЕНКО ЮРИЙ ПАВЛОВИЧ, ЛОБОК ГЕОРГИЙ АЛЕКСАНДРОВИЧ, ЛЕЩЕНКО НИКОЛАЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 15/78

Метки: процессор

Опубликовано: 07.04.1992

Код ссылки

<a href="https://patents.su/11-1725224-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Устройство для сопряжения двух магистралей

Следующий патент: Устройство для моделирования системы связи

Случайный патент: Устройство для передачи изделий