Программируемый управляющий модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

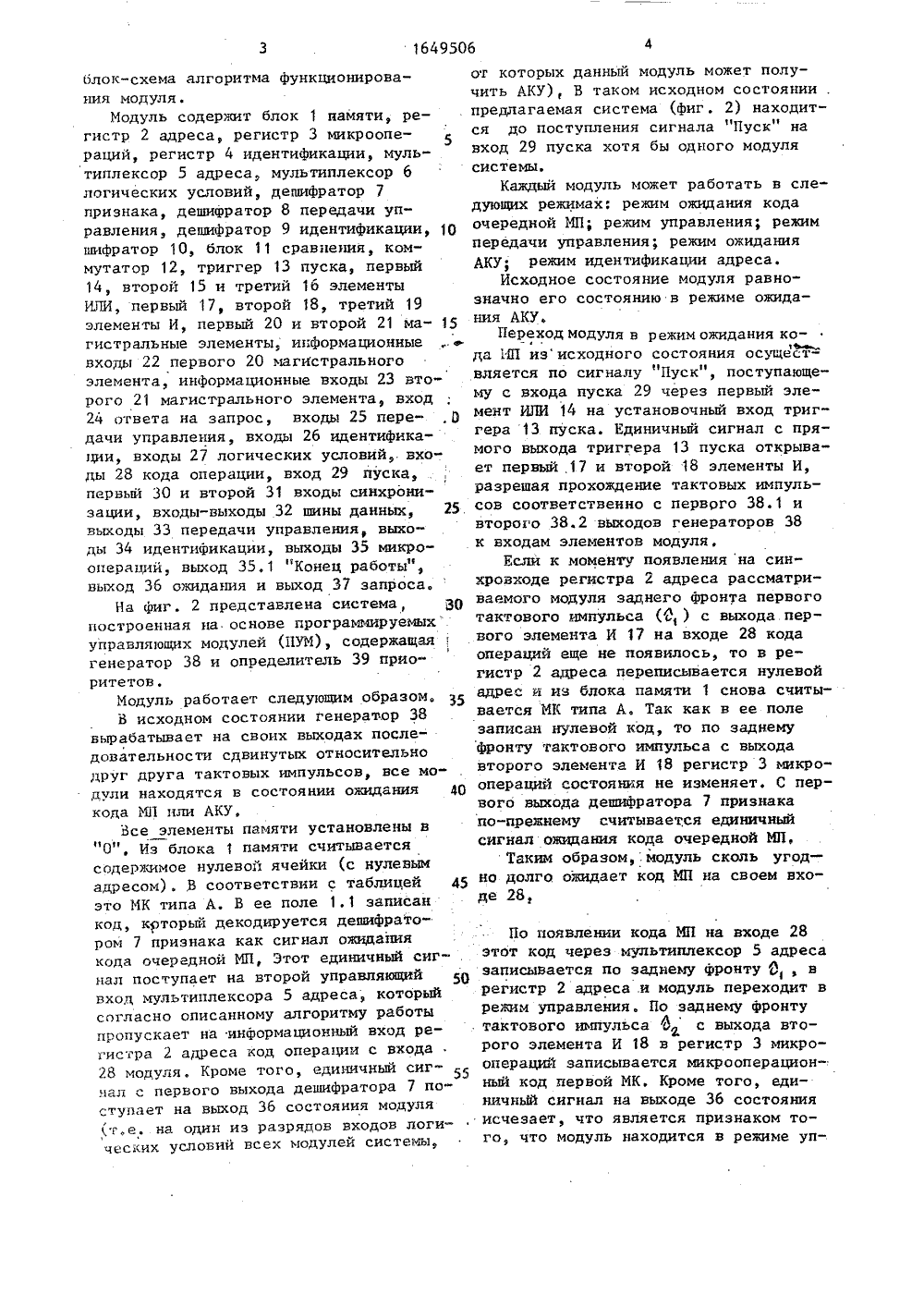

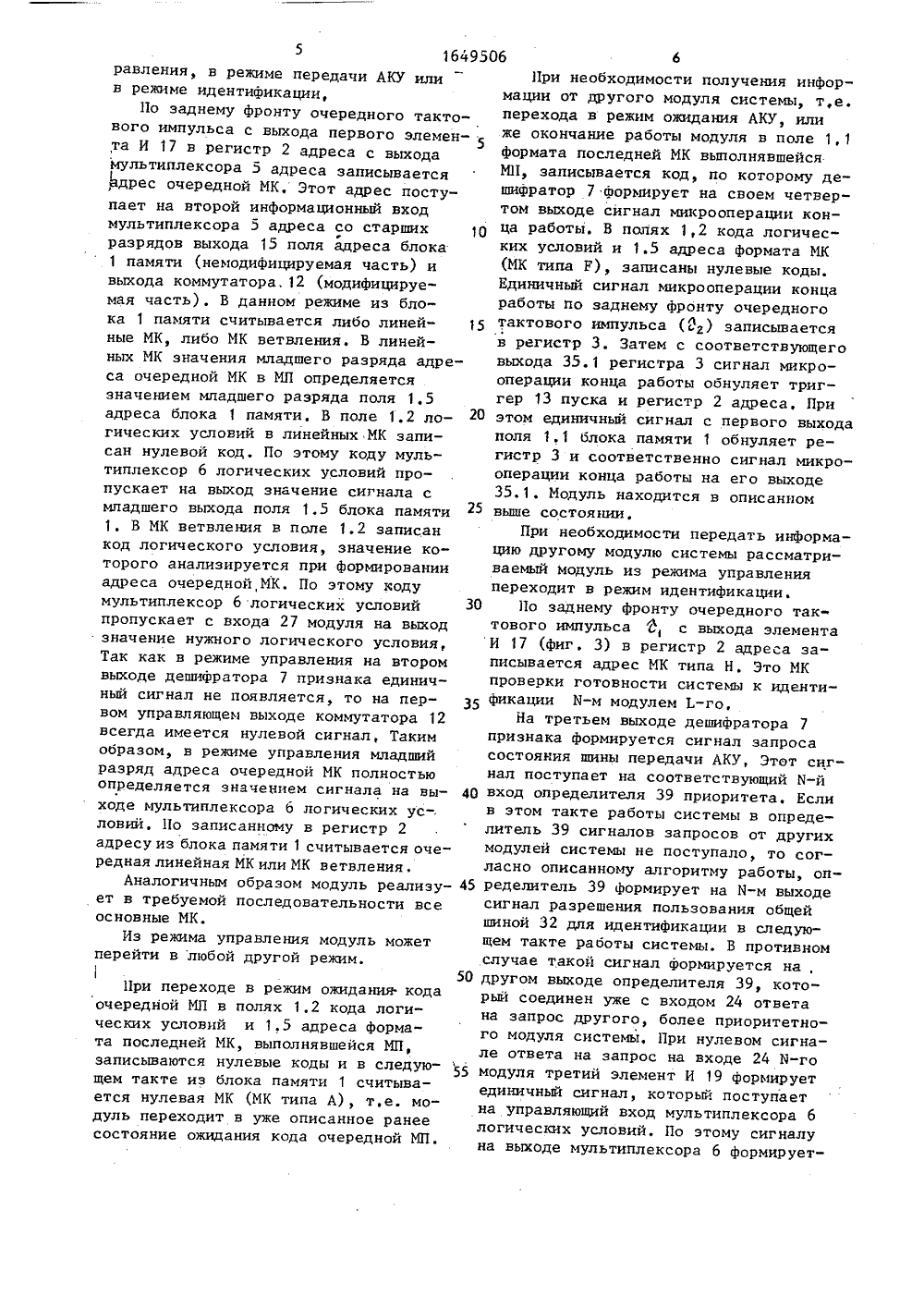

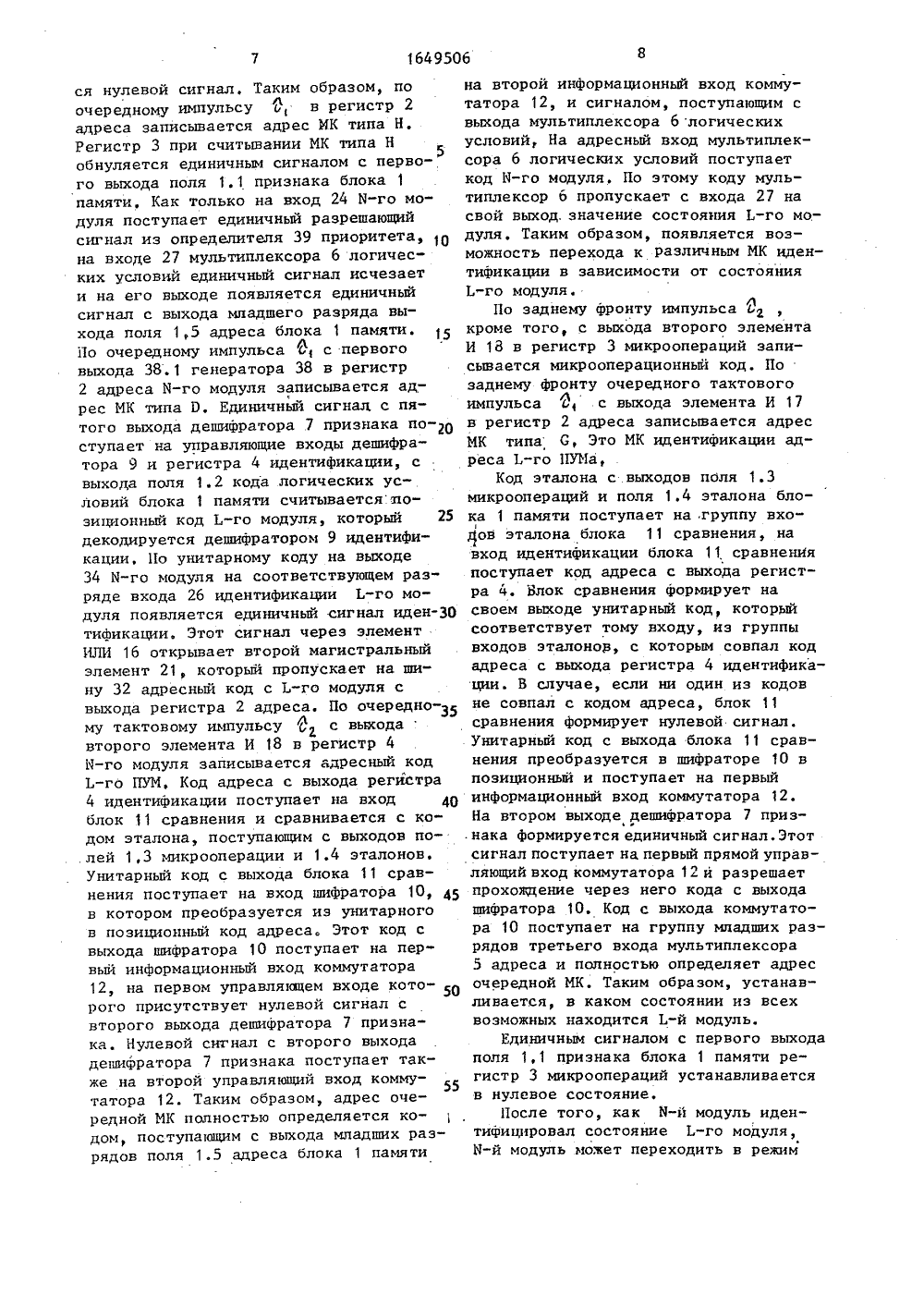

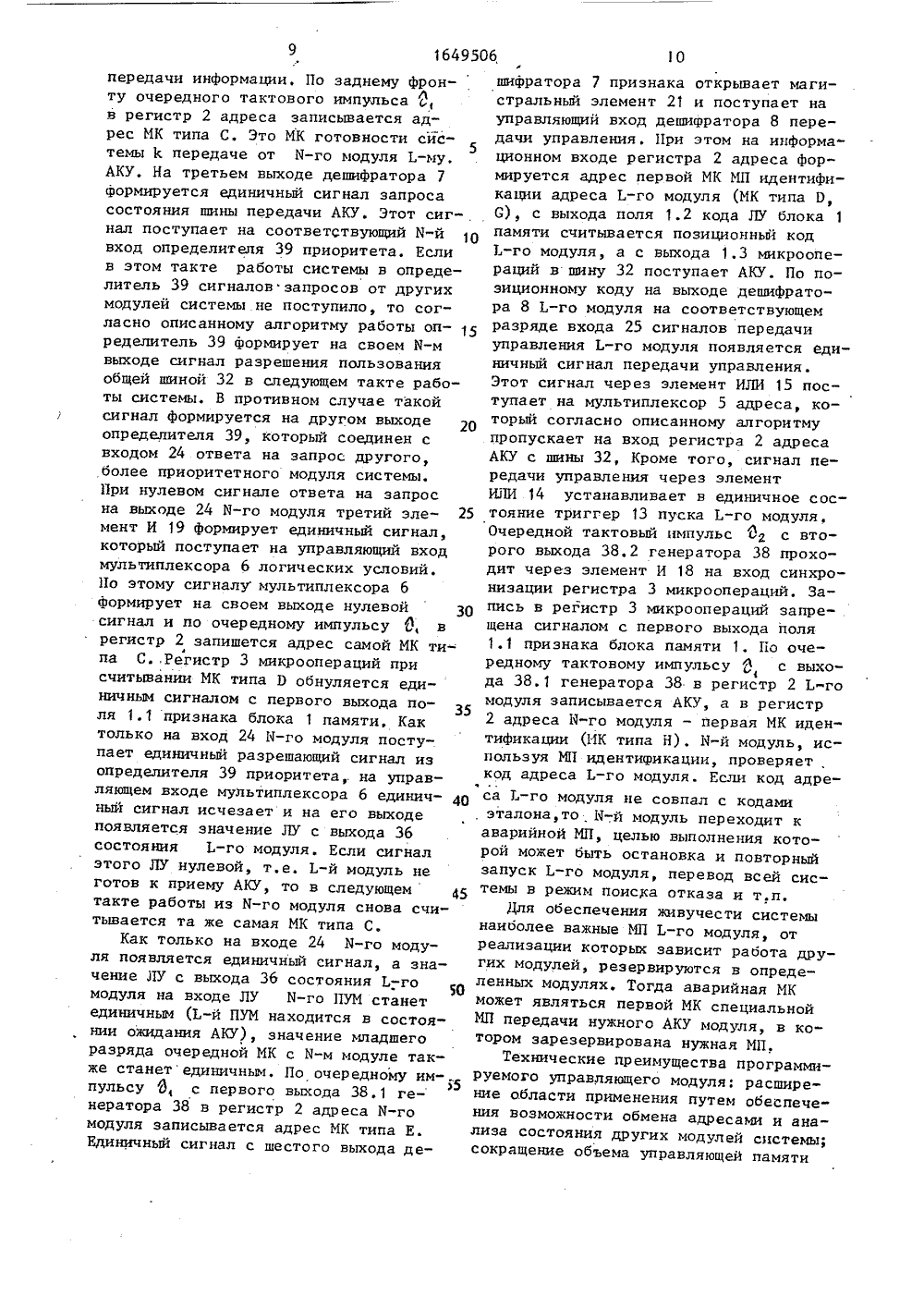

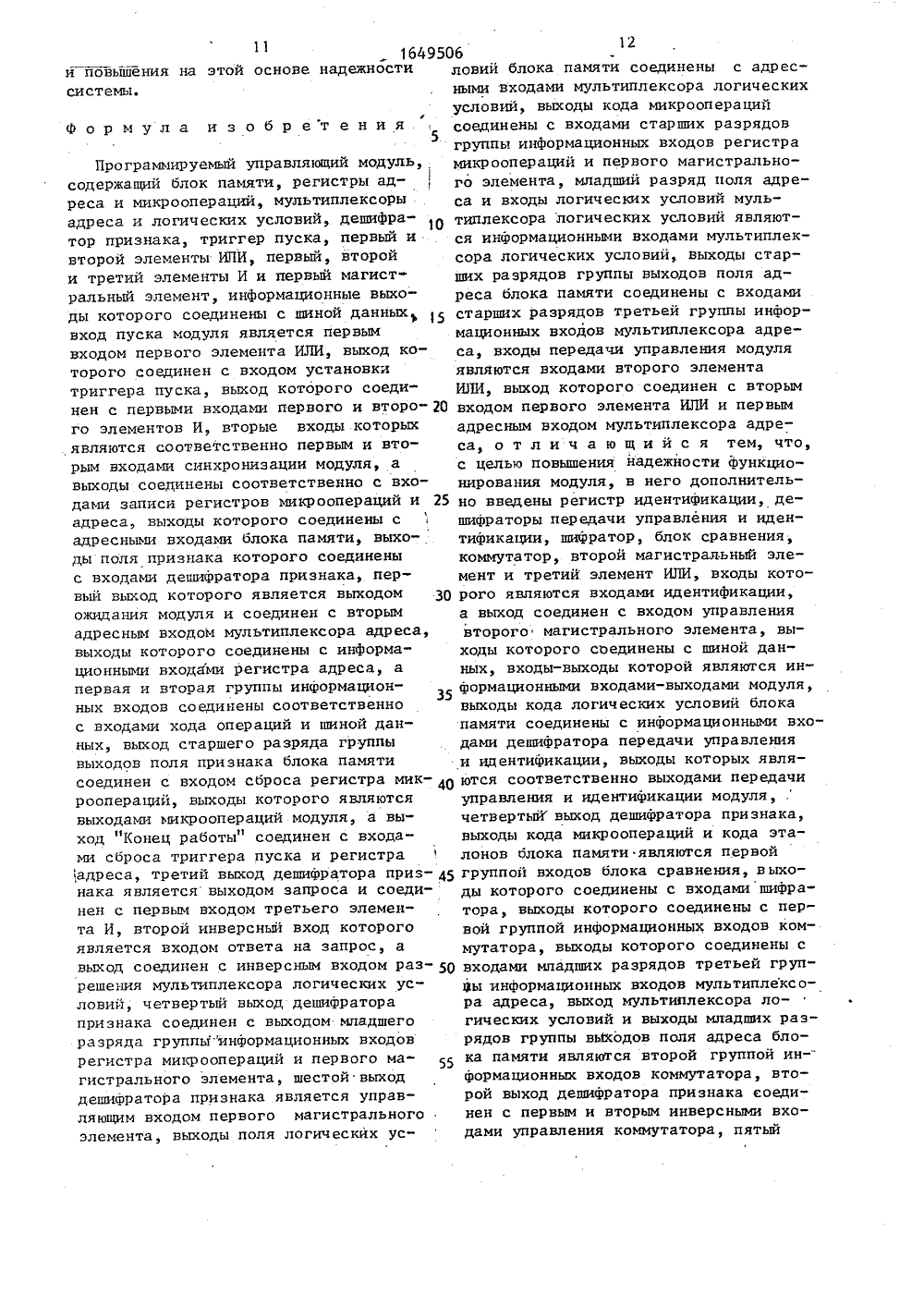

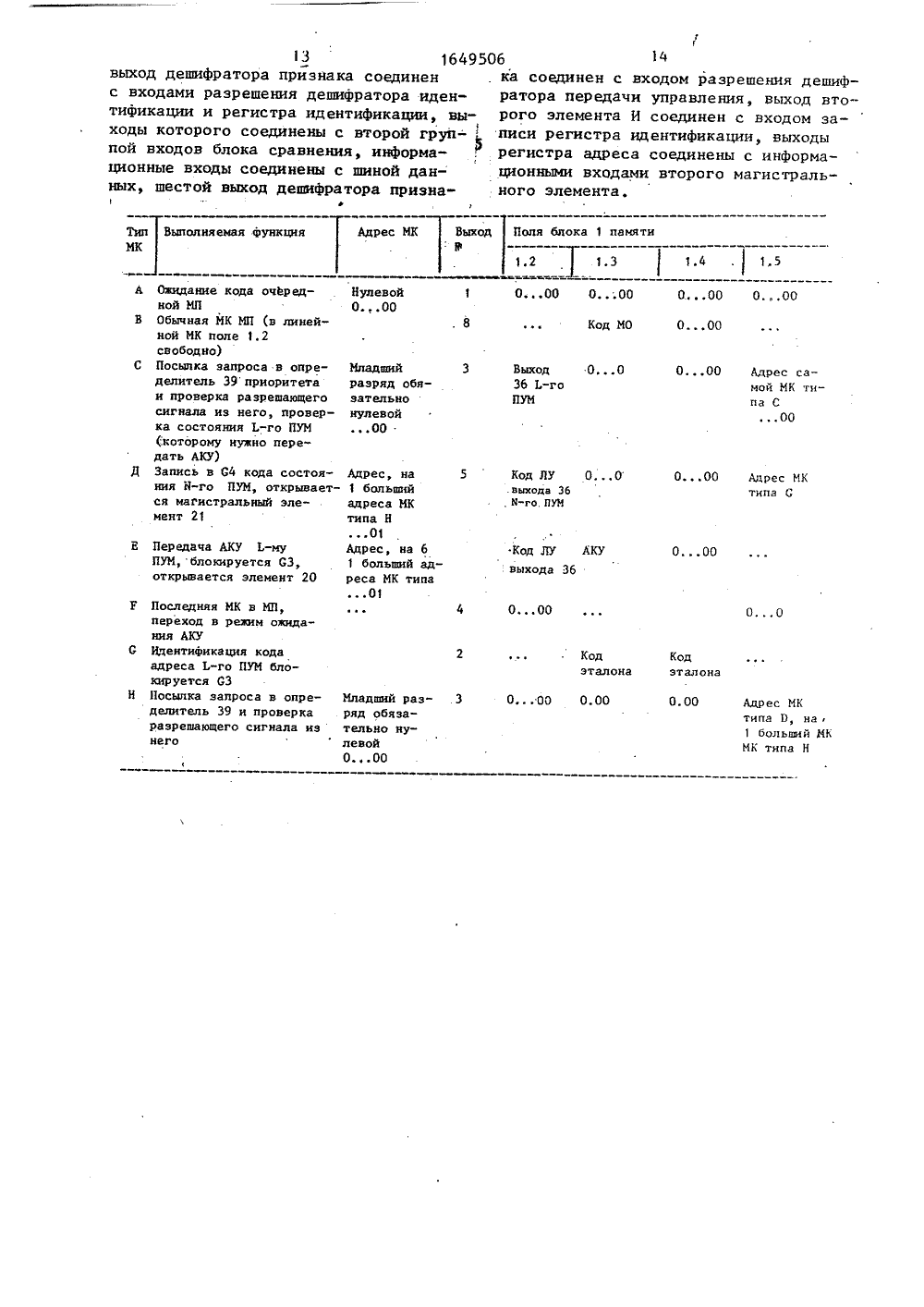

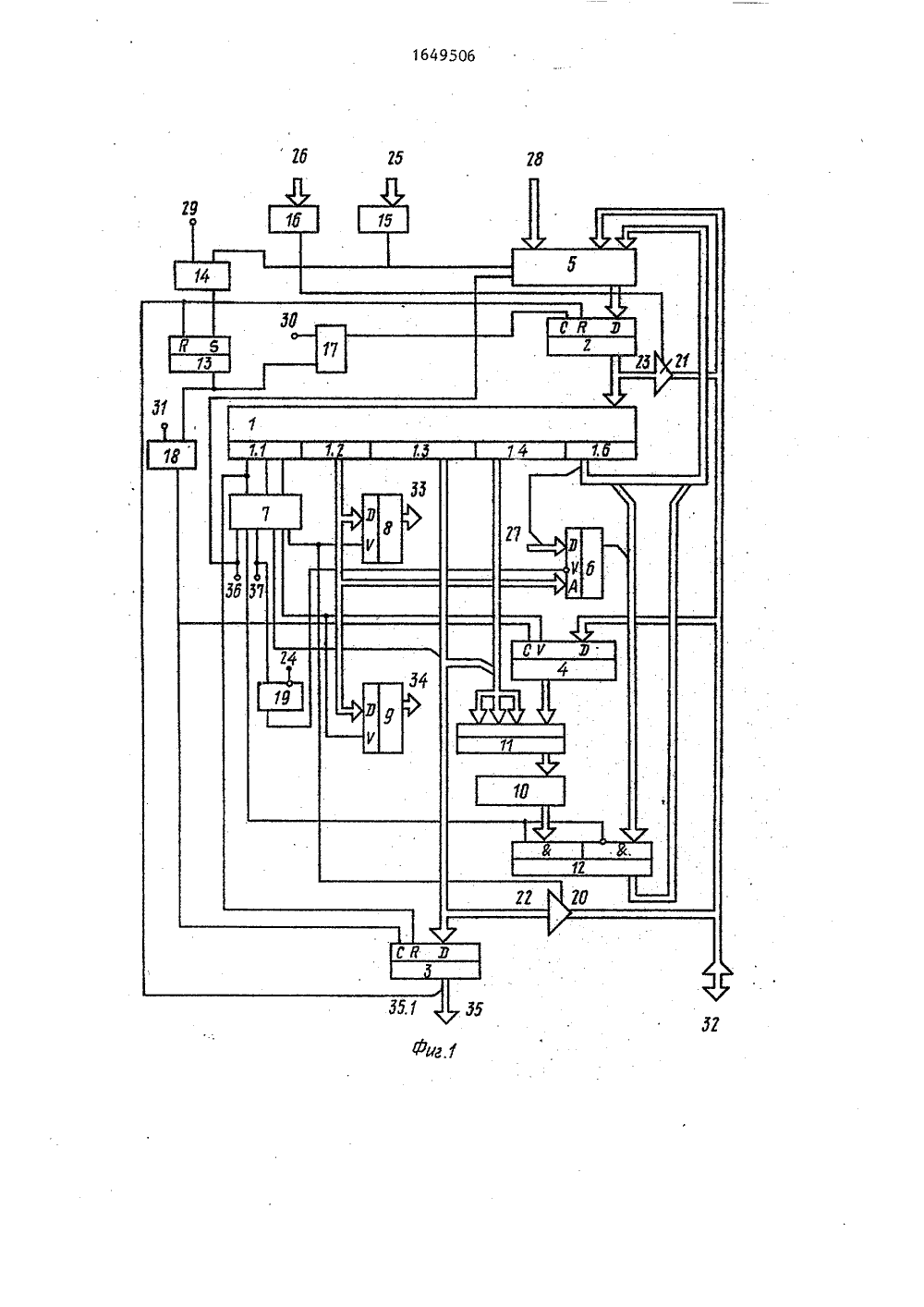

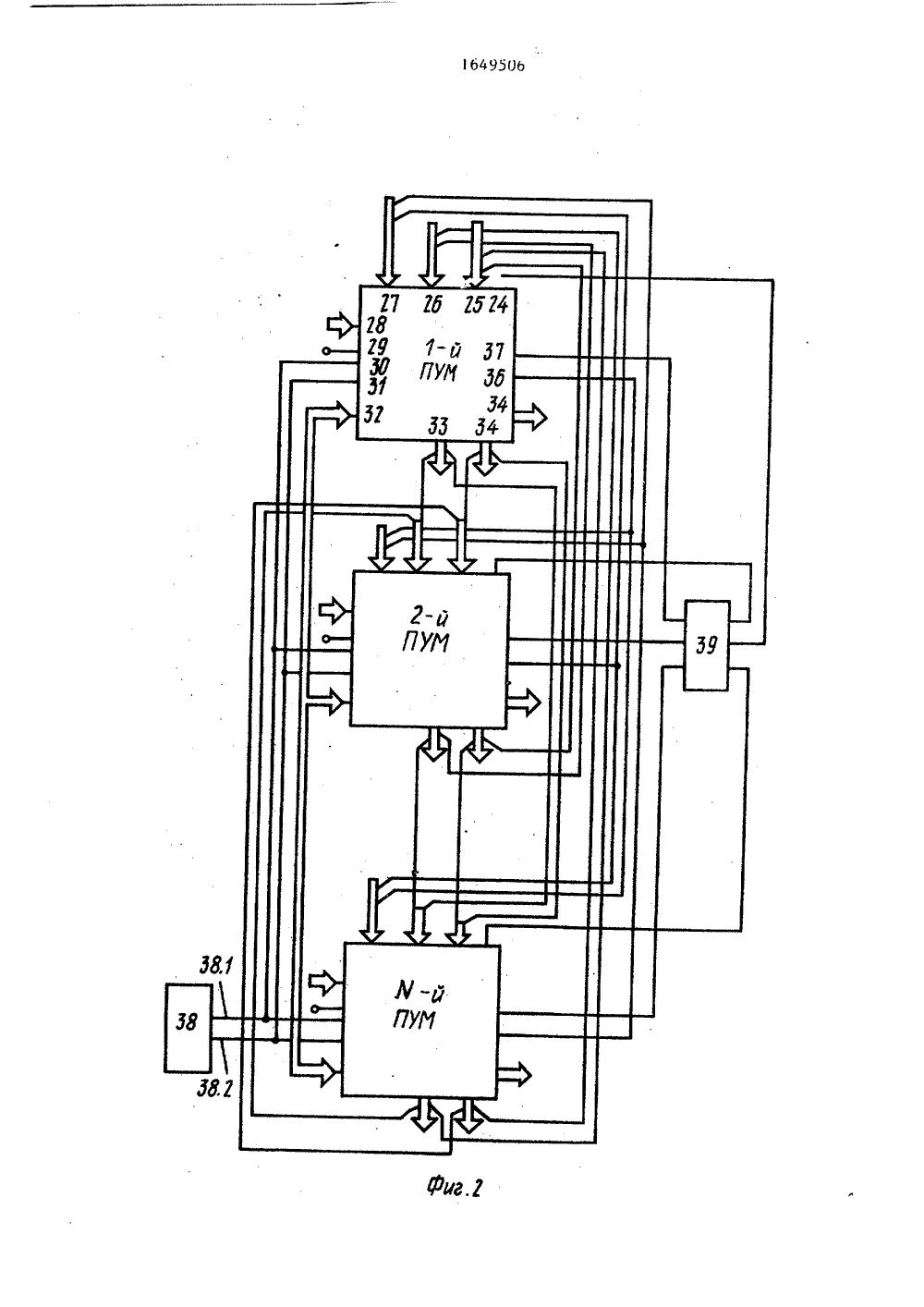

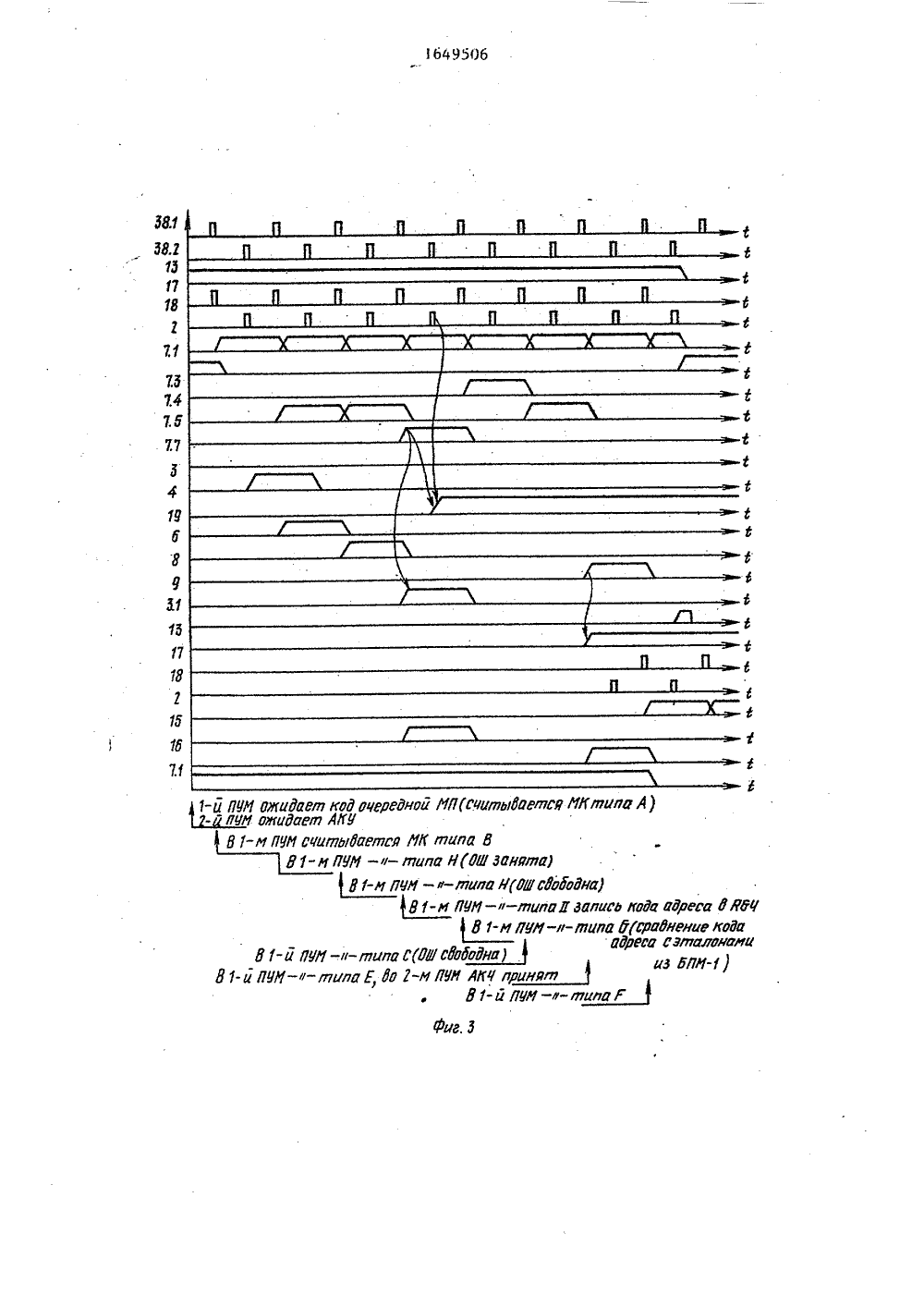

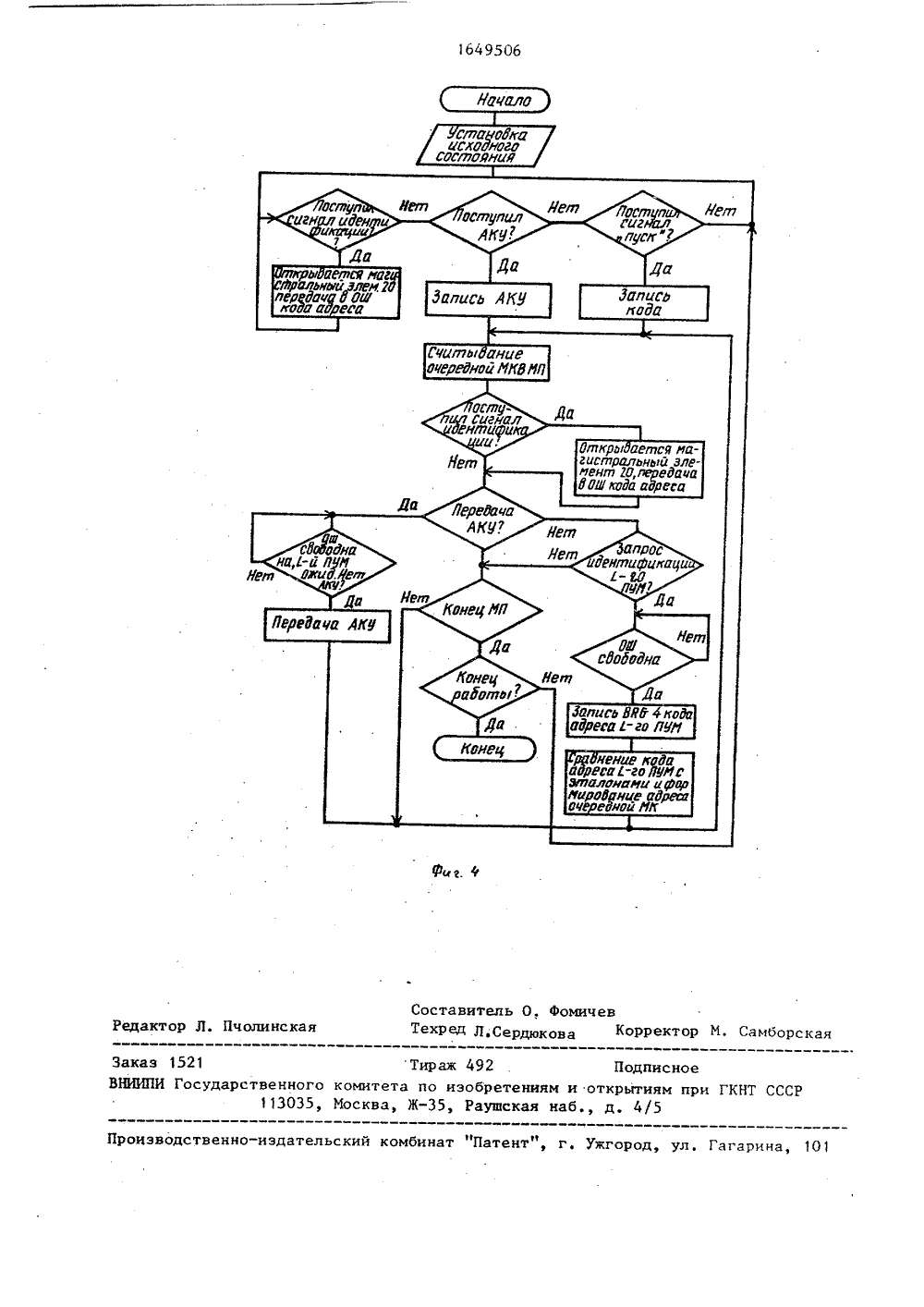

(1)5 Ь 0 В 19/0 ИСАНИЕ ИЗОБРЕТЕНИЯ УЭ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ П(НТ СССР ВТОРСНОМУ СВИДЕТЕЛЬС(56) Авторское свидетельство СССРФ 834669, кл. С 05 В 19/18, 1981,Авторское свидетельство СССРР 1149221, кл. С 05 В 19/18, 1985.Авторское свидетельство СССРпо заявке В 4370638/24,кл. С 05 В 19/08, 1988.(57) Изоьретение относится к автоматике и вычислительной технике и можетбыть использовано в распределенных отказоустойчивых системах АСУ ТП, системах станков с ЧПУ, использующих проИзобретение относится к автоматике и вычислительной технике и может Ьыть использовано в распределенных отказоустойчивых системах АСУ ТП (системах управления сложными взаимодействующими технологическими оЬъектами, системах станков с ИПУ и др,), использующих программный принцип управления, построенных по модульному принципу и допускающих наращивание атрукграммный принцип управления, построенных по модульному принципу и допускающих наращивание структуры при расширении числа выполняемых функций. Цель изобретения - повышение надежности модуля. Поставленная цель достигается тем, что в программируемый модуль, содержащий блок памяти, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый, второй и третий элементы И и первый магистральный элемент, дополнительно введены регистр идентификации, дешифраторы передачи управления и идентификации, шифратор, блок сравнения, коммутатор, второй магистральный элемент и третий элемент ИЛИ. Введение новых элементов позволяет осуществлять обмен адресами, анализировать состояние других модулей, включенных в систему, сократить объем управляющей памяти. 4 ил., 1 табл. туры при расширении числа выполняемых функций.Цель изоьретения - повышение наежности функционирования модуля.На фиг. 1 - Функциональная схема программируемого управляющего модулями на фиг, 2 - функциональная схема системы на модульной основе; на фиг, 3- временная диаграмма работы двух модулей распределенной системьц на фиг,4адреса д ЮбЧ днеиие кода сзталонаии 3 БПИ) о 1-й ПУФ-и-типа С(81 и ПЧК - й-типа Е оо 1 Фиг 5 1-и ПУИ 0 жидает ПУм ожидает цередной И 0(сцилл1649506 слаыой.а искооного сосания Записьлада Запись АКУ Счищы аниеочереднойИИВЯ Ла перез аЯКУ Нет . Конец КП йередача Аку Нещсдободна Да Уев ло еиаЬюпиДа Запись Ид аккадаадреса Е-го ПЮ Да Составитель О. фомичевТехред Л,Сердюкова Корректор М. Самборская Редактор Л. Пчолинская Заказ 1521 Тираж 492 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101 оглуп игн иден и икации Даы ауге наг Яральныйллеи 2пероедачу ада сд 1 одна на,Е-й ЩЮ нетавиФ.ел аомуУСигналенгпириии,йещ Неп /7 ости Неп 7сигналпускОткры аетср нагистральный гленент Ю,лщедачаЮИ/ яда адреса НетапрОСденпифинаоиЕУФДа д нение кода адреса Е-го ЛЮс ъпалонаии иФер ниробание адреса оч еенойю1649506 от которых данный модуль может получить АКУ), В таком исходном состоянии . предлагаемая система (фиг. 2) находится до поступления сигнала "Пуск" на вход 29 пуска хотя бы одного модуля системы.Каждый модуль может работать в следующих реяцмах: режим ожидания кода очередной МП; режим управления; режим передачи управления; режим ожидания АКУ; режим идентификации адреса,Йсходное состояние модуля равнозначно его состоянию в режиме ожидания АКУ.Переход модуля в режим ожидания кода МП изисходного состояния осуществляется по сигналу "Пуск", поступающему с входа пуска 29 через первый элемент ИЛИ 14 на установочный вход триггера 13 пуска. Единичный сигнал с прямого выхода триггера 13 пуска открывает первый 17 и второй 18 элементы И,разрешая прохождение тактовых импульсов соответственно с первого 38.1 и второго 38.2 выходов генераторов 38 к входам элементов модуля.Если к моменту появления на синхровходе регистра 2 адреса рассматриваемого модуля заднего фронта первого тактового импульса Я, ) с выхода перопераций еще не появилось, то в регистр 2 адреса переписывается нулевой адрес и из блока памяти 1 снова считыФронту тактового импульса с выходавторого элемента И 18 регистр 3 микроопераций состояния не изменяет, С перпо-прежнему считывается единичный сигнал ожидания кода очередной МП,Таким образом,.модуль сколь угодно долго ожидает код МП на своем вхоПо появлении кода МП на входе 28 этот код через мультиплексор 5 адреса записывается по заднему фронту О вВ регистр 2 адреса и модуль переходит в режим управления. По заднему фронту тактового импульса о с выхода второго элемента И 18 в регистр 3 микро- операций записывается микрооперационный код первой МК, Кроме того, едияичный сигнал на выходе 36 состояния исчезает, что является признаком того, что модуль находится в режиме упблок-схема алгоритма функционирования модуля.Модуль содержит блок 1 иамяти, регистр 2 адреса, регистр 3 микроопераций, регистр 4 идентификации, мультиплексор 5 адреса, мультиплексор 6логических условий, дешифратор 7признака, дешифратор 8 передачи управления, дешифратор 9 идентификации, 10шифратор 10, блок 11 сравнения, коммутатор 12, триггер 13 пуска, первый14, второй 15 и третий 16 элементыИЛИ, первый 17, второй 18, третий 19элементы И, первый 20 и второй 21 магистральные элементы, информационныевходы 22 первого 20 магистральногоэлемента, информационные входы 23 второго 21 магистрального элемента, вход24 ответа на запрос, входы 25 пере- . Одачи управления, входы 26 идентификации, входы 27 логических условий,. входы 28 кода операции, вход 29 пуска,первый 30 и второй 31 входы синхронизации, входы-выходы 32 шины данных, 25выходы 33 передачи управления, выходы 34 идентификации, выходы 35 микроопераций, выход 35,1 "Конец работы",выход 36 ожидания и выход 37 запроса.Иа Фиг. 2 представлена система,построенная на основе программируемыхуправляющих модулей (ПУМ), содержащая , вого элемента И 17 на входе 28 кодагенератор 38 и определитель 39 прио"ритетов.Модуль работает следующим образом.В исходном состоянии генератор 38 вается МК типа А. Так как в ее полевырабатывает на своих выходах после- аписан нулевой код, то по заднемудовательности сдвинутых относительнодруг друга тактовых импульсов, все модули находятся в состоянии ожидания 40кода МП нли АКУ, вого выхода дешнфратора 7 признакаВсе элементы памяти установлены в"О", Из блока 1 памяти считываетсясодержимое нулевой ячейки (с нулевымадресом), В соответствии с таблицей 45это МК типа А, В ее поле 1,1 записан декод, который декодируется дешифратором 7 признака как сигнал ожиданиякода очередной МП, Этот единичный сигнал поступает на второй управляющий 5 Овход мультиплексора 5 адреса, которыйсогласно описанному алгоритму работыпропускает на информационный вход регистра 2 адреса код операции с входа28 модуля, Кроме того, единичный сигнал с первого выхода дешифратора 7 поступает на выход 36 состояния модулят,е. на один из разрядов входов логических условий всех модулей системы,30 5 164950равления, в режиме передачи АКУ илив режиме идентификации,По заднему фронту очередного тактового импульса с выхода первого элемен 5та И 17 в регистр 2 адреса с выходамультиплексора 5 адреса записываетсяадрес очередной МК, Этот адрес поступает на второй информационный входмультиплексора 5 адреса со старшихразрядов выхода 15 поля адреса блока1 памяти (немодифицируемая часть) ивыхода коммутатора, 12 (модифицируемая часть). В данном режиме из блока 1 памяти считывается либо линейные МК, либо МК ветвления. В линейных МК значения младшего разряда адреса очередной МК в МП определяетсязначением младшего разряда поля 1,5адреса Ьлока 1 памяти, В поле 1.2 логических условий в линейных МК записан нулевой код. По этому коду мультиплексор 6 логических условий пропускает на выход значение сигнала смладшего выхода поля 1,5 блока памяти1. В МК ветвления в поле 1,2 записанкод логического условия, значение которого анализируется при формированииадреса очередной,МК. По этому ходумультиплексор 6 логических условийпропускает с входа 27 модуля на выходзначение нужного логического условия,Так как в режиме управления на второмвыходе дешифратора 7 признака единичный сигнал не появляется, то на первом управляющем выходе коммутатора 12всегда имеется нулевой сигнал, Такимобразом, в режиме управления младшийразряд адреса очередной МК полностьюопРеделяется значением сигнала на выходе мультиплексора 6 логических ус-.ловий, По записанному в регистр 2адресу из блока памяти 1 считывается очередная линейная МК или МК ветвления.Аналогичным образом модуль реализует в треЬуемой последовательности всеосновные МК,Из режима управления модуль можетперейти в любой другой режим. 1 5011 ри переходе в режим ожидания. кода очередной МП в полях 1.2 кода логических условий и 1.5 адреса формата последней МК, выполнявшейся МП, записываются нулевые коды и в следующем такте из блока памяти 1 считывается нулевая МК (МК типа А), т,е. модуль переходит в уже описанное ранее состояние ожидания кода очередной МП. 6 6При необходимости получения информации от другого модуля системы, т,е.перехода в режим ожидания АКУ, илиже окончание работы модуля в поле 1,1формата последней МК выполнявшейсяМ 11, записывается код, по которому дешифратор 7 формирует на своем четвертом выходе сигнал микрооперации конца работы. В полях 1,2 кода логических условий и 1.5 адреса формата МК(МК типа Г), записаны нулевые коды,Единичный сигнал микрооперации концаработы по заднему фронту очередноготактового импульса (О) записываетсяв регистр 3Затем с соответствующеговыхода 35. 1 регистра 3 сигнал микрооперации конца работы обнуляет триггер 13 пуска и регистр 2 адреса, Приэтом единичный сигнал с первого выходаполя 1.1 ьлока памяти 1 обнуляет регистр 3 и соответственно сигнал микрооперации конца работы на его выходе35.1. Модуль находится в описанномвыше состоянии,При необходимости передать информацию другому модулю системы рассматриваемый модуль из режима управленияпереходит в режим идентификации.По заднему фронту очередного тактового импульса 2, с выхода элементаИ 17 (фиг, 3) в регистр 2 адреса записывается адрес МК типа Н, Это МКпроверки готовности системы к идентификации И-м модулем Ь-го,На третьем выходе дешифратора 7признака формируется сигнал запросасостояния шины передачи АКУ, Этот сигнал поступает на соответствующий И-йвход определителя 39 приоритета. Еслив этом такте работы системы в определитель 39 сигналов запросов от другихмодулей системы не поступало, то согласно описанному алгоритму работы, определитель 39 формирует на И-м выходесигнал разрешения пользования оЬщейшиной 32 для идентификации в следующем такте работы системы. В противномслучае такой сигнал формируется на,другом выходе определителя 39, который соединен уже с входом 24 ответана запрос другого, более приоритетного модуля системы. При нулевом сигнале ответа на запрос на входе 24 Н-гомодуля третий элемент И 19 формируетединичный сигнал, который поступаетна управляющий вход мультиплексора 6логических условий. По этому сигналуна выходе мультиплексора 6 формирует 1649506ся нулевой сигнал, Таким образом, по очередному импульсу ь, в регистр 2Ладреса записывается адрес ИК типа Н, Регистр 3 при считывании МК типа Н обнуляется единичным сигналом с первого выхода поля 1, 1 признака блока памяти, Как только на вход 24 Я-го модуля поступает единичный разрешающий сигнал из определителя 39 приоритета, 10 на входе 27 мультиплексора б логических условий единичный сигнал исчезает и на его выходе появляется единичный сигнал с выхода младшего разряда выхода поля 1,5 адреса блока 1 памяти.По очередному импульса 6 с первого выхода 38. 1 генератора 38 в регистр 2 адреса И-го модуля записывается адрес МК типа П, Единичный сигнал с пятого выхода дешифратора 7 признака поступает на управляющие входы дешифратора 9 и регистра 4 идентификации, с выхода поля 1,2 кода логических условий блока 1 памяти считывается позиционный код Ь-го модуля, который 25 декодируется дешифратором 9 идентификации, По унитарному коду на выходе 34 И-го модуля на соответствующем разряде входа 26 идентификации Ь-го модуля появляется единичный сигнал идентификации. Этот сигнал через элемент ИЛИ 16 открывает второй магистральный элемент 21, который пропускает на шину 32 адресный код с Ь-го модуля с выхода регистра 2 адреса. По очередному тактовому импульсус выходаХвторого элемента И 18 в регистр 4 И-го модуля записывается адресный код Ь-го ПУМ, Код адреса с выхода регистра 4 идентификации поступает на вход 40 блок 11 сравнения и сравнивается с кодом эталона, поступающим с выходов по.лей 1,3 микрооперации и 1.4 эталонов, Унитарный код с выхода блока 11 сравнения поступает на вход шифратора 10, 45 в котором преобразуется из унитарного в позиционный код адреса. Этот код с выхода шифратора 10 поступает на первый информационный вход коммутатора 12, на первом управляющем входе кото рого присутствует нулевой сигнал с второго выхода дешифратора 7 признака. Нулевой сигнал с второго выхода дешифратора 7 признака поступает также на второй управляющий вход коммутатора 12. Таким образом, адрес очередной МК полностью определяется кодом, поступающим с выхода младших разрядов поля 1.5 адреса блока 1 памяти на второй информационный вход коммутатора 12, и сигналом, поступающим свыхода мультиплексора 6 логическихусловий, На адресный вход мультиплексора 6 логических условий поступаеткод 11-го модуля, По этому коду мультиплексор 6 пропускает с входа 27 насвой выход. значение состояния Ь-го модуля, Таким образом, появляется возможность перехода к Различным МК идентификации в зависимости от состоянияЬ-го модуля.По заднему Фронту импульсакроме того, с выхода второго элементаИ 18 в регистр 3 микроопераций записывается микрооперационный код. Позаднему фронту очередного тактовогоимпульса , с выхода элемента И 17Лв регистр 2 адреса записывается адресМК типа С, Это МК идентификации адреса Ь-го ПУМа,Код эталона с выходов поля 1.3микроопераций и поля 1.4 эталона блока 1 памяти поступает на,группу вхоов эталона блока 11 сравнения, навход идентификации блока 11 сравненйяпоступает код адреса с выхода регистра 4, Нлок сравнения формирует насвоем выходе унитарный код, которыйсоответствует тому входу, из группывходов эталонов, с которым совпал кодадреса с выхода регистра 4 идентификации. В случае, если ни один из кодовне совпал с кодом адреса, блок 11сравнения формирует нулевой сигнал.Унитарный код с выхода блока 11 сравнения преобразуется в шифраторе 10 впозиционный и поступает на первыйинформационный вход коммутатора 12.На втором выходе дешифратора 7 признака формируется единичный сигнал. Этотсигнал поступает на первый прямой управляющий вход коммутатора 12 и разрешаетпрохождение через него кода с выходашифратора 10. Код с выхода коммутатора 10 поступает на группу мпадших разрядов третьего входа мультиплексора5 адреса и полностью определяет адресочередной МК, Таким образом, устанавливается, в каком состоянии из всехвозможных находится Ь-й модуль.Единичным сигналом с первого выходаполя 1,1 признака блока 1 памяти регистр 3 микроопераций устанавливаетсяв нулевое состояние.После того, как Я-й модуль идентифицировал состояние Ь-го модуля,И-й модуль может переходить в режим164950 передачи информации. По заднему фронту очередного тактового импульса в регистр 2 адреса записывается адрес МК типа С. Это МК готовности системы Е передаче от Я-го модуля Ь-му. АКУ. На третьем выходе дешифратора 7 формируется единичный сигнал запроса состояния шины передачи АКУ. Этот сиг- . нал поступает на соответствующий И-й вход определителя 39 приоритета, Если в этом такте работы системы в определитель 39 сигналов запросов от других модулей системы не поступило, то согласно описанному алгоритму работы оп ределитель 39 формирует на своем В-м выходе сигнал разрешения пользования общей шиной 32 в следующем такте работы системы. В противном случае такой сигнал формируется на дРугом выходе определителя 39, который соединен с входом 24 ответа на запрос другого, более приоритетного модуля системы. При нулевом сигнале ответа на запрос на выходе 24 И-го модуля третий эле мент И 19 формирует единичный сигнал, который поступает на управляющий вход мультиплексора 6 логических условий. По этому сигналу мультиплексора 6 формирует на своем выходе нулевои 30 сигнал и по очередному импульсу 8, в регистр 2 запишется адрес самой МК тиЛпа С.,Регистр 3 микроопераций при считывании МК типа П обнуляется единичным сигналом с первого выхода поля 1.1 признака блока 1 памяти, Как только на вход 24 11-го модуля поступает единичный разрешающий сигнал из определителя 39 приоритета,. на управляющем входе мультиплексора 6 единич ный сигнал исчезает и на его выходе появляется значение ЛУ с выхода 36 состояния Ь-го модуля. Если сигнал этого ЛУ нулевой, т.е. Ь-й модуль не готов к приему АКУ, то в следующем такте работы из И-го модуля снова считывается та же самая МК типа С.Как только на входе 24 И-го модуля появляется единичный сигнал, а значение ЛУ с выхода 36 состояния Ь-го модуля на входе ЛУ И-го ПУМ станет единичным (Ь-й ПУМ находится в состоянии ожидания АКУ), значение младшего разряда очередной МК с И-м модуле также станет единичным. По очередному им-пульсу 8, с первого выхода 38,1 ге 5 нератора 38 в регистр 2 адреса М-го модуля записывается адрес МК типа Е. Единичный сигнал с шестого выхода де 6, 1 Ошифратора 7 признака открывает магистральный элемент 21 и поступает на управляющий вход дешифратора 8 передачи управления. При этом на информационном входе регистра 2 адреса формируется адрес первой МК МП идентификации адреса Ь-го модуля (МК типа В, С), с выхода поля 1.2 кода ЛУ ьлока 1 памяти считывается позиционный код Ь-го модуля, а с выхода 1,3 микроопераций в шину 32 поступает АКУ. По позиционному коду на выходе дешифратора 8 Ь-го модуля на соответствующем разряде входа 25 сигналов передачи управления Ь-го модуля появляется единичный сигнал передачи управления. Этот сигнал через элемент ИЛИ 15 поступает на мультиплексор 5 адреса, который согласно описанному алгоритму пропускает на вход регистра 2 адреса АКУ с шины 32, Кроме того, сигнал передачи управления через элемент ИЛИ 14 устанавливает в единичное состояние триггер 13 пуска Ь-го модуляОчередной тактовый импульс 8 с второго выхода 38.2 генератора 38 проходит через элемент И 18 на вход синхронизации регистра 3 микроопераций. Запись в регистр 3 микроопераций запрещена сигналом с первого выхода поля 1.1 признака блока памяти 1. По очередному тактовому импульсус выхо 4 да 38, 1 генератора 38 в регистр 2 Ь-го модуля записывается АКУ, а в регистр 2 адреса Н-го модуля - первая МК идентификации (ИК типа Н), 19-й модуль, используя МП идентификации, проверяет, код адреса Ь-го модуляЕсли код адреса Ь-го модуля не совпал с кодамиэталона,то 11-й модуль переходит к аварийной МП, целью выполнения которой может ьыть остановка и повторный запуск Ь-го модуля, перевод всей системы в режим поиска отказа и т.п.Для оьеспечения живучести системынаиьолее важные МП Ь-го модуля, от реализации которых зависит раьота других модулей, резервируются в определенных модулях. Тогда аварийная МК может являться первой МК специальной МП передачи нужного АКУ модуля, в котором зарезервирована нужная МП,Технические преимущества программируемого управляющего модуля: расширение области применения путем оьеспечения возможности обмена адресами и анализа состояния других модулей системы; сокращение объема управляющей памяти164950 и повышения на этой основе надежности л системы,Формула Программируемый управляющий модуль, содержащий блок памяти, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИПИ, первый, второй и третий элементы И и первый магистральный элемент, информационные выходы которого соединены с шинои данныхь 15 вход пуска модуля является первым входом первого элемента ИЛИ, выход которого соединен с входом установки триггера пуска, выход которого соединен с первыми входами первого и второ" 20 го элементов И вторые входы которых являются соответственно первым и вторым входами синхронизации модуля, а выходы соединены соответственно с входами записи регистров микроопераций и 25 адреса, выходы которого соединены с адресными входами блока памяти, выходы поля признака которого соединены с входами дешифратора признака, первый выход которого является выходом Зо ожидания модуля и соединен с вторым адресным входом мультиплексора адреса, выходы которого соединены с информационными входами регистра адреса, а первая и вторая группы информационных входов соединены соответственно с входами хода операций и шиной данных, выход старшего разряда группы выходов поля признака блока памяти соединен с входом сьроса регистра мик О роопераций, выходы которого являются выходами микроопераций модуля, а выход "Конец работы" соединен с входами сброса триггера пуска и регистра ,адреса, третий выход дешифратора приз нака является выходом запроса и соединен с первым входом третьего элемента И, второй инверсный вход которого является входом ответа на запрос, а выход соединен с инверсным входом раз О решения мультиплексора логических условий, четвертый выход дешнфратора признака соединен с выходом младшего разряда группы инФормационных входов регистра микроопераций и первого магистрального элемента, шестой выход дешифратора признака является управляющим входом первого магистрального элемента, выходы поля логических усиз обр ет ения.5 12бовий блока памяти соединены с адресными входами мультиплексора логических условий, выходы кода микроопераций соединены с входами старших разрядов группь 1 информационных входов регистра микроопераций и первого магистрального элемента, младший разряд поля адреса и входы логических условий мультиплексора логических условий являются информационными входами мультиплексора логических условий, выходы старших разрядов группы выходов поля адреса блока памяти соединены с входами старших разрядов третьей группы информационных входов мультиплексора адреса, входы передачи управления модуля являются входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и первым адресным входом мультиплексора адреса, о т л и ч а ю щ и й с я тем, что, с целью повышения йадежности функционирования модуля, в него дополнительно введены регистр идентификации, дешифраторы передачи управления и идентификации, шиФратор, блок сравнения, коммутатор, второй магистральньй элемент и третий элемент ИЛИ, входы которого являются входами идентификации, а выход соединен с входом управления второго магистрального элемента, выходы которого соединены с шиной данных, входы-выходы которой являются инФормационными входами-выходами модуля, выходы кода логических условий блока памяти соединены с информационными входами дешифратора передачи управленияи идентификации, выходы которых являются соответственно выходами передачиуправления и идентификации модуля,четвертый выход дешифратора признака,выходы кода микроопераций и кода эталонов олока памяти являются первойгруппой входов блока сравнения, выходы которого соединены с входами шифратора, выходы которого соединены с первой группой информационных входов коммутатора, выходы которого соединены свходами младших разрядов третьей группы информационных входов мультиплексора адреса, выход мультиплексора логических условий и выходы младших разрядов группы вЫходов поля адреса блока памяти являются второй группой ин формационных входов коммутатора, второй выход дешифратора признака еоединен с первым и вторым инверсными входами управления коммутатора, пятый13 164950614выход дешифратора признака соединен ка соЕцинен с входом разрешения дешнфс входами разрешения дешифратора иден- ратора передачи управления, выход втотификации и регистра идентификации, вы- рого элемента И соединен с входом заходы которого соединены с второй груп писи регистра идентификации, выходы пой входов блока сравнения, информа- : регистра адреса соединены с информационные входы соединены с шиной дан- цнонными входами второго магистральных, шестой выход дешнфратора призна- ного элемента. Тю Выполняемая функцияМК Выход Поля блока 1 памяти Адрес МК 1.2 1.3 А Охидание 000 О.00.0 Нулевой очеред 0 Код МО Выход 0036 Ь-гоПУМ О Младшийразряд обязательнонулевой00 Адрес самой МК типа С00 000 Адрес МКтипа С Код ЛУ.выхода 36Н-го. ПУМКод ЛУ АКУвыхода 36 0 Передача АКУ Ь-муПУМ, олокируется СЗ,открывается элемент 20 ОО Кодэталона оэталона0.00 Адртип1 бМК 3 00 О Младший ра ряд обязательно нулевой 000 пре с МКО, нальший МКипа Н а а и Обычная МК МП (в линейной МК поле 1.2свободно)Посылка запроса в определитель 39 приоритетаи проверка разрешающегосигнала из него, проверка состояния Ь-го ПУМ(которому нушно передать АКУ)Запись в С 4 кода состояния Н-го ПУМ, открывается магистральный элемент 21 Р Последняя МК впереход в резимния АКУС Идентификация кодаадреса Ь-го ПУМ блкируется СЗН Посылка запроса в оделитель 39 и проверазрешающего сигналнего Адрес, на1 большийадреса МКтипа Н01Адрес, на 61 больший адреса МК типа01

СмотретьЗаявка

4638656, 17.01.1989

ПРЕДПРИЯТИЕ ПЯ Г-4651

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, МАРКОВ ПЕТР ЕВГЕНЬЕВИЧ, ВАЛОВ ОЛЕГ ГЕННАДИЕВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ

МПК / Метки

МПК: G05B 19/08

Метки: модуль, программируемый, управляющий

Опубликовано: 15.05.1991

Код ссылки

<a href="https://patents.su/11-1649506-programmiruemyjj-upravlyayushhijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый управляющий модуль</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Программируемый управляющий модуль

Случайный патент: Способ разложения амальгам щелочных металлов