Адаптивная система управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1566319

Авторы: Глумов, Земляков, Рутковский, Силаев

Текст

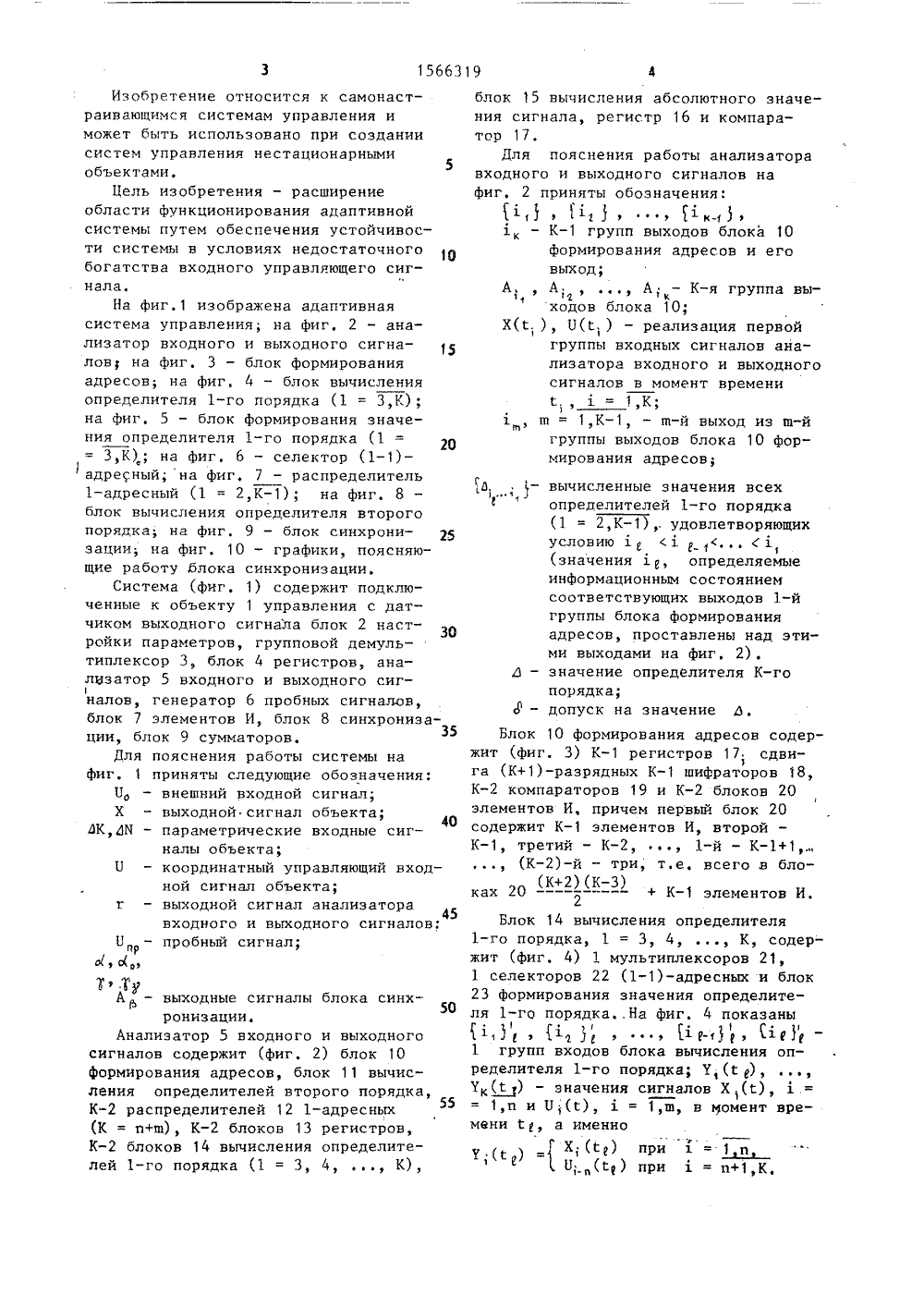

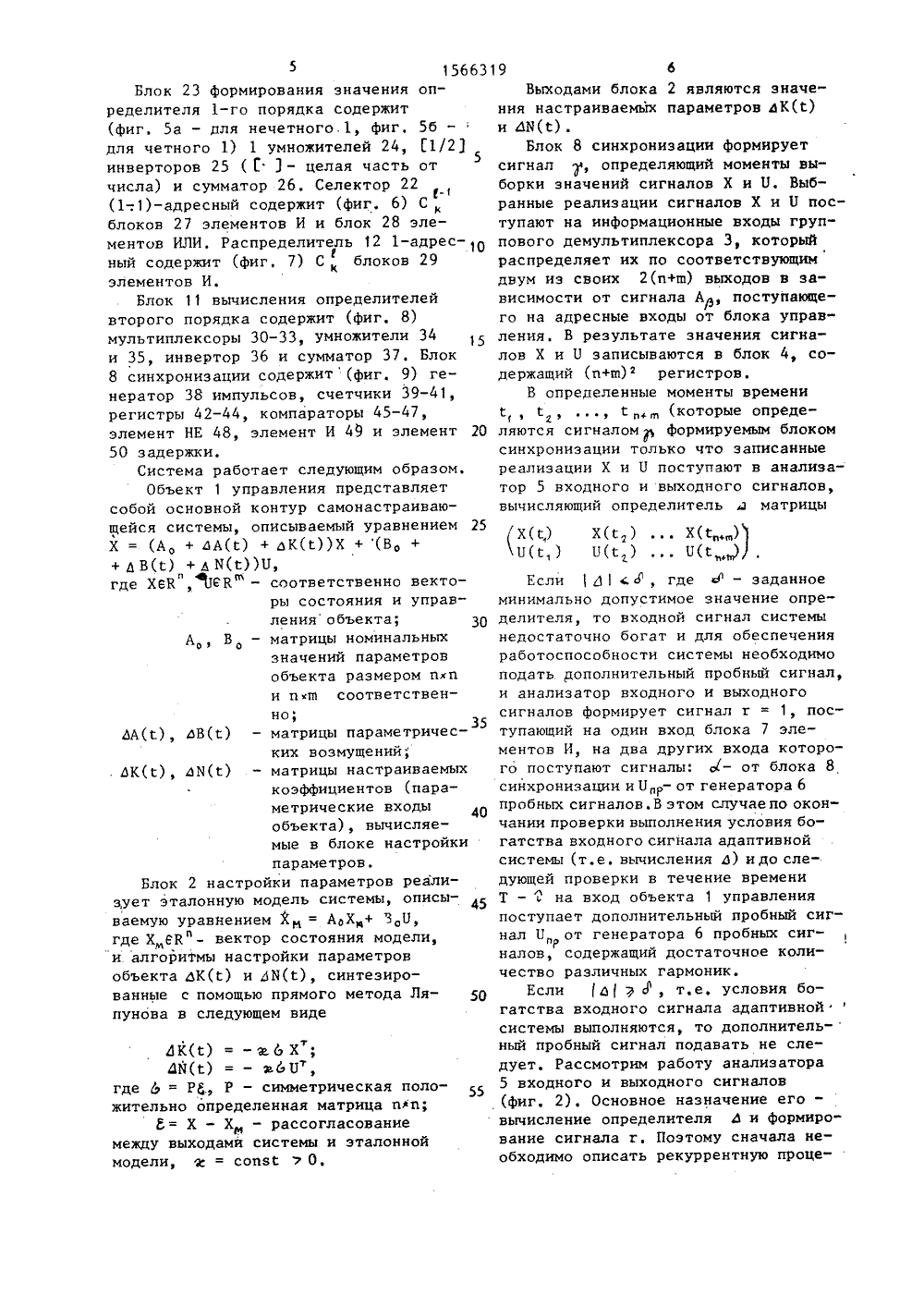

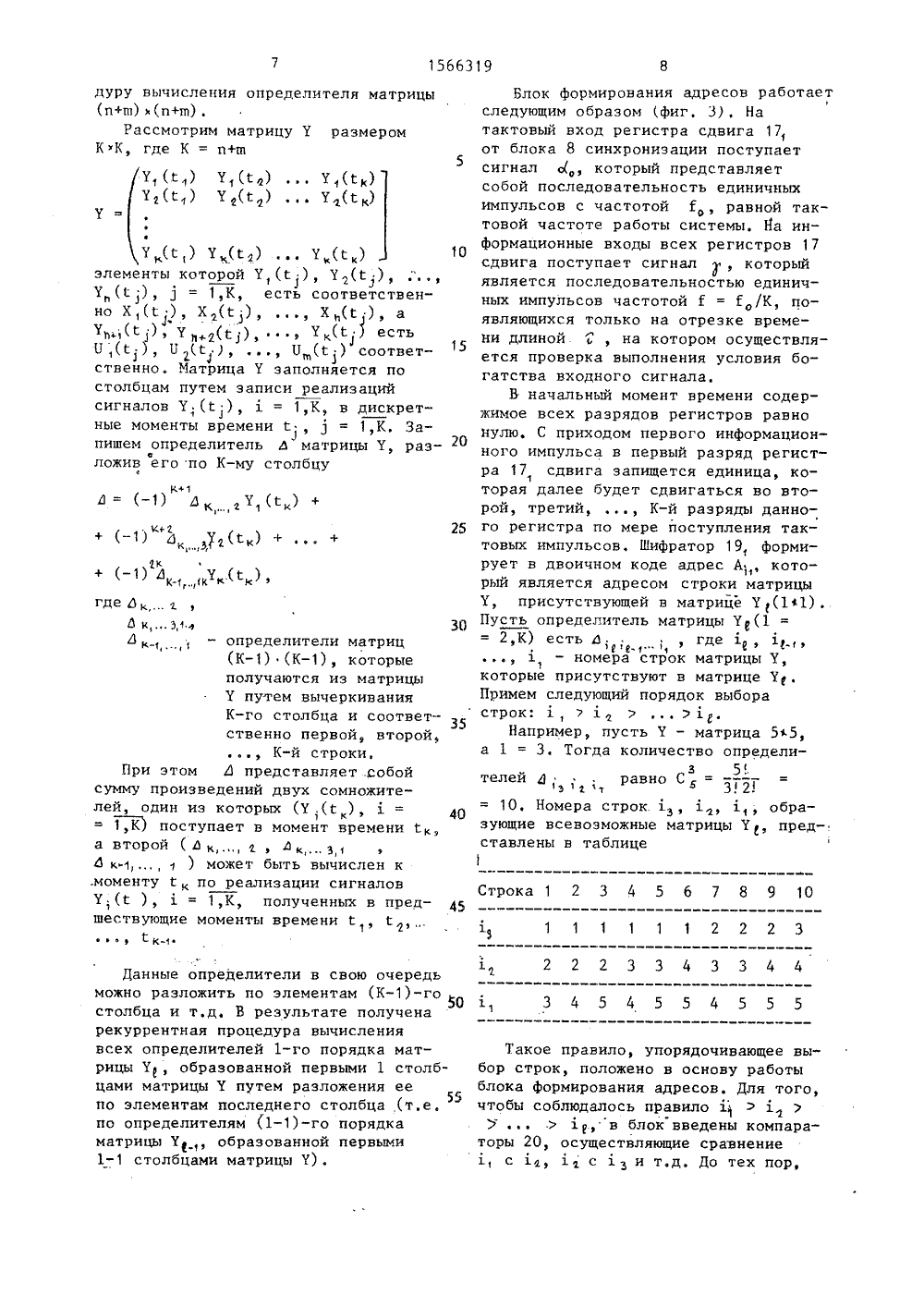

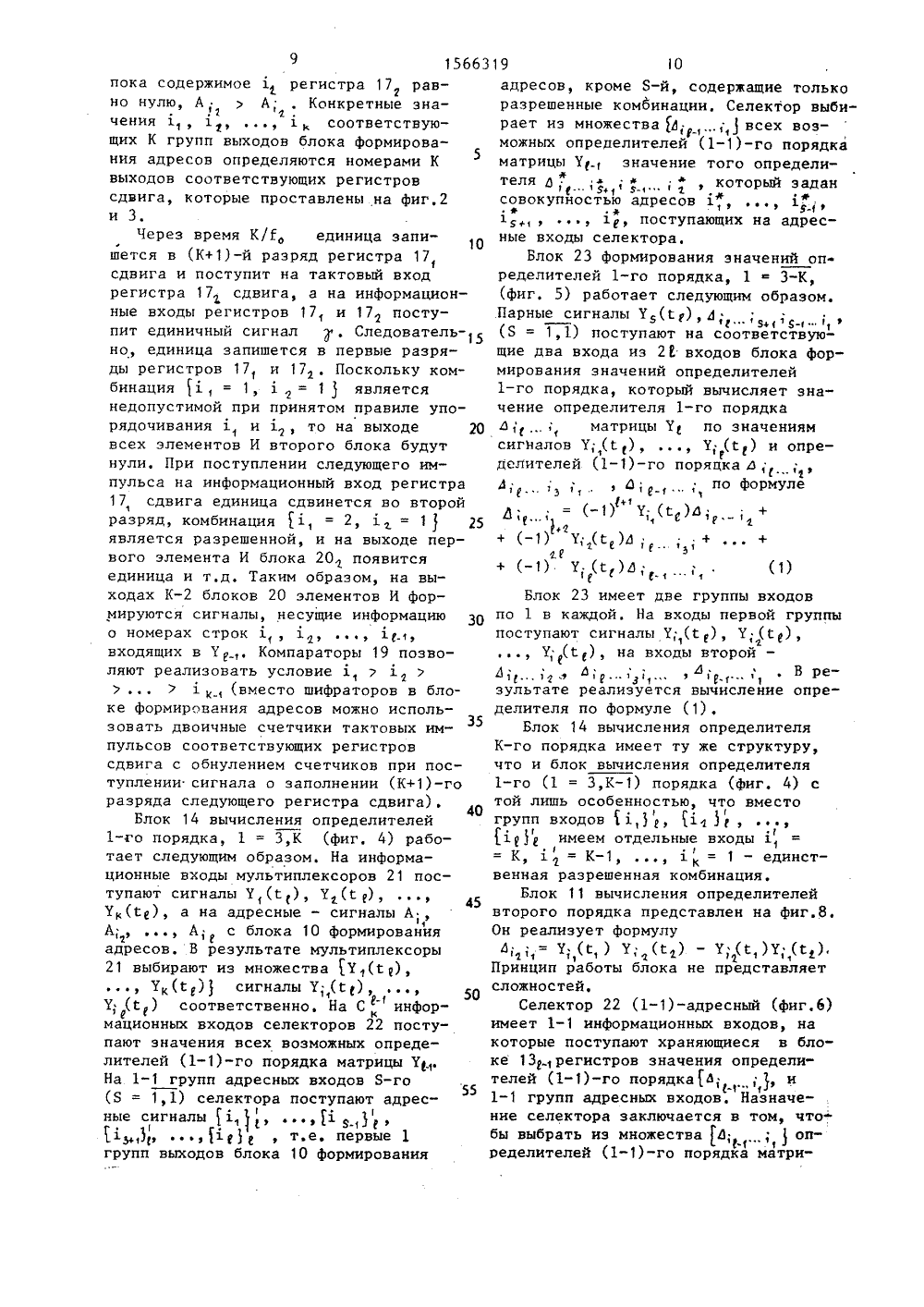

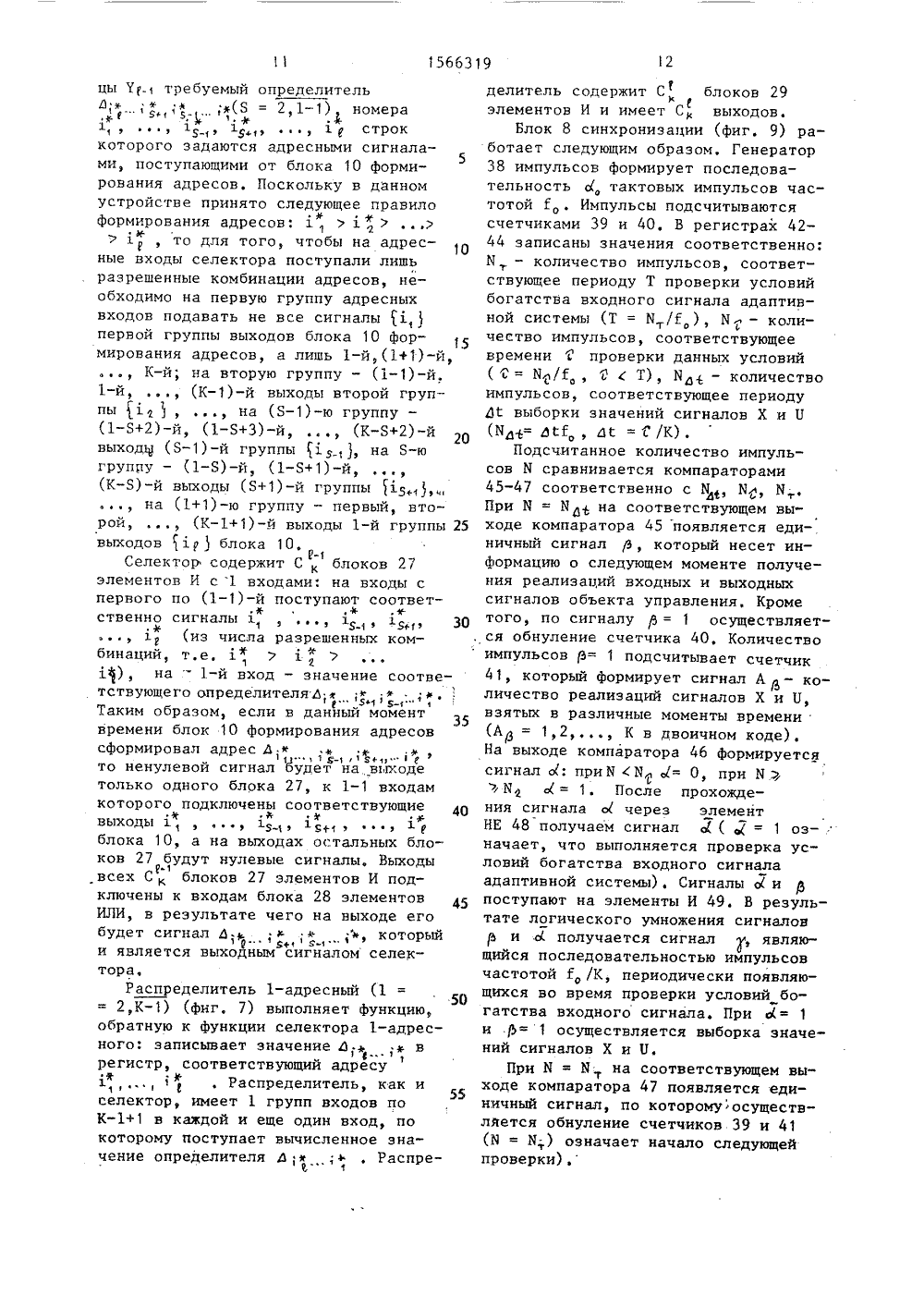

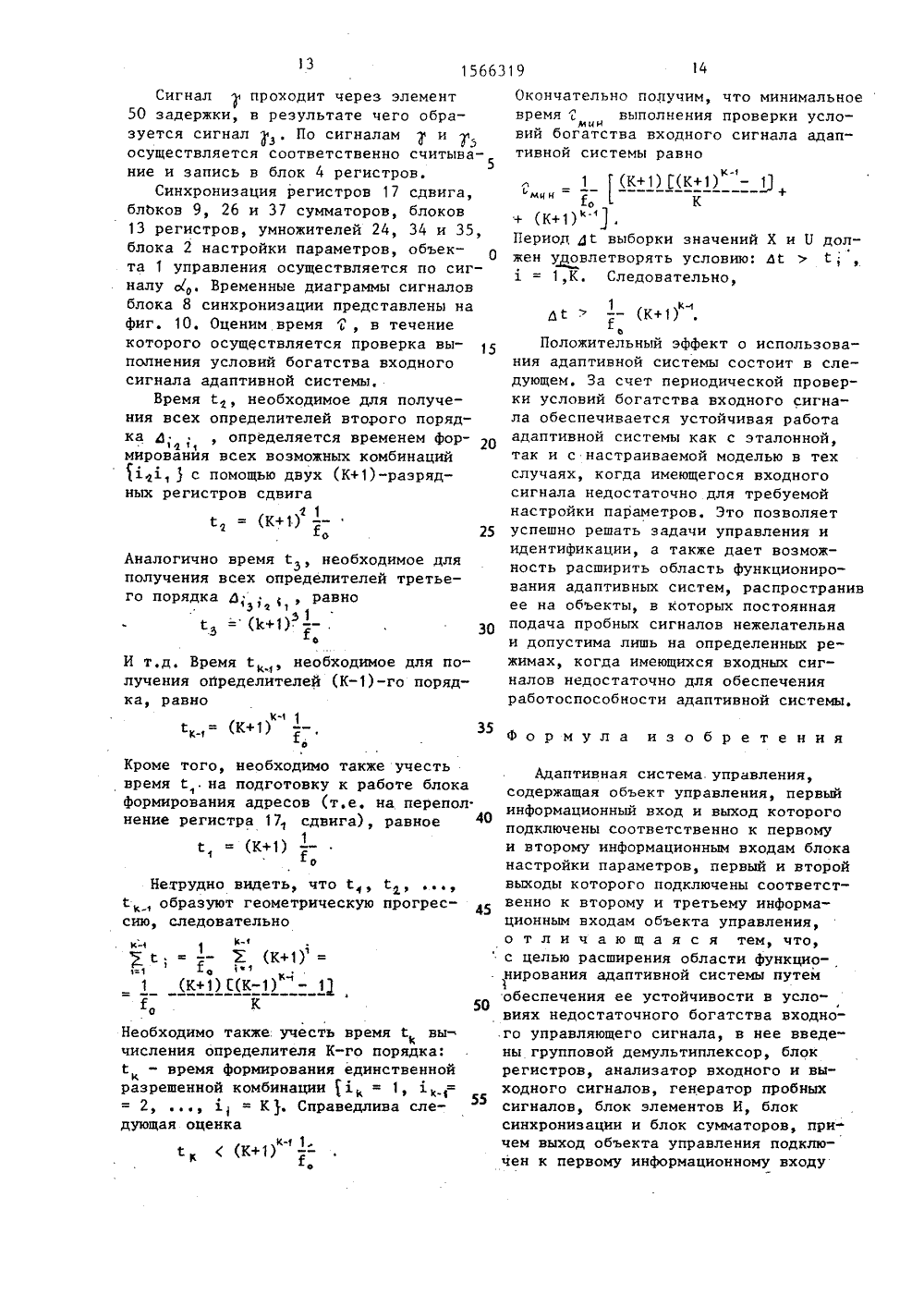

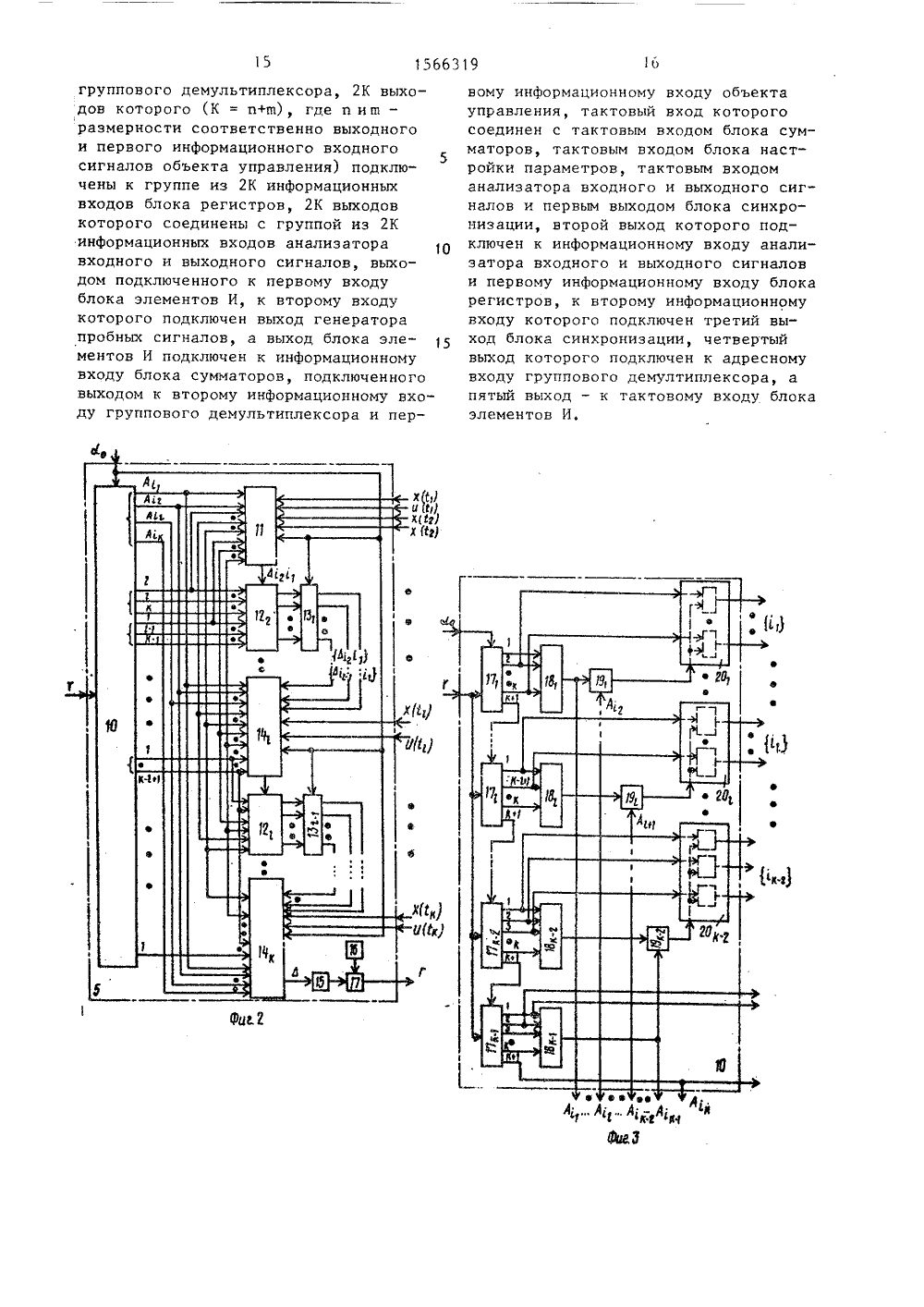

СОЮЗ СОВЕТСКИХСОЦИА ЛИСТ ИЧЕСНРЕСПУБЛИК, 156631 9) 1)Ь С 05 813 ИСАНИЕ ИЗОБРЕТЕ ЕЛЬСТ ТОР СКОМУ иваю 1 ашия Фие,ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМРИ ГКНТ СССР(71) Институт проблем управлени(56) Петров Б.Н., Рутковский ВКрутова И,Н, и др, Принципы посния и проектирования самонастращихся систем управления, - М.:ностроение, 1972, с, 105-106,(54) АДАПТИВНАЯ СИСТЕМА УПРАВПЕ(57) Изобретение относится к санастраивающимся системам управли может быть использовано при с нии систем управления нестационарными объектами, Целью изобретения является расширение области функционирования адаптивной системы путемобеспечения устойчивости системы вусловиях недостаточного богатствавходного управляющего сигнала, Апаптивная система управления содержитобъект 1 управления с датчиком выходного сигнала, блок 2 настройки параметров, групповой демультиплексор 3,блок 4 регистров, анализатор 5 входного и выходного сигналов, генерато 6 пробных сигналов, блок 7 злементов И, блок 8 синхронизации и блок9 сумматоров, 10 ил 1 табл.1566319 иаМ Составитель В,ХромовРедактор В.Данко Техред Л.Олийнык Корректор М.Максимишинец Тираж 661 Подписное аказ 1220 НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб д. 4/5Изобретение относится к самонастраивающимся системам управления иможет быть использовано при созданиисистем управления нестационарнымиобъектами,5Цель изобретения - расширениеобласти функционирования адаптивнойсистемы путем обеспечения устойчивости системы в условиях недостаточногобогатства входного управляющего сигнала.На Фиг,1 изображена адаптивнаясистема управления; на фиг, 2 - анализатор входного и выходного сигналов на фиг, 3 - блок формированияадресов; на фиг. 4 - блок вычисленияопределителя 1-го порядка (1 = З,К);на фиг, 5 - блок формирования значения определителя 1-го порядка (1 = 20З,К); на фиг. 6 - селектор (1-1)адресный;на фиг, 7 - распределитель1-адресный (1 = 2,К); на фиг, 8блок вычисления определителя второгопорядка; на фиг. 9 - блок синхронизации; на Фиг, 10 - графики, поясняющие работу блока синхронизации,Система (фиг, 1) содержит подключенные к объекту 1 управления с датчиком выходного сигнала блок 2 настройки параметров, групповой демультиплексор 3, блок 4 регистров, анализатор 5 входного и выходного сиг 1налов, генератор 6 пробных сигнагюв,блок 7 элементов И, блок 8 синхронизации, блок 9 сумматоров.Для пояснения работы системы нафиг, 1 приняты следующие обозначения:Ц - внешний входной сигнал;Х - выходной сигнал объекта;ЙКрДИ - параметрические входные сигналы объекта;11 - координатный управляющий входной сигнал объекта;т - выходной сигнал анализаторавходного и выходного сигналов:Ц - пробный сигнал;ф р щрурА- выходные сигналы блока синхронизации,Анализатор 5 входного и выходногосигналов содержит (фиг, 2) блок 1 Оформирования адресов, блок 11 вычисления определителей второго порядка,Краспределителей 12 1-адресных55(К = и+ш), Кблоков 13 регистров,Кблоков 14 вычисления определителей 1-го порядка (1 = 3, 4,, К), блок 15 вычисления абсолютного значения сигнала, регистр 16 и компаратор 17.Для пояснения работы анализатора входного и выходного сигналов на фиг, 2 приняты обозначения:д 1 р дг 1 рр 1 дкрд - Кгрупп выходов блока 10формирования адрес.ов и еговыход;А р , А; - К-я группа выходов блока 10;Х(С.,), Ц(Т) - реализация первойгруппы входных сигналов анализатора входного и выходногосигналов в момент временид = 1,К;ш = 1,К, - ш-й выход из ш-йгруппы выходов блока 10 Формирования адресов; вычисленные значения всехопределителей 1-го порядка(значения др, определяемыеинформационным состояниемсоответствующих выходов 1-йгруппы блока формированияадресов, проставлены над этими выходами на Фиг, 2).значение определителя К-гопорядка;допуск на значение Д,1 от = ое,К,Блок 10 формирования адресов содержит (фиг. 3) Крегистров 17 сдви) га (К+1)-разрядных Кшифраторов 18, Ккомпараторов 19 и Кблоков 20 элементов И, причем первый блок 20 содержит Кэлементов И, второй К, третий - К,, 1-й - К+1(К)-й - три, т,е, всего в бло(К+2)(К - 3)ках 20-- + Кэлементов И,2Блок 14 вычисления определителя 1-го порядка, 1 = 3, 4, .., К, содержит (фиг, 4) 1 мультиплексоров 21, 1 селекторов 22 (1-1)-адресных и блок 23 Формирования значения определителя 1-го порядкаНа Фиг, 4 показаны дд,5 г дд, 5, дд Ер, дЕУЕ 1 групп входов блока вычисления определителя 1-го порядка; У,(й ), Ук(1) - эначениЯ сигналов Х (Г)р1,п и 0;(с), д = 1,ш, в момент времени й, а именноХ;(е) приЦ;.Ир) при5 15663Блок 23 формирования значения определителя 1-го порядка содержит(1-.1)-адресный содержит (фиг. 6) Сблоков 27 элементов И и блок 28 элементов ИЛИ, Распределитель 12 1-адресный содержит (фиг7) Сблоков 298элементов И,Блок 11 вычисления определителейвторого порядка содержит (фиг, 8)мультиплексоры 30-33, умножители 34и 35, инвертор 36 и сумматор 37. Блок8 синхронизации содержит (фиг, 9) генератор 38 импульсов, счетчики 39-41,регистры 42-44, компараторы 45-47,элемент НЕ 48, элемент И 49 и элемент 2050 задержки.Система работает следующим образом.Объект 1 управления представляетсобой основной контур самонастраивающейся системы, описываемый уравнением 25Х = (Ао + ЬА(1) + дК(СХ + (Во ++ Ь В(г) + Ь И(еП,и , ргде Х 6 К, вК - соответственно векто -ры состояния и управления объекта; 30А В 0 - матрицы номинальныхзначений параметровобъекта размером пкпи пщ соответственФ35 ЬА(Г), ЬВ(Т) - матрицы параметрических возмущений ЬК, ЬХ(С) - матрицы настраиваемыхкоэффициентов (параметрические входы 40объекта), вычисляемые в блоке настройкипараметров.Блок 2 настройки параметров реализует эталонную модель системы, описываемую уравнением 1 н = АХ+ 3 П, где Х РК" - вектор состояния модели, и алгоритмы настройки параметров объекта дК и ЬИ(й), синтезированные с помощью прямого метода Ляпунова в следующем видедкИ) = -ж 6 х;БАЙИ) = - або,Где Ь = Р.р Р симметрическая поло 55жительно определенная матрица пФп;Е = Х - Х - рассогласованиефмежду выходами системы и эталонноймодели, :е = сопятО,19 6Выходами блока 2 являются значения настраиваемых параметров ЬК(С) и АХИ(С).Блок 8 синхронизации формирует сигнал у, определяющий моменты выборки значений сигналов Х и П. Выбранные реализации сигналов Х и П поступают на информационные входы группового демультиплексора 3, который распределяет их по соответствующим двум из своих 2(п+ш) выходов в зависимости от сигнала А , поступающего на адресные входы от блока управленияВ результате значения сигналов Х и П записываются в блок 4, содержащий (и+в) регистров.В определенные моменты времениЕ +, (которые определяются сигналом р формируемым блоком синхронизации только что записанные реализации Х и П поступают в анализатор 5 входного и выходного сигналов, вычисляющий определитель ы матрицы ЕслиДс 1, где У - заданное минимально допустимое значение определителя, то входной сигнал системы недостаточно богат и для обеспечения работоспособности системы необходимо подать дополнительный пробный сигнал, и анализатор входного и выходного сигналов формирует сигнал г = 1, поступающий на один вход блока 7 элементов И, на два других входа которого поступают сигналы: с- от блока 8 синхронизации и П - от генератора 6 пробных сигналов.В этом случаепо окончании проверки выполнения условия богатства входного сигнала адаптивной системы (т.е. вычисления Ь) и до следующей проверки в течение времени Т -на вход объекта 1 управления поступает дополнительный пробный сигнал П от генератора 6 пробных сигналов, содержащий достаточное количество различных гармоник.Если 1 ь1, т, е, условия богатства входного сигнала адаптивной системы выполняются, то дополнитель-ный пробный сигнал подавать не следует, Рассмотрим работу анализатора 5 входного и выходного сигналов (фиг, 2), Основное назначение его - вычисление определителя Ь и формирование сигнала г, Поэтому сначала необходимо описать рекуррентную проце 156 б 319дуру вычисления определителя матрицы (п+ш) х(и+т),Рассмотрим матрицу У размером КК, где К = и+ш У(а)(н) т (Е) теИ)И) У,(,) У (,)У элементы которой У,(С ), УУ(1:),= 1,К, есть соответственно Х,( ), Х(Т) Х( ), а 1;( ), Н (.) Н (1 ) соответствейно. Матрица У заполняется по столбцам путем записи реализаций сигналов 7 , ь. = 1,К, в дискретные моменты времени3 = 1 К, Заф пишем определитель д матрицы У, разложив его .по К-му столбцу1) к 2 (к) где ддк, 3ЗО Й , , - определители матриц( К ) ( К в 1 ) , которые получаются из матрицы У путем вычеркивания К-го столбца и с оо тв ет 35 ственно первой, второй,К-й строки.При этом А представляет собой сумму произведений двух сомножителей, один из которых (У 1 = 401,К) поступает в момент времениа второй ( й к, ., е.к, з, д к.1, , 1 ) может быть вычислен к .моменту Спо реализации сигналов У;( ), 1 = 1,К, полученных в пред шествующие моменты времени 1 , С9 ееу 1 Г,еДанные определители в свою очередь можно разложить по элементам (К)-го50 столбца и т,д, В результате получена рекуррентная процедура вычисления всех определителей 1-го порядка матрицы У, образованной первыми 1 столбцами матрицы У путем разложения ее55 по элементам последнего столбца (т,е, по определителям (1-1)-го порядка матрицы Уобразованной первыми1-1 столбцами матрицы У). Блок формирования адресов работаетследующим образом (фиг, 3). Натактовый вход регистра сдвига 17от блока 8 синхронизации поступаетсигнал ( который представляетсобой последовательность единичныхимпульсов с частотой Е , равной тактовой частоте работы системы, На информационные входы всех регистров 17сдвига поступает сигнал у, которыйявляется последовательностью единичных импульсов частотой й = Го/К, появляющихся только на отрезке времени длиной., на котором осуществляется проверка выполнения условия богатства входного сигнала,В начальный момент времени содержимое всех разрядов регистров равнонулю. С приходом первого информационного импульса в первый разряд регистра 17 сдвига запищется единица, которая далее будет сдвигаться во второй, третий.К-й разряды данного регистра по мере поступления тактовых импульсов. Шифратор 19, формирует в двоичном коде адрес А; который является адресом строки матрицыУ, присутствующей в матрице У Е(141) .Пусть определитель матрицы У(1- 2,К) есть й , где д , 1 Еее- - фд - номера строк матрицы У,которые присутствуют в матрице Уе,Примем следующий порядок выборастрок: 1, ) д )) 1 е.Например, пусть У - матрица 55,а 1 = 3. Тогда количество определиз 5.телей 3 равно Сз3 2.10. Номера строк. 1 , д , д , образующие всевозможные матрицы У , представлены в таблице2 3 4 5 6 7 8 9 10Строка 11 1 1 1 1 1 1 2 2 2 32 2 2 3 3 4 3 3 4 43 4 5 4 5 5 4 5 5 5Такое правило, упорядочивающее выбор строк, положено в основу работы блока формирования адресов. Для того, чтобы соблюдалось правило.) дЕ, в блок введены компараторы 20, осуществляющие сравнениес 1, 1, с 1 и т,д. До тех пор, 9 15663пока содержимое 1 С регистра 17 с равно нулю АА . Конкретные значения 1 1, , 1соответствующих К групп выходов блока формирования адресов определяются номерами Квыходов соответствующих регистровсдвига, которые проставлены на фиг,2и 3,Через время К/Г единица запишется в (К+1)-й разряд регистра 17сдвига и поступит на тактовый входрегистра 171 сдвига, а на информационные входы регистров 17, и 17 поступит единичный сигнал у, Следователь но, единица запишется в первые разряды регистров 171 и 17 . Поскольку комбинация 1, = 1, 1 . = 1 ) являетсянедопустимой при принятом правиле упорядочивания 1 и 1 , то на выходе 20всех элементов И второго блока будутнули, При поступлении следующего импульса на информационный вход регистра17 сдвига единица сдвинется во второй1разряд, комбинация1, = 2, 11 = 125является разрешенной, и на выходе первого элемента И блока 20 появитсяединица и т,д, Таким образом, на выходах Кблоков 20 элементов И формируются сигналы, несущие информациюо номерах строк 1 1, .1 С 1,входящих в УС,. Компараторы 19 позволяют реализовать условие 1, ) 1 ))) 1 , (вместо шифраторов в блоке формирования адресов можно использовать двоичные счетчики тактовых им 35пульсов соответствующих регистровсдвига с обнулением счетчиков при поступлении сигнала о заполнении (К+1)-горазряда следующего регистра сдвига). 40Блок 14 вычисления определителей1-го порядка, 1 = З,К (фиг. 4) работает следующим образом, На информационные входы мультиплексоров 21 поступают сигналы У,(СС)У( С),, 45У(СС), а на адресные - сигналы А11 фА;, , А; с блока 10 формированияадресов. В результате мультиплексоры21 выбирают из множества 11(СС),Ук(СС)1 сигналы У;,(СС)э 50У, (СС) соответственно. На С информационных входов селекторов 22 поступают значения всех возможных определителей (1-1)-го порядка матрицы У,На 1-1 групп адресных входов Б-го55(Я = 1,1) селектора поступают адрес 1 сные сигналы 1,Сэ 11 З.13 Сд1 1 . 1, т.е. первые 1групп выходов блока 10 формирования 19 Оадресов, кроме Я-й, содержащие толькоразрешенные комбинации, Селектор выбирает иэ множества Д;,.;, всех возможных определителей (1-1)-го порядкаматрицы УС, значение того определителякоторый задан1 С" 15+ й"1 ф,.совокупностью адресов 1, , 1е ФФ1 ф фпоступающих на адресные входы селектора.Блок 23 формирования значений определителей 1-го порядка, 1З-К,(Б = 1,1) поступают на соответствующие два входа из 2 с. входов блока формирования значений определителей1-го порядка, который вычисляет значение определителя 1-го порядкаа;матрицы УС по значениямсигиалов У;(С С), , У; (СС) и опре 1 Сделителей (1-1) - го поряцка й;СЛ й С по формуле+ (-1) 1; И,);С, .;, (1)Блок 23 имеет две группы входовпо 1 в каждой. На входы первой группыпоступают сигналы У;,(СС), У;(С),У; (С), на входы второй -Д Сзультате реализуется вычислейие определителя по формуле (1),Блок 14 вычисления определителяК-го порядка имеет ту же структуру,что и блок вычисления определителя1-го (1 = З,К) порядка (фиг. 4) стой лишь особенностью, что вместогрупп входов 1 1,) С, 1, 5 С,ХСЗС имеем отдельные входы 1Г= К 1 = К 1= 1 - единственная разрешенная комбинация.Блок 11 вычисления определителейвторого порядка представлен на фиг.8.Он реализует формулуй, - т;(,) У; (Е ) - У;(,)У,(С. )Принцип работы блока не представляетсложностей.Селектор 22 (1-1)-адресный (фиг.б)имеет 1-1 информационных входов, накоторые поступают храняющиеся в блоке 13 С,регистров значения определителей (1-1)-го порядка 16; ,; , и1-1 групп адресных входов, Назначение селектора заключается в том чтобы выбрать из множества Р 1; ;определителей (1-1)-го порядка матри 1566319цы Утребуемый определителье. ; ;(Я = 2, 1-1) номера1е1е 1 строккоторого задаются адресными сигналами, поступающими от блока 10 форми 5рования адресов, Поскольку в данномустройстве принято следующее правилоФормирования адресов: д) 1 " ) )) 1 , то для того, чтобы на адресные входы селектора поступали лишьразрешенные комбинации адресов, неОбходимо на первую группу адресныхвходов подавать не все сигналы 11,)первой группы выходов блока 10 фор 15мирования адресов, а лишь 1-й,(1+1)-й,К-й; на вторую группу - (1-1)-й.1-й,, (К)-й выходы второй группы ь. , , на (8-1)-ю группу -(К-Я)-й выходы (8+1)-й группы 1+на (1+1)-ю группу - первый, второй. , (К+1)-й выходы 1-й группы 25выходов 11блока 10,е-Селектор содержит С блоков 27элементов И с 1 входами: на входы спервого по (1-1)-й поступают соответ, венно алы1ф 5-1 ф 5 с ЗО1 (из числа разрешенных комбинаций, т.е, 1) 1)1), на - 1-й вход - значение соответствующего определителяй; ;1 е" 515-"Таким образом, если в данный моментвремени блок 10 формирования адресовсформировал адрес Ь111" 11 а 1/18+1 е Уто ненулевой сигнал ьудет на выходетолько одного блока 27, к 1-1 входамкоторого подключены соответствующие 40е ( еВЫХОДЫ 1 у ву 2.З1 З. ру 1блока 10, а на выходах остальных блоков 27 будут нулевые сигналы. Выходыевсех С к блоков 27 элементов И подключены к входам блока 28 элементовИЛИ, в результате чего на выходе егобудет сигнал й, который,у,1 фи является выходным сигналом селектора.Распределитель 1-адресный (12,К) (фиг, 7) выполняет функцию,50обратную к функции селектора 1-адресного: записывает значение й; ; в1 е"регистр, соответствующий адресуРаспределитель, как ифф Э55селектор, имеет 1 групп входов поК+1 в каждой и еще один вход, покоторому поступает вычисленное значение определителя Л,, Распределитель содержит С блоков 29мэлементов И и имеет С выходов.Блок 8 синхронизации (фиг, 9) работает следующим образом. Генератор38 импульсов формирует последовательность с, тактовых импульсов частотой Г . Импульсы подсчитываютсясчетчиками 39 и 40. В регистрах 4244 записаны значения соответственно:И - количество импульсов, соответствующее периоду Т проверки условийбогатства входного сигнала адаптивной системы (Т = И /Г,), Ил - количество импульсов, соответствующеевременипроверки данных условий(ь. = ИлИ 3 ( Т), Ид - количествоимпульсов, соответствующее периодуД выборки значений сигналов Х и П(Ид= дел аС = С /К),Подсчитанное количество импульсов И сравнивается компараторами45-47 соответственно с И И, И;,.При И = И на соответствующем выходе компаратора 45 появляется единичный сигнал р, который несет информацию о следующем моменте получения реализаций входных и выходныхсигналов объекта управления. Крометого, по сигналу / = 1 осуществляется обнуление счетчика 40, Количествоимпульсов = 1 подсчитывает счетчик41, который формирует сигнал А- количество реализаций сигналов Х и П,взятых в различные моменты времени .(Аз = 1,2 К в двоичном коде),На выходе компаратора 46 формируетсясигнал Ы: приИ (И о= О, при И э,Ъ И о( = 1. После прохождения сигнала о( через элементНЕ 48 получаем сигнал с 7 ( 7 = 1 означает, что выполняется проверка условий богатства входного сигналаадаптивной системы), Сигналы о 7 и рпоступают на элементы И 49, В результате логического умножения сигналовр и о получается сигнал у, являющийся последовательностью импульсовчастотой Г /К, периодически появляющихся во время проверки условий богатства входного сигнала. При Ы = 1и Р= 1 осуществляется выборка значений сигналов Х и П.При И = И на соответствующем вытходе компаратора 47 появляется единичный сигнал, по которомуОсуществляется обнуление счетчиков 39 и 4113 14 1566319 Сигнал у проходит через элемент50 задержки, в результате чего образуется сигнал у . По сигналам у и у,осуществляется соответственно считыва 5ние и запись в блок 4 регистров.Синхронизация регистров 17 сдвига,блЬков 9, 26 и 37 сумматоров, блоков13 регистров, умножителей 24, 34 и 35,блока 2 настройки параметров, объекта 1 управления осуществляется по сигналу о . Временные диаграммы сигналовблока 8 синхронизации представлены нафиг, 10. Оценим время Г, в течениекоторого осущЕствляется проверка выполнения условий богатства входногосигнала адаптивной системы,Время , необходимое для получения всех определителей второго порядка д , определяется временем фор1, 1мирования всех возможных комбинаций11, ) с помощью двух (К+1)-разрядных регистров сдвига1е, = (К+1) -о 25 30 35 Формула изобретения Кроме того, необходимо также учестьвремя С. на подготовку к работе блокаформирования адресов (т.е. на перепал.нение регистра 17 сдвига), равное 40;Е с; - ,Е (К+1) =11о1 (К+1) С(К) - 1оК 50 Аналогично время й , необходимое для получения всех определителей третьего порядка д; ;, равно51%+1)3 И т.д, Время йнеобходимое для получения определителей (К)-го порядка, равно-1 1С = (К+1)о Необходимо также учесть время С выКчисления определителя К-го порядка:й - время формирования единственнойкразрешенной комбинации 1 к = 1, 1 =- .., 11 = К, Справедлива следующая оценкаК С ( (К+1)КГ,Окончательно получим, что минимальное времявыполнения проверки усломинвий богатства входного сигнала адаптивной системы равно+ (К+1)Период Д 1 выборки значений Х и П должен удовлетворять условию; й 1 ) 1 = 1,К. Следовательно,дС(К+1)1 к фПоложительный эффект о использования адаптивной системы состоит в следующем. За счет периодической проверки условий богатства входного сигнала обеспечивается устойчивая работа адаптивной системы как с эталонной, так и с настраиваемой моделью в тех случаях, когда имеющегося входного сигнала недостаточно.для требуемой настройки параметров, Это позволяет успешно решать задачи управления и идентификации, а также дает возможность расширить область функционирования адаптивных систем, распространив ее на объекты, в которых постоянная подача пробных сигналов нежелательна и допустима лишь на определенных режимах, когда имеющихся входных сигналов недостаточно для обеспечения работоспособности адаптивной системы. Адаптивная система управления, содержащая объект управления, первый информационный вход и выход которого подключены соответственно к первому и второму информационным входам блока настройки параметров, первый и второй выходы которого подключены соответственно к второму и третьему информационным входам объекта управления, о т л и ч а ю щ а я с я тем, что, с целью расширения области функционирования адаптивной системы путем обеспечения ее устойчивости в условиях недостаточного богатства входного управляющего сигнала, в нее введены групповой демультиплексор, блок регистров, анализатор входного и выходного сигналов, генератор пробных сигналов, блок элементов И, блок синхронизации и блок сумматоров, при чем выход объекта управления подключен к первому информационному входу

СмотретьЗаявка

4400178, 29.03.1988

ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

ГЛУМОВ ВИКТОР МИХАЙЛОВИЧ, ЗЕМЛЯКОВ СТАНИСЛАВ ДАНИЛОВИЧ, РУТКОВСКИЙ ВЛАДИСЛАВ ЮЛЬЕВИЧ, СИЛАЕВ АНДРЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G05B 13/02

Метки: адаптивная

Опубликовано: 23.05.1990

Код ссылки

<a href="https://patents.su/11-1566319-adaptivnaya-sistema-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Адаптивная система управления</a>

Предыдущий патент: Пропорционально-интегральный регулятор

Следующий патент: Устройство для программного регулирования температуры

Случайный патент: Устройство для получения многократной пены