Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

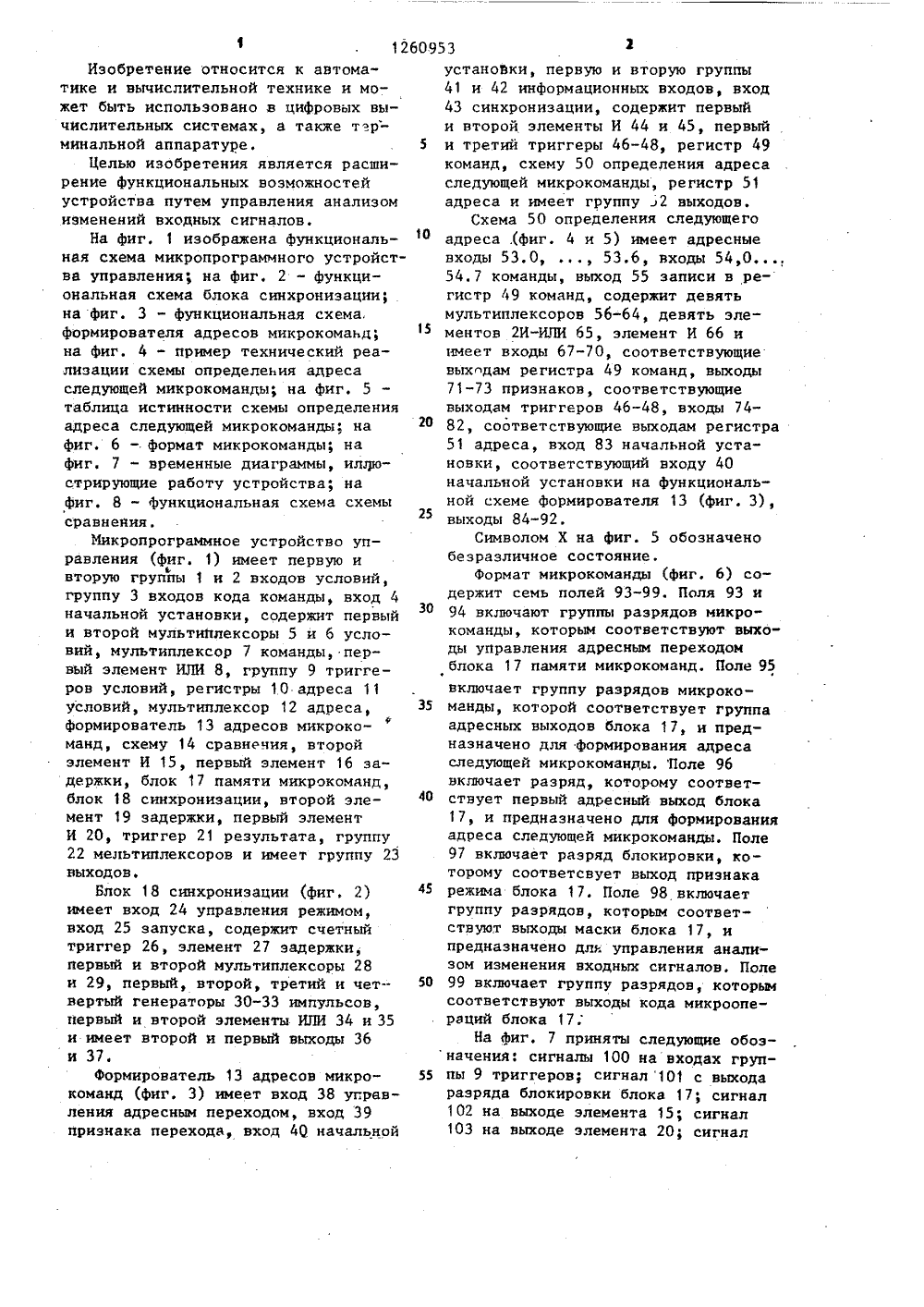

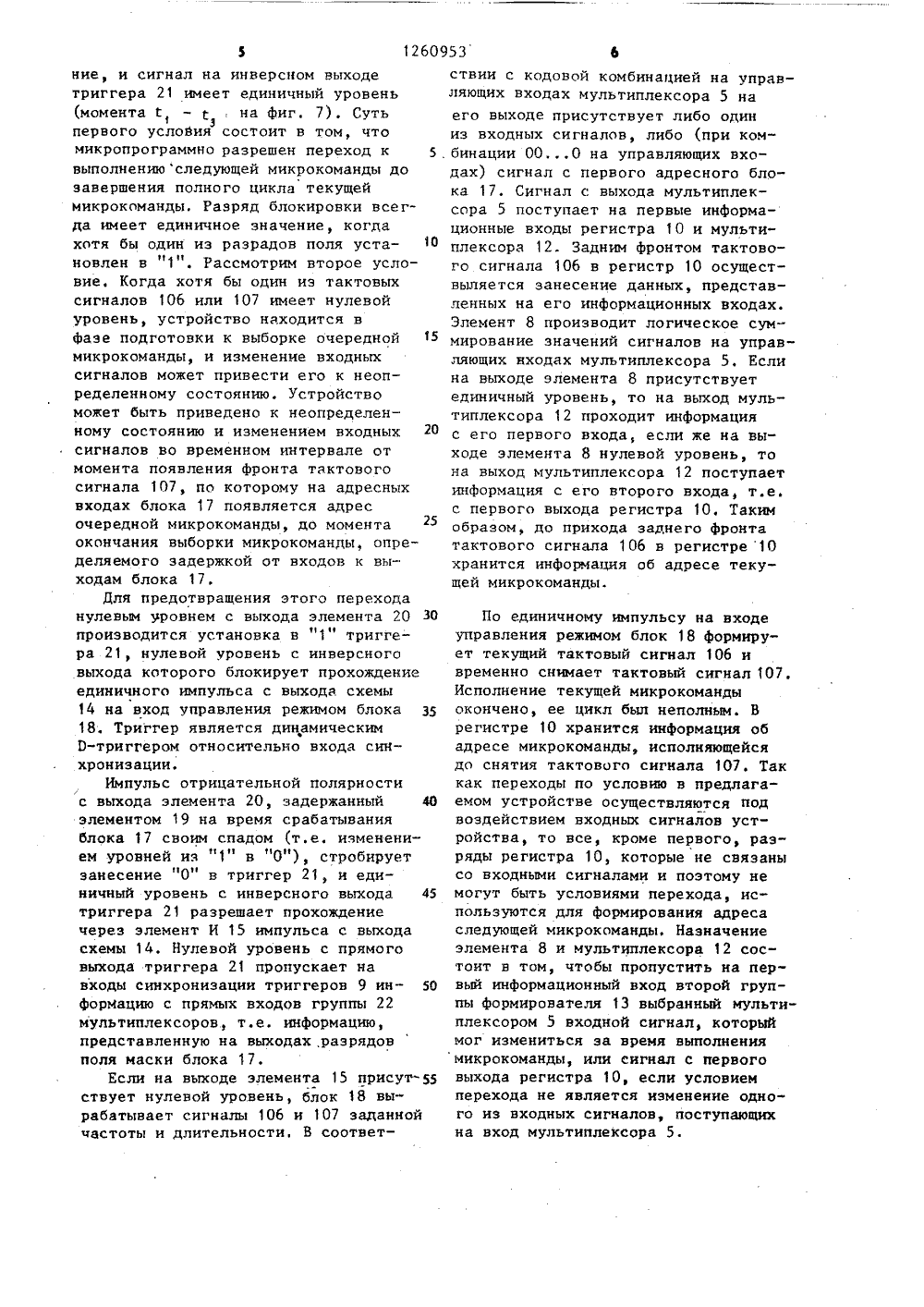

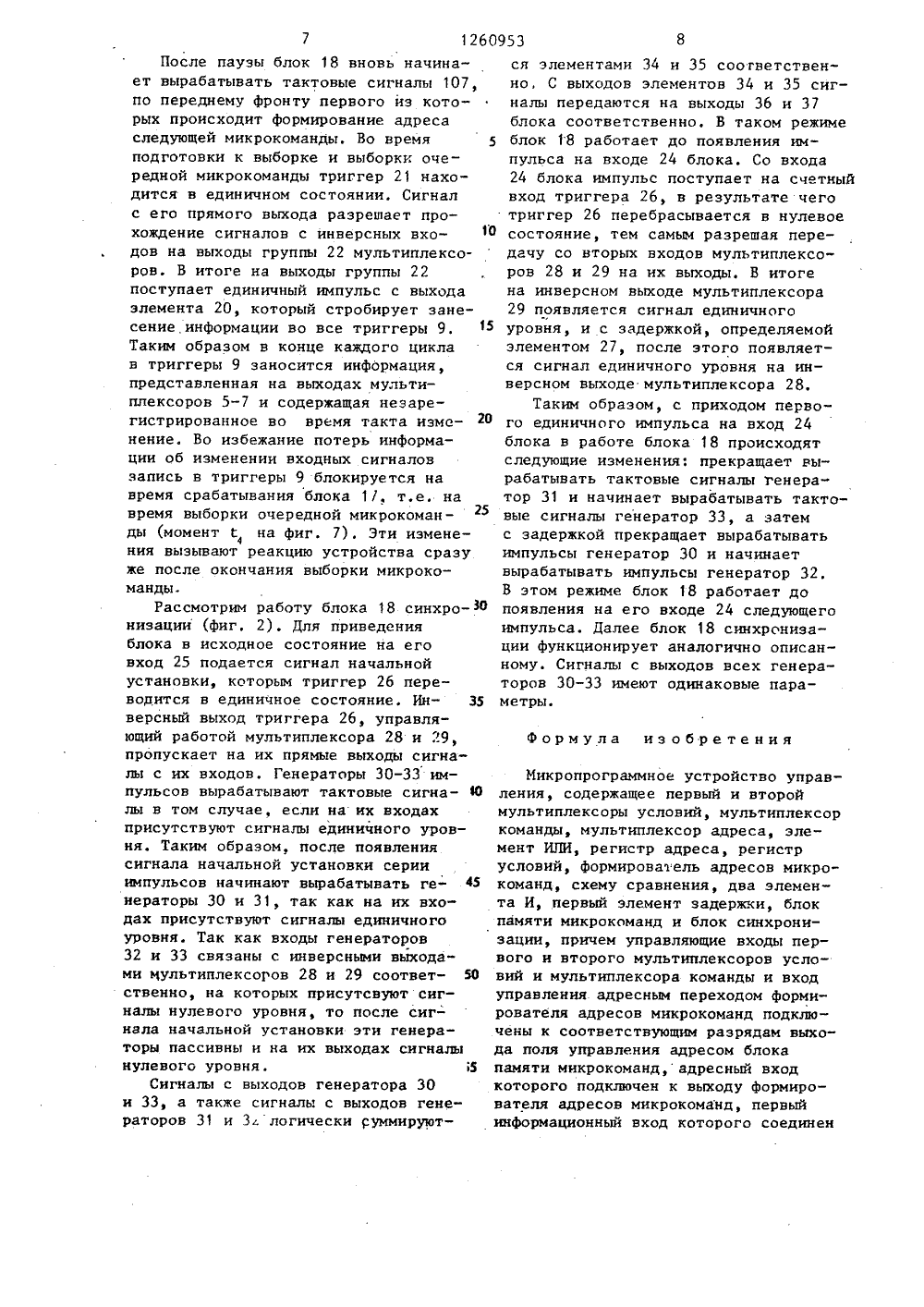

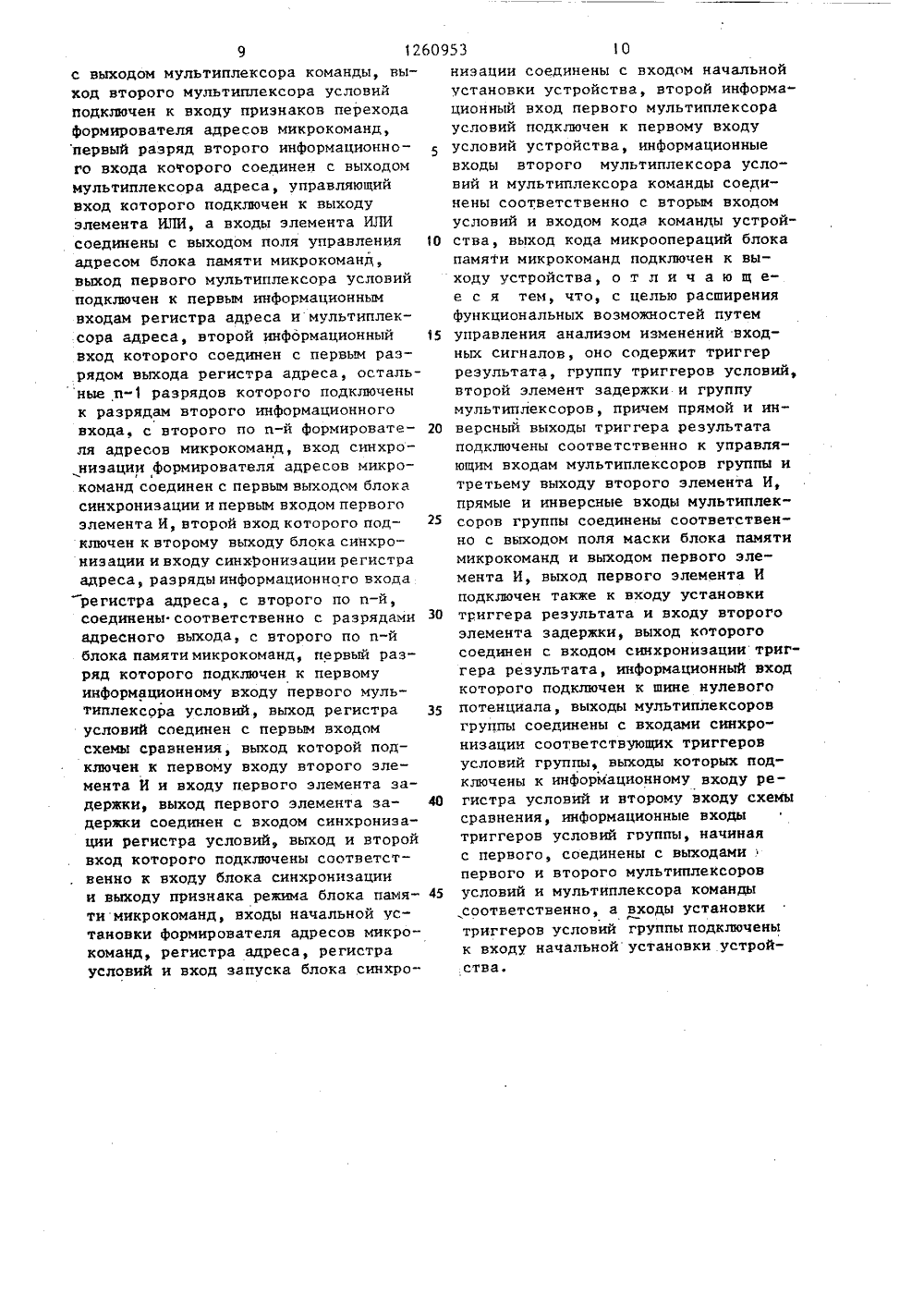

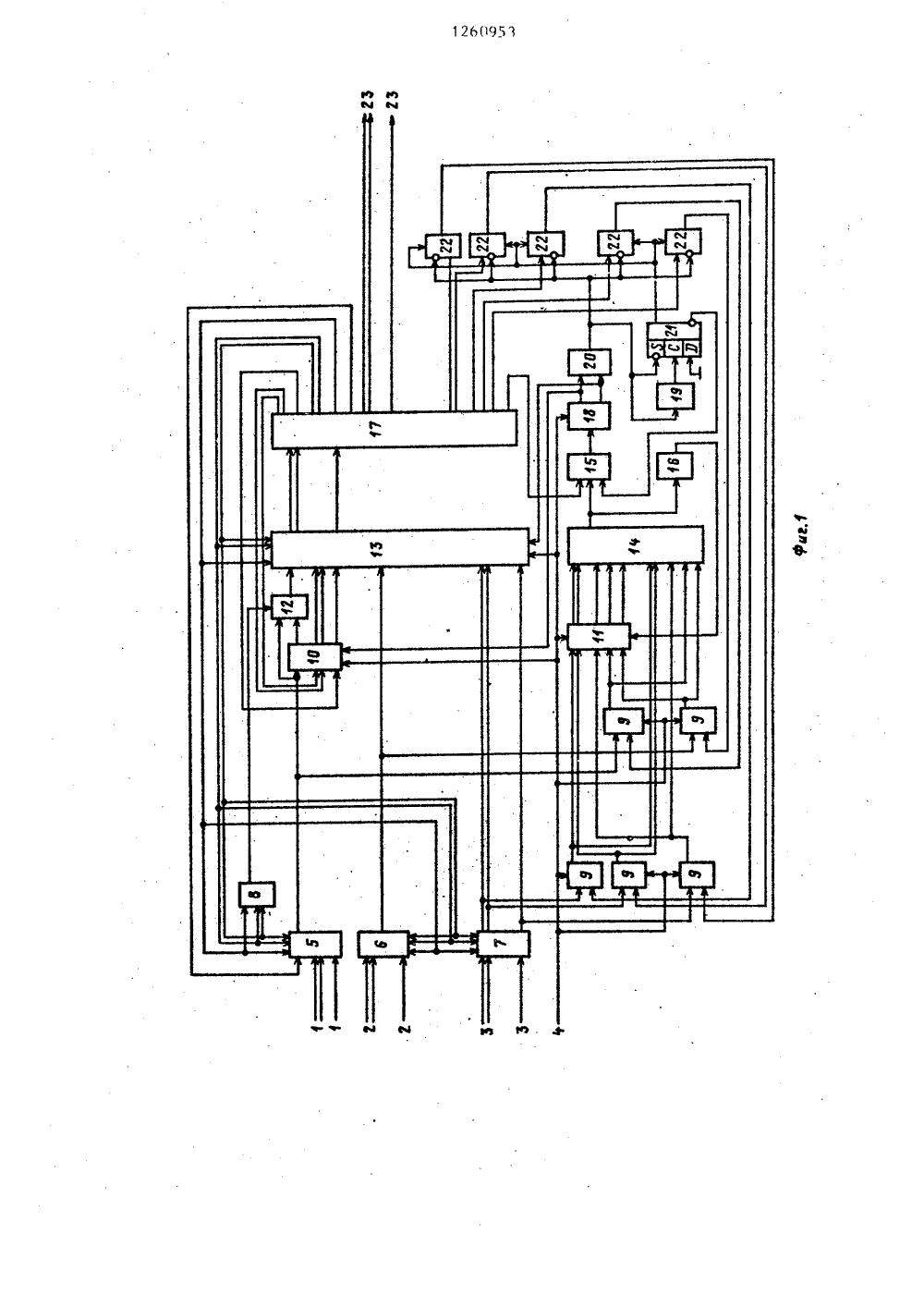

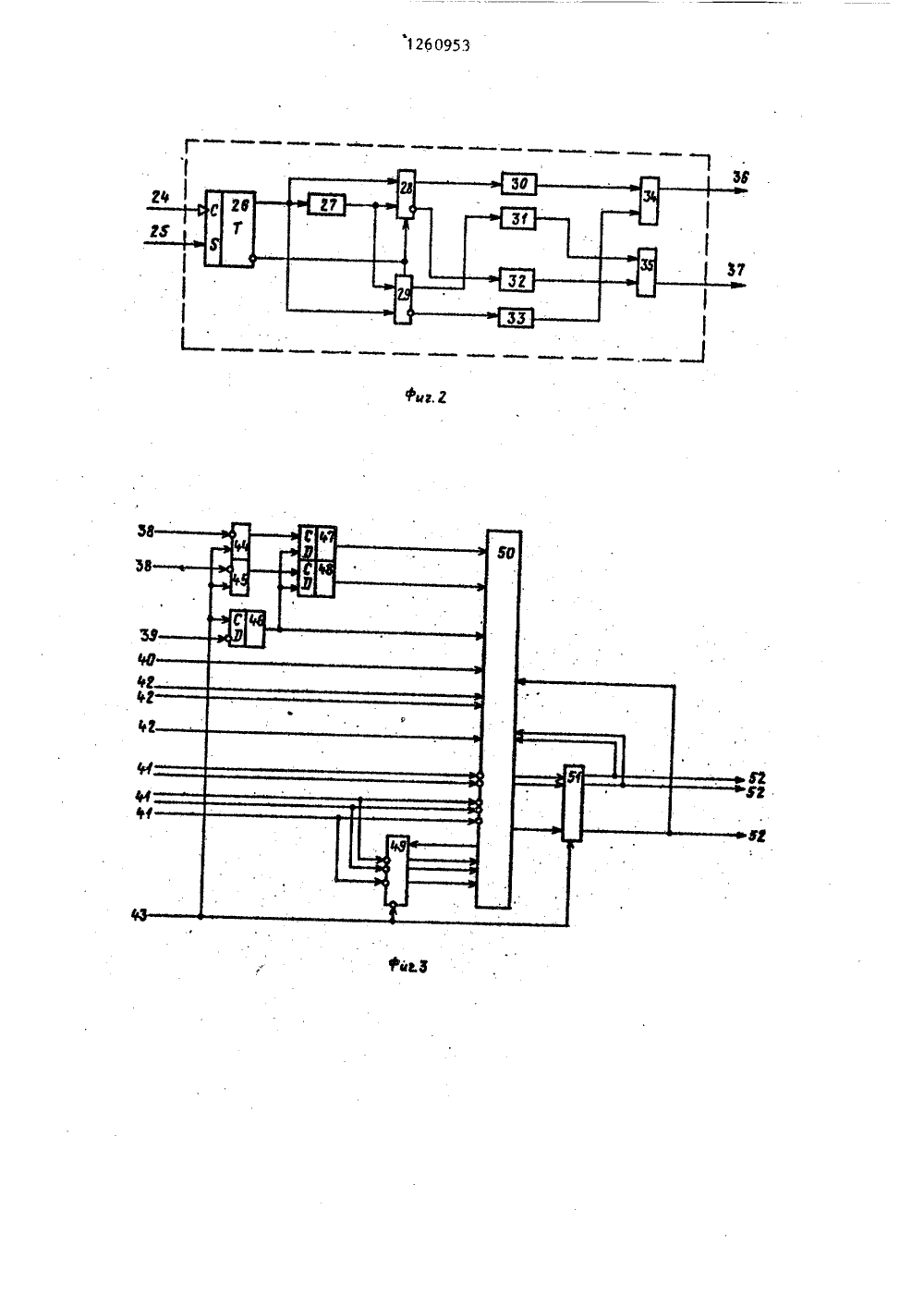

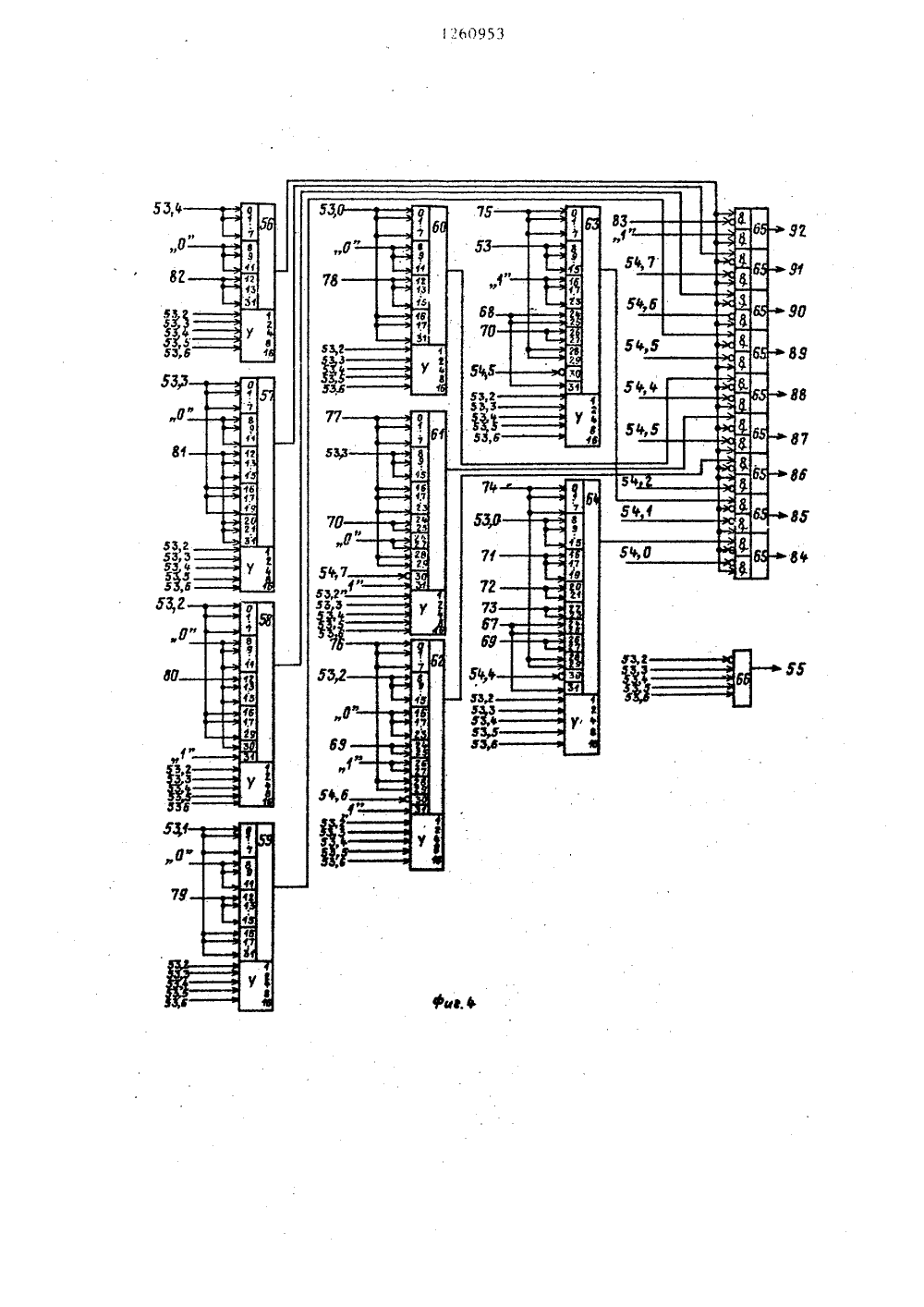

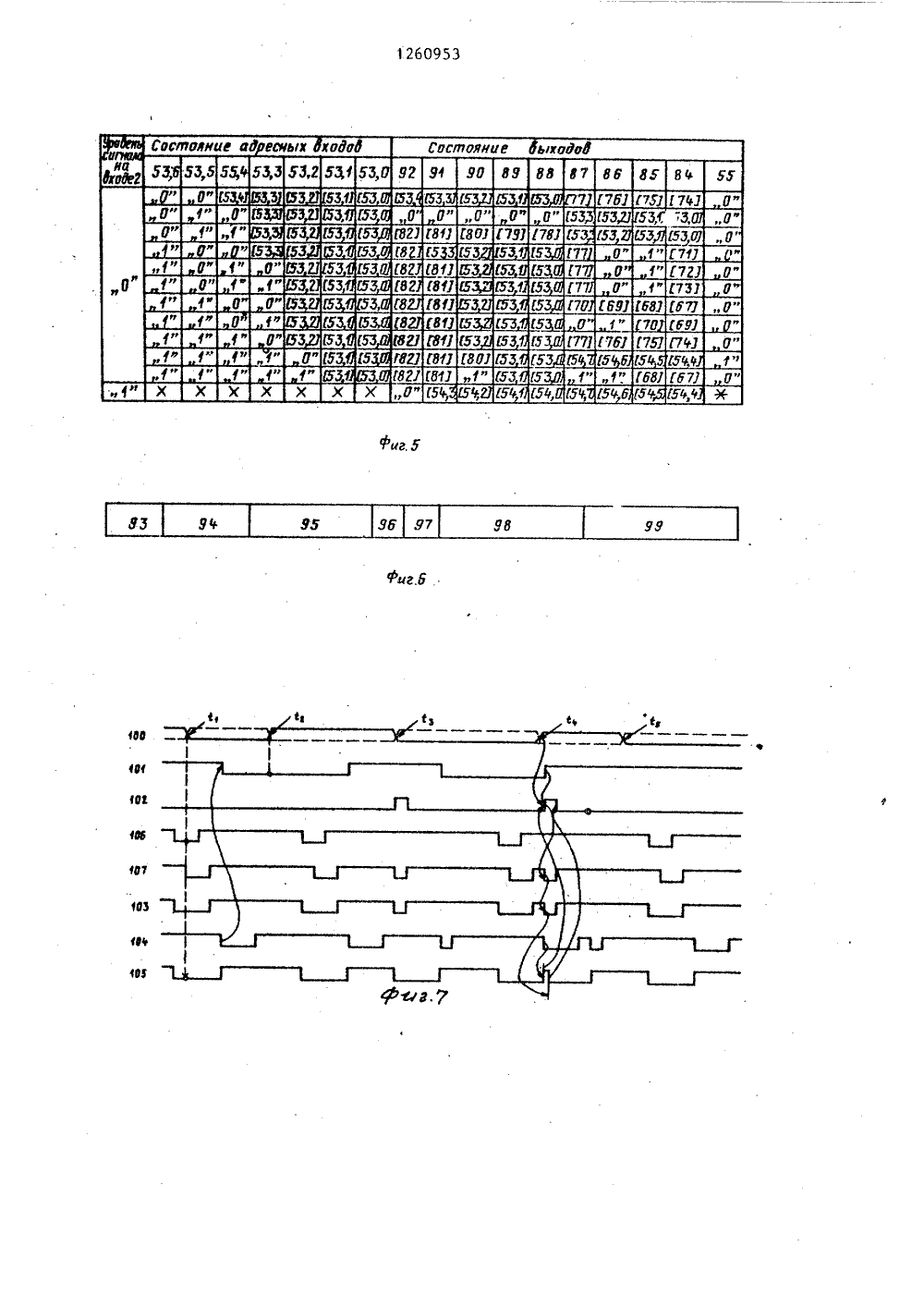

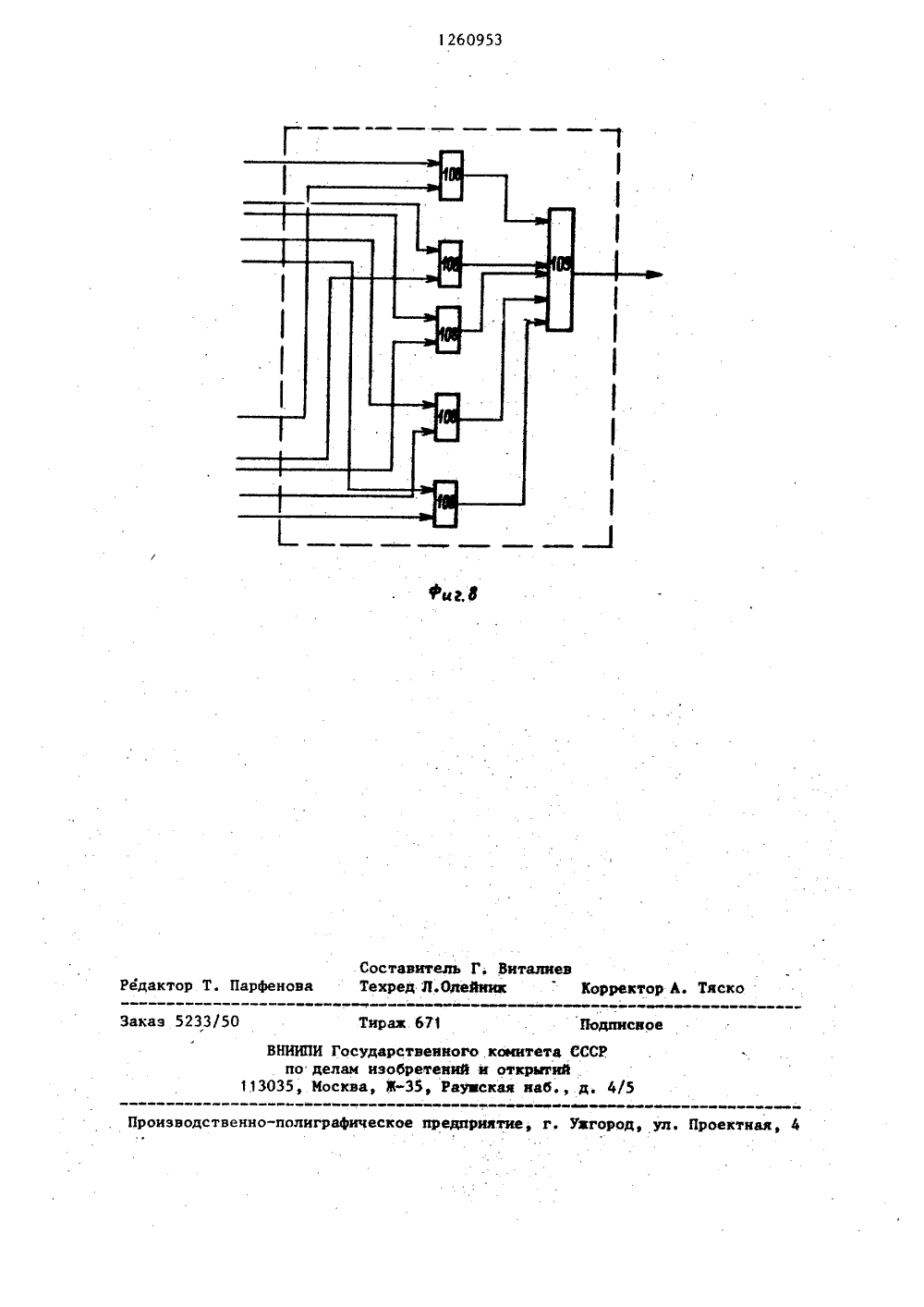

(19) (111 6 Г 9/2 НИЯ И 0 ИСА ЬСТВ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ А ВТОРСНОМУ СВИ(56) Авторское свидетельство СССР У 640294, кл. С 06 Р 9/22, 1978.Авторское свидетельство СССР В 1176328, кл. С 06 Г 9/22, 1984. (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, а также терминальной аппаратуре. Целью изобретения является расширение функциональных возможностей устройства путем управления анализом измененийвходных сигналов, С этой целью вустройство, содержащее первый и второй мультиплексоры условий, мультгплексор команды, мультиплексор адреса, элемент ИЛИ, регистр адреса, регистр условий, формирователь адресовмикрокоманд, схему сравнения, дваэлемента И, первый элемент задержки,блок памяти микрокоманд и блок синхронизации, введены триггер результата, группа триггеров условий, второйэлемент задержки и группа мультиплексоров. 8 ил.(7 Я ди ГОЛ ГВг Гб 81 Гб 7.Г уи 1 и Г 53 аи(54,4 Э иОи 1541 Г 54,154 б Х Х Сютввис ад юва одежд 1" О" 1 и 1 и уи 1 и Составное иадод ЮУ Г 531811 (ВО1260953 Составитель Г.Техред Л.Одейиик е Парфенова Редакт 671 Подписвенного комитета СССРетеиий и открытий3, Раувская иа 6., д. 4/5 33 За иое 33% 11303 Проек предприятие, г. Уагород И Государс делам изоб Москва, Жизводственно-полиграфическое орректор А. Тяско1 12Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, а также т рминальной аппаратуре,Целью изобретения является расширение функциональных возможностейустройства путем управления анализомизменений входных сигналов,На фиг. 1 изображена Функциональная схема микропрограммного устройства управления; на Фиг. 2 - Функциональная схема блока синхронизации;на фиг. 3 - функциональная схема,Формирователя адресов микрокомалд;на фиг4 - пример технический реализации схемы определеьия адресаследующей микрокоманды; на Фиг. 5таблица истинности схемы определенияадреса следующей микрокомандыф нафиг. 6 - формат микрокоманды; нафиг. 7 - временные диаграммы, иллюстрирующие работу устройства; наФиг. 8 - Функциональная схема схемысравнения.Микропрограммное устройство управления (фиг. 1) имеет первую иЬвторую группы 1 и 2 входов условий,группу 3 входов кода команды, вход 4начальной установки, содержит первыйи второй мультиплексоры 5 и б условий, мультиплексор 7 команды, первый элемент ИЛИ 8, группу 9 триггеров условий, регистры 10 адреса 11условий, мультиплексор 12 адреса,формирователь 13 адресов микрокоманд, схему 14 сравнения, второйэлемент И 15, первый элемент 16 задержки, блок 17 памяти мнкрокоманд,блок 18 синхронизации, второй элемент 19 задержки, первый элементИ 20, триггер 21 результата, группу22 мельтиплексоров и имеет группу 23выходов.Блок 18 синхронизации (фиг, 2)имеет вход 24 управления режимом,вход 25 запуска, содержит счетныйтриггер 26, элемент 27 задержки;первый и второй мультиплексоры 28и 29, первый, второй, третий и четвертый генераторы 30-33 импульсов,первый и второй элементы ИЛИ 34 и 35и имеет второй и первый выходы 36и 37.Формирователь 13 адресов микрокоманд (фиг. 3) имеет вход 38 ут;равления адресным переходом, вход 39признака перехода, вход 40 начальной 60953устанойки, первую и вторую группы41 и 42 информационных входов, вход 43 синхронизации, содержит первый и второй элементы И 44 и 45, первыйи третий триггеры 46-48, регистр 49команд, схему 50 определения адресаследующей микрокоманды, регистр 51адреса и имеет группу 2 выходов,Схема 50 определения следующегоадреса .(Фиг. 4 и 5) имеет адресныевходы 53.0, .., 53.6, входы 54,0.54.7 команды, выход 55 записи в регистр 49 команд, содержит девятьмультиплексоров 56-64, девять элементов 2 И-ИЛИ 65, элемент И 66 иимеет входы 67-70, соответствующиевыходам регистра 49 команд, выходы71-73 признаков, соответствующиевыходам триггеров 46-48, входы 7482, соответствующие выходам регистра51 адреса, вход 83 начальной установки, соответствующий входу 40начальной установки на функциональной схеме формирователя 13 (фиг. 3),выходы 84-92.Символом Х на фиг. 5 обозначенобезразличное состояние.формат микрокоманды (фиг. 6) содержит семь полей 93-99. Поля 93 и94 включают группы разрядов микрокоманды, которым соответствуют выходы управления адресным переходомблока 17 памяти микрокоманд. Поле 95включает группу разрядов микроко манды, которой соответствует группаадресных выходов блока 17, и предназначено для формирования адресаследующей микрокоманды, Поле 96включает разряд, которому соответ ствует первый адресный выход блока17, и предназначено для формированияадреса следующей микрокоманды. Поле97 включает разряд блокировки, которому соответсвует выход признака 45 режима блока 17. Поле 98 включаетгруппу разрядов, которым соответствуют выходы маски блока 17, ипредназначено для управления анализом изменения входных сигналов, Поле 50 99 включает группу разрядов, которымсоответствуют выходы кода микроопераций блока 17;На фиг. 7 приняты следующие обозначения: сигналы 100 на входах груп пы 9 триггеров; сигнал 101 с выходаразряда блокировки блока 17; сигнал102 на выходе элемента 15; сигнал103 на выходе элемента 20; сигнал104 на выходе элемента 19; сигнал 105на инверсном выходе триггера 21;сигналы 106 и 10 со второго и первого выходов блока 18 синхронизацииСхема 14 сравнения (фиг. 8) содержит группу 108 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ 109,Устройство работает следующимобразом.Для приведения устройства в исходное состояние на его вход 4 подается сигнал начальной установки,которым регистры 10 и 11, а такжегруппа 9 триггеров переводятся внулевое состояние, и по которому15блок 18 начинает вырабатывать сериитактовых сигналов 106 и 107. Крометого по сигналу начальной установкив формирователь 13 заносится первыйисполнительный адрес микропрограммы,поступающий на первые информационныевходы с выходов мультиплексора 7.Этот адрес появляется на выходахформирователя 13 с приходом фронтапервого тактового сигнала 107 свыхода блока 18.По адресу, представленному навыходах формирователя 13, происходитсчитывание микрокоманды иэ блока 17.Группы разрядов микрокоманды, като- ЗО,рым соответствуют выходы управленияадресным переходам блока 17 (т.е.поля 93 и 94 в формате микрокоманды),предназначены дгя управления работоймультиплексоров 5-7 и формирователя 13 соответственно. Группа адресных выходов блока 7 и сигналы свыходов мультиплексоров 5-7 используются для формирования адреса следующей микрокоманды. Разряд блокировки микрокоманды, которому соответствует выход управления режимомблока 17, предназначен для заданиярежима работы устройства во времяисполнения текущей микрокоманды. В 45том случае, если он установлен в "1",устройству разрешен переход к следующей микрокоманде до окончания полного цикла исполнения текущей микрокоманды, Если же разряд установлен 50в "0", устройство переходит к исполнению следующей микрокоманды толькопо окончании полного цикла исполнениятекущей микрокоманды. С соответствующих выходов блока 17 на выход 23 55устройства передается операционнаячасть микрокоманды, осуществляющаявоздействие на управляемуюмикропрограммным устройтствдм систему. Микро- команды исполняются за один такт.Рассмотрим работу устройства при выполнении произвольной микрокоманды.По фронту тактового импульса 107 наа выходах формирователя 13 формируется адрес, по которому происходит считывание микрокоманды из блока 17. Всоответствии с управляющими сигналами на выходе управления адреснымпереходом блока 17 на выходах мультиплексоров 5-7 присутствует определенная комбинация входных сигналов,которая подается на соответствующиеинформационные входы группы 9 триггеров типа защелка". На входах синхронизации триггеров 9 присутствуютуровни, определяемые значениями соотверствующих разрядов поля 98 маскиблока 17. Каждая микрокоманда допускает вполне определенное множествокомбинаций изменений входных сигналов устройства, ведущих к изменениюрежима работы, т,е. к переходу кследующей микрокомандедо окончанияполного цикла исполнения данной микрокоманды. Так в момент временипроисходит изменение режима работй(фиг. 7), а в момент временинет. В соответствии с этим кодируетсяполе маски. Те триггеры 9, которымсоответствуют установленные в "1"разряды поля маски, пропускают насвои выходы сигналы с информационныхвходов, те же триггеры, которым соответствуют разряды, установленные в"0", работают в режиме хранения, Вслучае несовпадения комбанации сигналов на выходах триггеров 9 и кода,записанного в регистр 11, схема 14вырабатывает единичный урбвень, который с задержкой, определяемой элементом 16, поступает на вход записирегистра 11, и в него записываетсякомбинация сигналов с выходов триггеров 9. Схема 14 вырабатывает сигнал нулевого уровня. Таким образом,если имело место несовпадение кодовна первом и втором входах схемы 14,она вырабатывает единичный импульс,длительность которого определяетсяэлементом 16,Единичный импульс с выхода схемы14 проходит на выход элемента 15 ипоступает на вход управления режимомблока 18 в том случае, если одновре-.менно выполняются два условия: разряд блокировки имеет единичное значе 1260953ние, и сигнал на инверсном выходетриггера 21 имеет единичный уровень(момента й, - с на фиг. 7). Суть3первого условия состоит в том, чтомикропрограммно разрешен переход к 5выполнению следующей микрокоманды дозавершения полного цикла текущеймикрокоманды, Разряд блокировки всегда имеет единичное значение, когдахотя бы один из раэрадов поля уста Оновлен в "1". Рассмотрим второе условие. Когда хотя бы один из тактовыхсигналов 106 или 107 имеет нулевойуровень, устройство находится вФазе подготовки к выборке очередной 15микрокоманды, и изменение входныхсигналов может привести его к неопределенному состоянию. Устройствоможет быть приведено к неопределенному состоянию и изменением входных 20сигналов во временном интервале отмомента появления фронта тактовогосигнала 107, по которому на адресныхвходах блока 17 появляется адресочередной микрокоманды, до моментаокончания выборки микрокоманды, определяемого задержкой от входов к выходам блока 17.Для предотвращения этого переходанулевым уровнем с выхода элемента 20 ЗОпроизводится установка в "1" тригге. -ра 21, нулевой уровень с инверсноговыхода которого блокирует прохождениеединичного импульса с выхода схемы14 на вход управления режимом блока з 518. Триггер является динамическим0-триггером относительно входа синхронизации.Импульс отрицательной полярностис выхода элемента 20, задержанный 40элементом 19 на время срабатыванияблока 17 своим спадом (т.е. изменением уровней из "1" в "0"), стробируетзанесение "0" в триггер 21, и единичный уровень с инверсного выхода 45триггера 21 разрешает прохождениечерез элемент И 15 импульса с выходасхемы 14. Нулевой уровень с прямоговыхода триггера 21 пропускает навходы синхронизации триггеров 9 информацию с прямых входов группы 22мультиплексоров, т.е. информацию,представленную на выходах, разрядовполя маски блока 17,Если на выходе элемента 15 присут ствует нулевой уровень, блок 18 вырабатывает сигналы 106 и 107 заданнойчастоты и длительности. В соответствии с кодовой комбинацией на управляющих входах мультиплексора 5 наего выходе присутствует либо одиниз входных сигналов, либо (при комбинации 000 на управляющих входах) сигнал с первого адресного блока 17. Сигнал с выхода мультиплексора 5 поступает на первые информационные входы регистра 10 и мультиплексора 12. Задним фронтом тактового сигнала 106 в регистр 10 осуществыляется занесение данных, представленных на его информационных входах.Элемент 8 производит логическое суммирование значений сигналов на управляющих входах мультиплексора 5, Еслина выходе элемента 8 присутствуетединичный уровень, то на выход мультиплексора 12 проходит информацияс его первого входа, если же на выходе элемента 8 нулевой уровень, тона выход мультиплексора 12 поступаетинформация с его второго входа, т.е.с первого выхода регистра 10. Такимобразом, до прихода заднего фронтатактового сигнала 106 в регистре 10хранится информация об адресе текущей микрокоманды. По единичному импульсу на входе управления режимом блок 18 формирует текущий тактовый сигнал 106 и временно снимает тактовый сигнал 107, Исполнение текущей микрокоманды окончено, ее цикл был неполным. В регистре 10 хранится информация об адресе микрокоманды, исполняющейся до снятия тактового сигнала 107. Так как переходы по условию в предлагаемом устройстве осуществляются под воздействием входных сигналов устройства, то все, кроме первого, разряды регистра 10, которые не связаны со входными сигналами и поэтому не могут быть условиями перехода, используются для формирования адреса следующей микрокоманды, Назначение элемента 8 и мультиплексора 12 состоит в том, чтобы пропустить на пер" вый информационный вход второй группы формирователя 13 выбранный мультиплексором 5 входной сигнал, который мог измениться за время выполнения микрокоманды, или сигнал с первого выхода регистра 10, если условием перехода не является изменение одного из входных сигналов, поступающих на вход мультиплексора 5.После паузы блок 18 вновь начинает вырабатывать тактовые сигналы 107, по переднему фронту первого из которых происходит формирование адреса следующей микрокоманды. Во время подготовки к выборке и выборки очередной микрокоманды триггер 21 находится в единичном состоянии. Сигнал с его прямого выхода разрешает прохождение сигналов с инверсных входов на выходы группы 22 мультиплексоров. В итоге на выходы группы 22 поступает единичный импульс с выхода элемента 20, который стробирует занесение информации во все триггеры 9. Таким образом в конце каждого цикла в триггеры 9 заносится информация, представленная на выходах мультиплексоров 5-7 и содержащая незарегистрированное во время такта изменение. Во избежание потерь информации об изменении входных сигналов запись в триггеры 9 блокируется на время срабатывания блока 17, т.е. на время выборки очередной микрокоманды (момент С, на фиг. 7). Эти изменения вызывают реакцию устройства сразу же после окончания выборки микрокоманды.Рассмотрим работу блока 18 синхро- З 0 низации (фиг, 2). Для приведения блока в исходное состояние на его вход 25 подается сигнал начальной установки, которым триггер 26 переводится в единичное состояние. Ин версный выход триггера 26, управляющий работой мультиплексора 28 и 29, пропускает на их прямые выходы сигналы с их входов. Генераторы 30-33 импульсов вырабатывают тактовые сигна лы в том случае, если на их входах присутствуют сигналы единичного уровня. Таким образом, после появления сигнала начальной установки серии импульсов начинают вырабатывать ге нераторы 30 и 31, так как на их входах присутствуют сигналы единичного уровня. Так как входы генераторов 32 и 33 связаны с инверсными выходами мультиплексоров 28 и 29 соответ ственно, на которых присутсвуют сигналы нулевого уровня, то после сигнала начальной установки эти генераторы пассивны и на их выходах сигналы нулевого уровня. 5Сигналы с выходов генератора 30 и 33, а также сигналы с выходов генераторов 31 и 3 логически суммируются элементами 34 и 35 соответственно. С выходов элементов 34 и 35 сигналы передаются на выходы 36 и 37 блока соответственно. В таком режиме блок 18 работает до появления импульса на входе 24 блока. Со входа 24 блока импульс поступает на счетный вход триггера 26, в результате чего триггер 26 перебрасывается в нулевое состояние, тем самым разрешая передачу со вторых входов мультиплексоров 28 и 29 на их выходы, В итоге на инверсном выходе мультиплексора 29 появляется сигнал единичного уровня, и с задержкой, определяемой элементом 27, после этого появляется сигнал единичного уровня на инверсном выходе мультиплексора 28,Таким образом, с приходом первого единичного импульса на вход 24 блока в работе блока 18 происходят следующие изменения: прекращает вырабатывать тактовые сигналы генератор 31 и начинает вырабатывать тактовые сигналы генератор 33, а затем с задержкой прекращает вырабатывать импульсы генератор 30 и начинает вырабатывать импульсы генератор 32, В этом режиме блок 18 работает до появления на его входе 24 следующего импульса. Далее блок 18 синхронизации функционирует аналогично описанному. Сигналы с выходов всех генераторов 30-33 имеют одинаковые параметры.Формула изобретенияМикропрограммное устройство управления, содержащее первый и второй мультиплексоры условий, мультиплексор команды, мультиплексор адреса, элемент ИЛИ, регистр адреса, регистр условий, формирователь адресов микро- команд, схему сравнения, два элемента И, первый элемент задеряии, блок памяти микрокоманд и блок синхронизации, причем управляющие входы первого и второго мультиплексоров условий и мультиплексора команды и вход управления адресным переходом формирователя адресов микрокоманд подключены к соответствующим разрядам выхода поля управления адресом блока памяти микрокоманд, адресный вход которого подключен к выходу формирователя адресов микрокоманд, первый информационный вход которого соединенс выходом мультиплексора команды, выход второго мультиплексора условийподключен к входу признаков переходаформирователя адресов микрокоманд,первый разряд второго информационного входа которого соединен с выходоммультиплексора адреса, управляющийвход которого подключен к выходуэлемента ИЛИ, а входы элемента ИЛИсоединены с выходом поля управления 1 Оадресом блока памяти микрокоманд,выход первого мультиплексора условийподключен к первым информационнымвходам регистра адреса и мультиплексора адреса, второй информационный 15вход которого соединен с первым разрядом выхода регистра адреса, остальные празрядов которого подключенык разрядам второго информационноговхода, с второго по и-й Формирователя адресов микрокоманд, вход синхронизации формирователя адресов микрокоманд соединен с первым выходом блокасинхронизации и первым входом первогоэлемента И, второй вход которого подключен к второму выходу блока синхронизации и входу синхРонизации регистраадреса, разряды информационного входарегистра адреса, с второго по п-й,соединены соответственно с разрядамиадресного выхода с второго по п-йблока памяти микрокоманд, первый разряд которого подключен к первомуинформационному входу первого мультиплексора условий, выход регистра 35условий соединен с первым входомсхемы сравнения, выход которой подключен к первому входу второго элемента И и входу первого элемента задержки, выход первого элемента задержки соединен с входом синхронизации регистра условий, выход и второйвход которого подключены соответственно к входу блока синхронизациии выходу признака режима блока памяти микрокоманд, входы начальной установки Формирователя адресов микрокоманд, регистра адреса, регистраусловий и вход запуска блока синхрониэации соединены с входом начальнойустановки устройства, второй информационный вход первого мультиплексораусловий подключен к первому входуусловий устройства, информационныевходы второго мультиплексора условий и мультиплексора команды соединены соответственно с вторым входомусловий и входом кода команды устройства, выход кода микроопераций блокапамяти микрокоманд подключен к выходу устройства, о .т л и ч а ю щ ее с я тем, что, с целью расширенияФункциональных возможностей путемуправления анализом изменений входных сигналов, оно содержит триггеррезультата, группу триггеров условий,второй элемент задержки и группумультиплексоров, причем прямой и инверсный выходы триггера результатаподключены соответственно к управляющим входам мультиплексоров группы итретьему выходу второго элемента И,прямые и инверсные входы мультиплексоров группы соединены соответственно с выходом поля маски блока памятимикрокоманд и выходом первого элемента И, выход первого элемента Иподключен также к входу установкитриггера результата и входу второгоэлемента задержки, выход которогосоединен с входом синхронизации триггера результата, информационный входкоторого подключен к шине нулевогопотенциала, выходы мультиплексоровгруппы соединены с входами синхро"низации соответствующих триггеровусловий группы, выходы которых подключены к информационному входу регистра условий и второму входу схемысравнения, информационные входытриггеров условий группы, начинаяс первого, соединены с выходами:первого и второго мультиплексоровусловий и мультиплексора командысоответственно, а входы установкитриггеров условий группы подключенык входу начальной установки устройства.

СмотретьЗаявка

3864651, 01.03.1985

ПРЕДПРИЯТИЕ ПЯ Р-6380

МИРЕЦКИЙ ИГОРЬ ЮРЬЕВИЧ, ВОЛОДИН АЛЕКСАНДР КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.09.1986

Код ссылки

<a href="https://patents.su/11-1260953-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для дифференцирования частотно-импульсных сигналов

Следующий патент: Микропрограммное устройство управления с динамической памятью

Случайный патент: Ускоритель многозарядных ионов