Устройство управления для селекторного канала

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

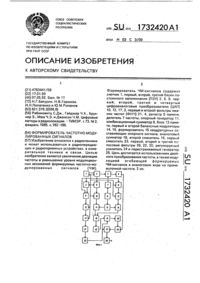

(56) Авторское свидетельство СССР1003066, кл. С Об Г 3/04, 1983,Авторское свидетельство СССР690472, кл. С 06 Р 3/04, 1976,(54) УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ СЕЛЕКТОРНОГО КАНАЛА(57) Изобретение относится к областивычислительной техники и может бытьиспользовано при разработке системыввода-вывода ЭВМ с микропрограммнымуправлением каналами ввода-вывода. И 9)8 Юв 1 238095 А 1 Целью изобретения является повышение скорости передачи данных каналапри работе с цепочкой данных за счетпредварительной выборки следующегоуправляющего слова канала. Устройствосодержит первый и второй регистрыфлажков, коммутатор флажков, первыйи второй счетчики адреса буфера, коммутатор счетчиков адреса буфера, первый и второй счетчики байтов буфера,коммутатор счетчиков байтов буфера,узел модификации, первый и второйрегистры анализа счетчика байтов, коммутатор счета байтов, первый и второйузлы сравнения, коммутатор сигналасравнения, первый второй узлы нулясчетчика, первый и второй коммутаторынуля счетчика, блок переключения,узел занесения. 11 ил, 12380951238095 Составитель Т. Лрешеедактор СЛисина Техред Л.Сердюкова Корректор Л, Пилипенко Тираж 671венного комитета СССРтений и открытий35, Раушская наб., д. 4/5 каз 3293/50 ВНИИПИ Государс по делам изобр 113035, Москва, Ж1238095 2 1Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при разработке системыввода-вывода ЭВМ, в частности для. управления работой аппаратуры обрамления буфера данных в селекторном канале,Цель изобретения - повышение скорости передать данных при работе сцепочкой данных.:Поставленная цель достигается тем,что. во время смены УСК при работес цепочкой данных канал одновременно может работать с двумя УСК, ОдноУСК используется для работы интерфейсом, а другое для работы с оперативной памятью.На Фиг, 1 представлена структурная схема устройства управления дляселекторного канала, на Фиг, 2 -функциональная схема первого регистра признаков второго регистрапризнаков, пятого коммутатора (показана коммутация флажка программноуправляемого прерывания); на Фиг.3 вкоммутация флажков цепочки команд,цепочки данных и подавления индикации неверной длины, а также коммутация Флажков блокировки записи в память и флажка косвенной адресации,на Фиг. 4 в ,функциональная схемапервого счетчика,адреса второго счетчика адреса, первого коммутатора, на.Фиг. 5 - функциональная схема первого счетчика байтов, блока модификации, второго счетчика байтов, второго коммутаторами на Фиг. 6 - первыйрегистр состояния счетчика байтов,второй регистр состояния счетчикабайтов, первая схема сравнения, вторая схема сравнения, третий и четвертый коммутаторы ; на фиг, 7 -первый дешифратор, второй дешифратор,шестой и седьмой коммутаторы нафиг. 8 - таблица переключения выходов блока задания режимов обмена;на фиг. 9 - блок задания режимовобмена, на Фиг, 10 - формировательсигналов занесения на фиг. 11распределение локальной памяти канала. 10 15 20 25 30 35 45 50 55 Устройство управления (фиг.1) содержит первый регистр 1 признаков, второй регистр 2 нриэнаков, первый счетчик 3 адреса, первый счетчик 4 байтов блок 5 модификации, первый регистр 6 состояния счетчика байтов, первую схему 7 сравнения, первый дешифратор 8, пятый коммутатор 9 флажков, второй счетчик 1 О .адреса, первый коммутатор 11, второй счетчик 12 байтов, второй коммутатор 13,второй регистр 14 состояния счетчика байтов, вторую схему 15 сравнения, третий коммутатор 16, четвертый коммутатор 17, второй дешифратор 18, шестой коммутатор 19, седьмой коммутатор 20, блок 21 заданиярежимов обмена, Формирователь 22 сигналов занесения, шину 23 данных устройства, информационную шину 24 устройства, управляющую шину 25 устройства, управляющий вход 26 устройства,коммутирующий вход 27 устройства,шину 28 счетчика .байтов, адреснуюшину 29 устройства, первый управляющий выход 30 устройства, второй управляющий выход 31 устройства.Блок 21 задания режимов обмена(Фиг.9) содержит триггеры 32-36,элемент 37 сложения по модулю два, элементы И в И 38-40, первый режимныйвыход 41, третий режимный выход 42,второй режимный выход 43,разрешающийвыход 44,Формирователь, 22 сигналов занесения (Фиг,10) содержит триггеры 45и 46, элементы И-ИЛИ 47 и 48, элементы И 49 и 50, эпементы ИЛИ 51 и 52, второй выход 53 формирователя,третий выход 54 Формирователя, первый выход 55 Формирователя,Первый регистр 1 признаков (фиг.2) содержит группу триггеров 56 и элемент И-ИЛИ 5. Второй регистр 2 признаков содержит группу триггеров 58и элемент И-ИЛИ 59. Пятый коммутатор 4 О 9 содержит элемент И-ИЛИ 60, три элемента И-ИЛИ 61 (фиг.3 а) и два элемента И-ИЛИ 62 (Фиг.Зб),Первый счетчик 3 адреса (фиг.4) содержит реверсивный двоичный счетчик 63, элемент И-ИЛИ 64, элемент ИЛИ 65-67. Второй счетчик 10 адреса содержит реверсивный двоичный счетчик 68 и элемент И-ИЛИ 69. Первый коммутатор 11 состоит из группы элементов И-ИЛИ 70Первый счетчик 4 байтов (фиг,5) содержит реверсивный двоичный счетчик 71, элемент И 72,. элемент И-ИЛИ 73, элементы ИЛИ 74-76. Блок модификации содержит сумматор 77, группу элементов И 78. Второй счетчик 12 байтов содержит реверсивный двоичный счетчик 79, элемент И 80, элемент И-ИЛИ 8 1, Второй коммутатор3 1238095 413 состоит из группы элементов или из второго регистра признаков посигналам с выходов блока 21 заданияПервый. регистр б состояния счет- режимов обмена. Первый 3 и второй 1 О,чика бантов (фиг.б). содержит регистр счетчики адреса предназначены для ука 83, элемент И-ИЛИ 84. Второй регистр 5 зания адреса байта в буфере (точнеесостояния счетчика байтов 14 содержит в двойном слове буфера, для чегорегистр 85, элемент И-ИЛИ 86, Первая достаточно трех разрядов) при записисхема 7 сравнения содержит группу в буфер байта данных с ШИН-А или приэлементов 87 сложения по модулю два, чтении байта данных из буфера наэлемент И 88, Вторая схема 15 сравне ШИН;Кния содержит группу элементов 89 сло- Входы 81, 82 двоичных реверсивныхжения по модулю два, элемент И 90. счетчиков служат для задания режимаТретий коммутатор 16 содержит группу работы счетчика; 00 - хранение ф 01элементов И-ИЛИ 91, элемент И 92, добавление единицы по сигналу наЧетвертый коммутатор 17 содержит эле входе С; 1 О - вычитание единицы помент И-ИЛИ 93, сигналу на входе С, 11 - занесениеПервый дешифратор 8 (фиг.7) со- информации с входа П по сигналу. надержит триггер 94, элемент И-ИЛИ 95,входе СВторои дешифратор 18 содержит триггер Первый коммутатор 11 предназначен96 элемент И-ИЛИ 97ЭИЛИ 97. Щестои комму для коммутации выходов первого 3 итатор 19 содержит элемент И-ИЛИ 98. второго 10 счетчиков адреса на адСедьмой коммутатор 20 содержит эле-ресную шину 29 устройства и далеемент И-ИЛИ 99. в буфер, где определяет адрес байтаИнформационная шина 24 устройства буфера, Первый 4 и второй 12 пятисодержит следующие линии: 100 - д 5 разрядные счетчики байтов служат длясигнал микропрограммной установки подсчета байтов, находящихся. в бутригге а 87 101Р , 1 в ,шина счетчика 1 Фере, Второй коммутатор 13 служит для102 - сигнал "Счетчик"Счетчик равен нулю11, коммутации выходов первого 4 и втбро 103 - шина константы для модифика- го 12 счетчиков байтов на вход блока.ции счетчика баитов в разделенном 5 модификации, Последний служит дляи.цикле, модификации первого 4 и второго 12счетчиков байтов в разделенных цикУправляющая шина 25 устройствалах на константу, которая поступаетсодержит следующие линии: 104 - сиг- на информационный вход блока 5 модинал сброса канала; 105 и 106 - синхро" Фикацикации по шине 1 , Если на входе103, Есигналы 107 и 108 - сигналы занесе- З 5 81 сусумматора (фиг.5) находится77 (ф .5)ния: 109 - об атный вво110 - единичныи сигнал, то выполняется сумчнал модификации счетчика адреса бу- мирование, а если нулевой - то вычифера, 111 - сигнал модификации счет- тание,ачика байтов буфера, 112 - сигнал за- Первый б и второй 14 регистры со несения в разделенном цикле, 1 13 - 40 стояния счетчика байтов предназначеввод; 114 - сигнал выполнения микро- ны для отображения состояния счетчипрограммы цепочки данных 115 - сиг- ка байтов расположенного в локал ной5ьнал УСК готово ; 116 - вывод, 117 - памяти, на аппаратуре канала. Занесевыполняется разделенный цикл. ние информации в регистры 6 и 14 син Управляющии вход 26 устройства хронизировано с занесением ее во втосодержит следующие линии адресации рую ячейку локальной памяти,При вылокальнои памяти; 118 - запись в полнении операций ввода регистр соседьмую ячейку локальной памяти; стояния счетчика байтов сравнивается119 - запись в восьмую ячейку локаль- со счетчиком байтов буфера и их раной памяти, 120 - запись.в первую 5 б венство говорит о том, что все данячейку. локальной памяти, 121 - запись ные по текущему УСК переданы в канал,Разрядность регистра состоянияч нПервыи и второи 2 регистры призна счетчика байтов зависит от размераков предназначены для хранения флаж- буфера. Для буфера в шестнадцать байков двух последовательных УСК, связан 55 тов регистр состояния счетчика байных флажком цепочки данных. Пятый ком. тов должен быть пятиразрядным (0-4)/мутатор 9 предназначен для объявления Шина 101 счетчика сделана такимдействительными флажками из пеового образом что в а. 0-4о в разряды - регистра1 23.809 5состояния заносятся разряды (3-7) младшего байта счетчика и байтов на локальной памяти, а на установку разрядов 0-2 регистра состояния заведена еще и сборка всех разрядов 5 старшего байта и разряды 0-2 младшего байта счетчика байтов из локальной памяти, это разрешает сравнение счетчика байтов буфера с регистром .состояния счетчика байтов только по сле того, как он начинает отображать действительное значение счетчика байтов из локальной памяти,Третий коммутатор 16 предназначен для коммутации на шину 28 счет чика байтов выходов первого 6 и второго 14 регистров состояния счетчика байтов в зависимости от состояния выхода 41 блока 21 задания режимов обмена, Если при вводе периферий ное устройство присылает сигнал УПР-А, когда еще счетчик байтов в локальной памяти не исчерпан, то с выхода блока управления интерфейсом поступает. сигнал на коммутирующий вход 27 уст ройства и в этом случае коммутируются выходы первого 4 или второго 12 счетчиков байтов буфера в зависимости от состояния выхода 41 блока 21 задания режимов обмена. 30Устройство управления каналами использует информацию с выхода третьего коммутатора 16 для формирования константы модификации адреса дан. ных и счетчика байтов, для формирования маски для оперативной памяти в разделенных циклах. Эта же константа по шине 103 поступает ка вход блока 5.Первая схема 7 сравнения служит 40 для сравнения первого счетчика 4 байтов буфера с первым регистром 6 состояния счетчика байтов. Сигнал сравнения с выхода узла сравнения говорит при вводе о том, что все байты 45 данных с периферийного устройствапереданы в канал. Вторая схема 15 сравнения служит для сравнения второго счетчика 12 байтов буфера с вторым регистром 14 состояния счетчика байтов.Четвертый коммутатор 17 служит для выбора сигнала сравнения с выходов первой 7 или второй 15 схем сравнения в зависимости от состояния вы хода 43 блока 21 задания режимов обмена, Первый 8 и второй 18 дешифраторы предназначены для фиксации в 6канале сигнала "Счетчик байтов равен нулю" в зависимости от состояния выходов 41 и 43 блока 21 задания режимов обмена. Этот сигнал .поступает по линии 102 из устройства управления каналами, когда второе слово УСК с нулевым счетчиком байтов считывается из оперативной памяти во вторую ячейку локальной памяти (сигнал 108), когда второе слово УСК с нулевым счетчиком байтов пересылается в микропрограммные предвыборки (при вводе) во вторую ячейку локальной памяти а также при выполнении последнего разделенного цикла, в котором нулевой после модификации счетчик байтов записывается во вторую ячейку локальч. ной памяти (сигнал 112). Необходимость в дешифраторах вызвана тем, что в канале может быть такое состояние, когда он хранит одновременно два сигнала "Счетчик равен нулю",Например, в предвыборке при вводе еще до получения сигнала "Счетчик равен нулю" для первого УСК может быть получен этот сигнал для второго УСК. Шестой 19 и седьмой 20 коммутаторы введены в связи с разделением функции сигнала "Счетчик равен нулю" по времени. Шестой коммутатор 19 осуществляет коммутацию по сигналу 43 выхода блока 21, а седьмой коммутатор 20 осуществляет коммутацию по сигналу 41 с выхода блока 21. Блок 21 задания режимов обмена предназначен для управления работой всех указанных блоков.Перенумеровывают все УСК, связанные флажком цепочки данных, начиная с того, в котором первым указан фла-, . жок цепочки данных, и ему присваивают первый номер (1,2,3,4). Состояние выходов блока 21 определяет следующее, 0 на выходе 41 - работа с оперативной памятью идет под управлением УСК с нечетным номером, 1 на выходе 41 - работа с оперативной памятью идет под управлением УСК с четным номером; 0 на выходе 43 - работа с интерфейсом идет под управлением УСК с нечетным номером; 1 на выходе 43 - работа с интерфейсом идет под управлением УСК с четным номером,На фиг. 8 показана последовательность переключения выходов блока 21 для ввода и вывода, если канал выполняет три связанных флажком цепочки данных УСК, Первая позиция в таблице,7 1238095 8 показывает исходное состоянис вы- ративной памяти первое слово первого ходов блока 21, в это же состояние УСК в первую ячейку локальной памятиблок 21 переходит после обработ- (фиг,1). При этом вырабатывается сигки прерывания в канале, Если более. нал 107 занесения, по которому код трех УСК связано Флажком цепочки дан операции заносится. в канал и устаных, то из позиции 6 блок переключе- навливается сигнал 113 "Ввод" на ния переходит в позицию 3 и т.д, управляющей шине 25 устройства, выФормирователь 22 сигналов занесе- полняется занесение трех младших ния .используется для выработки сигна- разрядов адреса данных с шины 23 данлов занесения на выходах 55 и 53, ес ных устройства в первый счетчик 3 адли выполняется микропрограмма предвы- реса (фиг.4), выполняется сброс перборки УСК при вводе или микропрограм- вого счетчика 4 байтов буфера (фиг.5) - ма цепочки данных при выводе. Канал заносятся нули в двоичный реверсивиспользует для работы восемь ячеек , ный счетчик 71 с выхода блока 5 моди- локальной памяти (Фиг,11).Первая и 15 фикации, в котором на входах группы вторая ячейки используются для хране-. элементов И 78 отсутствует сигнал 117 ния текущего УСК; третья ячейка - для разделенного цикла, Затем микропрохранения адреса УСК; седьмая и вось- грамма считывает второе слово первомая ячейки - для хранения предвы- го УСК, при этом вырабатывается сигбранного УСК, 20 нал 108 занесения, по которому выРассматривается работа устройства полняется занесение в первый регистр управления во встроенном селекторном признаков и в первый регистр 6 соканале с микропрограммным управлением. стояния счетчика байтов с шины 10 1 В этом случае шина 23 данных устрой- счетчика информационной шины 24 ства соединена с выходной шиной дан устройства (Фиг,6).ных центрального процессора, информа- Далее микропрограмма запускает ционная шина 24 устройства соедине- начальную выборку в канале и устана с выходом устройства управления навливает триггер "УСК готово" вканалами, управляющая шина 25 уст- блоке управления канала. Сигнал 115 ройства соединена с выходом блока . ЗО поступает на вход блока 21, В блоуправления каналом,управляющий вход ке 21 по совпадению сигналов на деся соединен с выходом блока локаль- , том (отсутствует сигнал 114 выполчнои памяти каналов, коммутирующий нения микропрограммы цепочки данных) вход 27 устройства соединен с вы- и одиннадцатом входах элемента И-ИЛИодом бло а управления интерфейсом, З 5 38 сигнал с его выхода переключает шина 28 счетчиксчетчика байтов соединена с триггер 32 в противоположное состоявходом устройства управления кана- ние (в этом случае в состояние "0") лами, адресная шина 29 устройства по синхросигналу 105, а по синхросоединена с блоком управления буфе- сигналу 106 устанавливается новое ром данных, первый и второй управля- що значение триггеров 33 36 и выходы 41Э У ющие выходы 30 и 31 устройства соеди блока пеоеключения переходят виены с входами блока управления ин- состояние "00".терфейсом.Канал работает следующим образом Пока аппаратура канала выполняЕтВ исходном состоянии после сбро- начальную выбоРку микропрограмма, есса канала или после сброса в начале ли есть флажок цепочки данных, леревыполнения цепочки команд (сигнал ходит к предвыборке второго УСК.Мик-104) выходы 41 и 43 блока 21 нахо- рокоманда МК 7 анализирует код опедятся в состоянии "01", триггеры 45 и46 Формирователя 22 сброшены. Расмат- правлениям. Далее в случае ввода или ривается выполнение трех УСК свя- ввода обРатного выполняет анализ на7занных Флажком цепочки данных в пер- самоопределенную цепочку В случае вом из которых задана операция ввода, . самоопределенной цепочки предвыборкане выполняется. Микрокоманда МК 9 счиОперация ввода-вывода (в этом слу- тывает первое слово УСК в седьмуючае операция ввода) инициируется ко ячейку локальной памяти, МК 10 выполмандои ввода-вывода "Начать ввод- няет анализ кода операции, если кодвывод (НВВ) Микропрограмма, реали- операции08" "Переход в канале, то,зующая команду НВВ считыв ает из опе- выполняется опять анализ на самоопре1238 деление и считывание первого слова УСК и анализ кода операции на "08". Микрокоманда МК 11 считывает второе слово УСК в восьмую ячейку локальной памяти, МК 13 устанавливает триггер 45 занесения Формирователя 22 сигналом микропрограммной установки 39,При выполнении МК 14 по сигналу 118 с выхода блока локальной памяти каналов и сброшенному триггеру 46 О предвыборки вырабатывается сигнал занесения с выхода 55, по которомумладшие три разряда адреса данных пред- выбранного УСК заносятся во второй счетчик 10 адреса и. происходит сброс 5 второго счетчика 12 байтов, как указано для первых счетчика адреса и байтов. Во время выполнения ЙК 15 по сигналу 119 с выхода блока локальной памяти вырабатывается сигнал 53 занесения, по которому выполняется занесение во второй регистр 14 анализа счетчика байтов и во второй ре-, гистр 2 признаков. Во время выполнения ИК 16 сигналом 100 микропрограммной установки с выхода устройства управления канала устанавливается триггер 46 предвыборки Формирова 30 теля 22, сигнал с выхода которого (есть сигнал 113 "Ввод")через элемент .И 50 и элемент ИЛИ 51 сбрасывается триггер 45 занесения. Затем микропрограмма предвыборки передает управление микропрограмме реализации команды НВВ, которая анализирует результат начальной выббрки и, еслион успешен, заканчивает выполнение НВВ с нулевым признаком результата, ПерифсФийное устройство, с которым канал устанавливает связь в начальной выборке, через некоторое время начинает передавать,цанные, которые поступают с шин абонента в канал и записываются в буфер согласно адре-. 45 су, который поступает на вход блока управления буфером с выхода первого счетчика 3 адреса буфера через коммутатор 11 счетчиков адреса буфера. Первый счетчик 3 адреса буфера моди фицируется на +1 ио сигналу 110 модификации с блока управления каналом, первый счетчик 4 байтов буфера моди- фицируется на +1 по сигналу 111 модификации. По мере поступления дан ных с интерфейса буфер заполняется, а когда первый регистр адреса бу,фера после очередной модификации по 095 1 О казывает границу двойного слова,данные иэ первого двойного слова буфера передаются в память в так называемом разделенном цикле, а. данныес интерфейса записываются во второедвойное слово буфера. В разделенномцикле двойное слово данных из буфераканала передается в оперативную память,.модифицируется адрес данных врегистре адреса данных канала, счетчик байтов во второй ячейке локальной памяти. Разделенный цикл - этоодна микрокоманда, аппаратурно формируемая в регистре микрокоманд по запросу из канала, вставляемая в любуюпоследовательность микрокоманд, выполняемых центральным процессором,В разделенном цикле выполняетсямодификация счетчика байтов буфераи регистра состояния счетчика байтов.Первый счетчик 4 байтов буфера уменьшается на константу, численно равнуюколичеству байтов, переданных изканала в оперативную память. Кодификация выполняется узлом 5 модификации, на первый вход которого поступает константа модификации по шине103 с выхода устройства управленияканалами. На второй вход узла 5поступает сигнал 1.17 разделенногоцикла, на третий вход поступает выход первого счетчика 4 байтов буферачерез коммутатор 13. счетчиков байтовбуфера (Фиг.5),: занесение модифицированного значения в первый счетчик4 байтов с выхода узла 5 модификациивыполнения по сигналу 112 занесенияв разделенном цикле,Счетчик байтов из локальной памятив разделенном цикле для модификациисчитывается на вход АЛУ, модифицируется и модифицированный записываетсяво вторую ячейку локальной памяти,Одновременно идет и занесение в первый регистр б анализа счетчика байтов с шины 101 счетчика с выхода устройства управления каналами, по сигналу 112 занесения в разделенном цикле а. Когда последний байт по первому УСК УСК принят в буфер, вырабатываетсясигнал сравнения с выхода первой схемы 7 сравнения, который проходит через коммутатор 17 на вход блока 21,а с выхода 30 устройства - в блокуправления интерфейсом, где определяет конец передачи данных при вводе, если в канале нет Флажка цепочки

СмотретьЗаявка

3723916, 11.04.1984

ПРЕДПРИЯТИЕ ПЯ М-5339

ВОРОНЦОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, КАРПЕЙЧИК ВИКТОР ВЛАДИМИРОВИЧ, МАЗИКИН БОРИС ВИКТОРОВИЧ, ПРОНИН ВЛАДИСЛАВ МИХАЙЛОВИЧ, РЫМАРЧУК АЛЕКСАНДР ГРИГОРЬЕВИЧ, ЯНОВСКАЯ АЛЛА ГЕОРГИЕВНА

МПК / Метки

МПК: G06F 13/12

Метки: канала, селекторного

Опубликовано: 15.06.1986

Код ссылки

<a href="https://patents.su/11-1238095-ustrojjstvo-upravleniya-dlya-selektornogo-kanala.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления для селекторного канала</a>

Предыдущий патент: Устройство для ввода информации от асинхронных абонентов

Следующий патент: Устройство для подключения абонентов к магистрали электронной вычислительной машины

Случайный патент: Способ охлаждения холодильной камеры