Система передачи и приема информации с коррекцией ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

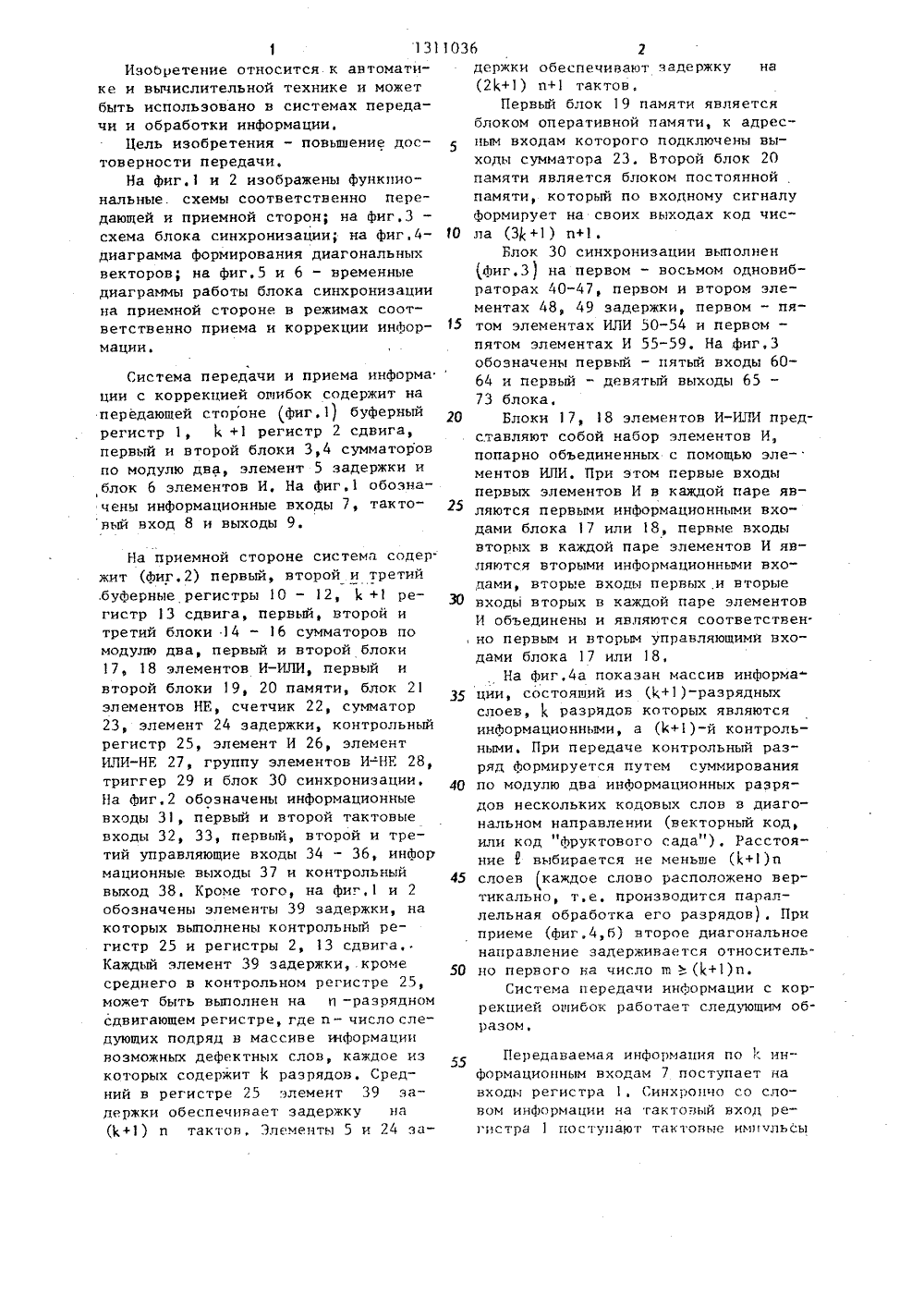

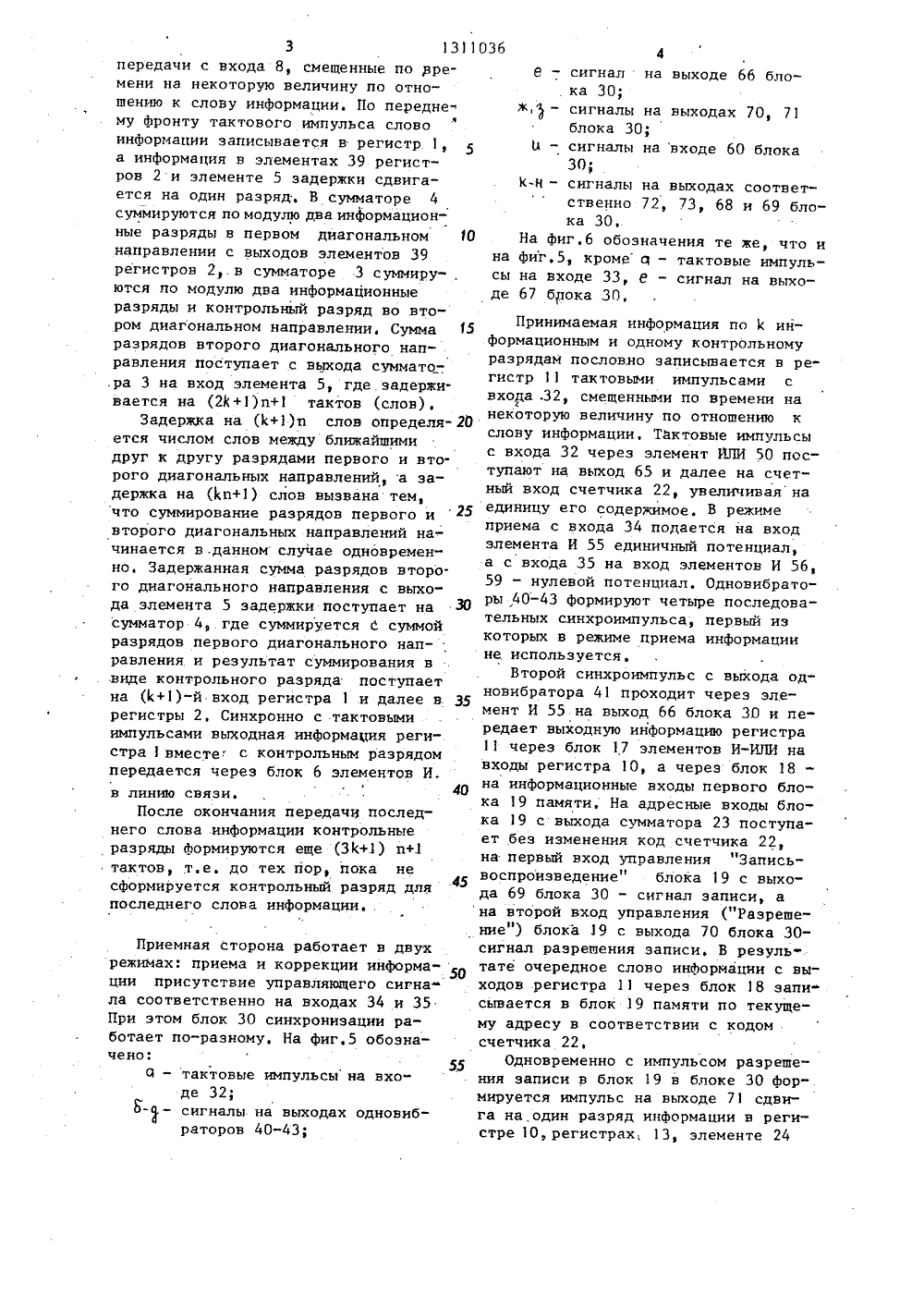

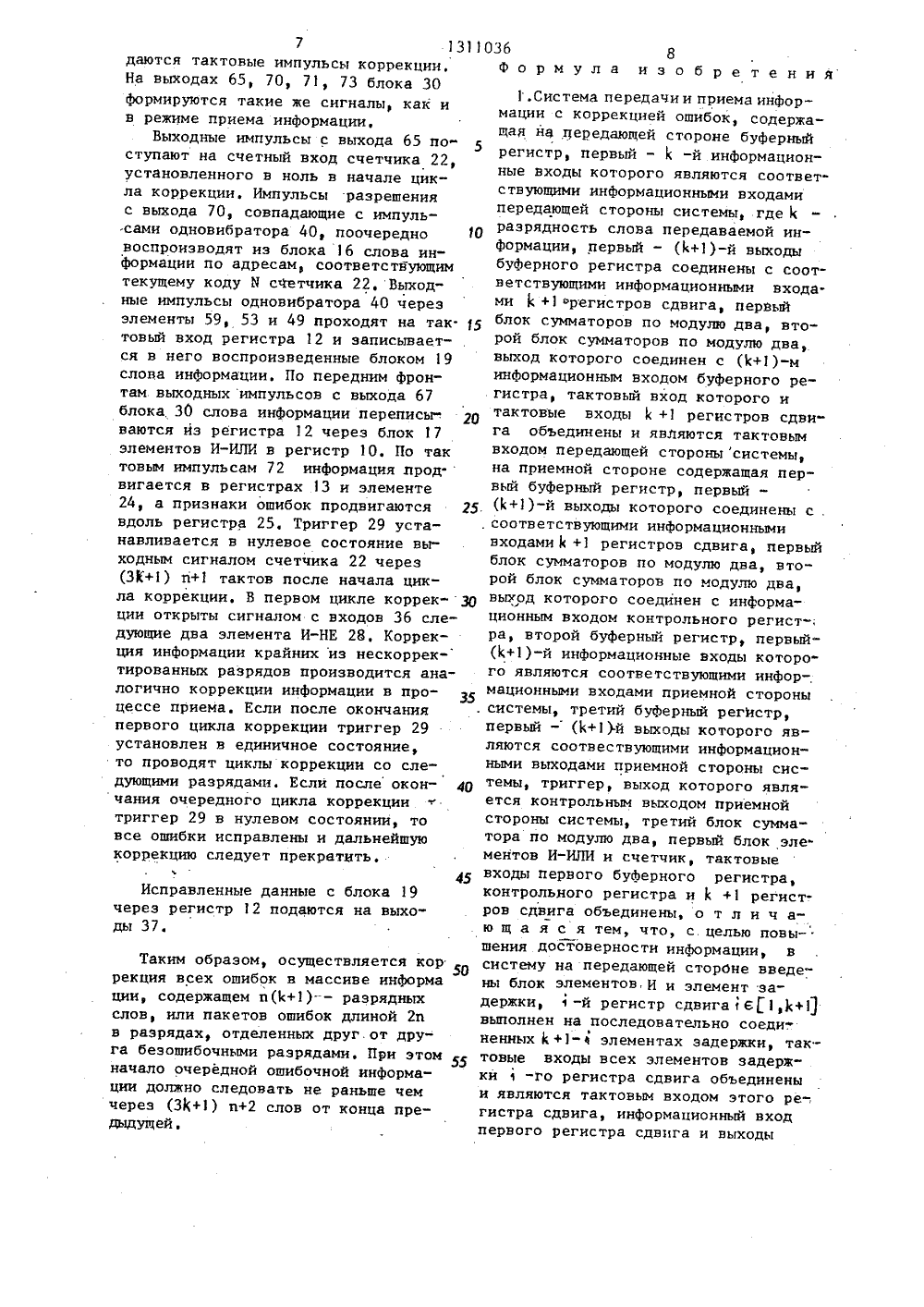

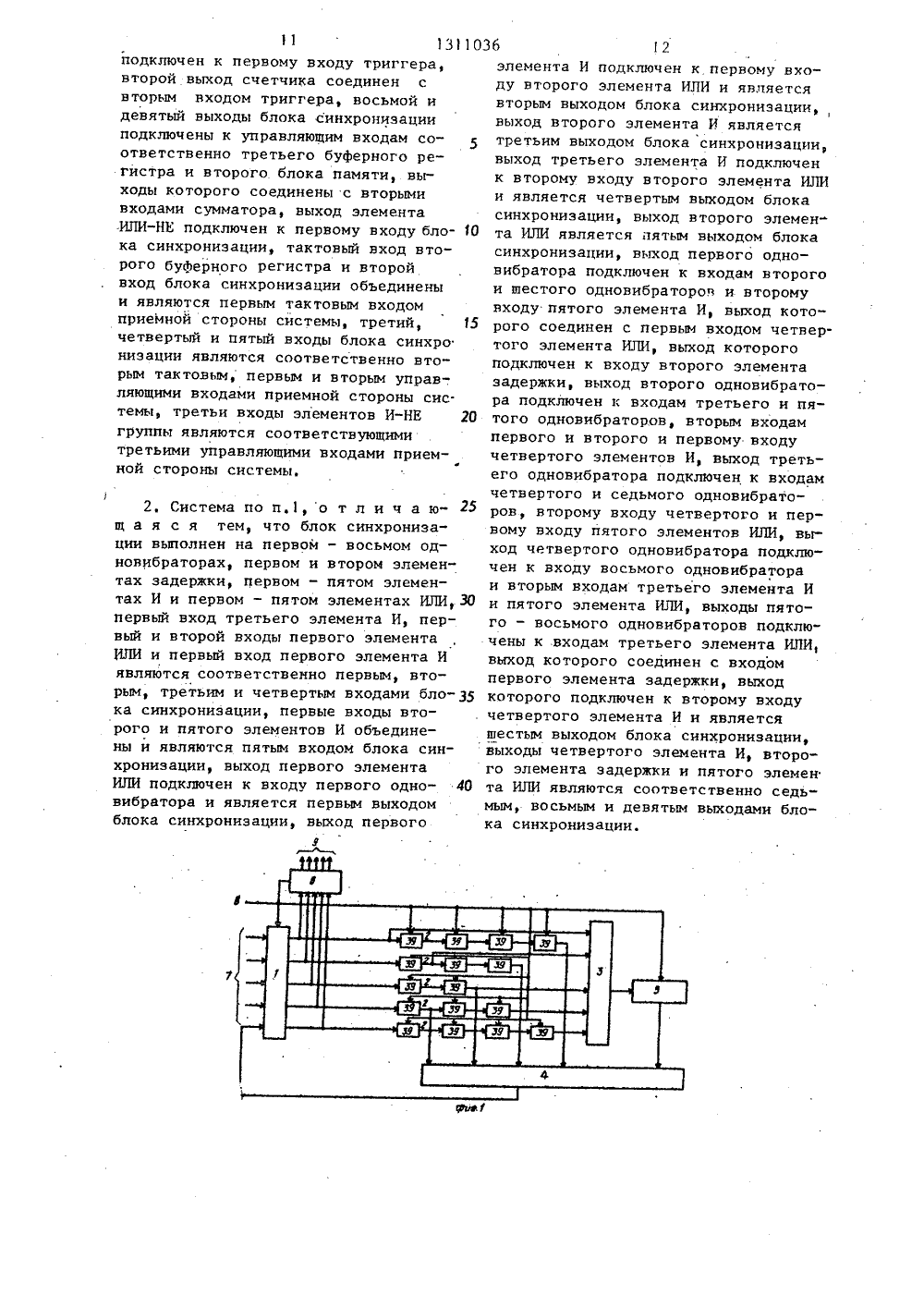

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 1191 а 1 59 4 Н 03 М 13/00 ЗОБРЕТЕНИЯ МАЦИ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к автоматике и вычислительной технике, Егоиспользование в системах передачи иобработки информации позволяет повысить достоверность передачи. Система содержит на передающей стороне буфе ный регистр, регистр сдвига и блоки сумматоров по модулю два, на приемной стороне содержит буферные регис ры, регистры сдвига, блоки сумматоров по модулю два, блок элементов И-ИЛИ, счетчик, контрольный регистр и триггер, Введение на передающей стороне элемента задержки и блока элементов И и на приемной стороне блока элементов И в И, блоков памяти, блока элементов НЕ, сумматора, элемента задержки, элемента И, элемента ИЛИ-НЕ, элементов И-НЕ и блока синхронизации обеспечивает.стопр центную коррекцию массива информаци из и (1+1)-разрядных слов, 1 з.п. ф-лы, 6 ил.Редактор М, Циткина Заказ 1903/5 б Тираж 902ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д.4/5 Подписное Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 41 131Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в системах передачи и обработки информации,Цель изобретения - повьпдение достоверности передачи,На Фиг,1 и 2 изображены Функциональные. схемы соответственно передающей и приемной сторон; на фиг.Зсхема блока синхронизации; на фиг,4 диаграмма формирования диагональныхвекторов; на фиг.5 и 6 - временныедиаграммы работы блока синхронизациина приемной стороне в режимах соответственно приема и коррекции информации,Система передачи и приема информа ции с коррекцией ощибок содержит на передающей стороне (фиг,1) буферный регистр 1, 1 +1 регистр 2 сдвига, первый и второй блоки 3,4 сумматоров по модулю два, элемент 5 задержки и блок 6 элементов И, На Фиг,1 обозначены информационные входы 7, тактовый вход 8 и выходы 9.На приемной стороне система содер. жит (фиг,2) первьгй, второй и третий .буферные регистры 10 - 12, 1 +1 регистр 13 сдвига, первый, второй и третий блоки 14 - 16 сумматоров по модулю два, первый и второй блоки 17, 18 элементов И-ИЛИ, первый и второй блоки 19, 20 памяти блок 21 элементов НЕ, счетчик 22, сумматор 23, элемент 24 задержки, контрольный регистр 25, элемент И 26, элемент ИЛИ-НЕ 27, группу элементов И-НЕ 28, триггер 29 и блок 30 синхронизации. На Фиг,2 обозначены информационные входы 31, первый и второй тактовые входы 32, 33, первый, второй и третий управляющие входы 34 - 36, инфор мационные выходы 37 и контрольный выход 38, Кроме того, на Фиг,1 и 2 обозначены элементы 39 задержки, на которых выполнены контрольный регистр 25 и регистры 2, 13 сдвига, Каждый элемент 39 задержки, кроме среднего в контрольном регистре 25, может быть выполнен на и -разрядном сдвигающем регистре, где и - число следующих подряд в массиве иформации возможных дефектных слов, каждое из которых содержит К разрядов, Средний в регистре 25 элемент 39 задержки обеспечивает задержку на (1+1) и тактов, Элементы 5 и 24 за 1036 2 45 50 55 5 го 15 20 25 30 35 40 держки обеспечивают задержку на (2+1) и+1 тактовПервый блок 19 памяти является блоком оперативной памяти, к адресным входам которого подключены выходы сумматора 23. Второй блок 20 памяти является блоком постоянной памяти, который по входному сигналу формирует на своих выходах код числа (3+1) и+1.Блок 30 синхронизации выполнен 1 фиг.З) на первом - восьмом одновибраторах 40-47, первом и втором элементах 48, 49 задержки, первом - пятом элементах ИЛИ 50-54 и первом - пятом элементах И 55-59, На фиг,З обозначены первый - пятый входы 60- 64 и первый - девятый выходы 65 73 блока,Блоки 17, 18 элементов И-ИЛИ представляют собой набор элементов И попарно объединенных с помощью элементов ИЛИ, При этом гервые входы первых элементов И в каждой паре являются первыми информационными входами блока 17 или 18, первые входы вторых в каждой паре элементов И являются вторыми информационными входами, вторые входы первых,и вторые нходь 1 вторых в каждой паре элементов И объединены и являются соответственно первым и вторым управляющими входами блока 17 или 18На Фиг,4 а показан массив информа" ции, состоящий иэ (к+1)-разрядных слоев, К разрядов которых являются информационными, а (1+1)-й контрольными, При передаче контрольный разряд Формируется путем суммирования по модулю два информационных разрядов нескольких кодовых слов в диагональном направлении (векторный код, или код "Фруктового сада"), Расстояние 1 выбирается не меныпе (+1)и слоев (каждое слово расположено вертикально, т.е, производится параллельная обра.ботка его разрядов), При приеме (Фиг,4,б) второе диагональное направление задерживается относитель. но первого на число щ(к+1)и.Система передачи информации с коррекцией опибок работает следующим образом. Передаваемая информация по 1; информационным входам 7 поступает на входы регистра 1Синхронно со словом информации на тактовый вход регистра 1 поступают тактовые импульсыПриемная сторона работает в двух режимах: приема и коРрекции информа О ции присутствие управляющего сигнала соответственно на входах 34 и 35 При этом блок 30 синхронизации работает по-разному. На фиг,5 обозначено:с - тактовые импульсына входе 32;сигналы на выходах одновибраторов 40-43; 55 3 3110передачи с входа 8, смещенные по времени на некоторую величину по отношению к слову информации. По переднему фронту тактового импульса словоинформации записывается в регистр. 1,а информация в элементах 39 регистров 2 и элементе 5 задержки сдвигается на один разряд, В сумматоре 4суммируются по модулю два информационные разряды в первом диагональном 10направлении с выходов элементов 39регистров 2,. в сумматоре 3 суммиру" .ются по модулю два информационныеразряды и контрольный разряд во втором диагональном направлении, Сумма 15разрядов второго диагонального направления поступает с выхода суммато-,.Ра 3 на вход элемента 5, где.задерживается на (2 М +1)и+1 тактов (слов) .Задержка на (1+1)и слов определяется числом слов между ближайшимидруг к другу разрядами первого и второго диагональных направлений, а задержка на (1 сп+1) слов вызвана тем,что суммирование разрядов первого ивторого диагональных направлений начинается в,данном случае одновремен"но, Задержанная сумма разрядов второго диагонального направления с выхода элемента 5 задержки поступает на 3 Осумматор 4, где суммируется с суммойразрядов первого диагонального направления и результат суммирования ввиде контрольного разряда поступаетна (К+1)-й вход регистра 1 и далее в 35регистры 2, Синхронно с тактовымиимпульсами выходная информация регистра 1 вместе с контрольным разрядомпередается через блок 6 элементов И,в линию связи,После окончания передачи последнего слова информации контрольныеразряды формируются еще (ЗК+1) и+1тактов, .т.е. до тех пор, пока несформируется контрольный разряд для45последнего слова информации 36 4В - сигнал на выходе 66 блока 30;ж,) - сигналы на выходах 70, 71блока 30;О - сигналы на входе 60 блока30К-Н - сигналы на выходах соответственно 72, 73, 68 и 69 блока 30.На фиг.б обозначения те же, что и на фиг.5, кроме О - тактовые импульсы на входе 33, Г - сигнал на выходе 67 бпока 30,Принимаемая информация по К информационным и одному контрольномуразрядам пословно записывается в регистр 11 тактовыми импульсами свхода,32, смещенными по времени наснекоторую величину по отношению кслову информации, Тактовые импульсыс входа 32 через элемент ИЛИ 50 поступают на выход 65 и далее на счетный вход счетчика 22, увеличиваянаединицу его содержимое. В режимеприема с входа 34 подается на входэлемента И 55 единичный потенциал,а с входа 35 на вход элементов И 56,59 - нулевой потенциал, Одновибраторы,40-43 формируют четыре последовательных синхроимпульса, первый изкоторых в режиме приема информациине. используется.Второй синхроимпульс с выхода одновибратора 41 проходит через элемент И 55 на выход 66 блока 30 и передает выходную информацию регистра11 через блок 17 элементов И-ИЛИ навходы регистра 10, а через блок 18на информационные входы первого блока 19 памяти, На адресные входы блока 19 с выхода сумматора 23 поступает без изменения код счетчика 22,на первый вход управления Записьвоспроизведение" блока 19 с выхода 69 блока 30 - сигнал записи, ана второй вход управления ("Разрешение") блока 19 с выхода 70 блока 30"сигнал разрешения записи. В резуль,тате очередное слово информации с выходов регистра 11 через блок 18 запи"сывается в блок 19 памяти по текущему адресу в соответствии с кодомсчетчика 22,Одновременно с импульсом разрешения записи в блок 19 в блоке 30 фор"мируется импульс на выходе 71 сдви"га на один разряд информации в регистре 10, регистрах, 13, элементе 24и в регистре 25. В сумматоре.15 суммируется по модулю два информационные и контрольный разряды в первом диагональном направлении, в сумматоре 14 суммируются инФормационные и 5 контрольный разряды ва втором диагональном направлении, Сумма разрядов второго диагонального направления, задержанная. элементом 24 на (21+1) и+1 тактов, суммируется по модулю два в сумматоре 15 с суммой разрядов первого диагонального направления.На выходе сумматора 15 формируется или единичный сигнал нарушения четности суммы по модулю два разрядов двух диагональных направлений, или нулевой сигнал при сохранении четно" сти суммы разрядов двух диагональных направлений, Единичные и нулевые сигналы сумматора 15 являются признака ми наличия и отсутствия ошибок и последовательно запоминаются в контрольном регистре 25.Каждый ошибочный разряд представ лен в регистре 25 двумя единичными признаками, которые располагаются через определенное количество разрядов друг от друга в зависимости отномера дефектного разряда, Импульсами с выхода 71 блока 30 признаки ошибок продвигаются в регистре 25 от его вхсща к выходу. На элементах И-НЕ 28 производится определение попарно совпадающих единичных признаков ошибок. Наличие ошибок в каждом раз 35 ряде слова определяется одним из элементов 28, соответствующим этому разряду, В процессе приема информации контролируется наличие попарно совпа. 40 дающих ошибок в двух крайних разрядах, Дпя этого на третьи входы двух соответствующих элементов 28 посту" пает единичный потенциал управляющей команды с входов 36, а на третьи 45 входы остальных элементов 28 поступает нулевой потенциал. При наличии совпадающих признаков ошибок на выходе соответствующего элемента 28 устанавливается нулевой потенциал, который поступает на установочные входы (к+2)-го - (2 МФ 1)-го элементов 39 задержки или элемента И 26, запрещая передачу совпадающих признаков ошибок в следующий разряд. ре" гистра 25, Нулевой сигнал с выхода элемента И-НЕ 28 через элементИЛИ-НЕ 2 поступает на первый вход блока 30, участвуя в образовании сигнала на выходе 69 и формируя сигнал на выходе 68, В блоке 30 с помощью одновибраторов 42 и 43 формируется сигнал на выходе 73, поступа- ющий на вход второго блока 20 памяти. По .этому сигналу на выходе блока 20 формируется код (3+1)п+1, который в сумматоре 23 вьчитается из кода И счетчика 22. По сигналу с вьг хода 70, совпадающему с импульсом одновибратора 42, в блоке 19 производится воспроизведение по адресу И-(31+1)пслова информации, которое по переднему фронту импульса 73 записывается в регистр 12 и поступает на первые входы двухвходовых сумматоров по модулю два блокч 16, На вторые входы сумматоров блока 16 поступают проинвертированные блоком 21 сигналы с выходов элементов И-НЕ 28. При наличии совпадающих признаков ошибок на второй вход соответствующего суматтора блока 16 поступает единичный сигнал. На выходах блока 16 образуется слово информации, скорректированное по первому и (+1) разрядам, которое через блок 18 по сигналу с выхода 68 поступает на информационные входы блока 19, где и записывается по тому же адресу импульсом разрешения с выхода 70, совпадающим с выходным сигналом одновибратора 43.Если признаки ошибок не совпали на элементах И-НЕ 28, то элемент ИЛИ-НЕ 27 Формирует нулевой сигнал, элемент И 57 блока 30 не вырабатывает на выходе 68 сигнала передачи информации с выхода блока 16 через блок 18, а на выходе 70 - сигнала записиинформации в блок 19. Слово информации по данному адресу в блоке 19 остается без изменений,Таким образом производится кор" рекция всех слов принимаемой информации, После окончания приема в блоке 19 будет записан весь массив принятой информации, скорректированный в первом и (+1) разрядахПри наличии нескорректированных ошибок они проходят на выход регистра 25 и устанавливают триггер 29 в единичное состояние, В этом случае необходимо провести дополнительную коррекцию информации, записанной в блоке 19,Для проведения коррекции на вход 35 подается ед иничный потенциал на вход 34 - нулевой, а по входу 33 по11036 8 формула изобретения 7 13 даются тактовые импульсы коррекции, На выходах 65, 70, 71, 73 блока 30 Формируются такие же сигналы, как и в режиме приема информации.Выходные импульсы с выхода 65 поступают на счетный вход счетчика 22, установленного в ноль в начале цикла коррекции. Импульсы разрешения с выхода 70, совпадающие с импуль-сами одновибратора 40, поочередно воспроизводят из блока 16 слова информации по адресам, соответствующим текущему коду И счетчика 22. Выходные импульсы одновибратора 40 через элементы 59, 53 и 49 проходят на так. товый вход регистра 12 и записывается в него воспроизведенные блоком 19 слова информации. По передним фронтам выходных импульсов с выхода 67 блока, ЗО слова информации переписьг". ваются из регистра 12 через блок 17 элементов И-ИЛИ в регистр 10. По так товым импульсам 72 информация прод" вигается в регистрах 13 и элементе 24, а признаки ошибок продвигаются вдоль регистра 25, Триггер 29 устанавливается в нулевое состояние выходным сигналом счетчика 22 через (ЗК+1) и+1 тактов после начала цикла коррекции. В первом цикле коррек-ции открыты сигналом с входов 36 следующие два элемента И-НЕ 28. Коррекция информации крайних из нескорректированных разрядов производится аналогично коррекции информации в процессе приемаЕсли после окончания первого цикла коррекции триггер 29 установлен в единичное состояние, то проводят циклы коррекции со следующими разрядами. Если после окончания очередного цикла коррекции с триггер 29 в нулевом состоянии, то все ошибки исправлены и дальнейшую коррекцию следует прекратить.ЪИсправленные данные с блока 19 через регистр 12 подаются на выхо" ды 37. Таким образом, осуществляется кор рекция всех ошибок в массиве информа ции, содержащем п(1+1) разрядных слов, или пакетов ошибок длиной 2 п в разрядах, отделенных друг от дру" га безошибочными разрядами, При этом начало очередной ошибочной информации должно следовать не раньше чем через (3+1) п+2 слов от конца предыдущей. 10 15 20 25 30 35 40 45 50 55 1.Система передачи и приема информации с коррекцией ошибок, содержащая на цередающей стороне буферный регистр, первый - 1 -й информационные входы которого являются соответ" ствующими информационными входами передающей стороны системы, где 1 разрядность слова передаваемой информации, первый - (1+1)-й выходы буферного регистра соединены с соответствующими информационными входа. ми+1 фрегистров сдвига, первый блок сумматоров по модулю два, второй блок сумматоров по модулю два, выход которого соединен с (1+1)-м информационным входом буферного регистра, тактовый вход которого и тактовые входы 1 +1 регистров сдви" га обьединены и явЛяются тактовым входом передающей стороны системы, на приемной стороне содержащая первый буферный регистр, первый - (1+1)-й выходы которого соединены с . соответствующими информационными входами к +1 регистров сдвига, первый блок сумматоров по модулю два, второй блок сумматоров по модулю два, выход которого соединен с информационным входом контрольного регистра, второй буферный регистр, первый- (1+1)-й информационные входы которого являются соответствующими инфор-, мационными входами приемной стороны системы, третий буферный регистр, первый - 9+1).й выходы которого являются соотвествующими информацион" ными выходами приемной стороны системы, триггер, выход которого является контрольным выходом приемной стороны системы, третий блок сумматора по модулю два, первый блок эле" ментов И-ИЛИ и счетчик, тактовые входы первого буферного регистра, контрольного регистра и 1 +1 регистров сдвига объединены, о т л и ч аю щ а я с я тем, что, с. целью повы-. шения достоверности информации, в систему на передающей стороне введе" ны блок элементов, И и элемент задержки,-й регистр сдвига61,1+11 выполнен на последовательно соеди-. ненных М +1-элементах задержки, тактовые входы всех элементов задерж" ки-го регистра сдвига объединены и являются тактовым входом этого ре-, гистра сдвига, информационный вход первого регистра сдвига и выходы10 единены с адресными входами первогоблока памяти, выходы второго буферного регистра подключены к соответ-.ствующим первым информационным входам блоков элементов И-ИЛИ, второйвыход блока синхронизации подключенк первым управляющим входам блоковэлементов И-ИЛИ, третий и четвертый выходы блока синхронизации соединеныс вторыми управляющими входами соответственно первого и второго блоковэлементов И-ИЛИ, выходы которых подключены к информационным входам соответственно первого буферного регистра и первого блока памяти, пятый ишестой выходы блока синхронизациисоединены с первым и вторым управляющими входами первого блока памяти,выходы которого соединены с информационными входами третьего буферногорегистра, выходы которого подключены к соответствующим вторым информационным входам первого блока элементов И-ИЛИ и первым входам третьегоблока сумматоров по модулю два, вьгходы которого соединены с вторымиинформационными входами второго блока элементов И-ИЛИ, выход первогоблока сумматоров по модулю два соединен с информационным входом элемента задержки, выход которого сое"динен с (1+2)-м входом второго блока сумматоров по модулю два, седьмойвыход блока синхронизации подключен 35 к тактовым входам элемента задержкии контрольного регистра, информаци-.онный вход и выходы первого - 1 -гоэлементов задержки контрольного регистра подключены к первым входам 4 О соответственно +1)-го - первого1элементов И-НЕ группы, выходыД+1)-го - (21+1)-го элементов задержки контрольного регистра подключены к вторым входам соответственнопервого - (1+1)-го элементов И-НЕгруппы, выходы которых подключены ксоответствующим входам элемента ИПИНЕ, соответствующим входам блока элементов НЕ, установочным входам соответственно (1 +1)- гопервого элементовзадержки контрольного регистра и соответственно к установочным входам(1+2)-го - (21+1)-го элементов задержки контрольного регистра и первому входу элемента И, выход(21+1)-го элемента задержки контрольного регистра соединен с вторымвходом элемента И, выход которого 9 1311036 (1 -1)-х элементов задержки 1 -х регистров сдвига, кроме, первого подключены к соответствующим входам перво. го блока сумматоров по модулю два, выходы (1+1" 1)-х элементов задержки-х регистров сдвига, кроме последнего подключены к соответствующим входам второго блока сумматоров по мо 1дулю два, выход первого блока сумматоров по модулю два соединен 10 с информационным входом элемента задержки, выход которого соединен сМ+Ц-и входом второго блока сум - маторов по модулю два, тактовые входы элемента задержки и блока элементов И объединены и подключены к тактовому входу передающей стороны системы, информационные входы блока элементов И подключены к соответствующим выходам буферного регистра, выходы блока элементов И являются соответствующими выходами передающей стороны системы, на приемной стороне системы введены первый и второй блоки памяти., блок элементов НЕ, второй блок элементов И-ИЛИ, элемент задержки, элемент ИЛИ-НЕ, группа из 1 +1 элементов И-НЕ, элемент И, сумматор и блоксинхронизации, контрольный регистр выполнен на последовательно соединенных 2 к+1 элементах задержки, информационный вход первого из которых является информационным входом контрольного регистра, тактовые входы элементов задержки контрольного регистра объединены и являются тактовым входом контрольнОго регистра, 41-й регистр сдвига выполнен на пос" ледовательно соединенных ( - +1-)2 элементах задержки, тактовые входы всех элементов задержки 1 -го регистра сдвига объединены и являются тактовым входом этого регистра сдвига, информационный вход первого регистра сдвига и выходы (1-1)-х эле 1ментов задержки-х регистров сдвига кроме первого подключены к соответствующим входам первого сумматора по модулю два, выходы (1(+1-1)-х элементов задержки-х регистров сдвига, кроме (1+1.)-го, и информационный вход (1+1)-го регистра сдвига подключены к соответствующим входам второго блока сумматоров по модулю два, первый выход блока синхронизации соединен с входом счетчика, первые выходы которого подключены к первым входам сумматора, выходы которого со131103подключен к первому входу триггера, второй выход счетчика соединен с вторым входом триггера, восьмой и девятый выходы блока синхронизации подключены к управляющим входам соответственно третьего буферного регистра и второго блока памяти, выходы которого соединены с вторыми входами сумматора, выход элемента .ИЛИ-НЕ подключен к первому входу бло ка синхронизации, тактовый вход второго буферного регистра и второй вход блока синхронизации объединены и являются первым тактовым входом приемной стороны сйстемы, третий, 15 четвертый и пятый входы блока синхро низации являются соответственно вторым тактовым, первым и вторым управляющими входами приемной стороны системы, третьи входы элементов И-НЕ 20 группы являются соответствующими третьими управляющими входами приемной стороны системы. 2, Система по п.1,о т л и ч а ю щ а я с я тем, что блок синхронизации выполнен на первом - восьмом одновибраторах, первом и втором элементах задержки, первом - пятом элементах И и первом - пятом элементах ИЛИ, 30 первый вход третьего элемента И, первый и второй входы первого элемента ИЛИ и первый вход первого элемента И являются соответственно первым, вторым, третьим и четвертым входами бло-З 5 ка синхронизации, первые входы второго и пятого элементов И объединены и являются пятым входом блока синхронизации, выход первого элемента ИЛИ подключен к входу первого одно вибратора и является первым выходом блока синхронизации, выход первогоУ 6 12элемента И подключен к первому входу второго элемента ИЛИ и являетсявторым выходом блока синхронизациивыход второго элемента И являетсятретьим выходом блока синхронизации,выход третьего элемента И подключенк второму входу второго элемента ИЛИи является четвертым выходом блокасинхронизации, выход второго элемен"та ИЛИ является пятым выходом блокасинхронизации, выход первого одновибратора подключен к входам второгои шестого одновибраторов и второмувходу пятого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которогоподключен к входу второго элементазадержки, выход второго одновибратора подключен к входам третьего и пятого одновибраторов, вторым входампервого и второго и первому входучетвертого элементов И, выход третьего одновибратора подключен к входамчетвертого и седьмого одновибраторов, второму входу четвертого и первому входу пятого элементов ИЛИ, выход четвертого одновибратора подключен к входу восьмого одновибратораи вторым входам третьего элемента Ии пятого элемента ИЛИ, выходы пятого - восьмого одновибраторов подключены к входам третьего элемента ИЛИ,выход которого соединен с входомпервого элемента задержки, выходкоторого подключен к второму входучетвертого элемента И и являетсяшестым выходом блока синхронизации,выходы четвертого элемента И, второго элемента задержки и пятого элемента ИЛИ являются соответственно седьмым, восьмым и девятым выходами блока синхронизации.

СмотретьЗаявка

3940953, 06.08.1985

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

СМИРНОВ ГЕОРГИЙ АЛЬБЕРТОВИЧ, САФОНЕНКО ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: информации, коррекцией, ошибок, передачи, приема

Опубликовано: 15.05.1987

Код ссылки

<a href="https://patents.su/10-1311036-sistema-peredachi-i-priema-informacii-s-korrekciejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема информации с коррекцией ошибок</a>

Предыдущий патент: Устройство для передачи информации последовательным кодом

Следующий патент: Устройство для подключения ламп накаливания к источнику постоянного тока

Случайный патент: Устройство для сводообрушения плохосыпучих материалов в бункерах