Процессор цифровой вычислительной машины

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1164723

Авторы: Нестеренко, Новиков, Супрун

Текст

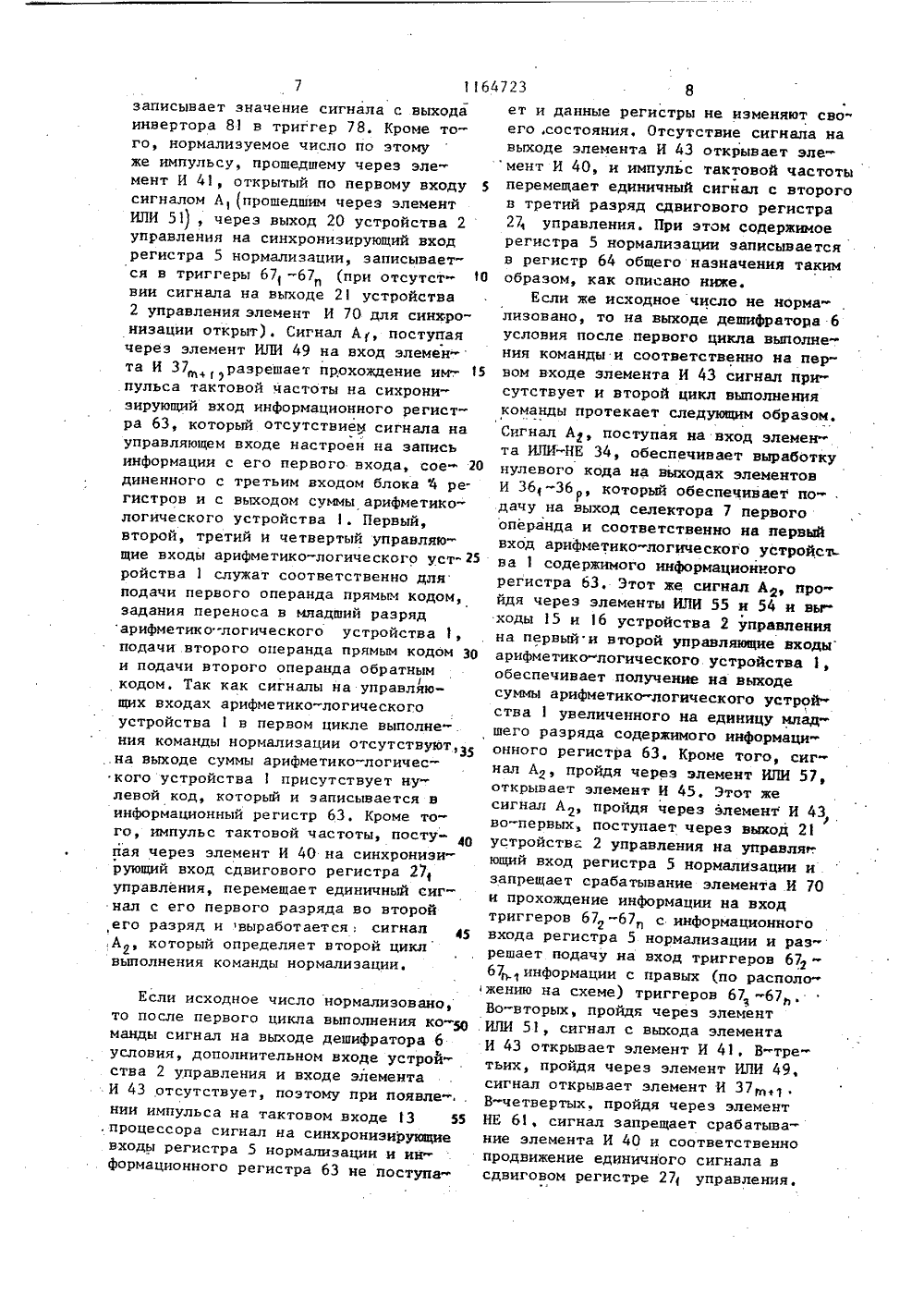

( 9) ( 1) 51) 6 06 Р 5/ ПИСАНИЕ ИЗОБРЕТЕН К АВТОРСК естерен ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54)(57) ПРОЦЕССОР ЦИФРОВОЙ ВЬЧИСЛИТЕЛЪНОЙ МАШИНЫ. содержащий арифметико-логическое устройство, устройство управления, запоминающее устройство, блок регистров, селекторы первого и второго операндов и селектор результата, выход которого соединен с первым входом блока регистров, первая и вторая группы выходов которого.подключены к входам селекторов первого второго операндов соответственно, выходы которых соединены соответственно с первыч и вторым входами арифметико-логического устройства, выходы которого соединены соответст- венно с группой входов селектора результата, адресный выход блока ре. гистров соединен с адресным входом запоминающего устройства, выход кото рого соединен с вторым входом блока регистров и с кодовым входом устрой ства управления, тактовый вход кото рого является тактовым входом процес сора., выходы устройства управления соединены соответственно с управляющими входами арифметико-логическогоустройства, блока регистров, селекторов первого и второго операндов иселектора результата, с синхронизирующим входом блока регистров и свходами обращения и записи запоминающего устройства, о т л и ч.а ющ и й с я тем, что, с целью расширения функциональных возможностейза счет нормализации чисел с фиксированной,запятой, в него введенырегистр нормализации, элементы сравнения, дешифратор условий и дешифратор нуля, причем выход селекторапервого операнда соединен с входомрегистра нормализации, выход которого подключен непосредственно ктретьему входу селектора результатаи через первый элемент сравненияк первому входу дешифратора условий,второй и третий входы которого соединены соответственно через второйэлемент сравнениям цешифратор нуляс выходом селектора первого операндаи информационным входом запоминающегоустройства, выход дешифратора условийподключен к входу устройства управления, соответствующие выходы которогоподключены к управляющим входам регистра нормализации и дешифратораусловий, четвертый вход которого соединен с тактовым входом процессора,а выход "суммы" арифметико-логичес,кого устройства соединен с третьимвходом блока регистров.1164723 оставитель В. Супрехред М.Пароцай Корректор М. Самборская ктор М, Цитк каз 418 сно ССС ВНИИПИ 1130д, 4 иал ППП "Патент", г, Ужгород, ул. Проектная, 4 Тираж 710Государственноглам изобретенийМосква, Ж, Р Подп комитета открыти ушская на1 1164Изобретение относится к вычислительной технике и может использовать-. ся при построении центральных процессоров цифровых вычислительных машине 5Целью изобретения является расширение Функциональных возможностей процессора за счет нормализации чисел с Фиксированной запятой.На фиг. 1 представлена блок-схема 10 процессора; на фиг. 2 - схема устрой. ства управления 1 на фиг. 3 - схема блока .регистров 1 на фиг. 4 схема регистра нормализации на фиг. 5 - схема управляемого дешифратора 1 на 15 фиг. б - схема дешифратора условия, на фиг. 7 - схема дешифратора записи.Процессор содержит арифметико-логическое устройство 1, устройство управления 1, запоминающее устройст во 3, блок 4 регйстров, регистр 5нормализации, дешифратор б условия, селектор 7 первого операнда, селектор 8 второго операнда; селектор 9 результата, дешифратор 10 нуля, эле менты 11 и 2 сравнения, Тактовый вход 13 процессора соединен с тактовыми входами устройства 2 управления и четвертым входом дешифратора 6 .условия. Устройство 2 управления имеет ЗО выходы 14-26.Устройство 2 управления (фиг. 2) содержит г сдвиговых регистров 27 управления, сдвиговый регистр 28, уп" равляемый дешифратор 29, регистр 30,.5 дешифратор 31 записи, триггеры 32 и 33, элемент ИЛИ-НЕ 34, р элементов И 35, р элементов И 36, (ш + 2) элементов И 37, элементы И 38-45, элементы ИЛИ.46-58,ц элементов ИЛИ 59, элемент И 60 и три элемента НЕ 611- 61,. Блок 4 регистров (фиг. 3) содержит адресный регистр.62, информационный регистр 63, ш регистров 64 общего назначения, счетчик 65 команд икоммутатор 66.Регистр 5 нормализации (фиг. 4)содержит и триггеров 67, иэлемен О . Фов И ИЛИ 68, элементы И 69 и 70 и инвертор 71..Управляемый дешифратор 29 (фиг, 5) содержит и элементов, ИЛИ 72, и эле. ментов И 73, и элементов И 74, ин вертор 75, буферный регистр 76 кода операции и дешифратор 77 кода операции,123 2Дешифратор 6 условия (фиг. 6) содержит триггер 78, коммутатор 79, элемент ИЛИ 80 и инвертор 81.Дешифратор 31 записи (фиг. 7) содержит дешифратор 82, р элементов И-ИЛИ 83 и инвертор 84.Работает процессор специализированной вычислительной машины при выполнении команды нормализации числа с фиксированной запятой следующим образом.Перед выполнением нормализации операнд располагается в регистре 641 общего назначения. В последнем цикле выполнения предыдущей команды с последнего разряда соответствующего сдвигового регистра 27 управления сигнал поступает на выход элемента ИЛИ 58. С выхода элемента ИЛИ 58 сигнал через элемент ИЛИ 56 поступает на управляющие входи регистра641 общего назначейия, коммутатора 66 и на вход продвижения счетчика команд 65 при этом коммутатор настраивается на подачу на адресный вход запоминающего устройства 3 содержимого регистра 64 1 общего назначения (адрес командного слова), счетчик 65 команд увеличивает на единицу код адреса команды, а регистр 641 общего назначения настраивается на прием кода с второго входа, соединенного с выходом счетчика 65 команд. Кроме того, сигнал с выхода элемента ИЛИ 58 через элемент ИЛИ 46 поступаетна вход обращения запоминающего устройства 3, командное слово с выхода которого поступает на кодовый вход устройства 2 управления, при этом поле признака адресации командного слова поступа ет на входы триггера 32 и элемента И 44, поле кода операции поступает на вход управляемого дешифратора 29, а поля И и К 2 командного слова поступают на вход регистра 30. В конце цикла при появлении импульса на шине 13 тактовой частоты "продви-., нутое" значение счетчика 65 команд записывается в регистр 641 общего назначения сигналом, поступившим с выхода элемента И 42 через элемент ИЛИ 48 на сихрониэирующий вход регистра 64 общего назначения.Если очередное командное слово Должно выполняться в формате 1 И (нулевое значение разряда признака адресации), то элемент И 44 закрыт,.наз . 1,164,7234его выходе сигнал отсутствует, поэто" той, которая имеет один операнд и дваму сигналы с выходов элемента ИЛИ 58результата,и инвертора 75 открывают элементы При этом в первомпервом цикле выполнеИ 741 в 74 п в управляемом дешифраторе ния режима выборки второго опе аорого операндасигнал 1 с выхода пер 29 и код операции через элементыв режиме ВХ сигнал ГИ 741 - 74, элементы ИЛИ 72 - 72 в вого разряда сдвигового регистра 28поступает на вход дешифратора 77 ко- через элемент ИЛИ 56 бо еспечиваетда операции, на последнем выходе кото" подачу на адресный.в дресный.вход запоминаюрого, если код операции соответствует щего устройства 3 кодкода адреса смекоманде нормализации числа с фиксиро" 0 щения из регист а 64 бгистра , о щего назнаванной запятой, появляется сигнал к чения .(в режиме ВХ командное словопоступает на вход сдвигового регистр% . занимает две со еет две соседних ячейки в памя271 управления и по импульсу тактовой"тв), а через элемент ИЛИ 46 - сигна.частоты, прошедшему через элемеид :.-:.-," ла обращения к зап ющия к запоминающему устройИ 40 на синхрониэирующий вход сдвиго ству 3. Смещение с выхода запоминавого регистра 271 управления, включа- ющвго устройЧтва 3 цоступает на втоет его первый разряд (элемент И 40 от- рой вход информациокн риационного регистракрыт для.импульса тактовой частоты 63 в блоке 4 регистров кото ыйтак как сигнал на выходе элемента сигналом Ру поступивпиюм чу впиюм через элеИ 43 отсутствует, .а на выходе элемен" 20 мент ИЛИ 50, выход 22 устройства 2та НЕ 61 присутствует). Одновременно управления на управляющий вход икс этим так как элемент И 39 открыт . формационного регистра 63 к, настроенсигналом с выхода элемента ИЛИ 58 по ка прием информации с второгоцки с второго егоимпульсу тактовой частоты, вырабаты- входа. Сигнал Р через элем квающего сигнал на выходе элемента 25 ИЛИ 49 поступает на вход элементаИ 39, значение признака адресации И 37,1, который в конце данногозаписывается в триггер 32, значение цикла пропускает импульс тактовойполей К 1 и К 2 записывается в регистр . частоты с тактового входа 13 процес.30, а значение кода операции запишет-,сора на синхронизирующий вход инфор.ся в буферный регистр 76 кода опера- ЗО мационного регистра 63, в которыйции. Кроме того, в этом же цикле и записывается смещение,по импульсу тактовой частоты "вытал-1По этому же импульсу тактовойкивается единичный сигнал с послед- частотьчастоты единичный сигнал продвкганего разряда сдвигового регистра 27 ется из первого во второй разрядуправления, который. был ранее включен 3 сдвсдвигового регистра 28, который выи обеспечивал сигнал на выходе элемен" рабатываера атывает сигнал Р . Во втором цик"та ИЛИ 58, после чего начинается пер- де режима бде режима выборки второго операндавый цикл выполнения команды нормали- . производпроизводится модификация (суммироэации. Если же поле адресации в вы ванне смещения с индексом, которыйбранном командном слове указывает на 4 р кахнаходится в регистре 64общего нарежим КХ, ие КК (единица в поле приз" значен,1значения, задаваемом полем В 2 конака адресации), то описанный процесс .мандмандного слова. Код 1 в поле К 2 реповторяется с той лишь. разницей, что гист 30,гистра О, поступая через открытыев триггер 32.записывается единица и алемен И 35 -35алементы- выход 26 устна выходе элемента И 44 присутствует 45 ройства 2ро ства управления на управляющийсигнал, который запрещает прохождение вход селектора 8 второго операнда,кода операции через элементы И 74 обеспечивает подачу содержимого ре 74 (команда с нулевым кодом операции гист 64 бгистра 1 общего назначения наотсутствует в системе команд), позто- второй вход арифметико-логическогому по импульсу тактовой частоты вклю 50 устройст а 1 Тустройства . Так как на входе элечается не первый разряд сдвигового мента ИЛИ-НЕ 344 присутствует сигналрегистра 27 управления, а первый раэ- Р то элементы И 36-36 Р закрыты иряд сдвигового регистра 28. Регистр на выход селектора 7 первого операн"28 обеспечивает выборку второго опе- да подается не содержимое регистраранда в режиме ВХ для других команд 5 64 общего као щего назначения, указанное поиз системы команд н подготовкУ испол лем К 1 в р глем в регистре 30, а содержимоенительного адреса для команды норма- ик -информационного регистра 63, котороелизации числа с фиксированной запя- поступае напоступает на первый вход арифметико й 116472 логического устройства 1. Сигнал Рчерез элементы ИЛИ 55 и 53, выходы15 и 17 устройства 2 управления поступает на первый и третий управляютщие входы эрифметико-логического . 5 устройства , которые служат соответственно для подачи прямым кодом первого и второго операндов, при этом . на выходе суммы арифметико-логического устройствапоявляется исполни О тельный адрес (сумма смещения и индек са), который через третий вход блока 4 регистров поступает на .вход адресного регистра 62. Кроме того, сигнал Г разрешает прохождение импульса 15йтактовой частоты через элемент И 37, на синхронизирующий вход адресного регистра 62 и запись в него исполнительного адреса.26По этому же импульсу тактовой час" тоты единичный сигнал перемещается свторого в третий разряд сдвиговогорегистра 28, который вырабатывает . сигнал Р., В третьем цикле режимавыборки второго операнда в режимеВХ, который для команд нормализациине имеет смыслового значения (используется для других команд из системы команд), на адресный, вход запоминающего устройства подается содер-жимое адресного регистра 62, так каксигнал на управляющем входе коммутатора 66 отсутствуетЧерез элементИЛИ 46 сигнап Р поступает на входобращения запоминающего устройства ЭЗ3, с выхода которого код второго операнда поступает на второй вход блока4 регистров и второй вход информационного регистра 63. Кроме того, сигнал Р через. элемент ИЛИ 50, выход ф 122 устройства 2 управления поступаетна управляющий вход информационногорегистра 63 и настраивает его на прием информации с второго его входа.Сигнал Р 1 через элемент ИЛИ 49, поступая на вход элемента И 37,л , раз"решает прохождению импульса тактовойчастоты на синхронизирующий вход информационного регистра 63, в которыйи записывается второи операнд. При фпоявлении сигнала Р на выходе эле 5мента НЕ 61 на входе триггера 33сигнал отсутствует, поэтому по импульсу тактовой частоты в триггер 33 записывается ноль, который на протяже нии первого цикла выполнения любой команды обеспечивает подачу второго операнда (вместо подачи индекса с уе",3 бгистра 64 общего назначения). Кроме того, сигнал Р , поступая на третий управляющий вход управляемого дешифратора 29, обеспечивает подачу кода операции с буферного регистра 76 кода операции через элементы И 731-73 л, элементы ИЛИ 21-72на вход дешифра" тора 77 кода операции и при коде операции, соответствующем команде нормализации, по импульсу тактовой часто" ты, поступившему через элемент И 40 на синхронизирующий вход сдвигового регистра 27 управления, в его первый разряд записывается единичный сигнал, после чего начинается собст" венно выполнение команды нормализации числа с фиксированной запятой,Нормализация числа с фиксированной запятой производится следующим образом.В первом. цикле выполнения команды на выходе сдвигового регистра 27 вырабатывается сигнал А 1. Код 1 выхода поля К регистра 30 через элементы И 36 -36, выход 25 устройства 2 управления поступает на управляющий вход селектора 7 первого операн" да и настраивает его на пропускание на его выход содержимого регистра 64; общего назначения. Число с выхода селектора 7 первого операнда поступает на входы элемента 11 сравнения, дешифратора 1 О нуля и на информационный вход регистра 5 нормализации, науправляющем входе 21 которого сигнал отсутствует, поэтому данное число поступает на входы триггеров 67 -67 . Элемент 11 сравнения выралбатывает сигнал на своем выходе при неравенстве знакового разряда числа самому старшему разряду мантиссы числа (число нормализовано), а дешиф" ратор О нуля вырабатывает сигнал 1 на своем выходе при равенстве числа нулю (число нормализовано), Таким образом, на выходе элемента ИЛИ 80 и, соответственно, на первом входе коммутатора 79 вырабатывается сигнал, если число нормализовано, и сигнал отсутствует, если число нужно нормализовать. Сигнал через выход 19 уст" ройства 2 управления поступает на управляющий вход дешифратора 6 условия и настраивает коммутатор 79 на пропускание сигнала с его первого входа, через инвертор .81 на вход триггера 78. Импульс тактовой частоты с тактового входа 13.процессора1164723 ет и данные регистры не изменяют сво"его,состояния. Отсутствие сигнала навыходе элемента И 43 открывает элемент И 40, и импульс тактовой частоты 5 перемещает единичный сигнал с второгов третий разряд сдвигового регистра27, управления. При этом содержимоерегистра 5 нормализации записываетсяв регистр 64 общего назначения таким 0 образом, как описано ниже.Если же исходное число не нормализовано, то на выходе дешифратора 6условия после первого цикла выполнения команды и соответственно на пер вом входе элемента И 43 сигнал присутствует и второй цикл выполнениякоманды протекает следующим образом.Сигнал А, поступая на вход элемента ИЛИ-НЕ 34, обеспечивает выработкунулевого кода на выходах элементовИ 36 -36, который обеспечивает подачу на выход селектора 7 первогооперанда и соответственно на первыйвход арифметико-логического устройства 1 содержимого информационногорегистра 63, Этот же сигнал А проЯэйдя через элементы ИЛИ 55 и 54 и выходы 15 и 16 устройства 2 управленияна первый и второй управляющие входыарифметика-логического. устройства 1,обеспечивает получение на выходесуммы арифметико-логического устройства 1 увеличенного на единицу младшего разряда содержимого информационного регистра 63. Кроме того, сигнал А, пройдя через элемент ИЛИ 57,открывает элемент И 45, Этот жесигнал А , пройдя через элемент И 43во-первых, поступает через выход 21фустройства 2 управления иа управляющий вход регистра 5 нормализации изапрещает срабатывание элемента И 70н прохождение информации на входтриггеров 67 -67 с информационноговхода регистра 5 нормализации и разрешает подачу на вход триггеров 67.267 информации с правых (по расположению на схеме) триггеров 67 67.Во-вторых, пройдя через элемент .ИЛИ 51, сигнал с выхода элементаИ 43 открывает элемент И 41, В-третьих, пройдя через элемент ИЛИ 49,сигнал открывает элемент И 37,.В-четвертых. пройдя через элементНЕ 61, сигнал запрещает срабатывание элемента И 40 и соответственнопродвижение единичного сигнала всдвиговом регистре 27 управления. Если исходное число нормализовано, то после первого цикла выполнения ко-щ манды сигнал на выходе дешифратора 6 условия, дополнительном входе устройства 2 управления и входе элемента И 43 отсутствует, поэтому при появле-, . нии импульса на тактовом входе 13 55 .процессора сигнал на синхронизирукаие входы регистра 5 нормализации и ин . формационного регистра 63 не поступазаписывает значение сигнала с выходаинвертора 81 в триггер 78. Кроме того, нормализуемое число по этомуже импульсу, прошедшему через элемент И 41, открытый по первому входусигналом А 1 прошедшим через элементИЛИ 5), через выход 20 устройства 2управления на синхронизирующий входрегистра 5 нормализации, записывается в триггеры 67 -67 П (при отсутствии сигнала на выходе 21 устройства2 управления элемент И 70 для синхро"низации открыт). Сигнал А, поступаячерез элемент ИЛИ 49 на вход элемента И 37 разрешает прохождение им-.Ф+7пульса тактовой частоты на сихронизирующий вход информационного регистра 63, который отсутствием сигнала науправляющем входе настроен на записьинформации с его первого входа, соедииенного с третьим входом блока ч ре.гистров и с выходом суммы арифметикологического устройства . Первый,второй, третий и четвертый управляющие входы арифметико-логического устройства 1 служат соответственно дляподачи первого операнда прямым кодом,задания переноса в мяадший разряд арифметико"логического устройства 1,подачи второго операнда прямым кодом 30и подачи второго операнда обратнымкодом. Так как сигналы на управляющих входах арифметико-логическогоустройствав первом цикле выполне-.ния команды нормализации отсутствуют ф 35 . на выходе суммы арифметико-логического устройства 1 присутствует нулевой код, который и записывается в информационный регистр 63. Кроме того, импульс тактовой частоты, посту пая через элемент И 40 на синхронизирующий вход сдвигового регистра 27 управления, перемещает единичный сигнал с его первого разряда во второй его разряд и 1 выработается . сигнал ,А, который определяет второй цикл выполнения команды нормализации.1 О ния второго цикла число не нормализо" 1 зано, то второй цикл в режима сдвига содержимого регистра 5 нормализации повторяется . Таким образом, второй цикл при выполнении команды нормализации повторяется (К + 1) раз, где К - .константа сдвига при нормализации, указывающая на число сдвигов мантиссы (на один разряд при каждом ,сдвиге) при нормализации. Константа сдвига К при нормализации формиру. ется в информационном регистре 63. При нулевом сигнале на выходе дешифратора 6 условия второй цикл вы- . полнения команды нормализации выполняется последний раз, после чего единичный сигнал перемещается иэ вто" рого разряда в третий разряд сдвигового регистра 271 управления, который вырабатывает сигнал А , и начинается выполнение третьего цикла.В третьем цикле выполнения команды нормализации производится запись второго результата (константы сдвига) в память, при этом сигнал А 5, поступая на вход элемента ИЛИ-КЕ 34, обеспечивает выработку на выходах элементов И Збнулевого кода, при котором содержимое информационного регистра 63 подается на выход селектора 7 первого операнда и соответственно на первый информационный вход запоминающего устройства 3Сигнал АЗ, поступающий на управляющий вход дешифратора 31 записи, обеспечивает подачу кода 1 с выхода по" ля К 2 регистра 30 на вход дешифратора 82, сигнал с выхода которого открывает элемент И 37,1. Кроме того, сигнал А 5 через элемент ИЛИ 55, выход 15 устройства 2 управления, поступая на первый управляющий вход арифметико-логического устройства 1, обеспечивает подачу константы сдвига на выход суммы арифметико-логического устройства 1, Кроме того, сигнал А 5 подается на входы тех элементов ИЛИ 59-59 (на чертеже показаны в виде Ар), чтобы на их выходах и соответственно на управляющем входе селектора 9 результата выработать код, обеспечивающий подачу содержимого с выхода суммы арифметико-логического устройства 1 на выход селектора 9 результата и входы регистров 64 общего назначения.Если команда нормализации выполня" ется в режиме КК (низкий потенциап 9 1 164723Кроме того отсутствие сигнала навыходе 19 устройства 2 управлениянастраивает коммутатор 79 на пропускание сигнала с выхода элемента 12сравнения через второй вход коммута"тора 79, инвертор 81 на вход тригге" .ра 78. Элемент 12 сравнивает знаковый разряд и разряд, следующий после старшего разряда мантиссы числа,находящегося в регистре 5 нормализа Оции (выходы триггеров 671 и 675 в .регистре 5 нормализации) и срабатыва"ет аналогично элементу 1 сравнения.При поступлении импульса на шину3 тактовой частоты сдвиговый регистр 5271 управления не изменяет своего . состояния, в регистре 5 нормализациипроисходит сдвиг мантиссы влево наодин разряд (последний разряд заполняется нулями), увеличенное на 20единицу, значение информационного регистра 63 с выхода суммы арифметикологического устройства 1 записывается в информационный регистр 63, а предварительное (не сдвинутое) число из 25регистра 5 нормализации записывается в регистр 64 общего назначения, так как код с выхода поля К регистра 30 через дешифратор 31 записи открывает элемент И 37, который пропускает синхроимпульс с выхода элемента И 45 на синхрониэирующий вход регистра 64 общего назначения, при этом сигнал А подается только на те входы элементов ИЛИ 591-59 (на чертеже35 обозначен в виде А), чтобы на их , выходах (выход 14 устройства 2 управ" ления) сформировался код, обеспечивающий подачу на выход селектора 9 результата и, соответственно на вхо" 40 ды регистров 64 общего назначения содержимого регистра 5 нормализации через его третий вход.Если после сдвига во втором цикле число станет нормализованным, в триг"45гер 78 по окончании импульса тактовой частоты запишется нулевой сигнали он с выхода дешифратора 6 условия поступит на дополнительный вход устройства 2 управления, после чего вто 50 рой цикл (определяется выдачей сигнала А на выход сдвигового регистра 271 управления) выполняется аналогично выполцению второго цикла при нормализованном исходном значении числа, причем в регистр 64 общего назначения при этом записывается нормализованное число. Если же после выполне-.1 11 на выходе триггера 32), то сигнал Апроходит через элемент И 60, элемент ИЛИ 57 и открывает элемент И 45 при этом импульс тактовойчастоты с шины 13 тактовой частоты проходит через элемент И 45, элемент И 37 на синхрониэирующий вход регистра 64 общего назначенияи записывает в него константу сдвига. Если же команда выполняется в режиме 1 И (высокий потенциал на выходе триггера 32)то сигнал А через элемент И 38, через элементы ИЛИ 46 и 47 поступает на вход обращения и вход записи запоминающего устройства 3, и константа сдвига записыг вается в запоминающее устройство 3 по исполнительному адресу, храня 64723 12щемуся в адресном регистре 62 и по"даваемому через коммутатор 66 наадресный вход запоминающего устрой"ства 3. После этого от импульса5 тактовой частоты единичный сигналперемещается из третьего в четвертый разряд сдвигового регистра 27который вырабатываетсигнал А, обес.печивающий, как описано вьппе, выра 1 О ботку очередного командного слова,При выполнении других команд изсистемы команд включаются соответствующие сдвиговые регистры 27 управления, которые вырабатывают на своихИ выходах сигналы, с помощью которыхвырабатываются соответствующие микрооперации на выходах устройств 2 управления,

СмотретьЗаявка

2818287, 20.09.1979

ПРЕДПРИЯТИЕ ПЯ А-7160

СУПРУН ВАСИЛИЙ ПЕТРОВИЧ, НЕСТЕРЕНКО ЮРИЙ ГРИГОРЬЕВИЧ, НОВИКОВ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 19/00

Метки: вычислительной, процессор, цифровой

Опубликовано: 30.06.1985

Код ссылки

<a href="https://patents.su/10-1164723-processor-cifrovojj-vychislitelnojj-mashiny.html" target="_blank" rel="follow" title="База патентов СССР">Процессор цифровой вычислительной машины</a>

Предыдущий патент: Устройство связи для вычислительной системы

Следующий патент: Устройство для реализации логических функций

Случайный патент: Монтажное соединение балок под сварку монтажных стыков