Специализированный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

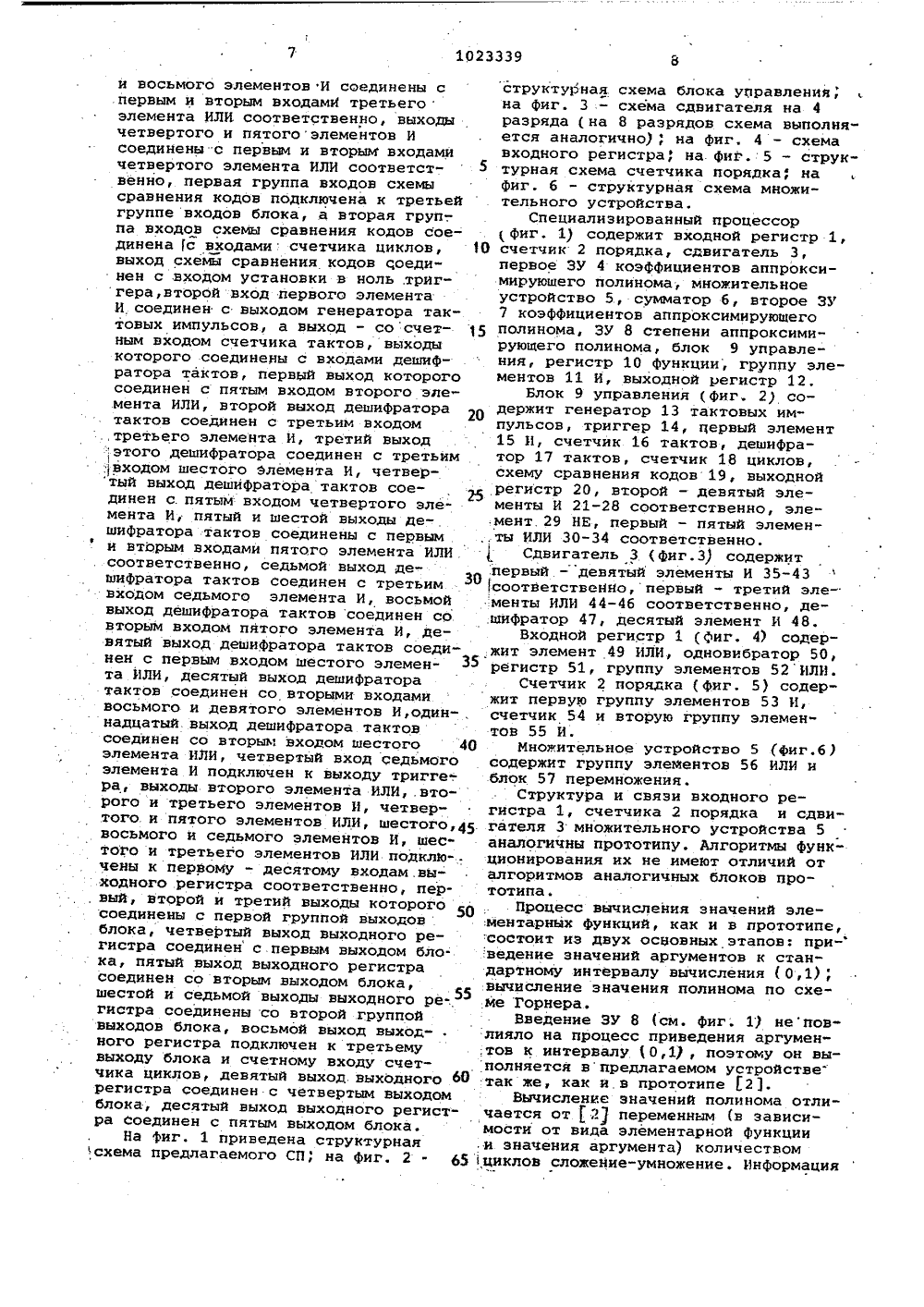

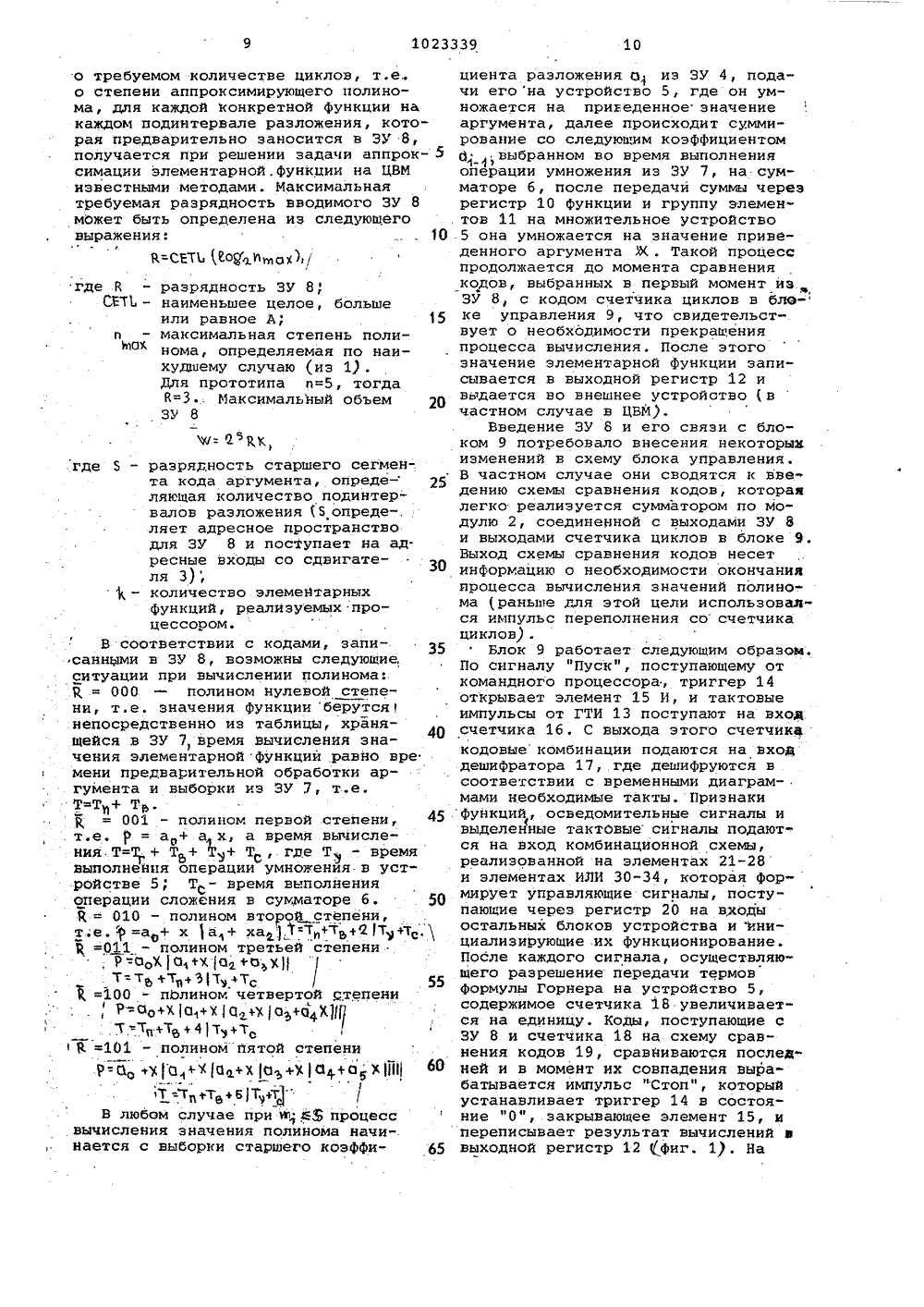

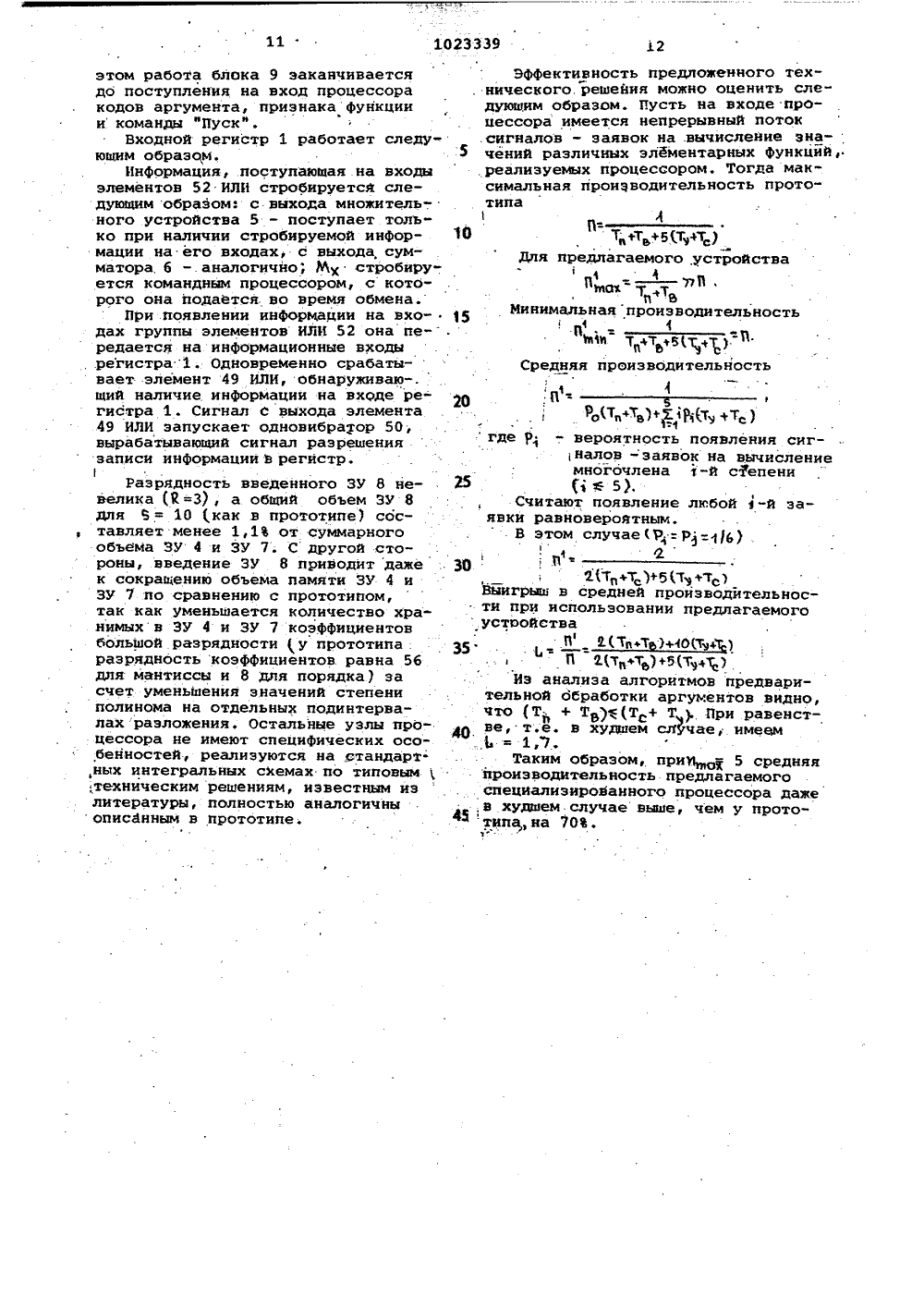

.Швыдкая Техред А,Ач Корректор Г.Ог еда е ал ППП "Патент", г, Ужгород, ул. Проектная, 4 аказ 4214/34 Тираж 706ВНИИПИ Государственн ло делам иэобретеии113035, Москва, Ж,Подписного комитета СССРи открытийаушская наб., д. 4/1023339 третьей группой ходов блока управления 2. Процессор по и, 1, о т л и.ч а ю щ и й с я тем, что блок управления содержит генератор тактовых. импульсов, триггер, девять элементов И, счетчик тактов, дешифратор тактов, шесть элементов ИЛИ, выходной регистр, счетчик циклов и схему сравнения кодов, причем вход запуска блока подключен к входу установки в единицу триггера, выход которого соединен с первыми входами первого и второго элементов И, первый вход первого элемента ИЛИ соединен с первым входом признака Функции блока, второй и третий входы признака функции блока соединены с первым и Вторым входами третьего элемента И и второго элемента ИЛИ,четвертый вход признака функции блока соединен с третьим входом Второго элемента ИЛИ и вторым входом первого элемента ИЛИ, первый вход первой группы входов блока соединен с первым входом четвертого элемен-та И, второй вход первой группы входов блока соединен со вторыми вхо" дами второго и четвертого элементов И и первым входом пятого элемента И, выход третьего элемента И соединен с первым входом, а выход первого элемента ИЛИ - со вторым входом шестого элемента И, первый вход признака функции блока соединен с четвертым входом второго элемента ИЛИ и первым входом седьмого элемента И, первый вход второй группы входов блока соединен со вторым входом седьмого элемента И, второй вход второй группы входов блока соединен с третьим входом четвертого элемента И, третий вход второй группы входов .соединен с четвертым входом четвертого элемента И и первыми входами восьмого и девятого элементов И, выходы седьмого и восьмого элементов И соединены с первым и вторым входами третье го элемента ИЛИ соответственно, выходы четвертого ипятого элементов И ,соединены с первым и вторым входами четвертого элемента ИЛИ соответст венно, первая группа входов схемы сравнения .кодов подключена к третьей группе входов блока, а вторая группа входов схемы сравнения кодов соедиИзобретение относится к вычислительной технике и может быть исполь иена с входами счетчика циклов, выход схемы сравнения кодов соединен свходом установки в ноль триггера,второй вход первого элемента И. соединен с выходом генератора тактовых.импульсов, а выход - со счетнымвходом счетчика тактов, выходы которого соединены с входами дешифратора тактов, первый выход которого соединен с пятым входом второго элемента ИЛИ, второй выход дешифраторатактов соединен с третьим входомтретьего элемента И, третий выходэтого дешифратора соединен с третьимвходом шестого элемента И, четвертый выход дешифратора тактов соединен с пятым входом четвертого элемента И, пятый и шестой выходы дешиФратора тактов соединены с первыми вторым входами пятого элемента ИЛИсоответственно, седьмой выход дешифратора. тактов соединен с третьимвходом седьмого элемента.И, восьмойвыход дешифратора тактов соединен совторым входом пятого .элемента И,девятый выход дешифратора .тактов соединен с первым входом шестого элемента ИЛИ, десятый выход дешифраторатактов соединен со вторыми входамивосьмого и девятого элементов И,одиннадцатый выход дешифратора тактов соединен.со вторым входом шестогоэлемента ИЛИ, четвертый вход седьмо-го элемента И подключен к выходутриггера, выходы второго элемента ИЛИ,второго и третьего элементов И, четвертого и пятого элементов ИЛИ, шестого, восьмого и седьмого элементовИ, шестого и третьего элементов. ИЛИподключены к первому в десятомувходам выходного регистра соответственно, первый, второй и .третий выходы которого соединены с первой группой выходов блока, четвертый выходвыходного регистра соединен с первымвыходом блока, пятый выход выходногорегистра соединен с вторым выходомблока, шестой и седьмой выходы выходного регистра соединены со второйгруппой выходов блока, восьмой выходвыходного регистра подключен к третьему выходу блока и счетному входусчетчика циклов, девятый выход выходного регистра соединен с четвертымвыходом блока,. десятый выход выходного регистра соединен с пятым выУодом блока,зовано в качестве периферийного устройства универсальных и специализиро.:где М = мса Р,РФ 11 Ц - максимальноеХЩ 11значение мои 1= 1,К)дуля И 1.1) йпроизводнойна интервалеО у 1) для 1 йФункции из 35 . множества Кфункций, реализуемых процессором,М - шаг интерпо ляцииТак как И является функцией отХ, то она может меняться на интервале в широКих пределах, Например, для,(Х+1 модуль шестой производной 45 .меняется от 720 прр Х =О до 5,63 приХ =1, т.е. более чем на два порядка,Следовательно, при Фиксированном внечении И в тех же пределах меняетсяи методическая ошибка. Еще большее 0 .различие М наблюдается у разныхпо свойствам функций, так при Х - ф 0модуль шестой производной Соъ ЩйХ(ьстремится в 0 дляЬи)+Ф) 720 . Таким образом, степень полиноМа, выб.ранная по наихудшему случаю.из условия (Ц, является величиной завышенной не только для тех функций, у которых Мсвою К;, но и для каждойконкретйой из функций при различныхзначениях аргумента, Следовательно;60 имеется теоретическая возможностьизменять степень аппроксимирующегополинома в процессе вычисления в э,,висимости от вида ЭФ и значения ар.,гумента при выполнении требования 65 1 обеспечения заданной методическойФ 30 ванных ЦВМ иликак специализированный фуйЩиональный преобразователь в 1 различных вычислительных и управляющих системах для вычисления элементарных функций с высокой точностью и быстродействием.Известен специализированный процессор - цифровой интерполятор высокого порядка, содержащий выход-. ной регистр, множительное устройство, постоянное зацоминаюшее устройство, сумматор, регистр функции, две группы элементов И, выходной буфер и блок управления. Процессор позволяет вычйслять значения элементарных функций, которые могут быть- разложены в ряд Тейлора 1.Недостаток такого процессора - отсутствие технических средств приведения значений аргумента к стандартному интервалу (0,.1) .и, как следствие, отсутствие возможности вычисления значений элементарных функций от аргументов, представленных в форме с плавающей точкой, чтО значительно сужает область приме"нения указанного специализированного процессора.. Наиболее близким к изобретению является специализированный процессор, содержащий входной регистр., счетчик порядка, сдвигатель, первое запоминающее устройствоЗУ), множительное устройство, сумматор, первую группу, элементов И, второе. . ЗУ, блок управления, регистр функции, вторую группу элементов И, выходной регистр, причем выходы входного регистра соединены с входами ,сдвигателя,множительного устройства, сумматора, первого ЗУ выходы счетчика порядка соединены с входами сдвигателя, множительного :устройства и блока управления, выходысдвигателя подключены.к входам второго ЗУ, выходы первого ЗУ подключены к входам множительного . устройства, выходы которого соединены с входами сумматора и входного регистравыходы сумматора подключены к входам регистра функции и входного. регистра, выходы первой группы элементов И подсоединены к входам суыиатора, выходы второго ЗУ подключены к входам первой груп-пы элементов И, выходы БУ соединены с входами счетчика порядка, пер. вой группы элементов И,регистра Функции, второй группы элементов И и выходного регистра, выходы регистра Функции подключены к входам второй группы элементов К и выходного . регистра, выходы второй группы элементов И связаны с входами МУ, выходы выходного регистра могут соединяться с входами внешних устройств. .Введение в процессор счетчика по,рядка, сдвигателя и первого ЗУ позволяет вычислять значения Функцийе", ппх, епх, соьх от .аргументовс плавающей точкой, т.е. расширитьдиапазон представления аргументов и,как следствие, расширить область применения устройства 2).Однако известное устройство ха".производительностью, обусловленнойотсутствием технических средств 10 адаптации к особенностям различныхэлементарных функций и характеру ихповедения в зависимости от текущегозначения аргумента.Причина этого кроется в методах 15 проектирования многофункциональныхспециализированных процессоров, вчастности - в методике выбора степени аппроксимирующего полинома й,которая выбирается исходя из усло вия обеспечения заданной методической погрешности аппроксимации придопустимых аппаратурных затратах.В случае использования ряда Тейлораметодическая ошибка равна 25мохщ)спогрешности. Это явля 6 тся резервом для увеличения производительности процессора.Целью изобретения является увеличение производительности специализированного процессора.Поставленная цель достигается тем, что в процессор, содержащий входной регистр, счетчик порядка, сдвигатель, первое и второе зало О минающие устройства коэффициентов аппроксимирующего полинома, множи" тельное устройство, сумматор, регистр функции, группу элементов И и выходной регистр, причем первая группа входов входного регистра подключена к входам мантиссы аргумента процессора, первая группа выходов этого регистра соединена с информационными входами сдвигателя, вторая группа выходов входного регистра соединена с адресными входами первого запоминающего устройства коэффициентов аппроксимирующего полинома, выходы которого подключены к первой группе входов множительного устройства, выходы которого подключены к входам первого слагаемого сумматора, выходы которого подключены ко второй группе входов входного регистра и информационным входам регистра функции, выходы которого соединены с информационными . входами выходного регистра и первыми входами элементов И группы, выходы которых соединены со второй группой 35 входов множительного устройства, выходы которого подключены к третьей группе входов входного регистра, третья группа выходов которого соединена с третьей группой входов мно О жительного устройства и входами второго слагаемого сумматора, устано" вочные входы счетчика порядка подключены к входам порядка аргумента процессора, первая группа выходов счетчика порядка подключена к четвертой группе входов множительного устройства, вторая группа выходов счетчика порядка соединена с управляющими входами сдвигателя, выходы которого соединены с адресными входами второго запоминающего устройства.коэффициентов аппроксимирующего полинома, выходы которого соединены с входами третьего слагаемого сумматора, вход запуска блока управления подключен к входу запуска процессора, входы признаков функции блока управления соединены с входами признаков функции процессора, первая группа входов, блока управ ления соединена с четвертой группой выходов входного регистра, вторая группа входов блока управления соединена со второй группой выходов счетчика порядка, первая группа вы ходов блока управления соединена с входами синхронизации счетчика порядка, вторая группа выходов блока управления соединена с выходами признаков процессора, первый выход блока управления соединен с входами синхронизации регистра функции, второй выход блока управления соединен с управляющим входом второго запоминающего устройства коэффициентов аппроксимирующего полинома третий выход блока управления соединен со вторыми входами элементов И группы, четвертый выход блока управления соединен с входом синхронизации выходного регистра, пятый выход блока управления соединен с входом установки в ноль выходного регистра, введено запоминающее устройство степени аппроксимирующего полинома, адресные входы которого подключены к выходам сдвигателя, а выходы соединены с третьей группой входов блока управления.Кроме того, блок управления содержит генератор тактовых импульсов, триггер, девять элементов И, счетчик тактов, дешифратор тактов, шесть элементов ИЛИ, выходной регистр, счетчик циклов и схему сравнения кодов, причем вход запуска блока подключен к входу установки в единицу триггера, выход которого соединен с .первыми входами первого и второго элементов И, первый вход первого элемента ИЛИ соединен с первым входом признака функции блока, второй и третий входы признака функции блока соединены с первым и вторым входами третьего элемента И и второго элемента ИЛИ, четвертый вход признака Функции блока соединен с третьим входом второго элемента ИЛИ и вторым входом первогоэлемента ИЛИ,. первый вход первой группы входов блока соединен с первым входом четвертого элемента И, второй вход первой группы входов блока соединен со вторыми входами второго и четвертого элементов И и первым входом пятого элемента И, выход третьего элемента И соеди- нен с первым входом, а выход пер-. вого элемента ИЛИ - со вторым входом шестого элемента И, первый вход признака Функции блока соединен с четвертым входом второго элемента ИЛИ и первым входом седьмого элемента И, первый вход второй группы входов блока соединен со вторым входом седьмого элемента И, второй вход второй группы входов блока соединен с третьим входом четвертого элемента И, третий вход второй группы входов блокй соединен с четвертым входом четвертого элемента И и первыми входами восьмого и девятого элементов И; выходы седьмогоструктурная схема блока управления, на фиг. 3 - схема сдвигателя на 4 разряда ( на 8 разрядов схема выполняется аналогично); на Фиг. 4 - схема входного регистра, на. Фиг. 5 - структурная схема счетчика порядка," на фиг. б - структурная схема множительного устройства.Специализированный процессорфиг. Ц содержит входной регистр 1, счетчик 2 порядка, сдвигатель 3, первое ЗУ 4 коэффициентов аппроксимирующего полинома, множительное устройство 5, сумматор б, второе ЗУ 7 коэффициентов аппроксимирующего полинома, ЗУ 8 степени аппроксимирующего полинома, блок 9 управления, регистр 10 функции, группу элементов 11 И, выходной регистр 12,Блок 9 управления (фиг. 2) содержит генератор 13 тактовых импульсов, триггер 14, цервый элемент 15 И, счетчик 16 тактов, дешифратор 17 тактов, счетчик 18 циклов, схему сравнения кодов 19, выходной регистр 20, второй - девятый элементы И 21-28 соответственно, элемент. 29 НЕ, первый - пятый элемен.ты ИЛИ 30-34 соответственно.Сдвигатель 3 (фиг.3) содержит первый - девятый элементы И 35-43 соответствеиио,первый - третий эле-. менты ИЛИ 44-46 соответственно, де:шифратор 47, десятый элемент И 48.Входной регистр 1 (Фиг, 4) содержит элемент 49 ИЛИ, одновибратор 50, регистр 51, группу элементов 52 ЕЛЕЗ.Счетчик 2 порядка ( фиг. 5) содержит первую группу элементов 53 И, счетчик 54 и вторую группу элементов 55 И.Множительное устройство 5 фиг.б) содержит группу элементов 56 ИЛИ и блок 57 перемножения.Структура и связи входного регистра 1, счетчика 2 порядка и сдвигателя 3 множительного устройства 5 аналогичны прототипу. Алгоритмы функционирования их не имеют отличий от алгоритмов аналогичных блоков прототипа.Процесс вычисления значений элементарных функций, как и в прототипе, :состоит из двух основных этапов: при" ведение значений аргументов и стандартному интервалу вычисления ( 0,1); вычисление значения полинома по схеме Горнера.Введение ЗУ 8 (см. Фиг. 1) неповлияло на процесс приведения аргумен:тов к интервалу 0,1), поэтому он выполняется впредлагаемом устройстве так же, как и.в прототипе 123.Вычисление значений полинома отличается от21 переменным (в зависимости от вида элементарной функции и значения аргумента) количеством 1 циклов сложение-умножение. Информация 65 и восьмого элементов И соединены с первым и вторым входамИ третьего элемента ИЛИ соответственно, выходы четвертого и пятогоэлементов И соединены с первым и вторым входами четвертого элемента ИЛИ соответст венно,.первая группа входов схемы сравнения кодов подключена к третьей группе входов блока, а вторая груп-, па входов схемы сравнения кодов соединена с входами счетчика циклов, ЕО выход схемы сравнения кодов соединен с входом установки в ноль .триггера, второй вход первого элемента И соединен с выходом генератора тактовых импульсов, а выход - со счет ным входом счетчика тактов, выходы которого соединены с входами дешифратора тактов, первый выход которого соединен с пятым входом второго элемента ИЛИ, второй выход дешифратора тактов соединен с третьим входом .,третьего элемента И, третий выход "этого дешифратора соединен с третьим . :входом шестого Элемента И, четвертый выход дешифратора тактов соединен с.пятым входом четвертого элемента И, пятый и шестой выходы де-. шифратора тактов соединены с первым и вторым входами пятого элемента ИЛИ соответственно, седьмой выход дешифратора тактов соединен с третьим входом седьмого элемента И, восьмой выход дешифратора тактов соединен со вторым входом пятого элемента И, девятый выход дешифратора тактов соединен с первым входом шестого элемен- З 5 та ИЛИ, десятый выход дешифратора тактов соединен со вторыми входами восьмого и девятого элементов И,один-, надцатый выход дешифратора тактов соединен со вторым входом шестого 40 элемента ИЛИ, четвертый вход Седьмого элемента И подключен к выходу тригге-. ра, выходы второго элемента ИЛИ,.вто-рого и третьего элементов И, четвертого и пятого элементов ИЛИ, шестого,45 восьмого и седьмого элементов И, шестого и третьего элементов ИЛИ подклю-. чены к первому - десятому входам .вымодного регистра соответственно, пер, вый, второй и третий. выходы которого соединены с первой группой выходов . блока, четвертый выход выходного регистра соединен с.первым выходом блока, пятый выход выходного регистра соединен со вторым выходом блока, шестой и седьмой выходы выходного ре гистра соединены со второй группой выходов блока, восьмой выход выход- . ного регистра подключен к третьему выходу блока и счетному входу счетчика циклов, девятый выход. выходного 60 регистра соединен с четвертым выходом блока, десятый выход выходного регист" ра Соединен с пятым выходОм блока,На фиг. 1 приведена структурная схема предлагаемого СП, на Фиг. 2о требуемом количестве циклов, т.ео степени аппроксимирующего полинома, для каждой конкретной функции накаждом подинтервале разложения, которая предварительно заносится в ЗУ 8,получается при решении задачи аппроксимации элементарной, функции на ЦВМизвестными методами. Максимальнаятребуемая разрядность вводимого ЗУ 8может быть определена из следующеговыражения: 10 К "СЕТ (,1 оф йо)/ где К - разрядность ЗУ 8,СЕТЬ - наименьшее целое, большеили равное А; 15и - максимальная степень полинома, определяемая по наихудшему случаю (из 1) .Для прототипа п=5, тогда8=3., Максимальный объем 20Зу 8ы= 1 к 55 где 5 - разрядность старшего сегмента кода аргумента, опреде-ляющая количество подинтервалов разложения (Ь опреде-.ляет адресное пространстводля ЗУ 8 и поступает на адресные входы со сдвигателя 3),количество элемеитарныхфункций, реализуемых процессором.В соответствии с кодами, записанными в ЗУ 8, возможны следующие,ситуации при вычислении полинома:К = 000 - полином нулевой степени, т.е. значения функции берутсянепосредственно из таблицы, хранящейся в ЗУ 7, время вычисления значения элементарной функции равно времени предварительной обработки аргумента и выборки из ЗУ 7, т.е.Т Т+ Ть001 - полином первой степени, 45.т.е.= а+ а х, а время вычисления Т=Т + Т + 1+ Т , где Т - времявыполнения операции умноженйя в устройстве 5; Т- время выполненияоперации сложения в сумматоре б. 50К = 010 - полином второй степени,т;е. ф =а + х 1 а+ ха),=Т,фТэ+Я )Т 1+Т,у =011 - полином третьей степени, =100 - пблином четвертой степеницо"1 д"ОЮООХЩ 1Т =Т+Тб+ 41 Т+ТТ =101 - полином-пятой степениР.а+Иа+МО,+Х О+Х 104.а ХГП 6 ОТ =твтэ+БГГч+ЯВ любом случае прим ф 3 процессвычисления значения полинома начи-.нается с выборки старшего коэффи циента разложения о из ЗУ 4, подачи его на устройство 5, где он умножается на приведенное значение аргумента, далее происходит суммирование со следующим коэффициентом б ,выбранном во время выполнения операции умножения из ЗУ 7, на сумматоре 6, после передачи суммы через регистр 10 функции и группу элементов 11 на множительное устройство 5 она умножается на значение приведенного аргумента Ж . Такой процесс продолжается до момента сравнения кодов, выбранных в первый момент иэ Зу 8, с кодом счетчика циклов в бло- ке управления 9, что свидетельствует о необходимости прекращения процесса вычисления. После этого значение элементарной функции записывается в выходной регистр 12 и выдается во внешнее устройствов частном случае в ЦВМ).Введение ЗУ 8 и его связи с блоком 9 потребовало внесения некоторых изменений в схему блока управления. В частном случае они сводятся к введению схемы сравнения кодов, которая легко реализуется сумматором по модулю 2, соединенной с выходами ЗУ 8 и выходами счетчика циклов в блоке 9. Выход схемы сравнения кодов несет информацию о необходимости окончания процесса вычисления значений полинома раньше для этой цели использоваася импульс переполнения со счетчика циклов) .Блок 9 работает следующим образом. По сигналу "Пуск", поступающему от командного процессора, триггер 14 открывает элемент 15 И, и тактовые импульсы от ГТИ 13 поступают на вход счетчика 16. С выхода этого счетчика кодовые комбинации подаются на вход дешифратора 17, где дешифруются в соответствии с временными диаграммами необходимые такты. Признаки функций, осведомительные сигналы и выделенные тактовые сигналы подаются на вход комбинационной схемы, реализованной на элементах 21-28 и элементах ИЛИ 30-34, которая Формирует управляющие сигналы, поступающие через регистр 20 на входы остальных блоков устройства и инициализирующие .их функционирование, После каждого сигнала, осуществляющего разрешение передачи термов формулы Горнера на устройство 5, содержимое счетчика 18 увеличивается на единицу. Коды, поступающие с ЗУ 8 и счетчика 18 на схему сравнения кодов 19, сравйиваются послед" ней и в момент их совпадения вырабатывается импульс "Стоп", который устанавливает триггер 14 в состояние "0", закрывающее элемент 15, и переписывает результат вычислений е выходной регистр 12 (Фиг. 1). На1023339 Пуп дфю Фй йм Ф.Ф

СмотретьЗаявка

3287934, 18.05.1981

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

УГРЮМОВ ЕВГЕНИЙ ПАВЛОВИЧ, ЛУЦИЙ СЕРГЕЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/11

Метки: процессор, специализированный

Опубликовано: 15.06.1983

Код ссылки

<a href="https://patents.su/10-1023339-specializirovannyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Специализированный процессор</a>

Предыдущий патент: Вероятностный коррелометр

Следующий патент: Устройство для решения дифференциальных уравнений

Случайный патент: Способ обработки резанием самовращающимся многолезвийным инструментом