Способ преобразования дискретных сигналов и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 940200

Авторы: Лев, Маркарян, Павличенко, Сирбиладзе

Текст

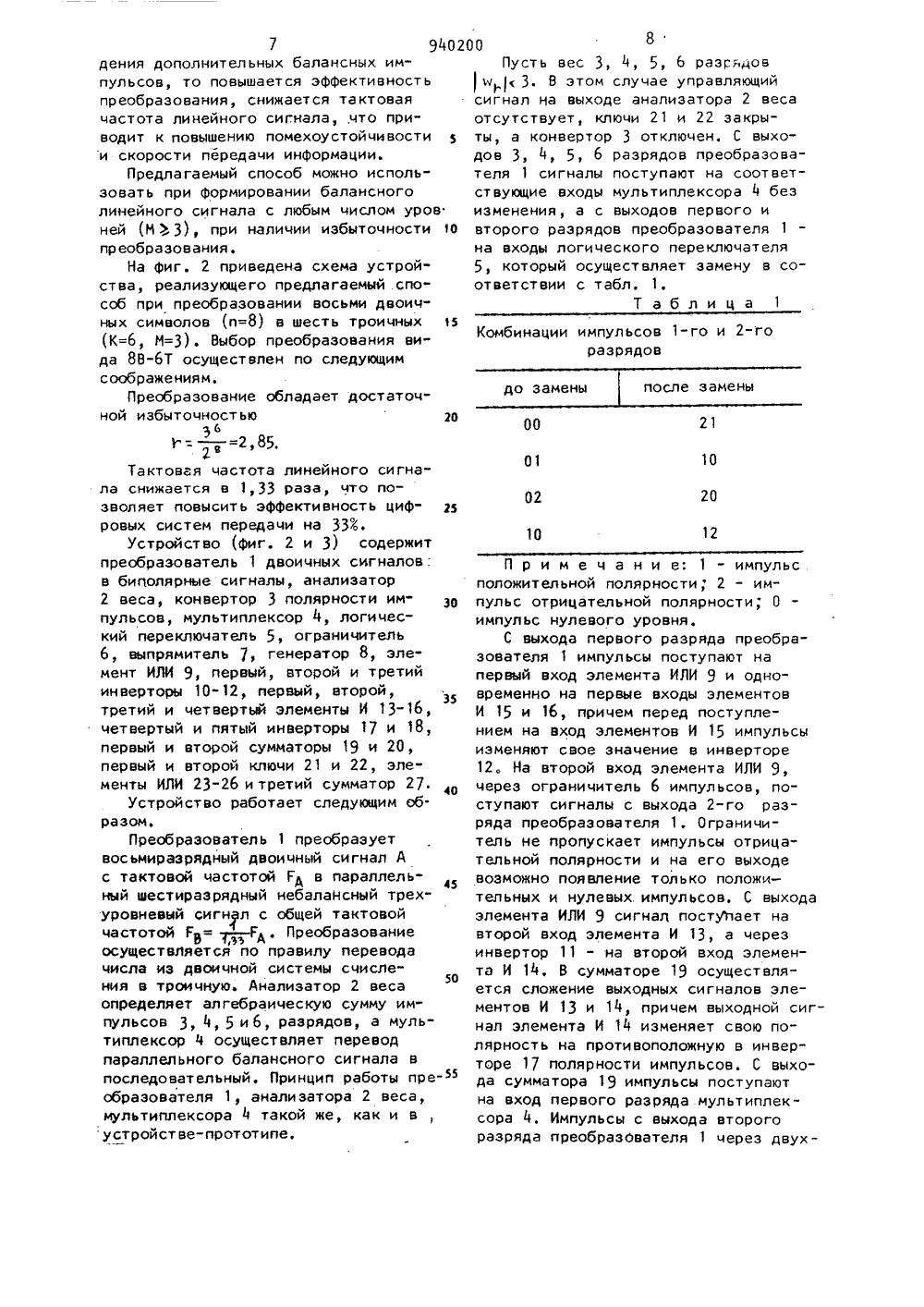

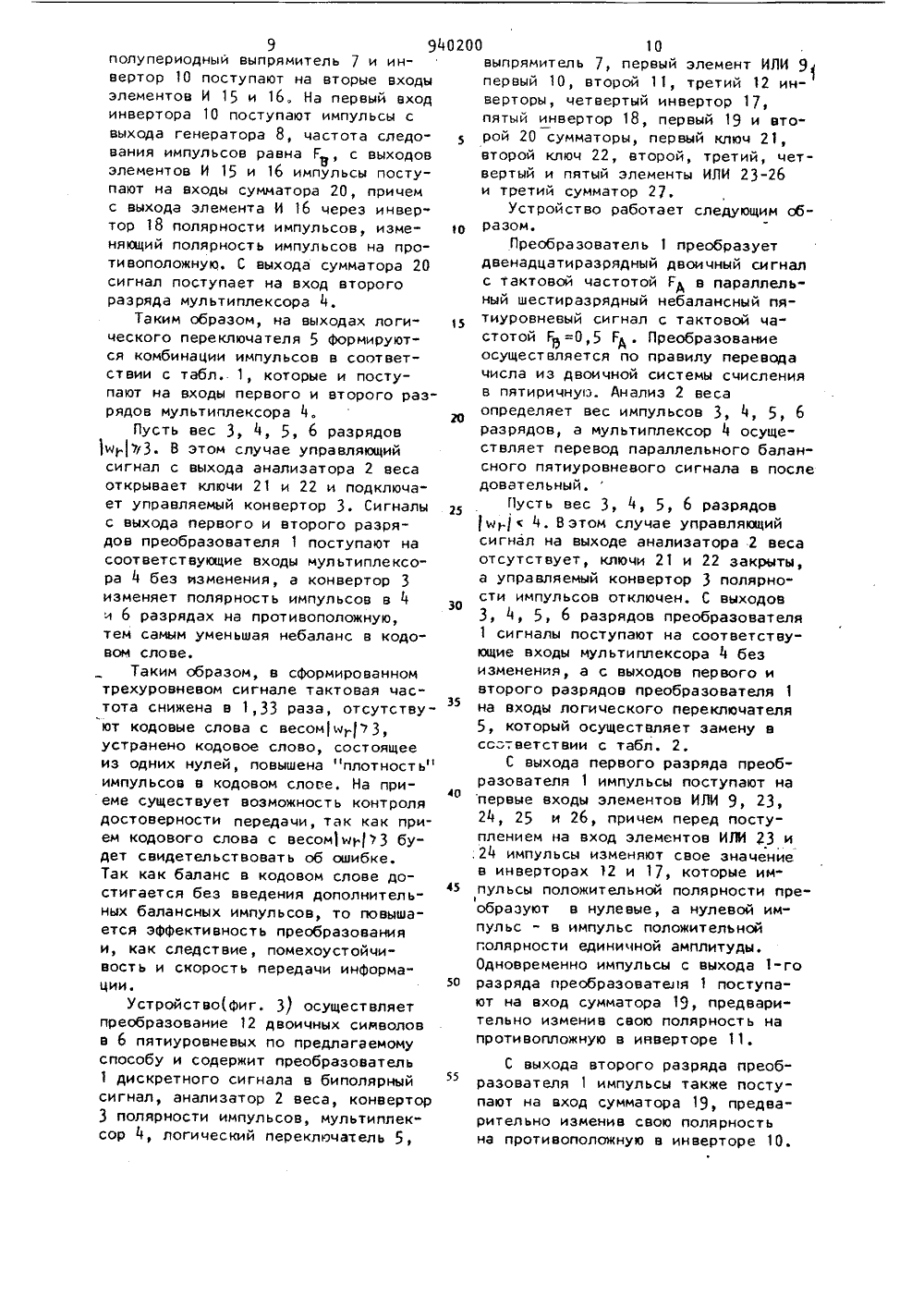

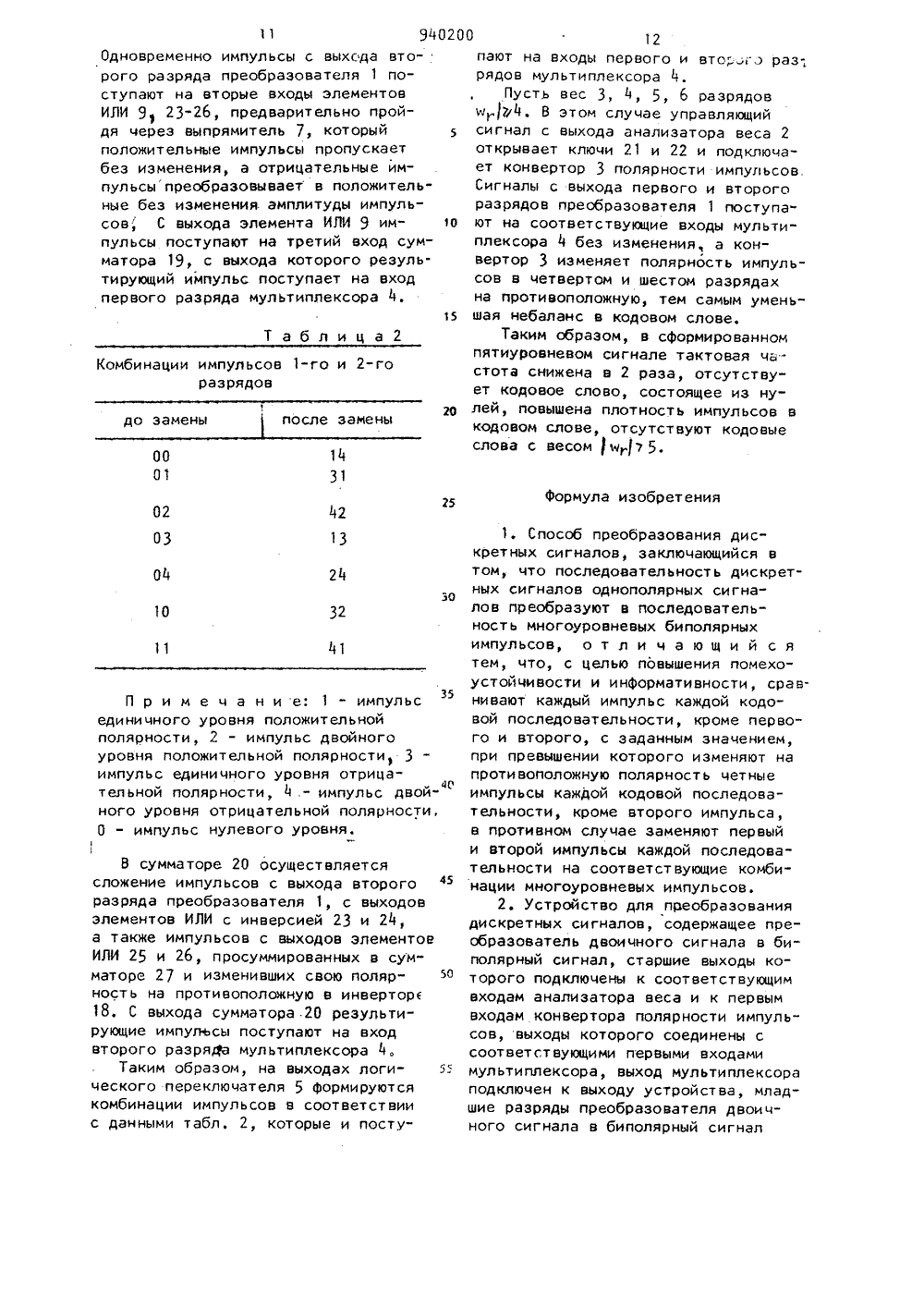

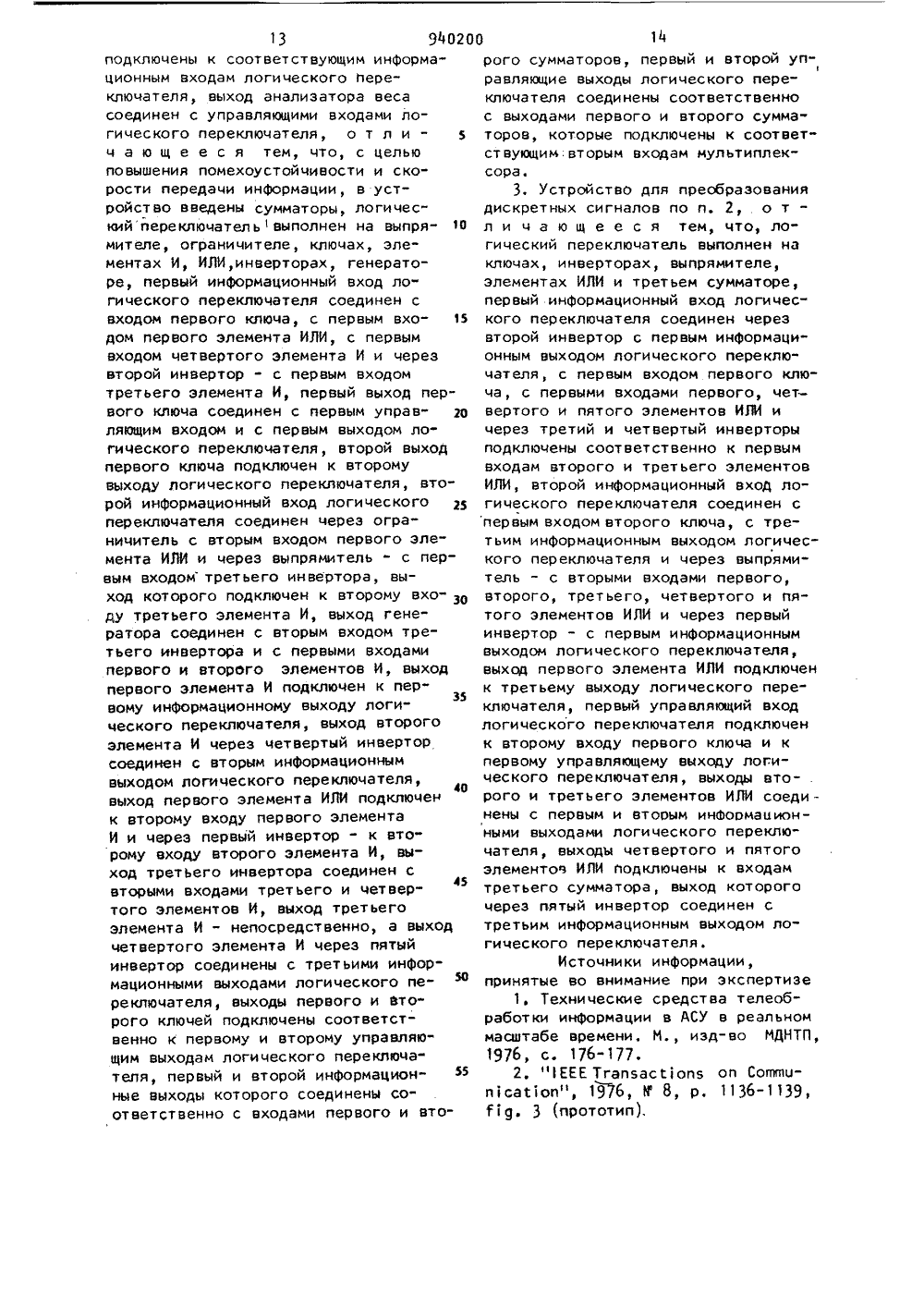

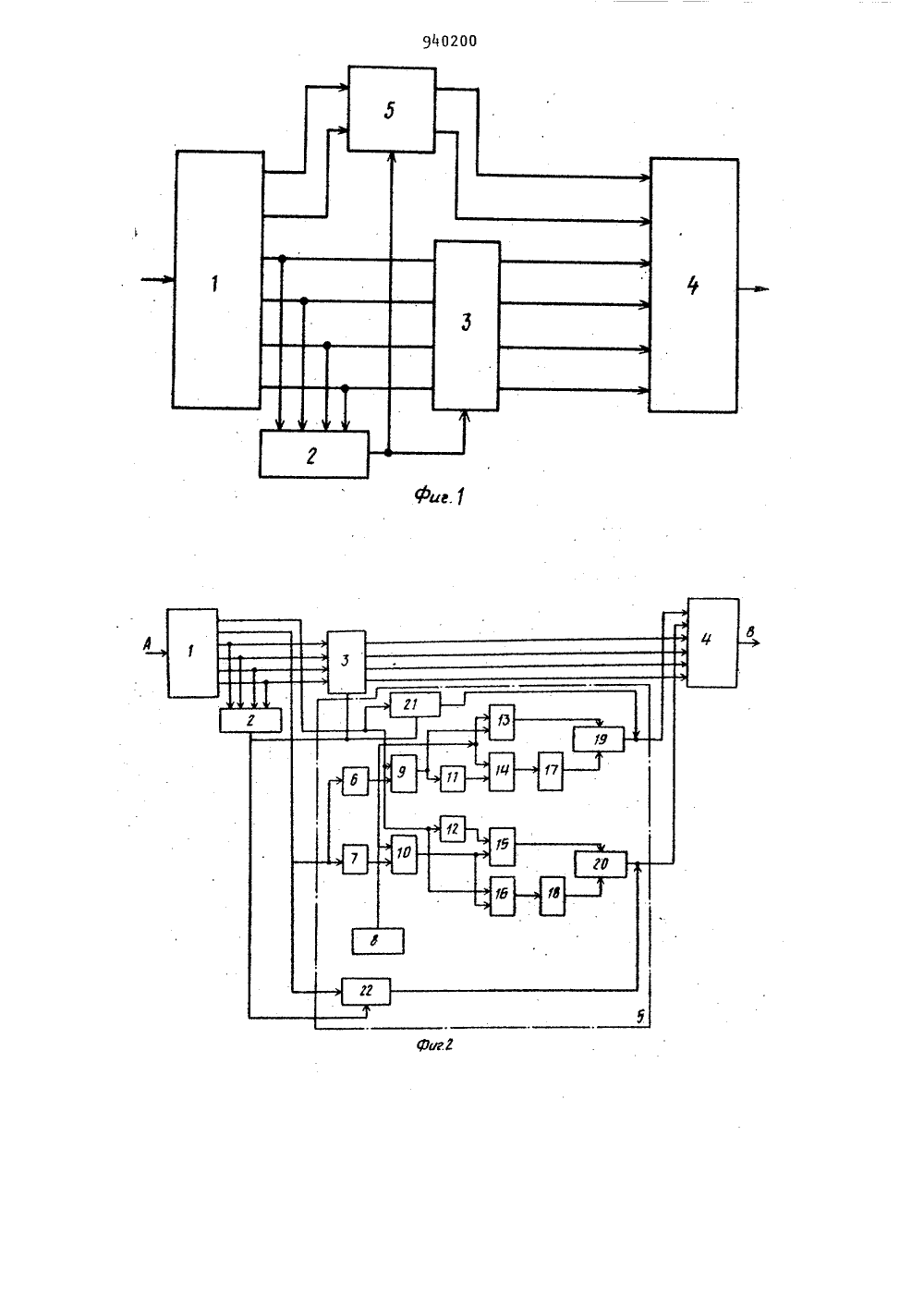

Союз СоветскихСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 940200(53)М. Кл, 0 08 С 19/28 с присоединением заявки РЙ 3 Ьеудерстеанвй квинтет СССР ае делен язееретееий н етерытвйДата опубликования описания 07,06,82(71) Заявитель Одесский электротехнический институт свя(54) СПОСОБ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ1Изобретение относится к технике цифровых систем передачи и может использоваться при передаче цифровых сигналов в линейных трактах, оборудованных регенераторами мно 5 гоуровневых сигналов.Известен способ преобразования двоичного сигнала в квазитроичный балансный сигнал и устройство для его реализации, в котором баланс-о ный многоуровневый сигнал получается путем преобразования исходного двоичного сигнала в балансный трехуровневый сигнал 11.Недостатком данного способа и реализующего его устройства является ограниченная область применения, поскольку они предназначены только на формирование квазитроичных балансных сигналов. гоНаиболее близким по технической сущности к предлагаемому является способ преобразования дискретных сигналов, заключающийся в том, что из последовательности дискретныход ополярных сигналов формируютпоследовательности многоуровневыхбиполярных импульсов и устройстводля преобразования дискретных сигналов, содержащее преобразователь двоич.ного сигнала в биполярный сигнал,старшие выходы которого подключенык соответствующим входам анализатора веса и к первым входам конвертора полярности импульсов, выходыкоторого соединены с соответствующими первыми входами мультиплексора,выход последнего подключен к выходуустройства, младшие разряды преобразователя дискретного сигнала в биполярный сигнал подключены к соответствующим информационным входам логического переключателя, выход анализатора веса соединен с управляющими,входами логического переключателя,первый выход которого подключен к управляющему входу конвертора полярно"сти импульсов, второй и третий выходыЭ 9 Й 020логического переключателя соединеныс вторыми входами мультиплексора2 .Недостатком известного способа иреализующего его устройства являетсянизкая помехоустойчивост,ь и низкаяинформативность.Цель изобретения - повышение помехоустойчивости и информативности,Поставленная цель достигаетсятем, что в способе преобразования дис-Окретных сигналов, заключающемся втом, что из последовательности дискретных однополярных сигналов Формируют последовательности многоуровневых биполярных сигналов, в которых 15сравнивают каждый импульс каждой кодовой последовательности, кроме первого и второго, с заданным значением, при превышении которого изменяютна противоположную полярность четныеимпульсы каждой кодовой последовательности, кроме второго импульса,в противном случае заменяют первыйи второй импульсы каждой последовательности на соответствующие комби- д 5нации многоуровневых импульсов,В устройство для преобразованиядискретных сигналов, содержащеепреобразователь двоичного сигналав биполярный сигнал, старшие выходы которого подключены к соответствующим входам анализатора веса и кпервым входам конвертора полярностиимпульсов, выходы которого соединеныс соответствующими первыми входами35мультиплексора, выход последнего подключен к выходу .устройства, младшиеразряды преобразователя двоичногосигнала в биполярный сигнал подключены к соответствующим информацион 40ным входам логического переключателя,,выход анализатора веса соединен суправляющими входами логического переключателя, первый выход которого под"ключен к управляющему входу конвер 45тора полярности импульсов, второй итретий выходы логического переключателя соединены с вторыми входамимультиплексора, введены сумматоры,логический переключатель выполнен навыпрямителе, ограничителе, ключах,элементах И, ИЛИ, инверторах, генераторе, первый информационный входлогического переключателя соединенс входом первого ключа, с первым входом первого элемента ИЛИ, с первымвходом четвертого элемента И и черезвторой инвертор - с первым входомтретьего элемента И, первый выход первого ключа соединен с первым управляющим входом и с первым выходом логического переключателя, второй выход первого ключа подключен к второму выходу логического переключателя, второй информационный вход логического переключателя соединен через ограничитель с вторым входом первого элемента ИЛИ и через вь 1 прямитель - с первым входом третьего инвертора, выход которого подключен к второму входу третьего элемента И, выход генератора соединен с вторым входом третьего инвертора и с первыми входами первого и второгоэлементов И, выход первого элемента И подключен к первому информационному выходу логического переключателя, выход второго элемента И через четвертый инвертор соединен с вторым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен , к второму входу первого элемента И и через первый инвертор - к второму входу второго элемента И, выход третьего инвертора соединен с вторыми входами третьего и четвертого элементов И, выход третьего элемента И - непосредственно, а выход четвертого элемента И через пятый инвертор соединен с третьими ияформационными выходами логического переключателя, выходы первого и второго ключей подключены соответственно к первому и второму управляющим выходам логичес" кого переключателя, первый и второй информационные выходы которого соединены соответственно с входами первого и второго сумматоров, первый и второй управляющие выходы логического переключателя соединены соответственно с выходами первого и второго сумматоров, которые подключены к соответствующим вторым входам мультиплексора.Логическийпереключатель выполнен на ключах, инверторах, выпрямителе, элементах ИЛИ и на третьем сумматоре, первый информационный вход логического переключателя соединен через второй инвертор с первым инФормационным выходом логического переключателя, с первым входом первого ключа, с первыми входами первого, четвертого и пятого элементов ИЛИ и через третий и четвертый инверторы подключены соответственно к первым входам второго и третьего элементов ИЛИ, второй информационный вход5 940 логического переключателя соединен с первым входом второго ключа, с третьим информационным выходом логического переключателя и через выпрямитель - с вторыми входами первого, второго, третьего, цетвертого и пятого элементов ИЛИ и церез первый инвертор - с первым информационным выходом логического переключателя выход первого элемента 1 о ИЛИ подключен к третьему выходу логического переключателя, первый уп - равляющий вход логического переключателя подключен к второму входу первого ключа и к первому управляюще му выходу логического переключателя, выходы второго и третьего элементов ИЛИ соединены с первым и вторым информационными выходами логического переключателя, выходы четвертого и пятого элементов ИЛИ подключены к входам третьего сумматора, выход которого через пятый инвертор соединен с третьим информационным выходом логического переключателя.На фиг. 1 представлена обобщенная схема устройства для осуществления спо соба; на Фиг.2 и 3 - варианты устройства с различным преобразованием.Устройство содержит ( фиг. 1/ преобразователь 1 последовательного двоичного сигнала в биполярный сигнал, анализатор 2 веса, инвертор 3 полярности импульсов, мультиплексор 4 и логический переключатель 5.Для пояснения последовательности35 способа рассмотрим работу обобщенной схемы устройства (фиг. 1). На вход преобразователя 1 подается исходный дискретный сигнал с такто" вой частотой ГА . Преобразователь работает по правилу перевода числа из двоичной системы сцисления в систему счисления с основанием И ) 2 при этом И двоичных импульсов заменяются на К И-уровневых (пъК), а общая тактовая частота сигнала снижается в и/К раз. На выходах преобразователяФормируется К-разрядное И-уровневое параллельное кодовое слово из множества разрешенных кодовых слов. В анализаторе 2 веса вычис. ляется алгебраическая сумма значений импульсов всех разрядов, кроме первого и второго. Бсли вычисленное значение превышает по абсолютной величине порог 1 и)соп 5 С, то анализатор 2 веса вырабатывает управляющий сигнал, который отключает 25 200 6логический переключатель 5 и включает конвертор 3 полярности импульсов,В конверторе 3 полярности импульсов,принцип работы которого такой же,как и в прототипе, осуществляетсяизменение полярности импульсов в четных разрядах, кроме второго, чтоуменьшает небаланс в кодовом слове.Логическийпереключатель 5 при этомотключен и импульсы первого и второго разряда подаются на мультиплексор 4 без изменения, последний осуществляет перевод параллельного многоуровневого балансного сигнала впоследовательный линейный сигнал стактовой частотой Гв - К/и Г .6 сли же алгебраическая суммаи,ссоп 51, то на выходе анализатора 2 веса управляющий сигнал отсутствует, конвертор 3 полярностиимпульсов отключается и импульсы всехразрядов, кроме первого и второгоподаются на мультиплексор 4 без изменения. В логическом переключателе5 осуществляется замена импульсовпервого и второго разрядов новымикомбинациями импульсов, которыминачинаются избыточные кодовые слова. Сформированное таким образомпараллельное многоуровневое балансное кодовое слово преобразуется вмультиплексоре 4 в последователь"ный линейный сигнал с тактовой частотой ГВ=К/п.ГА (Г 1 сГ ).Для сохранения однозначности декодирования на приеме в схему декодера также вводится логический перекюцатель, который оценивают импульсы первого и второго разрядов,Бсли принятое кодовое слово принадлежит к числу избыточных, то в ло,гическом переключателе осуществляетсязамена импульсов первого и второгоразрядов, обратная замене, осуществленной на передаче. В противномслучае импульсы первого и второгоразрядов не изменяются, а изменяются полярности импульсов в четныхразрядах кодового слова.Таким образом, в результате преобразования в сформированном многоуровневом сигнале отсутствуют кодовыеслова с большим весомустраняетсякодовое слово, состоящее из однихнулей, существует возможность контроля достоверности передачи на приеме, повышается плотность импульсовв кодовом слове. Поскольку балансв кодовом слове достигается без ввезрдоввляющий ра 2 веса закрыС выхо- еобразоваа соответора 4 без вого ивателяючателя мену в соц а 1 7 9402008дения дополнительных балансных им- Пусть вес 3, 4, 5, 6 рапульсов, то повышается эффективностьис 3. В этом случае упрапреобразования, снижается тактовая сигнал на выходе анализаточастота линейного сигнала, .что при- отсутствует, ключи 21 и 22водит к повышению помехоустойчивости 5 ты, а конвертор 3 отключени скорости передачи информации. дов 3, 4, 5, б разрядов прПредлагаемый способ можно исполь- теля 1 сигналы поступают нзовать при формировании балансного ствующие входы мультиплекслинейного сигнала с любым числом уров изменения, а с выходов перней (И3), при наличии избыточности о второго разрядов преобразопреобразования. на входы логического переклНа фиг. 2 приведена схема устрой, который осуществляет заства, реализующего предлагаемый .спо- ответствии с табл. 1.соб при преобразовании восьми двоич- Т аблиных символов (п=8) в шесть троичных 15(К=6, И=3). Выбор преобразования вида 8 ВТ осуществлен по следующимсоображениям.Преобразование обладает достаточной избыточностью зо211"= - =2 85,2 фТактовая частота линейного сигна 01ла снижается в 1,33 раза, что позволяет повысить эффективность циф- у 502 20ровых систем передачи на 33.Устройство (фиг. 2 и 3) содержит12преобразователь 1 двоичных сигналов:в биполярные сигналы, анализатор2 веса, конвертор 3 полярности импульсов, мультиплексор 4, логический переключатель 5, ограничитель6, выпрямитель 7, генератор 8, элемент ИЛИ 9, первый, второй и третийинверторы 10- 12, первый, второй,третий и четвертый элементы И 13- 16,четвертый и пятый инверторы 17 и 18,первый и второй сумматоры 19 и 20,первый и второй ключи 21 и 22, элементы ИЛИ 23-26 и третий сумматор 27 40Устройство работает следующим об.разом.Преобразователь 1 преобразуетвосьмиразрядный двоичный сигнал Ас тактовой частотой ГА в параллельный аестиразрядный небалансный трехуровневый сигнал с общей тактовойчастотой ГВ= Т в -ГА . Преобразованиеосуществляется по правилу переводачисла из двоичной системы счисления в троичную. Анализатор 2 веса50определяет алгебраическую сумму импульсов 3, 4, 5 иб, разрядов, а мультиплексор Ч осуществляет переводпараллельного балансного сигнала впоследовательный. Принцип работы пре образователя 1, анализатора 2 веса,мультиплексора 4 такой же, как и вустройстве-прототипе. Комбинации импульсов 1-го и 2-го разрядов00 10 1 О Примечание: 1-импульсположительной полярности; 2 - импульс отрицательной полярности; 0импульс нулевого уровня,выхода первого разряда преобразователя 1 импульсы поступают напервый вход элемента ИЛИ 9 и одновременно на первые входы элементовИ 15 и 16, причем перед поступлением на вход элементов И 15 импульсыизменяют свое значение в инверторе12. На второй вход элемента ИЛИ 9,через ограничитель 6 импульсов, поступают сигналы с выхода 2-го разряда преобразователя 1, Ограничитель не пропускает импульсы отрицательной полярности и на его выходевозможно появление только положительных и нулевых. импульсов. С выходаэлемента ИЛИ 9 сигнал поступает навторой вход элемента И 13, а черезинвертор 11 - на второй вход элемента И 14, В сумматоре 19 осуществляется сложение выходных сигналов элементов И 13 и 14, причем выходной сигнал элемента И 14 изменяет свою полярность на противоположную в инверторе 17 полярности импульсов. С выхода сумматора 19 импульсы поступаютна вход первого разряда мультиплексора 4. Импульсы с выхода второгоразряда преобразователя 1 через двух40200 10 50 9 9полупериодный выпрямитель 7 и инвертор 10 поступают на вторые входыэлементов И 15 и 16. На первый входинвертора 10 поступают импульсы свыхода генератора 8, частота следования импульсов равна Г , с выходовэлементов И 15 и 16 импульсы поступают на входы сумматора 20, причемс выхода элемента И 1 б через инвер"тор 18 полярности импульсов, изменяющий полярность импульсов на противоположную. С выхода сумматора 20сигнал поступает на вход второгоразряда мультиплексора 4,Таким образом, на выходах логи"ческого переключателя 5 Формируются комбинации импульсов в соответствии с табл 1, которые и поступают на входы первого и второго разрядов мультиплексора 4.Пусть вес 3, 4, 5, б разрядов1 хдЪ 3. В этом случае управляющийсигнал с выхода анализатора 2 весаоткрывает ключи 21 и 22 и подключает управляемый конвертор 3. Сигналыс выхода первого и второго разрядов преобразователя 1 поступают насоответствующие входы мультиплексора 4 без изменения, а конвертор 3изменяет полярность импульсов в 4и 6 разрядах на противоположную,тем самым уменьшая небаланс в кодовом слове.Таким образом, в сформированномтрехуровневом сигнале тактовая частота снижена в 1,33 раза, отсутствуют кодовые слова с весомиг 173,устранено кодовое слово, состоящееиз одних нулей, повышена "плотность"импульсов в кодовом слове, На приеме существует возможность контролядостоверности передачи, так как прием кодового слова с весом) и 7 3 будет свидетельствовать об ошибке.Так как баланс в кодовом слове достигается без введения дополнительных балансных импульсов, то повышается эффективность преобразованияи, как следствие, помехоустойчивость и скорость передачи информации.Устройствофиг. 3) осуществляетпреобразование 12 двоичных символовв б пятиуровневых по предлагаемомуспособу и содержит преобразователь1 дискретного сигнала в биполярныйсигнал, анализатор 2 веса, конвертор3 полярности импульсов, мультиплексор 4, логический переключатель 5,5 ю 35 20 25 эо 4 О 45 выпрямитель 7, первый элемент ИЛИ 9 первый 10, второй 11, третий 12 инверторы, четвертый инвертор 17, пятый инвертор 18, первый 19 и вто" рой 20 сумматоры, первый ключ 21, второй ключ 22, второй, третий, четвертый и пятый элементы ИЛИ 23-26 и третий сумматор 27.Устройство работает следующим образом.Преобразователь 1 преобразует двенадцатиразрядный двоичный сигнал с тактовой частотой ГА в параллельный шестиразрядный небалансный пятиуровневый сигнал с тактовой частотой ГВ =0,5 ГА . Преобразование осуществляется по правилу перевода числа из двоичной системы счисления в пятиричную. Анализ 2 веса определяет вес импульсов 3, 4, 5, б разрядов, а мультиплексор 4 осуществляет перевод параллельного балан" сного пятиуровневого сигнала в после довательный.Пусть вес 3, 4, 5, 6 разрядов к с 4. Вэтом слуцае управляющий сигнал на выходе анализатора 2 веса отсутствует, ключи 21 и 22 закрыты, а управляемый конвертор 3 полярности импульсов отключен. С выходов 3, 4, 5, 6 разрядов преобразователя 1 сигналы поступают на соответствующие входы мультиплексора 4 без изменения, а с выходов первого и второго разрядов преобразователя 1 на входы логического переключателя 5, который осуществляет замену в сс=тветствии с табл. 2.выхода первого разряда преобразователя 1 импульсы поступают на первые входы элементов ИЛИ 9, 23, 24, 25 и 26, причем перед поступлением на вход элементов ИЛИ 23 и 24 импульсы изменяют свое значение в инверторах 12 и 17, которые импульсы положительной полярности преобразуют в нулевые, а нулевой импульс - в импульс положительной голярности единичной амплитуды, Одновременно импульсы с выхода 1-го разряда преобразователя 1 поступают на вход сумматора 19, предварительно изменив свою полярность на противопложную в ияверторе 11. С выхода второго разряда преобразователя 1 импульсы также поступают на вход сумматора 19, предварительно изменив свою полярность на противоположную в инверторе 10.11 94 Одновременно импульсы с выхсда второго разряда преобразователя 1 поступают на вторые входы элементов ИЛИ 91 23-2 б, предварительно пройдя через выпрямитель 7, который положительные импульсы пропускает без изменения, а отрицательные импульсыпреобразовывает в положительные без изменения амплитуды импульсов, С выхода элемента ИЛИ 9 импульсы поступают на третий вход сумматора 19, с выхода которого результирующий импульс поступает на вход первого разряда мультиплексора 4.Таблица 2Комбинации импульсов 1-го и 2-горазрядовдо заменыпосле замены00010200 12 5 1 О 15 20 пают на входы первого и втог.э раз; рядов мультиплексора 4.Пусть вес 3, 4, 5, б разрядов иД 4, В этом случае управляющий сигнал с выхода анализатора веса 2 открывает ключи 21 и 22 и подключает конвертор 3 полярности импульсов Сигналы с выхода первого и второго разрядов преобразователя 1 поступают на соответствующие входы мультиплексора 4 без изменения, а конвертор 3 изменяет полярность импульсов в четвертом и шестом разрядах на противоположную, тем самым уменьшая небаланс в кодовом слове.Таким образом, в сформированном пятиуровнеаом сигнале тактовая частота снижена в 2 раза, отсутствует кодовое слово, состоящее из нулей, повышена плотность импульсов в кодовом слове, отсутствуют кодовые слова с весоми/7 5.25 42 13 02 03 04 10 32 41 П р и м е ч а н и е; 1 - импульс35 единичного уровня положительной полярности, 2 - импульс двойного уровня положительной полярности, 3 импульс единичного уровня отрица 4 Ртельной полярности, 4 - импульс двойного уровня отрицательной полярности, 0 - импульс нулевого уровня.1 В сумматоре 20 осуществляется сложение импульсов с выхода второго 45 разряда преобразователя 1, с выходов элементов ИЛИ с инверсией 23 и 24, а также импульсов с выходов элементов ИЛИ 25 и 26, просуммированных в сумматоре 27 и изменивших свою полярность на противоположную в инвертор 18, С выхода сумматора .20 результирующие импульсы поступают на вход второго разряда мультиплексора 4.Таким образом, на выходах логи ческого переключателя 5 формируются комбинации импульсов в соответствии с данными табл2, которые и постуформула изобретения 1, Способ преобразования дискретных сигналов, заключающийся в том, что последовательность дискретных сигналов однополярных сигналов преобразуют в последовательность многоуровневых биполярных импульсов, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости и информативности, сравнивают каждый импульс каждой кодовой последовательности, кроме первого и второго, с заданным значением, при превышении которого изменяют на противоположную полярность четные импульсы каждой кодовой последовательности, кроме второго импульса, в противном случае заменяют первый и второй импульсы каждой последовательности на соответствующие комбинации многоуровневых импульсов.2. Устройство для преобразования дискретных сигналов, содержащее преобразователь двоичного сигнала в биполярный сигнал, старшие выходы которого подключены к соответствующим входам анализатора веса и к первым входам конвертора полярности импульсов, выходы которого соединены с соответствующими первыми входами мультиплексора, выход мультиплексора подключен к выходу устройства, младшие разряды преобразователя двоичного сигнала в биполярный сигналработки информации в АСУ в реальноммасштабе времени, М., иэд-во ИДНТП,1976, с. 176-177.2, " ЕЕЕ Тгапэас 1 опз оп Согпгпцп 1 сас 1 оп", 1976, й 8, р, 1136-1139,1 р. 3 (прототип),13 94020 подключены к соответствующим информационным входам логического Переключателя, выход анализатора веса соединен с управляющими входами логического переключателя, о т л и - 5 ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости и скорости передачи информации, в устройство введены сумматоры, логичес" кийпереключатель выполнен на выпря мителе, ограничителе, ключах, элементах И, ИЛИ,инверторах, генераторе, первый информационный вход ло" гического переключателя соединен с входом первого ключа, с первым вхо дом первого элемента ИЛИ, с первым входом четвертого элемента И и через второй инвертор - с первым входом третьего элемента И, первый выход первого ключа соединен с первым управ ляющим входом и с первым выходом логического переключателя, второй выход первого ключа подключен к второму выходу логического переключателя, второй информационный вход логического переключателя соединен через ограничитель с вторым входом первого элемента ИЛИ и через выпрямитель - с первым входом третьего инвертора, выход которого подключен к второму вхо- З 0 ду третьего элемента И, выход генератора соединен с вторым входом третьего инвертора и с первыми входами первого и второго элементов И, выход первого элемента И подключен к пер 35 вому информационному выходу логического переключателя, выход второго элемента И через четвертый инвертор соединен с вторым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен к второму входу первого элемента И и через первый инвертор - к второму входу второго элемента И, выход третьего инвертора соединен с45 вторыми входами третьего и четвертого элементов И, выход третьего элемента И - непосредственно, а выход четвертого элемента И через пятый инвертор соединены с третьими информационными выходами логического пе 50 реключателя, выходы первого и второго ключей подключены соответственно к первому и второму управляющим выходам логического переключателя, первый и второй информационные выходы которого соединены соответственно с входами первого и вто 0 14 рого сумматоров, первый и второй уп" равляющие выходы логического переключателя соединены соответственнос выходами первого и второго сумматоров, которые подключены к соответ"ствующим:вторым входам мультиплексора. 3. Устройство для преобразования дискретных сигналов по и. 2, о тл и ч а ю щ е е с я тем, что, логический переключатель выполнен наключах, инверторах, выпрямителе,элементах ИЛИ и третьем сумматоре,первый информационный вход логичес"кого переключателя соединен черезвторой инвертор с первым информационным выходом логического переключателя с первым входом первого ключа, с первыми входами первого, четвертого и пятого элементов ИЛИ ичерез третий и четвертый инверторыподключены соответственно к первымвходам второго и третьего элементовИЛИ, второй информационный вход логического переключателя соединен спервым входом второго ключа, с третьим информационным выходом логического переключателя и через выпрямитель - с вторыми входами первого,второго, третьего, четвертого и пятого элементов ИЛИ и через первыйинвертор - с первым информационнымвыходом логического переключателя,выход первого элемента ИЛИ подключен к третьему выходу логического переключателя, первый управляющий входлогического переключателя подключенк второму входу первого ключа и кпервому управляющему выходу логического переключателя, выходы второго и третьего элементов ИЛИ соединены с первым и втооым информационными выходами логического переключателя, выходы четвертого и пятого элементов ИЛИ подключены к входам третьего сумматора, выход которого через пятый инвертор соединен с третьим информационным выходом логического переключателя.Источники информации,принятые во внимание при экспертизе 1, Технические средства телеоб 90200акаэ 73/73 Тираж 2 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва; Ж"35, Раущская наб., д, 4/5

СмотретьЗаявка

3229745, 31.12.1980

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ЛЕВ АЛЕКСАНДР ЮЛЬЕВИЧ, МАРКАРЯН ГАРЕГИН СТЕПАНОВИЧ, ПАВЛИЧЕНКО ЮРИЙ АГАФОНОВИЧ, СИРБИЛАДЗЕ ДАВИД АКАКИЕВИЧ

МПК / Метки

МПК: G08C 19/28

Метки: дискретных, преобразования, сигналов

Опубликовано: 30.06.1982

Код ссылки

<a href="https://patents.su/9-940200-sposob-preobrazovaniya-diskretnykh-signalov-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ преобразования дискретных сигналов и устройство для его осуществления</a>

Предыдущий патент: Устройство для приема телесигналов

Следующий патент: Устройство для контроля знаний обучаемых

Случайный патент: Приводное устройство