Способ прямого микропроцессорного управления тиристорным преобразователем и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

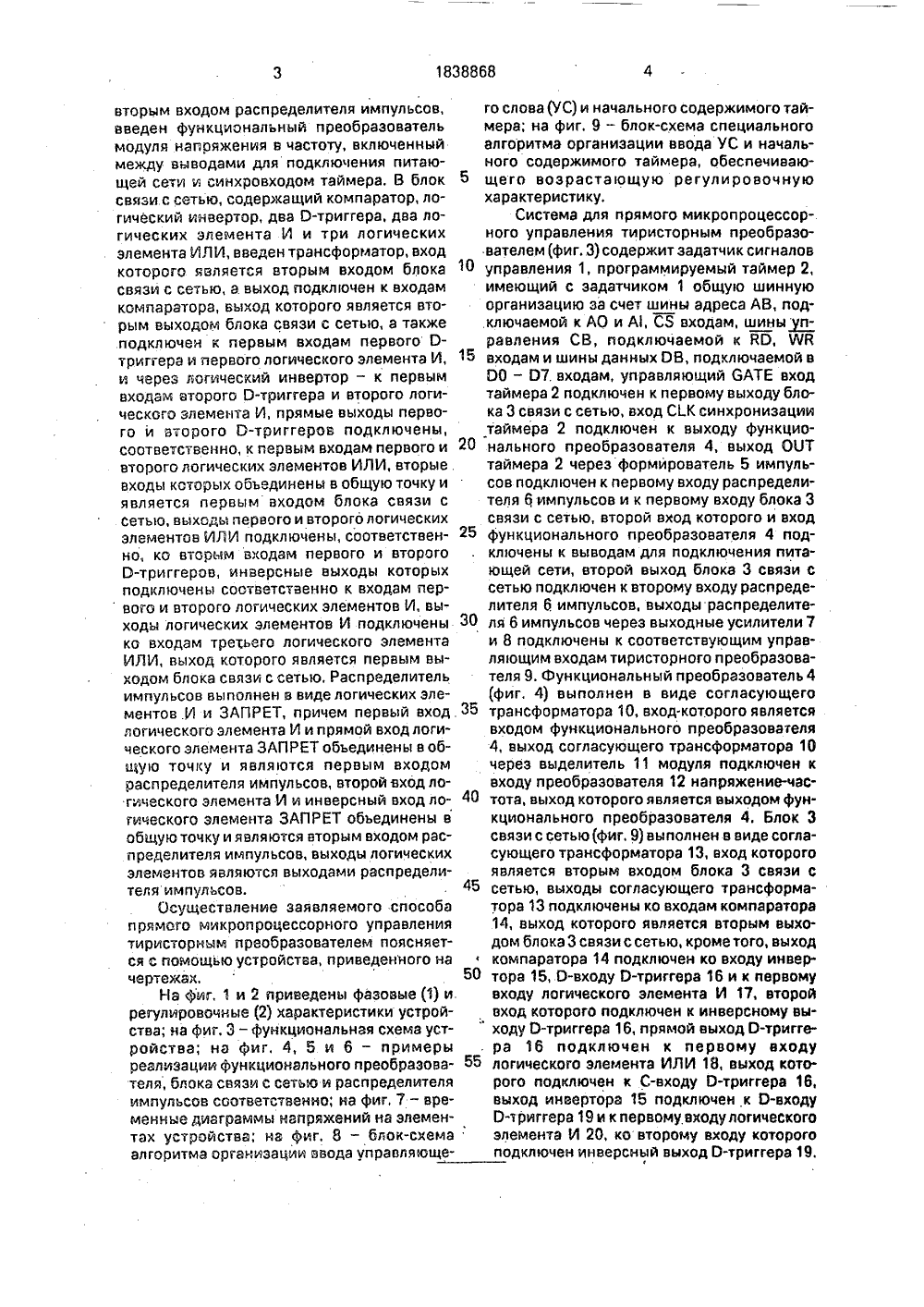

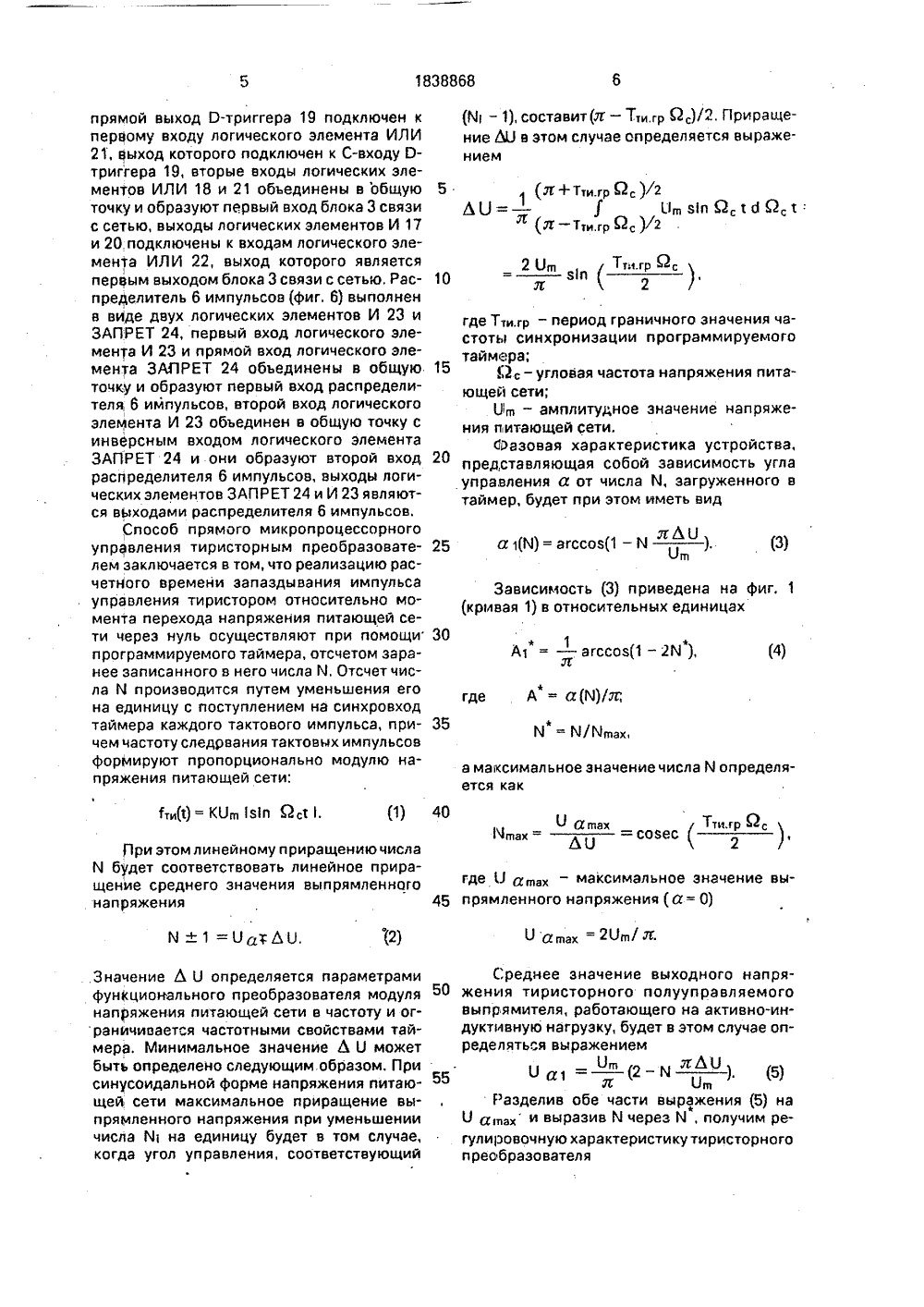

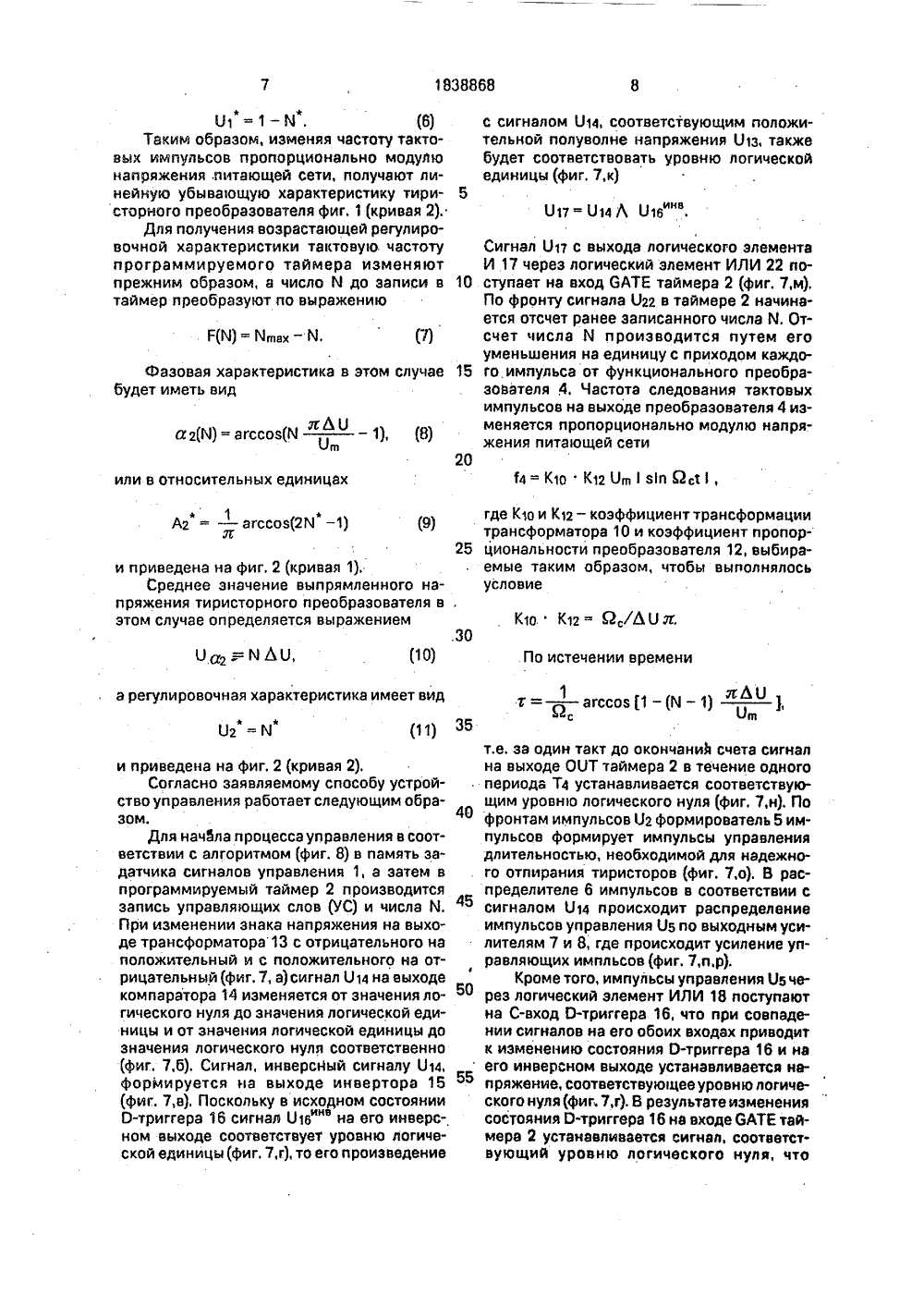

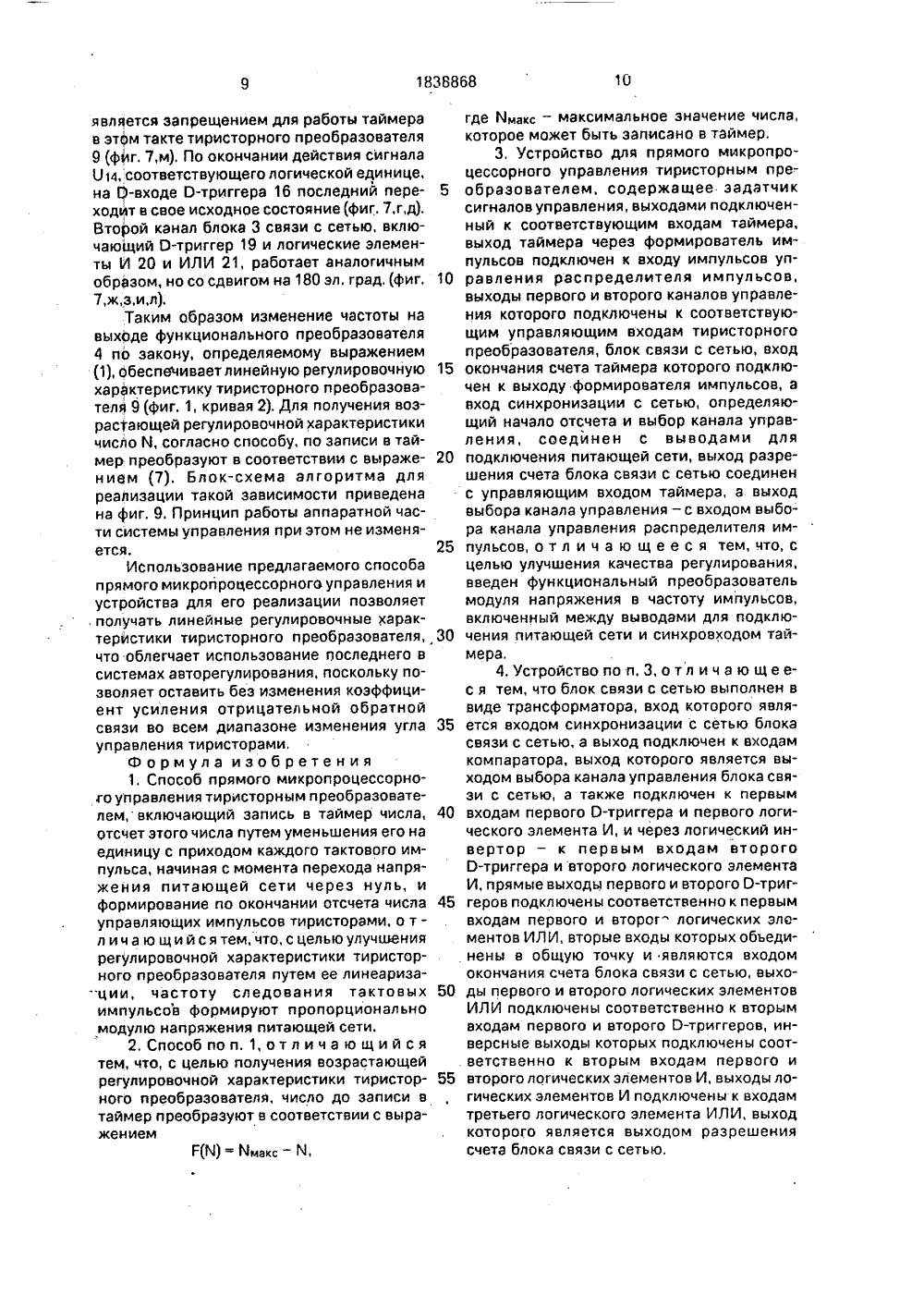

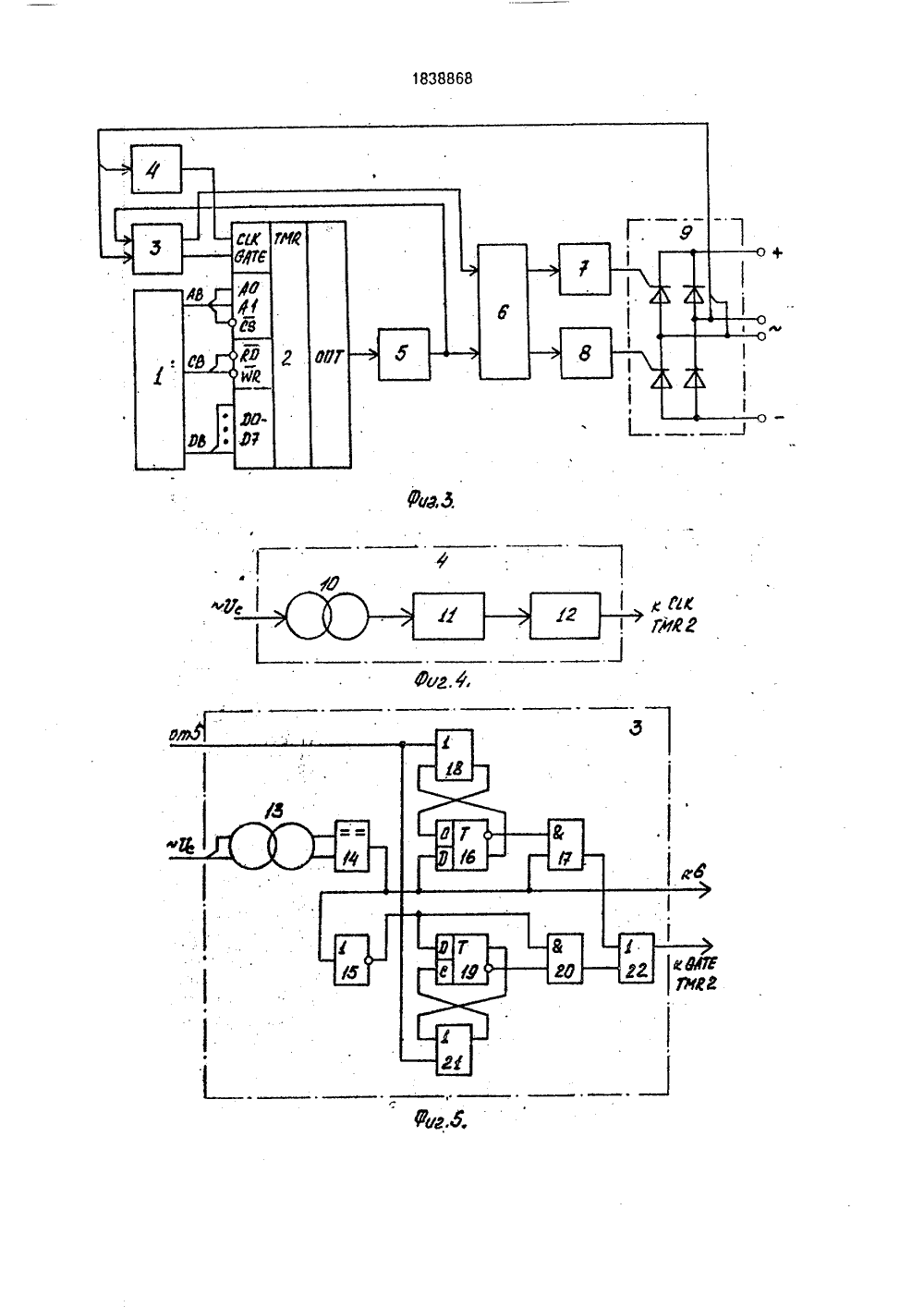

(5)5 НИЕ ИЗОБРЕТЕН О ПАТЕНТ ОИСТ ческии инститлбня, Е.И, Соко айнштейн Э,Г.ы управленияприводами.с, 240.ьство СССР/12, 1990. Мик- риМ ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(73) А.В. Кипенский56) Файнштейн В.ГФропроцессорные системсторными электроЭнергоатомиздат, 1986,Авторское свидетелМ 1660116, кл. Н 02 М 7 4) СПОСОБ ПРЯМОГО МИКРОПРОЦЕС ОРНОГО УПРАВЛЕНИЯ ТИРИСТОРНЫМ Изобретение относится к электротехнике и может быть использовано для управления тиристорными преобразователями,Целью изобретения является улучшение регулировочной характеристики тиристорного преобразователя путем ее линеаризации системой прямого микропроцессорного управления,Цель достигается тем, что в способе прямого микропроцессорного управления тиристорным преобразователем, включающем запись в таймер числа, отсчет этого числа путем уменьшения его на единицу с приходом каждого тактового импульса, начиная с момента синхронизации с напряжением питающей сети, и формирование, по окончании отсчета числа, управляющих импульсов тиристорами, согласно изобретению, частоту следования тактовых импульсов формируют пропорциональной модулю напряжения питающей сети, Для получения возрастающей регулировочной ПРЕОБРАЗОВАТЕЛЕМ И УСТР ВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ(57) Изобретение относится к электротехнике. Цель изобретения - улучшение регулировочной характеристики тиристорного преобразователя путем ее линеаризации системой прямого микропроцессорного управления, Новым в способе является то, что частоту, синхронизирующую работу таймера, формируют пропорционально модулю напряжения питающей сети, Отличительной особенностью устройства является то, что оно снабжено функциональным преобразователем, вход которого предназначен для подключения к шинам напряжения питающей сети, а выход подключен к входу синхронизации таймера, 2 с. и 3 з,п. ф-лы, 9 ил, ф характеристики тиристорного и реобразователя, число до записи в таймер преобразуют в соответствии с выражениемЦ) - Ивах Й,где Ивах - максимальное значение числа, которое может быть записано в таймер,Цель достигается также тем, что в устройство, содержащее задатчик сигналов управления, выходами подключенный к соответствующим входам таймера, а выход таймера через формирователь импульсов подключен к первому входу распределителя импульсов, выходы которого через выходные усилители подключены к соответствующим управляющим входам тиристорного преобразователя, блок связи с сетью, первый и второй входы которого подключены соответственно к выходу формирователя импульсов и к выводам для подключения питающей сети, первый и второй выходы блока связи с сетью соединены соответственно с управляющим входом таймера и сотах устройства; на фиг. 8 - блок-схема эл апгоригиа оргвиивации ввода упрввпааггав- по вторым входом распределителя импульсов, введен функциональный преобразователь модуля напряжения в частоту, включенный между выводами для подключения питающей сети и синхровходом таймера, В блок связи с сетью, содержащий компаратор, логический инвертор, два О-триггера, два логических элемента И и три логических элемента ИЛИ, введен трансформатор, вход которого является вторым входом блока связи с сетью, а. выход подключен к входам компаратора, выход которого является вторым выходом блока связи с сетью, а также подключен к первым входам первого О- триггера и первого логического элемента И, и через логический инвертор - к первым входам второго О-триггера и второго логического элемента И, прямые выходы первого и второго О-триггеров подключены, соответственно, к первым входам первого и второго логических элементов ИЛИ, вторые входы которых объединены в общую точку и является первым входом блока связи с сетью, выходы первого и второго логических элементов ИЛИ подключены, соответственно, ко вторым входам первого и второго О-триггеров, инверсные выходы которых подключены соответственно к входам пер вого и второго логических элементов И, выходы логических элементов И подключены ко входам третьего логического элемента ИЛИ, выход которого является первым выходом блока связи с сетью. Распределитель импульсов выполнен в виде логических элементов.И и ЗАПРЕТ, причем первый вход логического элемента И и прямой вход логического элемента ЗАПРЕТ объединены в общую точку и являются первым входом распределителя импульсов, второй вход логического элемента И и инверсный вход логического элемента ЗАПРЕТ объединены в общаую точку и являются вторым входом распределителя импульсов, выходы логических элементов являются выходами распределителя импульсов.Осуществление заявляемого способапрямого микропроцессорного управления тиристорным преобразователем поясняется с помощью устройства, приведенного на чертежах.На фиг, 1 и 2 приведены фазовые (1) ирегулировочные (2) характеристики устройства; на фиг. 3 - функциональная схема устройства; на фиг. 4, 5 и 6 - примеры реализации функционального преобразователя, блока связи с сетью и распределителя импульсов соответственно; на фиг. 7 - временные диаграммы напряжений на элеменго слова (УС) и начального содержимого таймера; на фиг. 9 - блок-схема специальногоалгоритма организации ввода УС и начального содержимого таймера, обеспечиваю 5 щего возрастающую регупировочнуюхарактеристику,Система для прямого микропроцессор-.ного управления тиристорным преобразователем (фиг. 3) содержит задатчик сигналов10 управления 1, программируемый таймер 2,имеющий с задатчиком 1 общую шиннуюорганизацию за счет шины адреса АВ, под.ключаемой к АО и А 1, СЯ входам, шины травления СВ, подключаемой к ВО, Яйвходам и шины данных ОВ, подключаемой вОО - О 7. входам, управляющий 6 АТЕ входтаймера 2 подключен к первому выходу блока 3 связи с сетью, вход С К синхронизациитаймера 2 подключен к выходу функцио 20 нального преобразователя 4, выход СОТтаймера 2 через формирователь 5 импульсов подключен к первому входу распределителя 5 импульсов и к первому входу блока 3связи с сетью, второй вход которого и вход25 функционального преобразователя 4 подключены к выводам для подключения питающей сети, второй выход блока 3 связи ссетью подключен к второму входу распределителя 6 импульсов, выходы распределите 30 ля 6 импульсов через выходные усилители 7и 8 подключены к соответствующим управляющим входам тиристорного преобразователя 9. Функциональный преобразователь 4(фиг. 4) выполнен в виде согласующего35 трансформатора 10, вход. которого являетсявходом функционального преобразователя4, выход согласующего трансформатора 10через выделитель 11 модуля подключен квходу преобразователя 12 напряжение-час 40 тота, выход которого является выходом функционального преобразователя 4. Блок 3связи с сетью(фиг, 9) выполнен в виде согласующего трансформатора 13, вход которогоявляется вторым входом блока 3 связи с45 сетью, выходы согласующего трансформатора 13 подключены ко входам компаратора14, выход которого является вторым выходом блока 3 связи с сетью, кроме того, выходг компаратора 14 подключен ко входу инвер 50 тора 15, О-входу О-триггера 16 и к первомувходу логического элемента И 17, второйвход которого подключен к инверсному вы" ходу О-триггера 16, прямой выход О-тригге. ра 16 подключен к первому входу55 логического элемента ИЛИ 18, выход которого подключен к С-входу О-триггера 16,выход инвертора 15 подключен к О-входуО-триггера 19 и к первому входу логическогоемента И 20, ко второму входу которогодключен инверсный выход О-триггера 19.(10) 01 = 1 - й, (6)Таким образом, изменяя частоту тактовых импульсов пропорционально модулю напряжения .питающей сети, получают линейную убывающую характеристику тиристорного преобразователя фиг. 1 (кривая 2).Для получения возрастающей регулировочной характеристики тактовую частоту программируемого таймера изменяют прежним образом, а число й до записи в таймер преобразуют по выражению Г(й)=й -й. (7) Фаэовая характеристика в этом случаебудет иметь вид а 2(й) = агссоз(й 1), (8)АДЬО или в относительных единицах и приведена на фиг. 2 (кривая 1).Среднее значение выпрямленного напряжения тиристорного преобразователя в этом случае определяется выражением а регулировочная характеристика имеет вид и приведена на фиг, 2 (кривая 2).Согласно заявляемому способу устройство управления работает следующим образом.Для начала процесса управления в соответствии с алгоритмом (фиг. 8) в память задатчика сигналов управления 1, а затем в программируемый таймер 2 производится запись управляющих слов (УС) и числа й. При изменении знака напряжения на выходе трансформатора 13 с отрицательного на положительный и с положительного на отрицательный (фиг. 7, а) сигнал Ои на выходе компаратора 14 изменяется от значения логического нуля до значения логической единицы и от значения логической единицы до значения логического нуля соответственно (фиг. 7,б). Сигнал, инверсНый сигналу 014, Формируется на выходе инвертора 15 (Фиг. 7,в). Поскольку в исходном состоянии О-триггера 16 сигнал 01 э на его инверсном выходе соответствует уровню логической единицы (фиг, 7,г), то его произведение с сигналом 014, соответствующим положительной полуволне напряжения 01 з, также будет соответствовать уровню логической единицы (фиг, 7,к)01 т 014 Л 01 з. Сигнал 017 с выхода логического элемента И 17 через логический элемент ИЛИ 22 поступает на вход ОАТЕ таймера 2 (фиг. 7,м), По фронту сигнала 022 в таймере 2 начинается отсчет ранее записанного числа й. Отсчет числа й производится путем его уменьшения на единицу с приходом каждого импульса от функционального преобразователя 4. Частота следования тактовых импульсов на выходе преобразователя 4 изменяется пропорционально модулю напряжения питающей сети 4 = К 10К 12 Овз 1 п Йс 1 3,где Ка и К 12 - коэффициент трансформации трансформатора 10 и коэффициент пропорциональности преобразователя 12, выбираемые таким образом, чтобы выполнялось условие КюК 12= И,/ЛОж По истечении времени т - агссоз 1 - (й - 1) 3, с 35т,е. за один такт до окончания счета сигнал на выходе ООТ таймера 2 в течение одного периода Т 4 устанавливается соответствующим уровню логического нуля (фиг. 7,н). По 40 фронтам импульсов 02 формирователь 5 импульсов формирует импульсы управления длительностью, необходимой для надежного отпирания тиристоров (фиг. 7,о). В распределителе 6 импульсов в соответствии с 45 сигналом 014 происходит распределениеимпульсов управления 05 по выходным усилителям 7 и 8, где происходит усиление управляющих импльсов (фиг. 7,п,р).Кроме того, импульсы управления 05 че рез логический элемент ИЛИ 18 поступаютна С-вход Р-триггера 16, что при совпадении сигналов на его обоих входах приводит к изменению состояния 0-триггера 16 и наего инверсном выходе устанавливается на пряжение, соответствующее уровню логического нуля (фиг, 7,г). В результате изменения состояния Р-триггера 16 на входе ОАТЕ таймера 2 устанавливается сигнал, соответствующий уровню логического нуля, чтоявляется запрещением для работы таймерав атеем такте тиристорного преобразователя9 (фг. 7,м). По окончании действия сигнала014, соответствующего логической единице,на )-входе О-триггера 16 последний переходит в свое исходное состояние (фиг. 7,г,д).Второй канал блока 3 связи с сетью, включающий О-триггер 19 и логические элементы И 20 и ИЛИ 21, работает аналогичнымобразом, но со сдвигом на 180 эл, град, (фиг.7,ж,з,и,л).Таким образом изменение частоты навыходе функционального преобразователя4 по закону, определяемому выражением(1), Обеспечивает линейную регулировочнуюхарактеристику тиристорного преобразователя 9 (фиг. 1, кривая 2). Для получения возрастающей регулировочной характеристикичисло й, согласно способу, по записи в таймер преобразуют в соответствии с выражениЕм (7). Блок-схема алгоритма дляреализации такой зависимости приведенана фиг. 9, Принцип работы аппаратной части системы управления при этом не изменяется,Использование предлагаемого способапрямого микропроцессорного управления иустройства для его реализации позволяет. получать линейные регулировочные характеристики тиристорного преобразователя,что облегчает использование последнего всистемах авторегулирования, поскольку позволяет оставить без изменения коэффициент усиления отрицательной обратнойсвязи во всем диапазоне изменения углауправления тиристорами,Формула изобретения1, Способ прямого микропроцессорного управления тиристорным преобразователем, включающий запись в таймер числа,отсчет этого числа путем уменьшения его наединицу с приходом каждого тактового импульса, начиная с момента перехода напряжения питающей сети через нуль, иформирование по окончании отсчета числауправляющих импульсов тиристорами, о тл ич а ю щи й с я тем, что, с целью улучшениярегулировочной характеристики тиристорного преобразователя путем ее линеариза"ции, частоту следования тактовыхимпульсов формируют пропорциональномодулю напряжения питающей сети.2, Способ поп. 1, отл ич а ю щи й сятем, что, с целью получения возрастающейрегулировочной характеристики тиристорного преобразователя, число до записи втаймер преобразуют в соответствии с выражениемЦМ) = Ймакс Й5 10 15 20 25 30 3540 4550 где Ймакс - максимальное значение числа, которое может быть записано в таймер.Э, Устройство для прямого микропроцессорного управления тиристорным преобразователем, содержащее эадэтчик сигналов управления, выходами подключенный к соответствующим входам таймера, выход таймера через формирователь импульсов подключен к входу импульсов управления распределителя импульсов, выходы первого и второго каналов управления которого подключены к соответствующим управляющим входам тиристорного преобразователя, блок связи с сетью, вход окончания счета таймера которого подключен к выходу формирователя импульсов, а вход синхронизации с сетью, определяющий начало отсчета и выбор канала управления, соединен с выводами для подключения питающей сети, выход разрешения счета блока связи с сетью соединен с управляющим входом таймера, а выход выбора канала управления - с входом выбора канала управления распределителя импульсов, о т л и ч а ю щ е е с я тем, что, с целью улучшения качества регулирования, введен функциональный преобразователь модуля напряжения в частоту импульсов, включенный между выводами для подключения питающей сети и синхровходом таймера.4, Устройство по и. 3, о тл и ч а ю щ е ес я тем, что блок связи с сетью выполнен в виде трансформатора, вход которого является входом синхронизации с сетью блока связи с сетью, а выход подключен к входам компаратора, выход которого является выходом выбора канала управления блока связи с сетью, а также подключен к первым входам первого О-триггера и первого логического элемента И, и через логический инвертор - к первым входам второго О-триггера и второго логического элемента И, прямые выходы первого и второго О-триггеров подключены соответственно к первым входам первого и второг- логических эламентов ИЛИ, вторые входы которых объединены в общую точку и являются входомокончания счета блока связи с сетью, выходы первого и второго логических элементовИЛИ подключены соответственно к вторым входам первого и второго О-триггеров, инверсные выходы которых подключены соот. ветственно к вторым входам первого и 55 второго логических элементов И, выходы логических элементов И подключены к входамтретьего логического элемента ИЛИ, выход которого является выходом разрешения счета блока связи с сетью,(Р Р 8 дб О 5.Устройство по п.З, отл и ч а ю ще ес я тем, что распределитель импульсов выполнен в виде логических элементов И и ЗАПРЕТ, причем первый вход логического элемента И и прямой вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом импульса управления распределителя импульсов, второй вход логического элемента И и инверсный вход логического элемента ЗАПРЕТ объединены в общую точку и являются входом выбора канала управления распределителя импульсов, вы . ходы логических элементов ЗАПРЕТ и И являются выходами первого и второго каналов управления распределителя импульсов.18388 б 8 Составитель Д.Кипенский ехред М.Моргентал КорректорМ.Самборска да зводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 1 каэ 2928 Тираж ВНИИПИ Государственного коми 1 ета 113035, Москве, Ж

СмотретьЗаявка

4942852, 10.06.1991

ХАРЬКОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

КИПЕНСКИЙ АНДРЕЙ ВЛАДИМИРОВИЧ, ДОЛБНЯ ВИКТОР ТИМОФЕЕВИЧ, СОКОЛ ЕВГЕНИЙ ИВАНОВИЧ, САВЧЕНКО ИГОРЬ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H02M 7/12

Метки: микропроцессорного, преобразователем, прямого, тиристорным

Опубликовано: 30.08.1993

Код ссылки

<a href="https://patents.su/9-1838868-sposob-pryamogo-mikroprocessornogo-upravleniya-tiristornym-preobrazovatelem-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ прямого микропроцессорного управления тиристорным преобразователем и устройство для его осуществления</a>

Предыдущий патент: Способ формирования эталонного сигнала для управления компенсатором мощности искажения

Следующий патент: Автономный инвертор тока

Случайный патент: Гидравлический пресс для получения изделий из металлического порошка