Устройство для идентификации аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

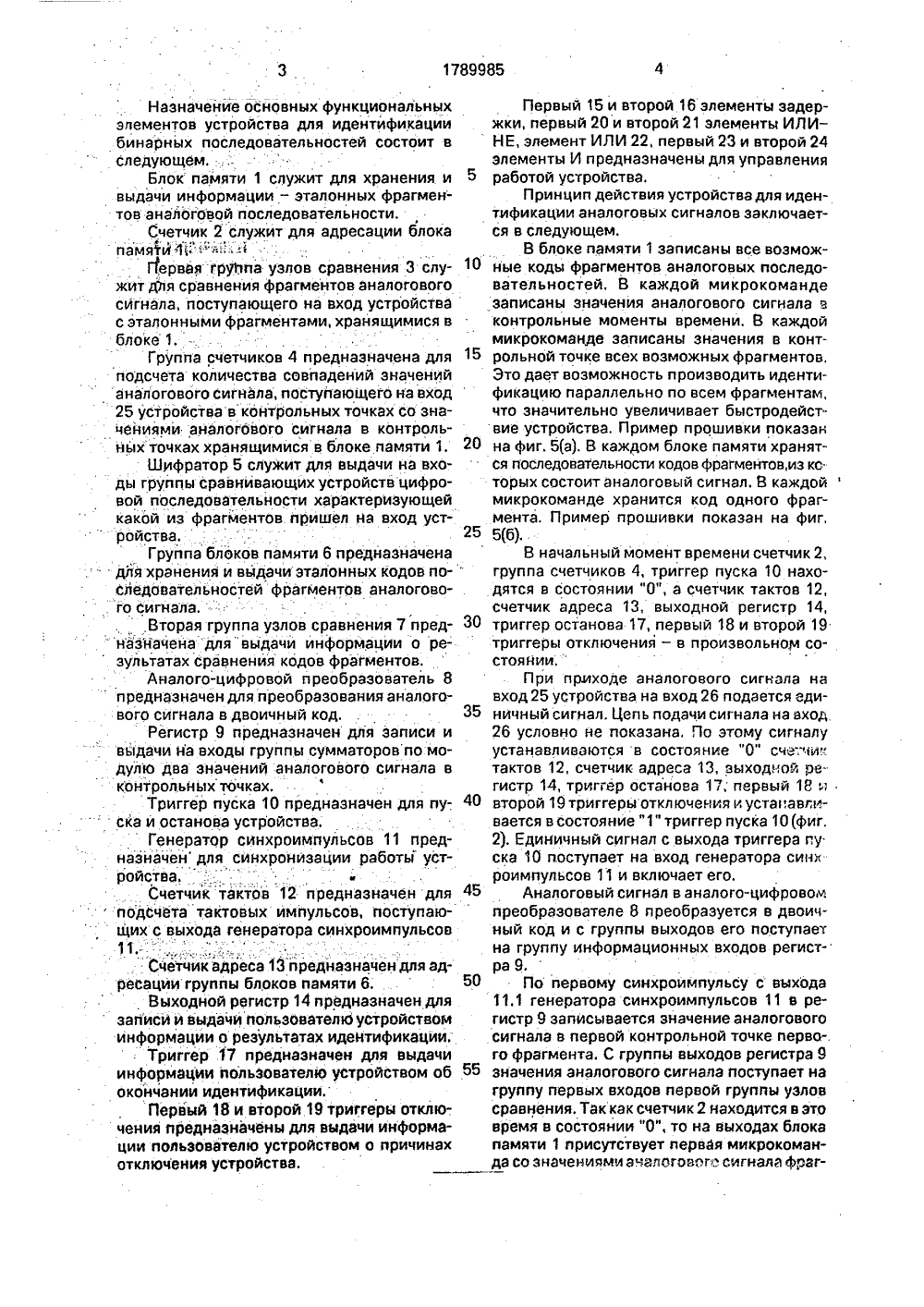

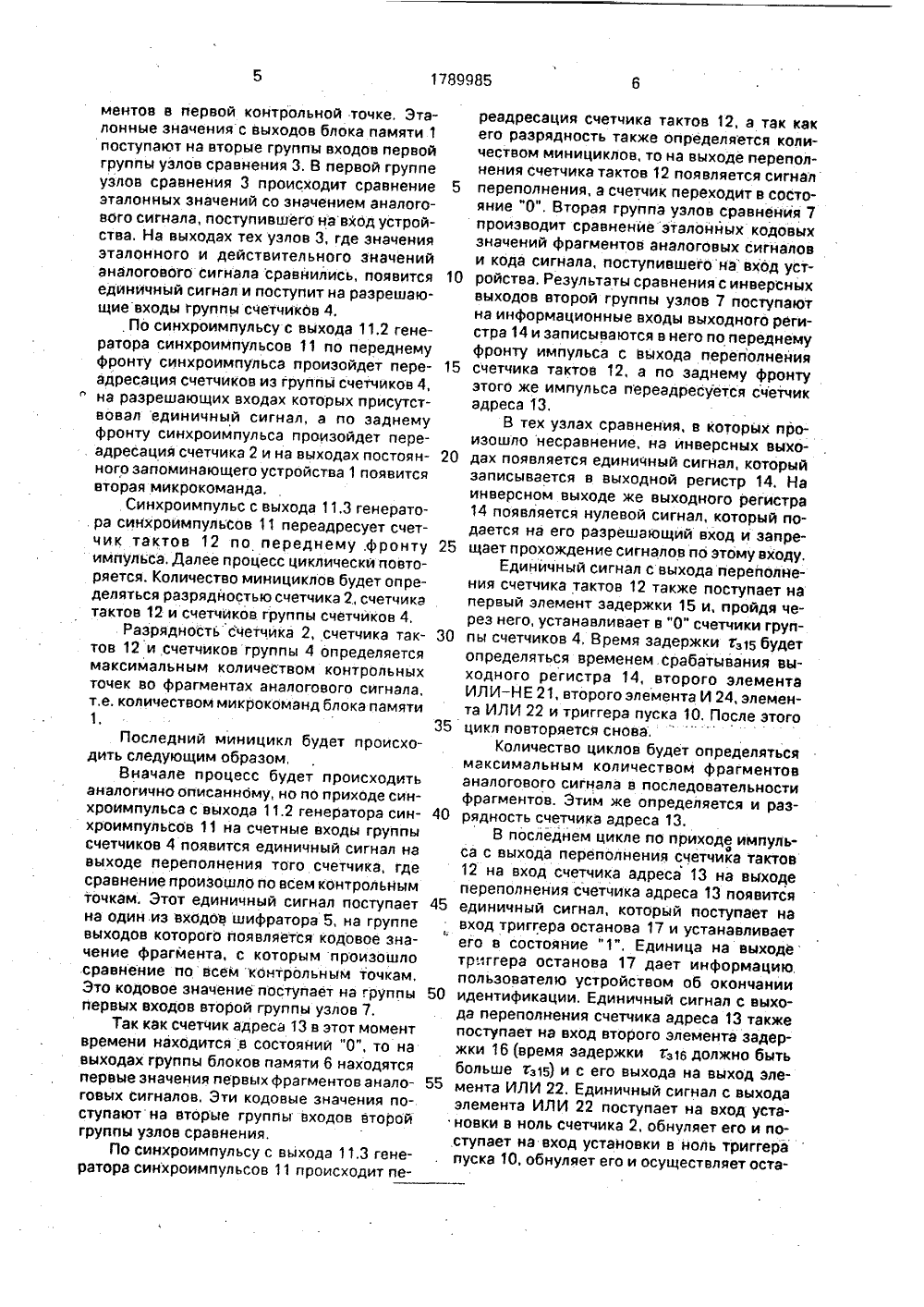

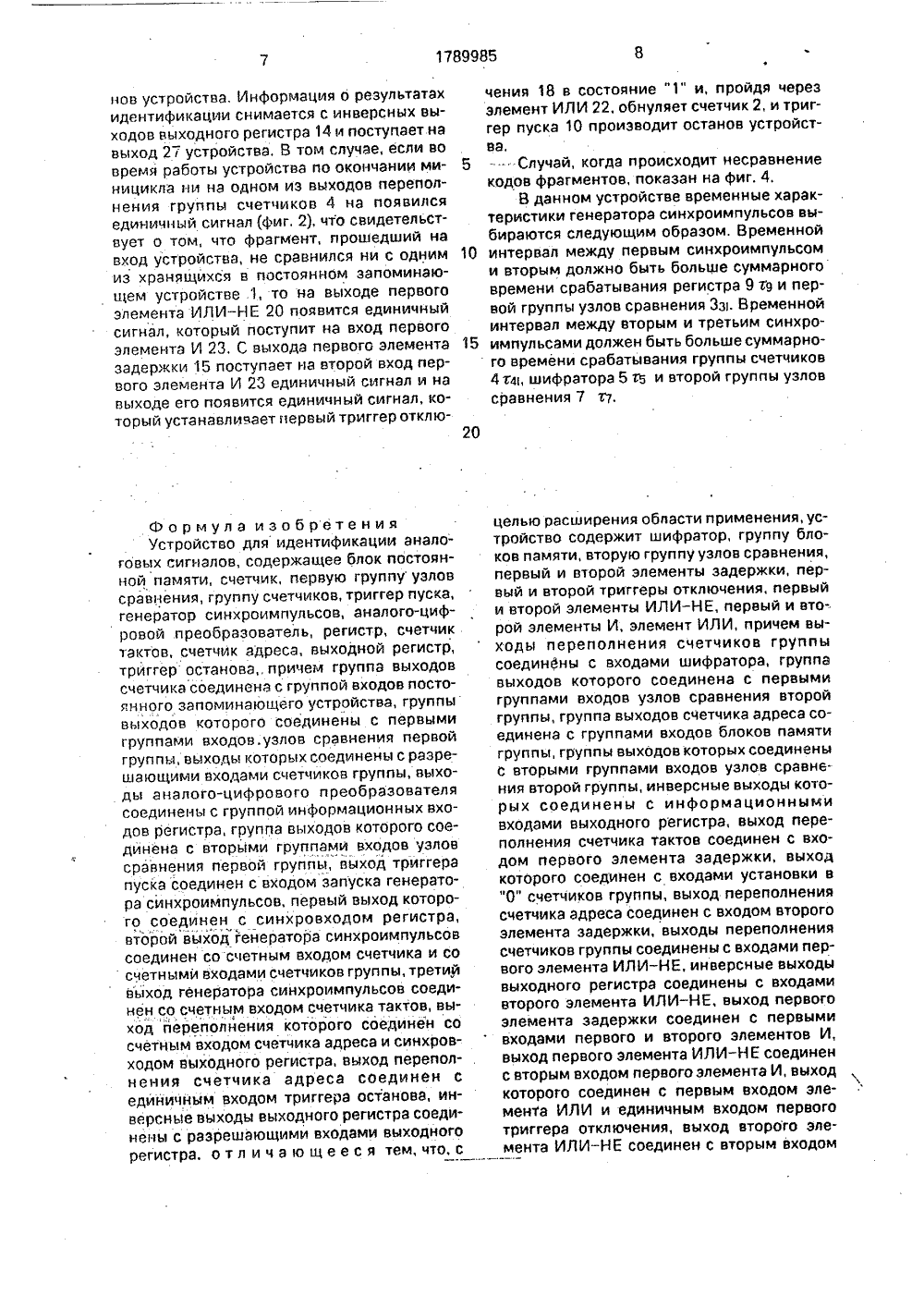

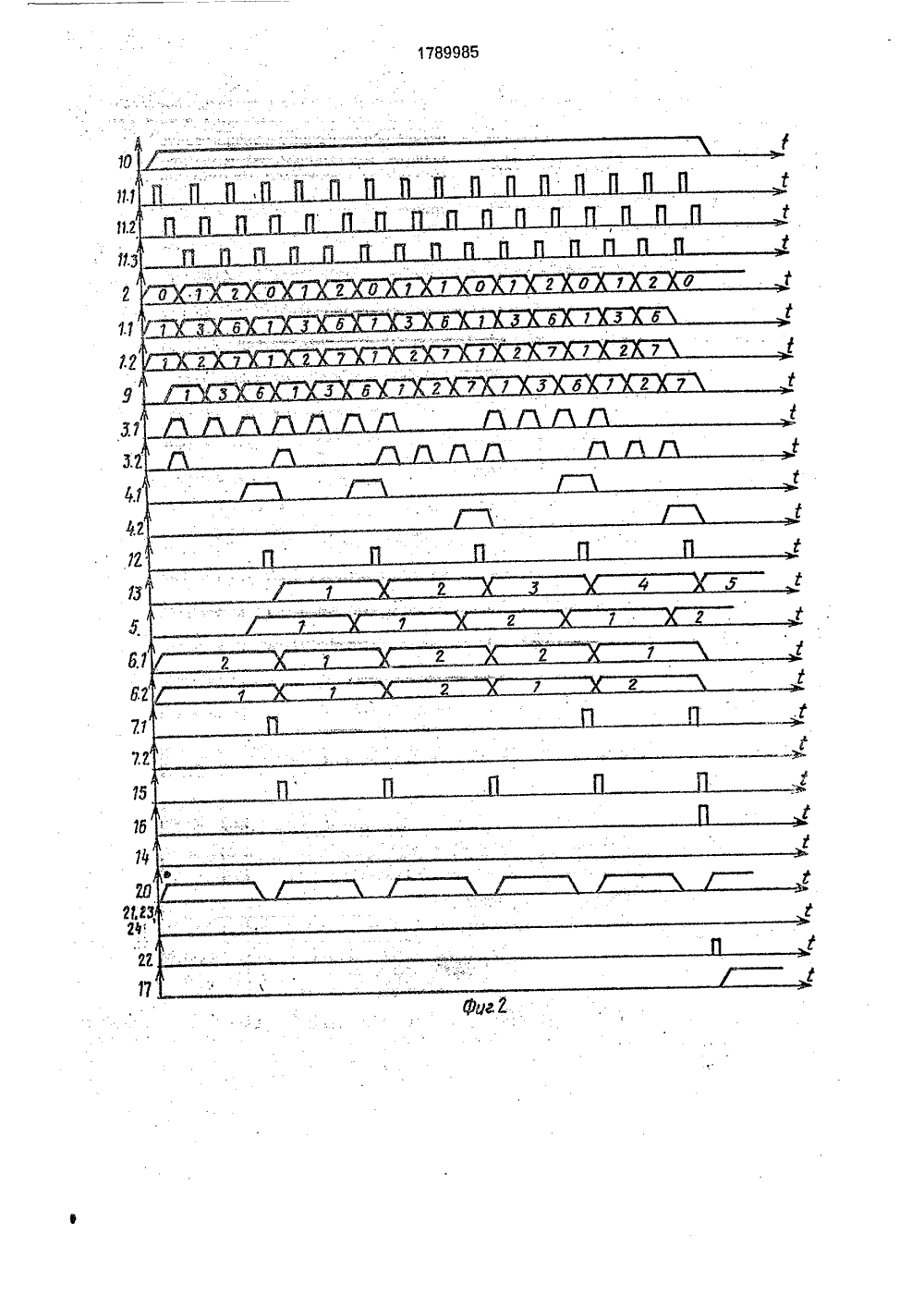

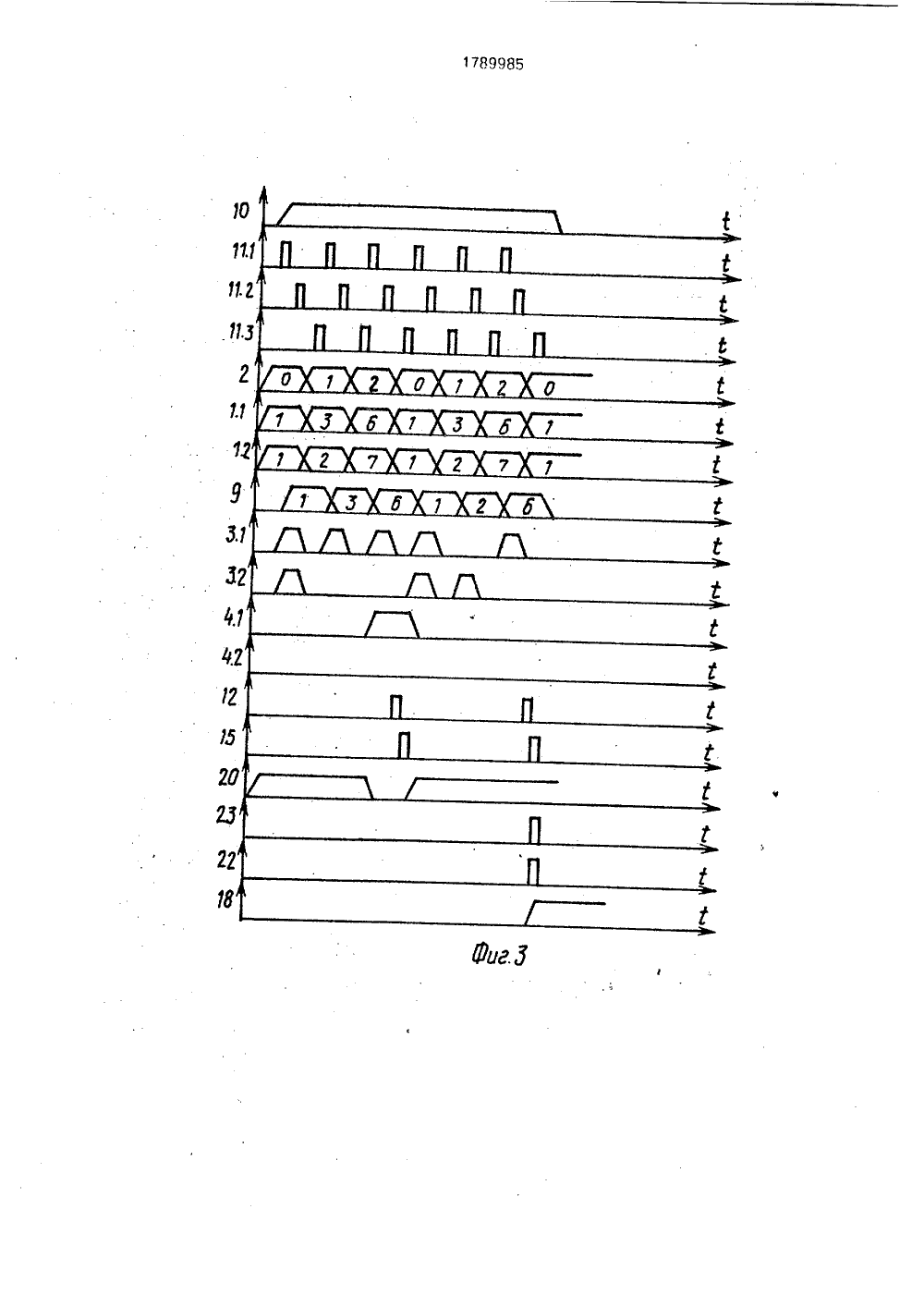

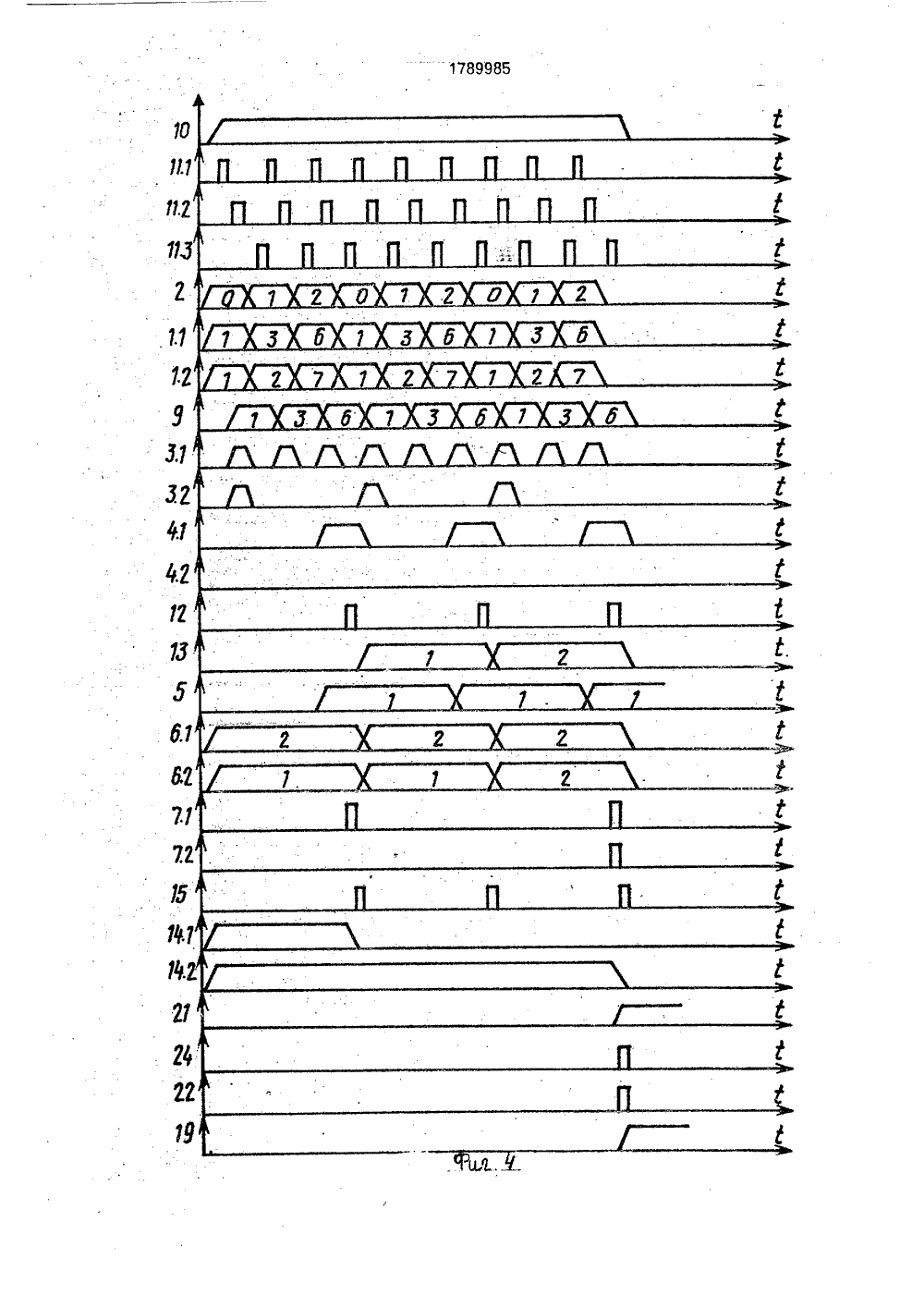

. Чернышов,монькин, С,П к, Ш Целью иэобретениние области примененlНа фиг, 1 предстаная схема устройствааналоговых сигналов;менные диаграммы фуройства; на фиг. 5, 6 - иблоков памяти предлапрототипа,я является расшия устройства,алена функциодля идентификна фиг. 2,3,4 -нкционированиримеры кодироваемого устройс ьврея уст- ания аи ВТОРСКОМУ СВИДЕТЕЛЬС(71) Конструкторское бюро электроп рибо ростроения(56) Авторское свидетельство СССР М 1376088, кл. 6 06 Е 11/16, 1986,Авторское свидетельство СССР М 1730611, кл, 6 06 Р 11/16, 1989.(54) УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ АНАЛОГОВЫХ СИГНАЛОВ(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в средствах идентификации аналоговых сигналов, поступающих на вход устройства от различных обьектов управлеИзобретение относится к автоматике и вычислительной технике и может быть использовано в средствах идентификации аналоговых сигналов, поступающих йа вход устройства от различных объектов управления, а также в средствах контроля, диагностирования и отладки систем. ния, а также в средствах контроля, диагностирования и отладки систем. Цель изобретения - расширение области применения устройства, Поставленная цель достигается путем дополнительного введения визвестное устройство для идентифйкации аналоговых сигналов шифратора, группы блоков памяти, второй группы узлов сравнения, первого и второго элементов задержки, пер-" вого и второго триггеров отключенйя, первого и второго элементов ИЛИ - НЕ, первого и второго элементов И, элемента ИЛИ, а также соответствующих связей между ними. Положительный эффект от использования заявляемого решения заключается в значительном выигрыше в объеме памяти, Кроме того, заявляемое устройство существенно З расширяет область применения прототипа на класс систем,-использующих более сложные сигналы. б ил. Устройств для идентификации анало 3 говых сигналов содержит блок памяти 1, счетчик 2, первую группу узлов сравнения 3, 0 группу счетчиков 4, шифратор 5, группу памя- О ти б, вторую группу узлов сравнения уст ройств 7, аналого-цифровой преобразователь . (Я 8, регистр 9, триггер пуска 10, генератор синхроимпульсов 11, счетчик тактов 12, счетчик адреса 13, выходной регистр 14, первый 15 и второй 16 элементы задержки, триггер оста- нова 17, первый 18 и второй 19 триггеры отключения; первый 20 и второй 21 элементы ИЛИ - НЕ, элемент ИЛИ 22, первый 23 и второй 24 элементы И, информационный вход 25, вход пуска 26, выход результата идентификации 27, выход останова 28, первый 29 и второй 30 выходы отключения.Назначение основных функциональныхэлементов устройства для идентификациибинарных последовательностей состоит вследующем.Блок памяти 1 служит для хранения. ивыдачи информации - эталонных фрагментов аналоговой последовательности.Счетчик 2 служйт для адресации блокапамяти 11 "д- -Г 1 ерввягруппа узлов сравнения 3 служит для сравнения фрагментов аналоговогосйгнала, поступающего на вход устройствас эталонными фрагментами, хранящимися вблоке 1.Группа счетчиков 4 предназначена дляподсчета количества совпадений значейийаналогового сигнала, пбстуйающего на вход25 устройства в контрольных точках со значениями аналогового сигнала в контрольныхточках хранящимисяв блоке памяти 1.Шифратор 5 служит для выдачи на входы группы сравнивающих устройств цифровой последовательности характеризующейкакой из фрагментов пришел на вход устройства,Группа блоков памяти 6 предназначенадля хранения и выдачи эталонных кодов последовательностей фрагментов аналогового сигнала,Вторая группа узлов сравнения 7 предназначена для выдачй информации о результатах сравнения кодов фрагментов.Аналого-цифровой преобразователь 8предназначен для преобразования аналогового сигнала в двоичный код.Регистр 9 предназначен для записи ивыдачи на входы группы сумматоров по модулю два значений аналогового сигнала вконтрольных точках,Триггер пуска 10 предназначен для пуска и останова устройства,Генератор синхроимпульсов 11 предназначен для синхронизации работы устройства,Счетчиктактов 12 предназначен для: подсчета тактовых импульсов, поступающих с выхода генератора синхроимпульсов11.Счетчик адреса 13 предйазначен для адресации группы блоков памяти 6,Выходной регистр 14 предназначен длязайисй и выдачи пользователю устройствоминформации о результатах идентификации.Триггер 17 предназначен для выдачиинформации пользователю устройством обокончании идентификации,Первый 18 и второй 19 триггеры отключения предназначены для выдачи информации пользователю устройством о причинахотключения устройства.5 10 Первый 15 и второй 16 элементы задержки, первый 20 и второй 21 элементы ИЛИ - НЕ, элемент ИЛИ 22, первый 23 и второй 24 элементы И предназначены для управления работой устройства.Принцип действия устройства для идентификации аналоговых сигналов заключается в следующем.В блоке памяти 1 записаны все возможные коды фрагментов аналоговых последовательностей, В каждой микрокомандезаписаны значения аналогового сигнала вконтрольные моменты времени. В каждоймикрокоманде записаны значения в конт 15 рольной точке всех возможных фрагментов,Это дает возможность производить идентификацию параллельно по всем фрагментам,что значительно увеличивает быстродействие устройства. Пример прошивки показан20 на фиг, 5 а), В каждом блоке памяти хранятся последовательности кодов фрагментов,из кс.торых состоитаналоговый сигнал. В каждоймикрокоманде хранится код одного фрагмента. Пример прошивки показан на фиг,25 5(б),В начальный момент времени счетчик 2,группа счетчиков 4, триггер пуска 10 находятся в состоянии "0", а счетчик тактов 12,счетчик адреса 13, выходной регистр 14,30 триггер останова 17, первый 18 и второй 19триггеры отключения - в произвольном состоянии,При приходе аналогового сигнала навход 25 устройства на вход 26 подается еди 35 ничный сигнал. Цепь подачи сигнала на вход26 условно не показана, По этому сигналуустанавливаются в состояние "О" счетчиктактов 12, счетчик адреса 13, выходной регистр 14, триггер останова 17; первый 18 и40 второй 19 триггеры отключения и устанавливается в состояние "1" триггер пуска 10 (фиг.2), Единичный сигнал с выхода триггера пу.ска 10 поступает на вход генератора синхроимпульсов 11 и включает его.45 Аналоговый сигнал в аналого-цифровомпреобразователе 8 преобразуется в двоичный код и с группы выходов его поступаетна группу информационных входов регистра 9,50 По первому синхроймпульсу с выхода11.1 генератора синхроимпульсов 11 в регистр 9 записывается значение аналоговогосигнала в первой контрольной точке перво-.го фрагмента. С группы выходов регистра 955 значения аналогового сигнала поступает нагруппу первых входов первой группы узловсравнения. Так как счетчик 2 находится в атовремя в состоянии "0", то на выходах блокапамяти 1 присутствует первая микрокоманде со значениями аналогового сигнала фрагментов в первой контрольной точке, Эталонные значения с выходов блока памяти 1поступают на вторые группы входов первойгруппы узлов сравнения 3, В первой группеузлов сравнения 3 происходит сравнениеэталонных значений со значением аналогового сигнала, поступившего на вхбд устройства. На выходах тех узлов 3, где значенияэталонного и действительного значенийаналогового сигнала сравнились, появитсяединичный сигнал и поступит на разрешающиевходы группы счетчиков 4.По синхроимпульсу с выхода 11,2 генератора синхроимпульсов 11 по переднемуфронту синхроимпульса произойдет переадресация счетчиков из группы счетчиков 4," на разрешающих входах которых присутствовал единичный сигнал, а по заднемуфронту синхроимпульсэ произойдет переадресация счетчика 2 и на выходах постоянного запоминающего устройства 1 появитсявторая микрокомэндэ,Синхроимпульс с выхода 11.3 генерато. ра синхроимпульсов 11 переадресует счетчик тактов 12 по переднему, фронтуимпульса. Далее процесс циклическй повторяется. Количество минициклов будет оп ределяться разрядностью счетчика 2, счетчикатактов 12 и счетчиков группы счетчиков 4,РазрядноСть счетчика 2, счетчика тактов 12 и счетчиков группы 4 определяетсямаксимальным количеством контрольныхточек во фрагментах аналогового сигнала,т,е. количеством микрокомэнд блока памяти1,Последний миницикл будет происходить следующим образом,Вначале процесс будет происходитьаналогично описаннбму, но по приходе синхроимпульса с выхода 11,2 генератора синхроимпульсов 11 на счетные входы группы счетчиков 4 появится единичный сигнал на выходе переполнения того счетчика, где сравнение произошло по всем контрольнцм точкам, Этот единичный сигнал поступает на один из входов шифратора 5, на группе выходов которого появляется кодовое значение фрагмента, с которым произошло сравнение по всем контрольным точкам, Это кодовое значение поступает на группы первых входов второй группы узлов 7.Так кэк счетчик адреса 13 в этот момент времени находится в состоянии "0", то на выходах группы блоков памяти 6 находятся первые значения первых фрагментов аналоговых сигналов, Эти кодовые значения поступают нэ вторые группы входов второй группы узлов сравнения,По синхроимпульсу с выхода 11.3 генератора синхроимпульсов 11 происходит переадресация счетчика тактов 12, а тэк какего разрядность также определяется количеством минициклов, то на выходе переполнения счетчика тактов 12 появляется сигнал5 переполнения, а счетчик переходит в состояние "0". Вторая группа узлов сравнения 7производит сравнение эталонных кодовыхзначений фрагментов аналоговых сигналови кода сигнала, поступившегона вход уст 10 ройства. Результаты сравнения с инверсныхвыходов второй группы узлов 7 поступаютна информационные входы выходного регистра 14 и записываются в него по переднемуфронту импульса с выхода переполнения15 счетчика тактов 12, а по заднему фронтуэтого же импульса переадресуется счетчикадреса 13.В тех узлах сравнения, в которых произошло несравнение, на инверсных выхо 20 дах появляется единичный сигнал, которыйзаписывается в выходной регистр 14. Наинверсном выходе же выходного регистра14 появляется нулевой сигнал, который подается на его разрешающий вход и запре 25 щает прохождение сигналов по этому входу,Единичный сигнал с выходапереполнения счетчика тактов 12 также поступает напервый элемент задержки 15 и, пройдя через него, устанавливает в "0" счетчики груп 30 пц счетчиков 4, Время задержки т,15 будетопределяться временем срабатывания выходного регистра 14, второго элементаИЛИ-НЕ 21, второго элемента И 24, элемента ИЛИ 22 и триггера пуска 10, После этого35 цикл повторяется снова,Количество циклов будет определятьсямаксимальным количеством фрагментованалогового сигнала в последовательностифрагментов. Этим же определяется и раз 40 рядность счетчика адреса 13.В последнем цикле по приходе импульса с выхода переполнения счетчика тактов12 нв вход счетчика адреса 13 на выходепереполнения счетчика адреса 13 появится45 единичный сигнал, который поступает навход триггера останова 17 и устанавливаетего в состояние "1", Единица на выходетриггера останова 17 дает информациюпользователю устройством об окончании50 идентификации. Единичный сигнал с выхода переполнения счетчика адреса 13 такжепоступает на вход второго элемента задержки 16 (время задержки тз 16 должно бытьбольше т 15) и с его выхода на выход эле 55 мента ИЛИ 22. Единичный сигнал с выходаэлемента ИЛИ 22 поступает на вход установки в ноль счетчика 2, обнуляет его и поступает на вход установки в ноль триггерапуска 10, обнуляет его и осуществляет оста1189985 5 10 20 нов устройства, Информация о результатах идентификации снимается с инверсных выходов выходного регистра 14 и поступает на выход 27 устройства, В том случае, если во время работц устройства по окончании миницикла ни нэ одном из выходов переполнения группы счетчиков 4 на появился единичный сигнал (фиг, 2), что свидетельствует о том, что фрагмент, прошедший на вход устройства, не сравнился ни с одним из хранящихся в постоянном запоминающем устройстве 1, то на выходе первого элемента ИЛИ - НЕ 20 появится единичный сигнал, который поступит на вход первого элемента И 23, С выхода первого элемента задержки 15 поступает на второй вход первого элемента И 23 единичный сигнал и на выходе его появится единичный сигнал, который устанавливает первый триггер отклюФормула изобретения Устройство для идентификации аналоговых сигналов, содержащее блок постоянной памяти, счетчик, первую группу узлов сравнения, группу счетчиков, триггер пуска, генератор синхроимпульсов, аналого-цифровой преобразователь, регистр, счетчик тактов, счетчик адреса, выходной регистр, триггер останова причем группа выходов счетчика соединена с группой входов постоянного запоминающего устройства, группы выходов которого соединенц с первыми группами входов, узлов сравнения первой группы, выходы которых соединены с разрешающими входами счетчиков группы, выходы аналого-цифрового преобразователя соединены с группой информационных входов регистра, группа выходов которого соединена с вторымй группами входов узлов сравнения первой группы, выход триггера пуска соединен с входом запуска генератора синхроимпульсов, первый выход которого соединен с синхровходом регистра,второй выход генератора синхроимпульсов соединен со счетным входом счетчика и со счетными входами счетчиков группы, третии выход генератора синхроимпульсов соединен со счетным входом счетчика тактов, вцход переполнения которого соединен со счетным входом счетчика адреса и синхровходом выходного регистра, вцход переполнения счетчика адреса соединен с единичнцм входом триггера останова, инверсные выходы выходного регистра соединенц с разрешающими входами выходного регистра. о т л и ч а ю щ е е с я тем, что, с чения 18 в состояние "1" и, пройдя через элемент ИЛИ 22, обнуляет счетчик 2, и триггер пуска 10 производит останов устройства,- Случай, когда происходит несравнение кодов фрагментов, показан на фиг, 4.В данном устройстве временные характеристики генератора синхроимпульсов выбираются следующим образом. Временной интервал между первым синхроимпульсом и вторым должно быть больше суммарного времени срабатывания регистра 9 щ и первой группы узлов сравнения Ззь Временной интервал между вторым и третьим синхроимпульсами должен быть больше суммарного времени срабатывания группы счетчиков4 т 4 ь шифратора 5 хь и второй группы узловсравнения 7 ту,целью расширения области применения, устройство содержит шифратор, группу блоков памяти, вторую группу узлов сравнения, первый и второй элементы задержки, первый и второй триггеры отключения, первый и второй элементы ИЛИ - НЕ, первый и второй элементы И, элемент ИЛИ, причем выходы переполнения счетчиков группы соединены с входами шифратора, группа выходов которого соединена с первыми группами входов узлов сравнения второй группы, группа выходов счетчика адреса соединена с группами входов блоков памяти группы, группы выходов которых соединены С вторыми группами входов узлов сравнения второй группы, инверсные выходы которых соединены с информационными входами выходного регистра, выход переполнения счетчика тактов соединен с входом первого элемента задержки, выход котОрого соединен с входами установки в "0" счетчиков группы, выход переполнения счетчика адреса соединен с входом второго элемента задержки, выходы переполнения счетчиков группы соединены с входами первого элемента ИЛИ - НЕ, инверсные выходы выходного регистра соединены с входами второго элемента ИЛИ - НЕ, выход первого элемента задержки соединен с первыми входами первого и второго элементов И, выход первого элемента ИЛИ-НЕ соединен с вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ и единичным входом первого триггера отключения, выход второго элемента ИЛИ-НЕ соединен с вторым входомвторого элемента И, выход которого соединен с вторым входом элемента ИЛИ и с единичным входом второго триггера отключения, выход второго элемента задержки соединен с третьим входом элемента ИЛИ, выход которого соединен с входами установки в "О" счетчика и триггера пуска, группа входов аналого-цифрового преобразователя является группой информационных входов устройства, единичный вход триггера пуска и входы установки в "О" счетчика тактов, счетчика адреса, выходного регистра, первого и второго триггеров отключения и триггера останова подключены к входам за.уска устройства, группа инверсных выходов выходного регистра является группой выходов результата идентификации устройства, выход триггера останова является выходом признака окончания иде, тификации устройства; выходы первого и в.рого триггеров отключения являются соответственно первыми вторыМ выходами отключения устройства.1789985 прес от т От а Опт тап тоа тоа ооо оат Оао оот о аа о От 1 от т ОО т ОО т оо а ото оот та т т от О та 111 П то 11 О О 11 О от Оат О 1 Р оо т тот ато ттт ото таа т ОО о от О 11 т тп о О ОО Опт т от П та т то О 11 от т пот Опт а то т та О 10 а та Опт атт 1 11 топ таа аОа О 01 тот т оттт т тапа ттоот т тото ттатт т таоо тттат опт опп Пот тп п оп т Пта От а тпо т по тпа Оо то ото Королтт ор Заказ 350 . Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открыти113035, Москва, Ж, Раущская наб., 4/5 ГКНТ СССР ул. Гагарина, 101 ород О ОООО о аоот ооото О Оотт Оот оо о о 1 О 1 о отто оог 11 о тапа о тоат о тото О тптт о 1 таа о ттат 0 1110 отттт 1 о Пап тооат т пото 1 о от т 1 о топ татот Рил. бСоставитель И.Сафроновадактор Л,Пигина Техред М. Моргентал оизводственно-издательский комбинат "Патент", г. У Пт 1 ото оот тоо тпо тпо и оп ппт тот П От птт 1 тт ппт птп ттп

СмотретьЗаявка

4913949, 25.02.1991

КОНСТРУКТОРСКОЕ БЮРО ЭЛЕКТРОПРИБОРОСТРОЕНИЯ

ЛУЧЕНКО ОЛЕГ АЛЕКСАНДРОВИЧ, ЧЕРНЫШОВ МИХАИЛ АНАТОЛЬЕВИЧ, БЕК АЛЕКСАНДР ВЛАДИМИРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, КАРЛАШ СЕРГЕЙ ПЕТРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/16

Метки: аналоговых, идентификации, сигналов

Опубликовано: 23.01.1993

Код ссылки

<a href="https://patents.su/9-1789985-ustrojjstvo-dlya-identifikacii-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для идентификации аналоговых сигналов</a>

Предыдущий патент: Устройство приоритета

Следующий патент: Устройство для сопряжения разноскоростных вычислительных устройств

Случайный патент: Алмазно-расточной станок