Устройство для измерения средних значений нестационарных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

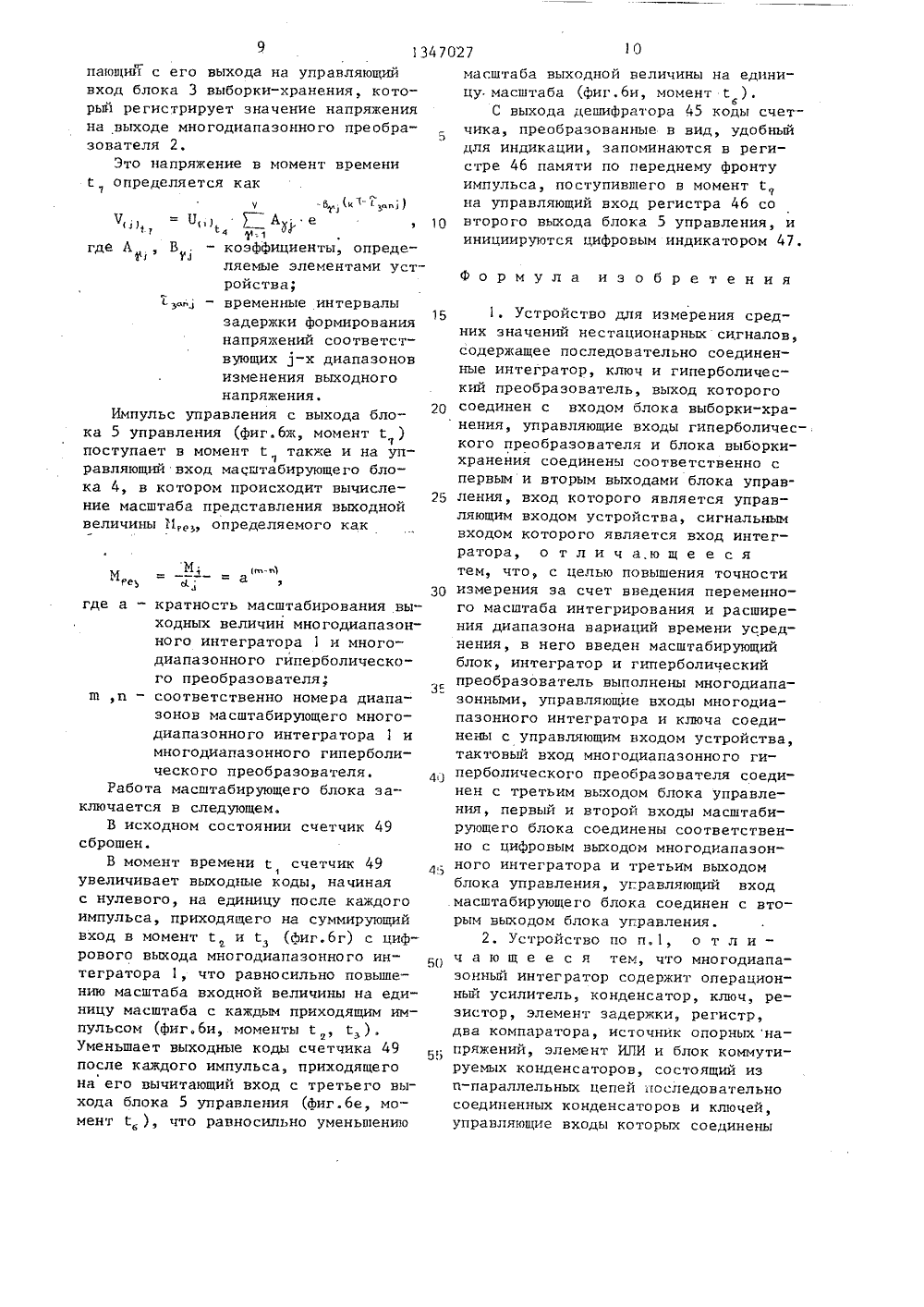

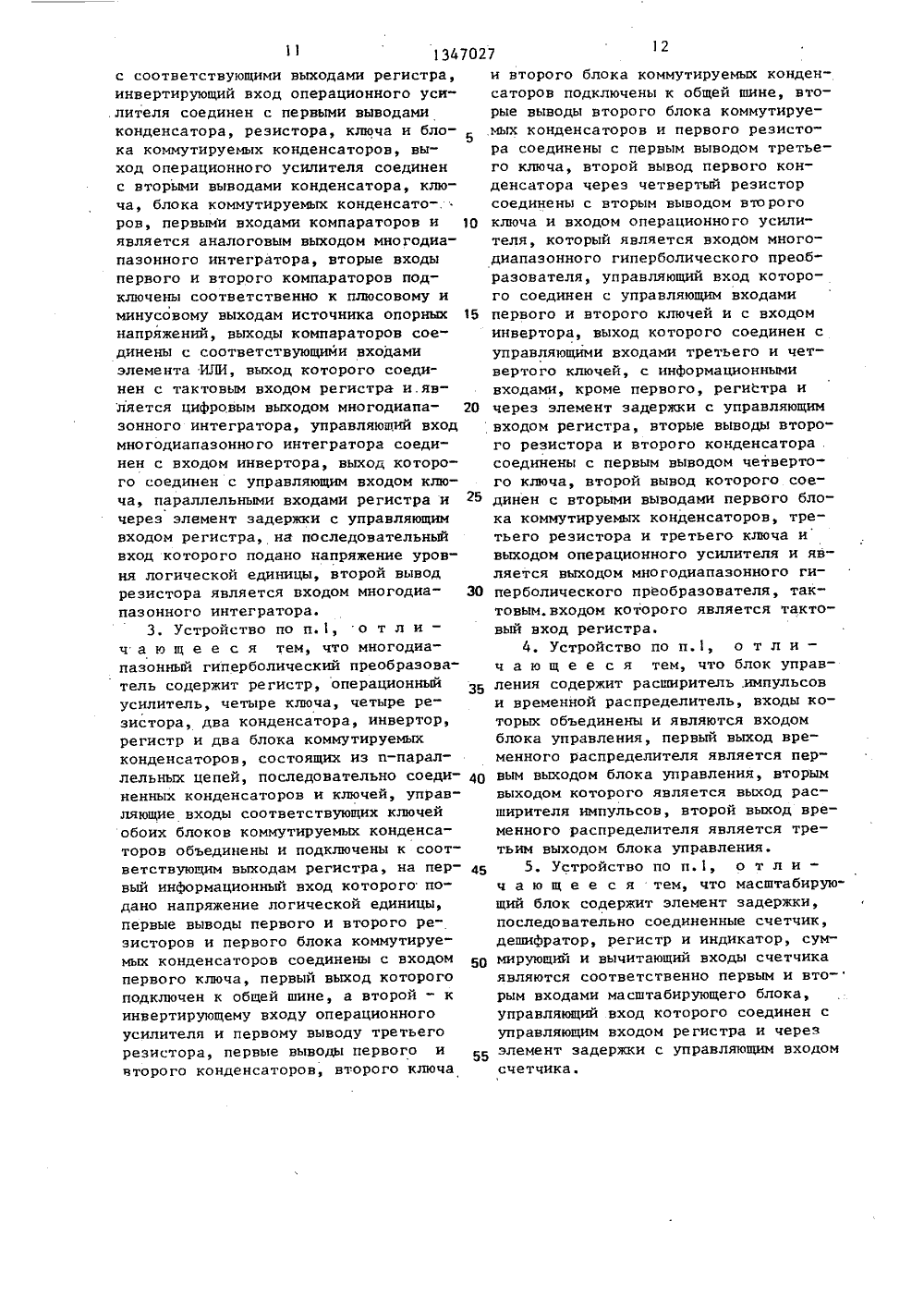

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК д 1 4 С 01 К 19 ОМИТЕТ СССРИЙ И ОТКРЫТИИ ОСУДАРСТВЕННЫЙПО ДЕЛАМ ИЗОБРЕТ(71) Куйбышевский авиационный институт им. акад. С,П.Королева(56) Справочник по нелинейным схемам.(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНИХЗНАЧЕНИЙ НЕСТАЦИОНАРНЫХ СИГНАЛОВ(57) Изобретение может быть использовано в установках технической диагностикипо спектральному составу шумов и вибраций, режимов работы различных промышленных объектов, а также в медицине при измерении среднегодавления крови в течение каждого сер,801347027 дечного цикла, среднего выдыхаемого объема двуокиси углерода в каждом дыхательном цикле. Цель изобретения -повышение точности измерения за счет введения переменного масштаба интегрирования и расширения диапазона вариаций времени усреднения. Для этого в устройство, содержащее интегратор 1, гиперболический преобразователь 2,блок 3 выборки-хранения, блок 5 управления, ключ 6, управляющий 7 исигнальный 8 входы, введен масштабирующий блок 4,а интегратор 1 и гиперболический преобразователь 2 выполнены многодиапазонными. Функциональные схемы и состав блока управления .мно- Сьугодиапазонного интегратора, многодиапазонного гиперболического преобразователя и масштабирующего блока приведены в описании изобретения. 4 з.п. ф лыь 6 ил1347027 25 Устройство для измерения средних значений нестационарных сигналов со-. 30 держит многодиапазонный интегратор 1, .многодиапазонный гиперболический преобразователь 2, блок 3 выоорки - хранения, масштабирующий блок 4, блок 5 управления, ключ 6, управляющий и сигнальный входы 7 и 8 устройства, причем управляющий вход 7 устройства соединен с входом блока 5 управления и с управляющими входами ключа 6 и многодиапазонного интегратора 1,вход 4 О которого соединен с сигнальным входом 8 устройства, а аналоговый выход - со входом ключа 6, выход которого соединен со входом многодиапазонного гиперболического преобразова теля 2, выход которого соединен со входом блока 3 выборки и хранения, цифровой выход многодиапазонного интегратора 1 соединен с первым входом масштабирующего блока 4, первый выход блока 5 управления соединен с управляющим входом многодиапазонного гиперболического преобразователя 2, второй выход блока 5 управления соединен с управляющими входами блока 3с выборки - хранения и масштабирующего блока 4, третий выход блока 5 управления соединен с тактовым входом многодиапазонного гиперболического преИзобретение относится к измерительной .технике, предназначено для измерения средних значений сигналов и может быть использовано в установках технической диагностики по спектральному составу шумов и вибраций режимов работы различных промышленных объектов, а также в медицине при измерении среднего давления крови в те чение каждого сердечного цикла, определении среднего выдыхаемого объема СО в каждом дыхательном цикле и т.дЦелью изобретения является повьппение точности измерения за счет введения переменного масштаба интегрирова- ния и расширения диапазона вариаций времени усреднения.На фиг.1 представлена структурная схема устройства для измерения средних значений нестационарного сигналов; на фиг,2-5 - функциональные схемы многодиапазонного интегратора, блока управления, многодиапазонного гиперболического преобразователя, масштабирующего блока; на фиг.б временная диаграмма работы устройства,образователя и вторым входом масштабирующего блокаМногодиапазонный интегратор 1 содержит (Фиг.2 ) конденсатор 9,ключ 10, резистор 11, источник 12 опорных напряжений, операцлонный усилитель 13, компараторы 14 и 15, элемент ИЛИ 16, инвертор 17 (не показан), элемент 18 задержки, регистр 19, блок 20 коммутируемых конденсаторов, содержащий последовательно соединенные ключи 21-121-п и конденсаторы 22-122-и. Вход операционного усилителя 13 соединен с первыми выводами резистора 11, конденсатора 9, ключа 10, и блока 20 коммутируемых конденсаторов, выход операционного усилителя 13, соединен со вторыми выводами блока 20 коммутируемых конденсаторов, ключа 10 конденсатора 9, с первыми входами компараторов 14, 15 и выходом много диапазонного интегратора. Плюсовой и минусовый выходы источника 12 опорных напряжений соединены соответственно со вторыми входами компараторов 14 и 15, выходы которых соединены со входами элемента ИЛИ 1 б, выходом соединенного с тактовым входом регистра 19, выходы которого соединены с управляющими входами соответствующих ключей 21-121-п. Второй вывод резистора 11 и вход инвертора соединены соответственно с сигнальным и управляющим входами многодиапазонного интегратора 1, выходы инвертора соединен с параллельными входами регистра 19, управляющим входом ключа 10 и через элемент 18 задержки - с управляющим входом регистра 9.Блок 5 управления (фиг.З) содержит расширитель 23 импульсов и временной распределитель 24, входы которых соединены со входом блока 5 управления, первый выхоц временногораспределителя 24 и выход расширителя 23 импульсов являются соответственно первым и втсрым выходами блока 5 управления второй выход временного распределителя 24 является третьим выходом блока 5 управления.Иногодиапазонньй гиперболическийпреобразователь 2 (фиг.,4) содержит элемент 25 задержки, операционныйусилитель 26, четыре ключа 27-30, четыре резистора 31 34 два конденса тора 35 и Зб, инвертор 37, два блока 38 и 39 коммутируемьх конденсаторов, регистр 40. Блоки 38 и 39 ком 1347027мутируемых конденсаторов содержатконденсаторы 41- 141-п, 42-142-ии ключи 43-143-п, 44-144-п,Вход операционного усилителя 26 сое 5динен с первыми выводами резистора 34ключа 28 и входом многодиапазонногогиперболического преобразователя 2.Выход операционного усилителя соединен с первыми выводами ключей 29 10и 30, выводом блока 38 коммутируемыхконденсаторов и выходом многодиапазонного гиперболического преобразователя 2, тактовый вход которого соединен с тактовым входом регистра 40, а 15.управляющий вход - с управляющимивходами ключей 27, 28 и через инвертор 37 - с управляющими входами ключей 29 и 30, с параллельными входамирегистра 40 и через элемент задержки - с управляющим входом регистра 40,выходы которого соединены с управляющими входами ключей 43-143-п и44-144-п блоков 38 и 39 коммутируемых конденсаторов, 25Второй вывод ключа 28, первый вывод блока 39 коммутируемых конденсаторов, первые выводы конденсаторов 35и 36, первый выход ключа 27 соединены с общей шиной. Второй вывод кон- ЗОденсатора 36 соединен со вторым выводом ключа 30 и первым выводом резистора 32, второй вывод которого соединен со входом клоча 27 и первыми выводами резистора 31 и блока 38 комму- З 5тируемых конденсаторов. Второй выводрезистора 31 соединен со вторыми выводами ключа 29 и блока 39 коммутируемых конденсаторов. Масштабирующийблок 4 фиг.5 содержит дешифратор 45,40регистр 46, индикатор 47, элемент 48задержки, сччтчик 49, суммирующий ивычитающий входы которого соединенысоответственно с первым и вторым входом масштабирующего блока 4, а выход 45через последовательно соединеннЫе дешифраторы 45 и регистр 46 соединен синдикатором 47. Управляющий входмасштабирующего блока 4 соединен суправляющим входом регистра 46 и че Орез элемент 48 задержки - с управляющим входом счетчика 49,Устройство для измерения среднихзначений нестационарных сигналов работает следующим образом. 55На вход 6 устройства поступаетвходная аналоговая информация - исследуемый сигнал (фиг.б), подлежащаяусреднению, а на вход 7 - управляющийимпульс, характеризующий своей длительностью заданное время усреднения Т,В исходном состоянии на входе 7 управления устройства установлено напряжение нулевого уровня (фиг,бб). При этом напряжение на аналоговом выходе многодиапазонного интегратора 1 отсутствует (фиг,бв) из-за нулевого уровня напряжения, поступаюЩего на его управляющий вход, отчего электронный ключ 10 замкнут, регистр 19 взведен, а электронные ключи 21-1 и 21-и замкнуты. На третьем выходе блока 5 управления устанавливается напряжение нулевого уровня (фиг.бж). 1 где М,= - С К- масштаб интегрированиямногодиапазонного интегратора 1 в первомдиапазоне масштабирования его выходногонапряжения;величина сопротивлениявремязадающего резистора 11;- величина емкости конденсатора 9;- напряжение входногосигнала;время, отсчитанное отмомента В момент времени с на управление1устройства подается управляющий импульс напряжения уровня логической "единицы" (фиг.бб), который запускает блок 5 управления, замыкает ключ б и снимает условия сброса с многодиапазонного интегратора 1, размыкая ключ 10.Напряжение на управляющем входе регистра 19 удерживается на уровне логической "единицы в течение времени задержки элемента 18 задержки достаточным для занесения нулевого кода на выходы регистра 19, При этом электронные ключи 21-1 и 21-и размыкаютсяКроме того, с момента С подачи1 управляющего импульса на вход 7 устройства напряжение Бна выходе операционного усилителя 13 многодиапазонного интегратора 1 изменяется сог- ласно выражению1- Ч ас = МЧ асГ К. 5 1 1 Ь фПри достижении напряжением П(1) уровня опорных напряжений, поступающих на вторые входы компараторов 14 и 15, в момент й срабатывает (в зависимости от полярности напряжения У(, соответствующий компаратор. Так, при положительной полярности срабатывает компаратор 14, а при отрицательной - компаратор 15.Выходной сигнал с выхода соответствующего компаратора (фиг,бг, момент й ) через элемент ИЛИ 16 посту-2пает на тактовый вход регистра 19 и на цифровой выход многодиапазонного интегратора 1. При этом на первом выходе регистра 19 в момент С,2 формируется напряжение уровня логической "единицы", так как на последовательном входе регистра 19 установлено напряжение уровня логической "единицы" отчего электронный ключ 21-1 замыкается, подключая конденсатор 22-1 параллельно конденсатору 9, выходное напряжение операционного усилителя 13 уменьшается скачком до величиныБ =- -- ПС +Сгде Б+рл Цо значение напряжения на выходе операционного усилителя 13 в момент времени компарирования2 ф величина емкости конденсатора 22-1; напряжения соответственно на плюсовом 2 Яор ор С1 (гБ ,2 Ч(2 я) (С +С ) В. СДля любого 1-го диапазона масштабирования выходной величины многодиапазонного интегратора 1 выходное напряжение операционного усилителя 13 и интегратора 1 в момент С. начала 1-го диапазона представится в виде и минусоном выходах источника опорных напряжений.В результате этого с момента (начала второго диапазона масштабирования выходной величины многодиапазонного интегратора 1) изменяется масштаб представления результирующего напряжения на выходе операционного усилителя 13:масштаб ин. Е С )С=1 Уц = М, Ч о):.оВ момент с ключ 6 размыкается, а так как ключ 28 разомкнут, напряжение на неинвертирующем входе операционного усилителя 26 равно напряжению на конденсаторе 35 (которое сохраняется равным напряжены;1 П(;) ), поэтому напряжения Чс с(((41-1) (41-К) (4- ) Ч и Ч на.конденсаторах соот(42- И) с,ветственно 41-1-41-п, 42-1-42-и и 36 сохраняются равными напряжению на конденсаторе 35. тегрированиямногодиапаОзонного интегратора 1 втом диапзоне масштабирования еговыходного напряжения.Тогда с момента е, начала 1-го1 Ндиапазона масштабирования напряжениена выходе операционного усилителя 13и на выходе интегратора 1 будет изменяться согласноП. =.иЧа,(1) 1 4 5Выходное напряжение многодиапазонного интегратора 1 поступает на входмногодиапазонного гиперболическогопреобразователя 2. Так как в течениедействия управляющего импульса на управляющем входе 7 устройства ключ. 27ро находится в состоянии, при которомего вход скоммутирован с его первымвыходом, ключи 43-143-п, 44-144-и блоков 38 и 39, ключи 29, 30 и 6замкнуты, а ключ 28 разомкнут, то напряжения на конденсаторах 35, 36,3541-1 и 41-п, 42-1 и 42-и равны входному. Это обеспечивается тем, чтооперационный усилитель 26 работает врежиме повторителя напряжения.По окончании действия управляющего импульса на управляющем входе 7устройства в момент , (фиг.бб) напряжение на выходе интегратора 1 пропорционально величине интеграла напряжения сигнала Ч за время усред 5нения Т:Ч, . = Б . - до замыкания клюс.Ъча 28.Также по окончании входного управляющего импульса в момент с на упФ равляющем входе блока 5 управления снимаются условия сброса временного распределителя 24, на выходе которого вырабатываются управляющие импульсы уровня логической единицы" в заданные моменты времени.С момента с до с на обоих выхо 5дах временного распределителя 24 остаются низкие уровни напряжений (уровни логического "нуля"), а с момента времени с на первом выходе временного распределителя формируется импульс высокого уровня напряжения, который переводит ключ 27 вовторое состояние, при котором его выход скоммутирован с его вторым входом. При этом замыкается ключ "8, а инвертирующий импульс с выхода инвертора 37 размыкает в момент с клю 5 25 чи 29 и 30, отчего разрываются цепи разряда конденсаторов 42-1, 42-п, 41-1 и 41-п.Напряжение на управляющем входе регистра 40 с момента с удерживает-ся уровнем логической "единицы" в течение времени задержки элемента 25 задержки достаточным для занесения Инулевого кода на выходы репистИра 40, кроме первого, на котором остается напряжение уровня логической 35 "единицы". При этом ключи 43-2, 43-п, 44-2, 44-п, разомкнуты, а ключи 43-1, 44-1 замкнуты. В результате конденсаторы 41-1, 42-1 и 36 подключаются через соответствующие резисторы 31, 33, 40 32 к инверсному входу операционного усилителя 26. Токи, поступающие на вход операционного усилителя 26, суммируются. 45В результате этого на выходе операционного усилителя 26 формируется напряжение, оппроксимирующее гиперболическую зависимоСть11 )с 50Чпо закону- буН ъъ 1чЧ = Б 1)А ф4 т:1 55 где а =А ,В ,4 - коэффициенты, определяемые элементами гиперболического преобразователя 2. В соответствии с программой работы временного распределителя 24 в момент времени С на его втором выходе формируется импульс, поступающий на тактовый вход регистра 40 и на второй вход масштабирующего блока 4. При этом на первом выходе регистра 40 формируется напряжение уровня логического нуля, а на второмвыходе - напряжение уровня логической(начала второго диапазона измененйявыходного напряжения многодиапазонного гиперболического преобразЬвателя 2)изменяется масштаб представления результирующего напряжения на выходеоперационного усилителя 26 и на выходе преобразователя 2, что реализуется подключением с момента с черезрезисторы 31 и 33 ко входу операционного усилителя 26 конденсаторов 41-2и 42-2 соответственно.С поступлением импульсов со второго выхода временного распределителя 24 происходит сдвиг логическойединицы в старшие разряды регистра 40, что приводит к коммутации соответствующих конденсаторов блоков 38и 39.При 1-той коммутации (п1 т, 1) смомента с (1 + 4) начала 1-го диапазона изменения выходного напряжениямногодиапазонного гиперболическогопреобразователя 2 напряжение Ч (1,1)на выходе операционного усилителя 26изменяется от Б 1по закону,аппроксимирующему гиперболическуюзависимость),Ч. = о3 " с-с,где. - масштабный множитель в 1-томдиапазоне изменения выходного напряжения,При этом ы. определяется емкостьюпараллельно скоммутированных конденсаторов блоков 38 и 39.Спустя временной интервал КТ(К - масштабный коэффициент, которыйвыбирается из условия быстродействияустройства), после окончания действия управляющего импульса на входеблока 5 управления расширитель 23 импульсов в момент времени сс + КТформирует управляющий импульс, посту 1347027 10пающий с его выхода на управляющийвход блока 3 выборки-хранения, который регистрирует значение напряженияна выходе многодиапазонного преобразователя 2,Это напряжение в момент времениопределяется как7ч -6 (к ао 11Ц,1 ) А,где Л ., В . - коэффициенты, опредеУ 1 У 1ляемые элементами устройства;временные интервалызадержки формированиянапряжений соответствующих 1-х диапазоновизменения выходногонапряжения.Импульс управления с выхода блока 5 управления (фиг.бж, момент)поступает в моменттакже и на управляющий вход масштабирующего блока 4, в котором происходит вычисление масштаба представления выходнойвеличины И определяемого как М(т-юМ = аРеь Ыгде а - кратность масштабирования выходных величин многодиапазонного интегратора 1 и многодиапазонного гиперболического преобразователя;ш ,и - соответственно номера диапазонов масштабирующего многодиапазонного интегра.тора 1 и многодиапазонного гиперболического преобразователя.Работа масштабирующего блока заключается в следующем.В исходном состоянии счетчик 49 сброшен.В момент времени г счетчик 491увеличивает выходные коды, начиная с нулевого, на единицу после каждого импульса, приходящего на суммирующий вход в момент С и Ез (фиг.бг) с цифрового выхода многодиапазонного интегратора 1, что равносильно повышению масштаба входной величины на единицу масштаба с каждым приходящим импульсом (фиг.би, моменты С Г. ).Уменьшает выходные коды счетчика 49 после каждого импульса, приходящего на его вычитающий вход с третьего выхода блока 5 управления (фиг.бе, момент Т ), что равносильно уменьшению4 50 55 15 20 25 ЗО 3" 40 масштаба выходной величины на единицу масштаба (фиг.би, момент г. ).С выхода дешифратора 45 коды счетчика, преобразованные в вид, удобный для индикации, запоминаются в регистре 46 памяти по переднему фронту импульса, поступившего в момент на управляющий вход регистра 4 б со второго выхода блока 5 управления, и инициируются цифровым индикатором 47. Формула изобретения 1. Устройство для измерения средних значений нестационарных сигналов, содержащее последовательно соединенные интегратор, ключ и гиперболический преобразователь, вьгход которого соединен с входом блока выборки-хранения, управляющие входы гиперболического преобразователя и блока выборки- хранения соединены соответственно с первым и вторым выходами блока управления, вход которого является управляющим входом устройства, сигнальным входом которого является вход интегратора, о т л и ч а,ю щ е е с я тем, что, с целью повышения точности измерения за счет введения переменного масштаба интегрирования и расширения диапазона вариаций времени усреднения, в него введен масштабирующий блок, интегратор и гиперболический преобразователь выполнены многодиапазонными, управляющие входы многодиапазонного интегратора и ключа соединены с управляющим входом устройства, тактовый вход многодиапазонного гиперболического преобразователя соединен с третьим выходом блока управления, первый и второй входы масштабирующего блока соединены соответственно с цифровым выходом многодиапазонного интегратора и третьим выходом блока управления, угравляющий вход .масштабирующего блока соединен с вторым выходом блока угравления.2. Устройство по п,1, о т л и -ч а ю щ е е с я тем, что многодиапазонный интегратор содержит операционный усилитель, конденсатор, ключ, резистор, элемент задержки, регистр, два компаратора, источник опорных напряжений, элемент ИЛИ и блок коммутируемых конденсаторов, состоящий изи-параллельных цепей последовательносоединенных конденсаторов и ключей,управляющие входы которых соединеныс соответствующими выходами регистра, инвертирующий вход операционного усилителя соединен с первыми выводами конденсатора, резистора, ключа и бло ка коммутируемых конденсаторов, выход операционного усилителя соединен с вторыми выводами конденсатора, ключа, блока коммутируемых конденсато-. ров, первыми входами компараторов и 10 является аналоговым выходом многодиапазонного интегратора, вторые входы первого и второго компараторов подключены соответственно к плюсовому и минусовому выходам источника опорных 15 напряжений, выходы компараторов соединены с соответствующими входами элемента ИЛИ, выход которого соединен с тактовым входом регистра и.является цифровым выходом многодиапа зонного интегратора, управляющий вход многодиапазонного интегратора соединен с входом инвертора, выход которого соединен с управляющим входом ключа, параллельными входами регистра и через элемент задержки с управляющим входом регистра, на последовательный вход которого подано напряжение уровня логической единицы, второй вывод резистора является входом многодиа пазонного интегратора.3. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что многодиапазонный гиперболический преобразователь содержит регистр, операционный усилитель, четыре ключа, четыре резистора, два конденсатора, инвертор, регистр и два блока коммутируемых конденсаторов, состоящих из п-параллельных цепей, последовательно соеди ненных конденсаторов и ключей, управляющие входы соответствующих ключей обоих блоков коммутируемых конденсаторов объединены и подключены к соответствующим выходам регистра, на первый информационный вход которого подано напряжение логической единицы, первые выводы первого и второго резисторов и первого блока коммутируемых конденсаторов соединены с входом первого ключа, первый выход которого подключен к общей шине, а второй - к инвертирующему входу операционного усилителя и первому выводу третьего резистора, первые выводы первого и второго конденсаторов, второго ключа и второго блока коммутируемых конденсаторов подключены к общей шине, вторые выводы второго блока коммутируемых конденсаторов и первого резистора соединены с первым выводом третьего ключа, второй вывод первого конденсатора через четвертый резисторсоединены с вторым выводом второгоключа и входом операционного усилителя, который является входом многодиапазонного гиперболического преобразователя, управляющий вход которого соединен с управляющим входамипервого и второго ключей и с входоминвертора, выход которого соединен суправляющими входами третьего и четвертого ключей, с информационнымивходами, кроме первого, регистра ичерез элемент задержки с управляющимвходом регистра, вторые выводы второго резистора и второго конденсаторасоединены с первым выводом четвертого ключа, второй вывод которого соединен с вторыми выводами первого блока коммутируемых конденсаторов, третьего резистора и третьего ключа ивыходом операционного усилителя и является выходом многодиапазонного гиперболического преобразователя, тактовым.входом которого является тактовый вход регистра,4. Устройство по п.1, о т л и -ч а ю щ е е с я тем, что блок управления содержит расширитель .импульсови временной распределитель, входы которых объединены и являются входомблока управления, первый выход временного распределителя является первым выходом блока управления, вторымвыходом которого является выход расширителя импульсов, второй выход временного распределителя является третьим выходом блока управления.5. Устройство по и.1, о т л ич а ю щ е е с я тем, что масштабирующий блок содержит элемент задержки,последовательно соединенные счетчик,дешифратор, регистр и индикатор, суммирующий и вычитающий входы счетчикаявляются соответственно первым и вто-рым входами масштабирующего блока,управляющий вход которого соединен суправляющим входом регистра и черезэлемент задержки с управляющим входомсчетчика.13 ч 7027 иг йи ищ Воа.гир 1йи.гиа АМ Ф ггЖа КорректорВ,Бутяга Составитель Г.КозуТехред И.Попович едактор Н,Егорова 17(44 ВНИИПИ и 113035, Подписно Тираж 729 Государственного комитета делам изобретений и открытии Москва, Ж, Раушская наб., оизводственно-полиграфическое предприятие, г. Ужгор Проектная

СмотретьЗаявка

3973073, 04.11.1985

КУЙБЫШЕВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. АКАД. С. П. КОРОЛЕВА

МЕДНИКОВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, ПОРЫНОВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G01R 19/00

Метки: значений, нестационарных, сигналов, средних

Опубликовано: 23.10.1987

Код ссылки

<a href="https://patents.su/9-1347027-ustrojjstvo-dlya-izmereniya-srednikh-znachenijj-nestacionarnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для измерения средних значений нестационарных сигналов</a>

Предыдущий патент: Газоразрядный датчик

Следующий патент: Устройство для измерения средних значений нестационарных сигналов

Случайный патент: Станок для отбортовки обечаек