Устройство для кодирования и декодирования информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

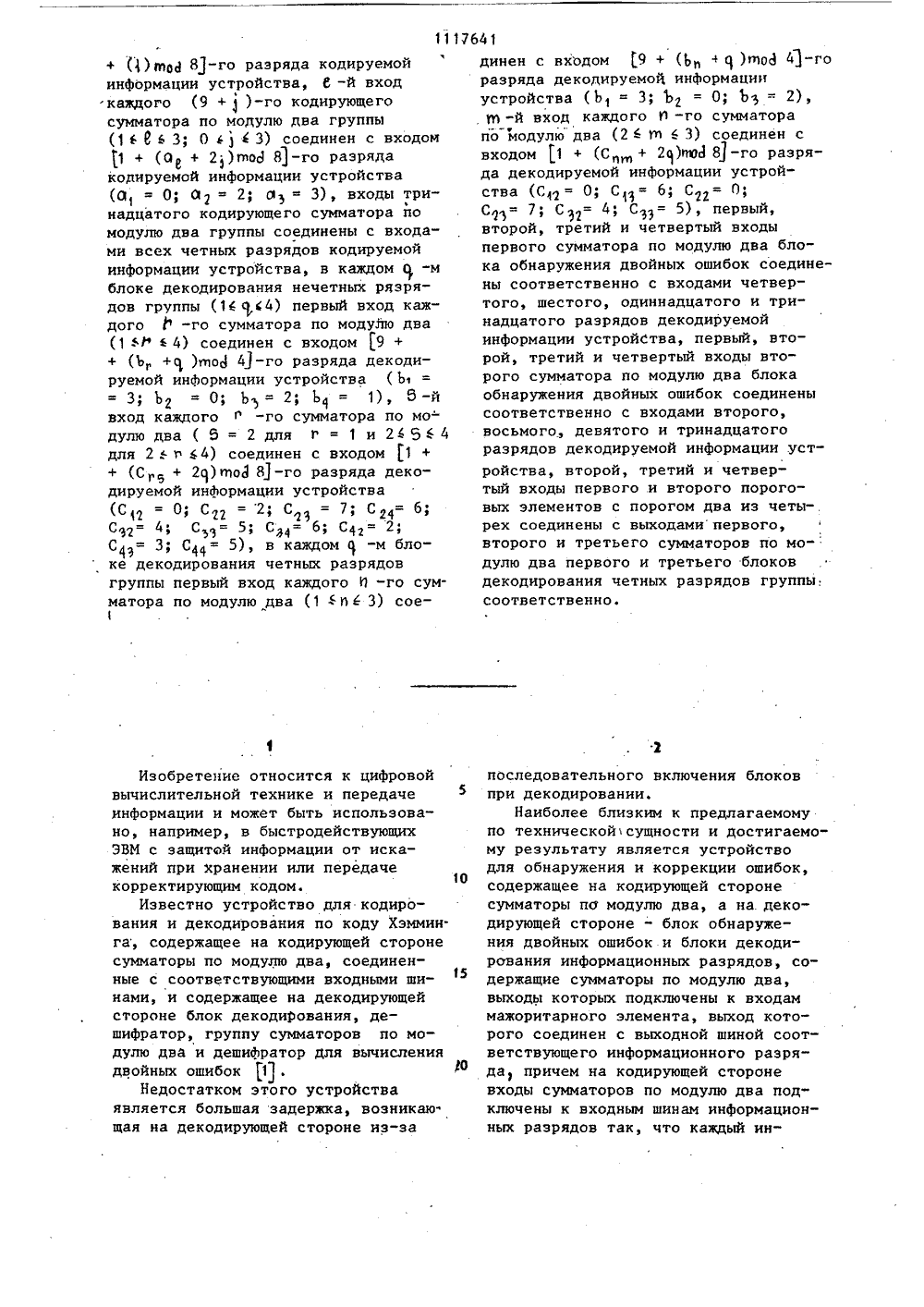

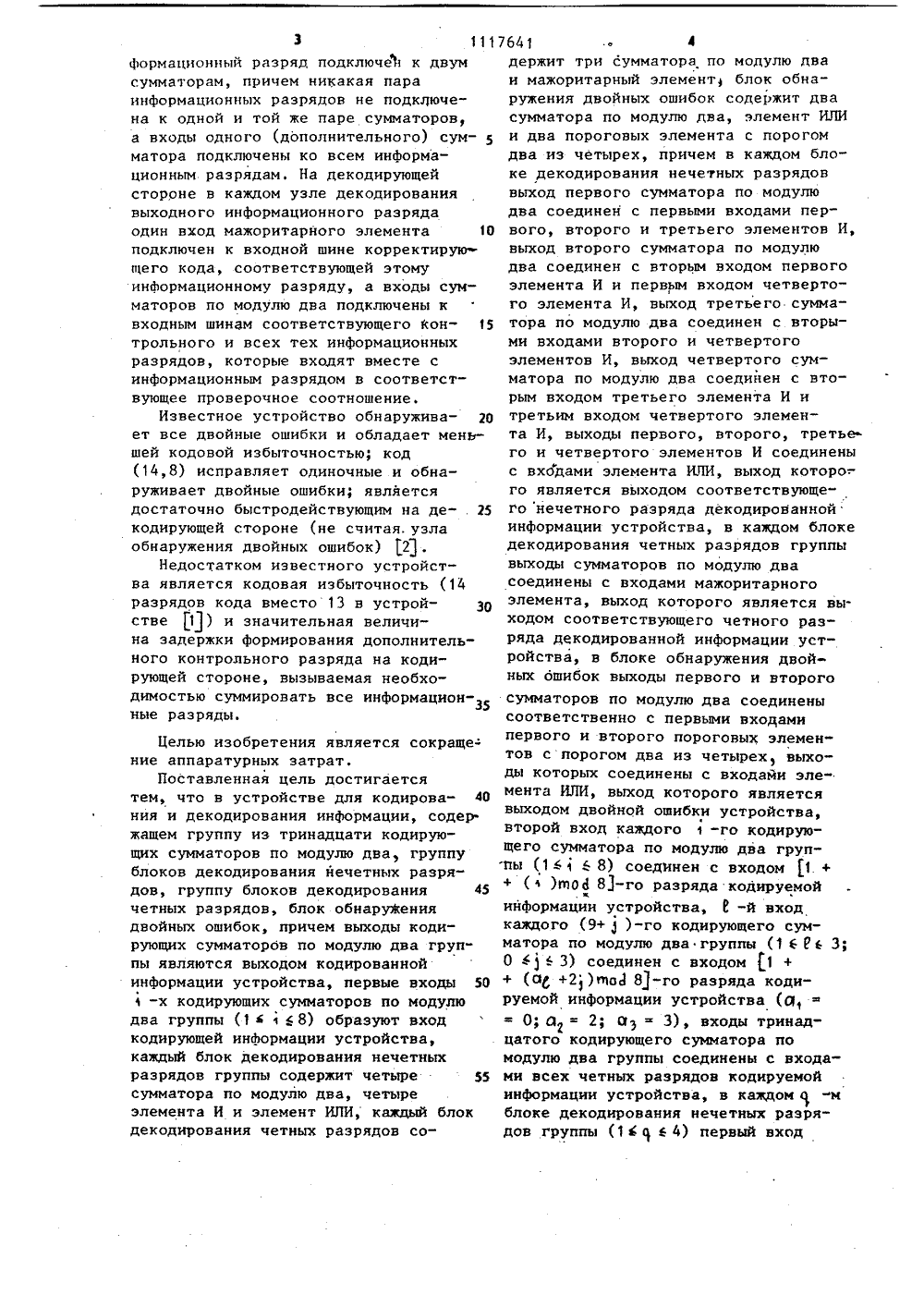

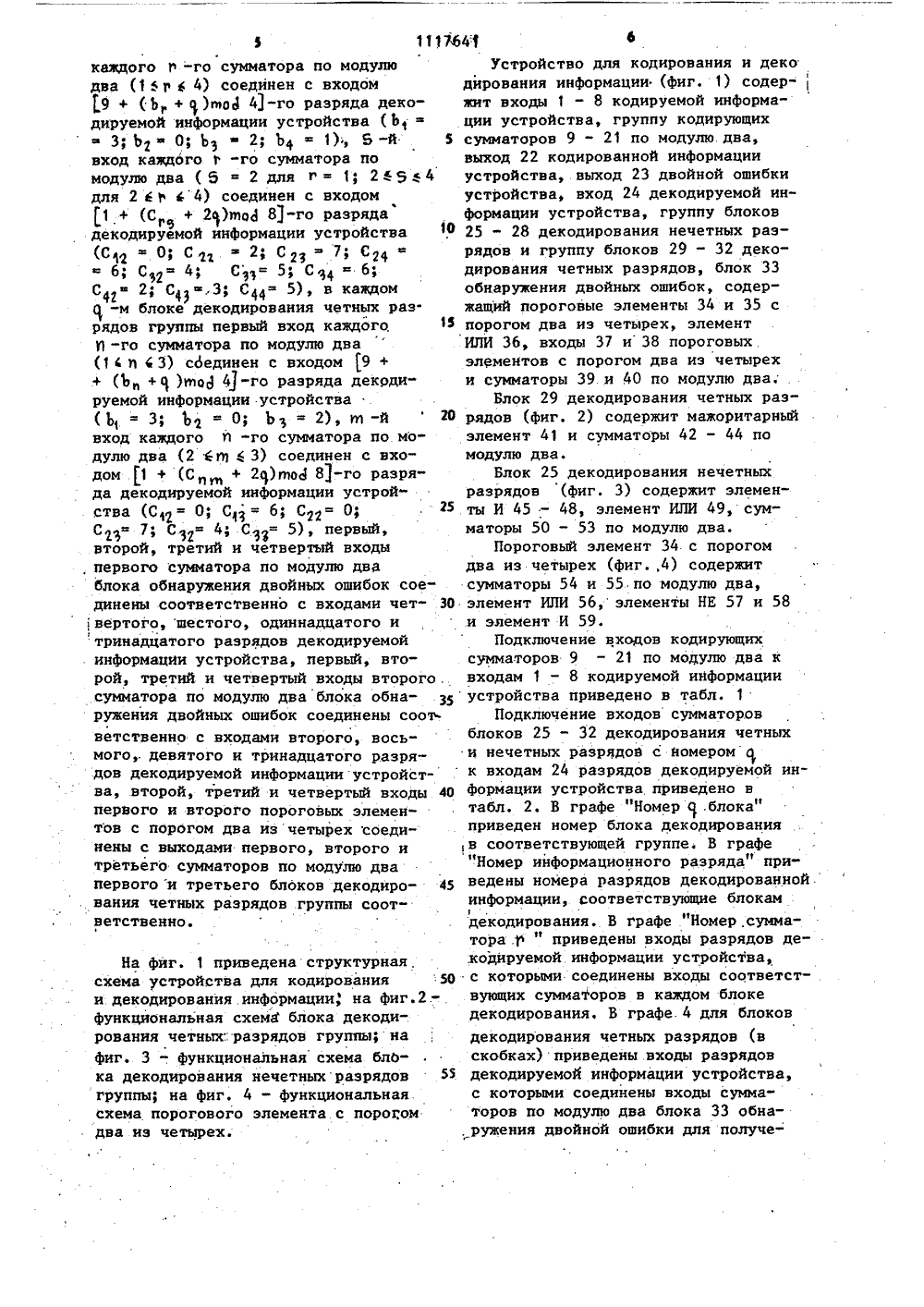

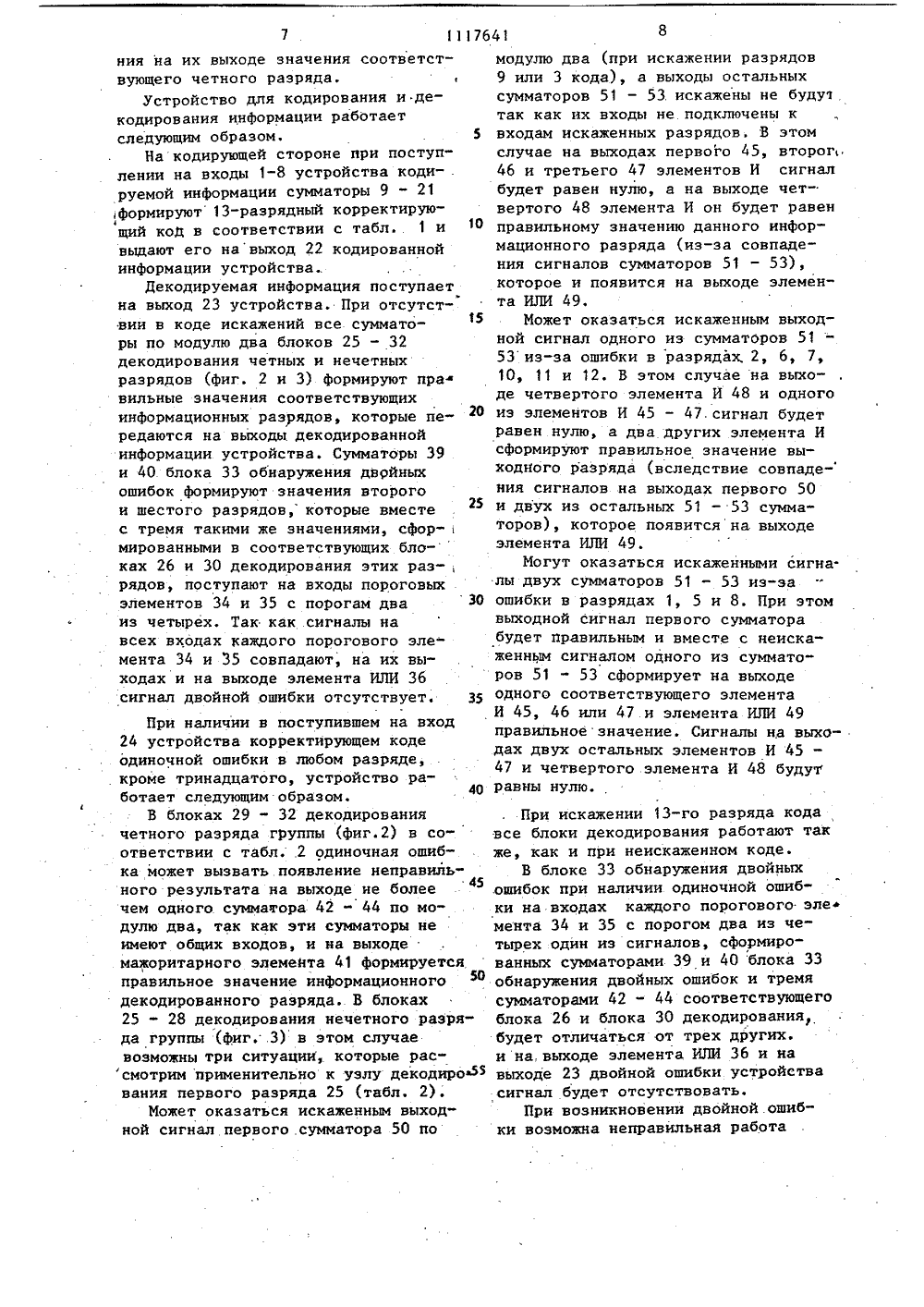

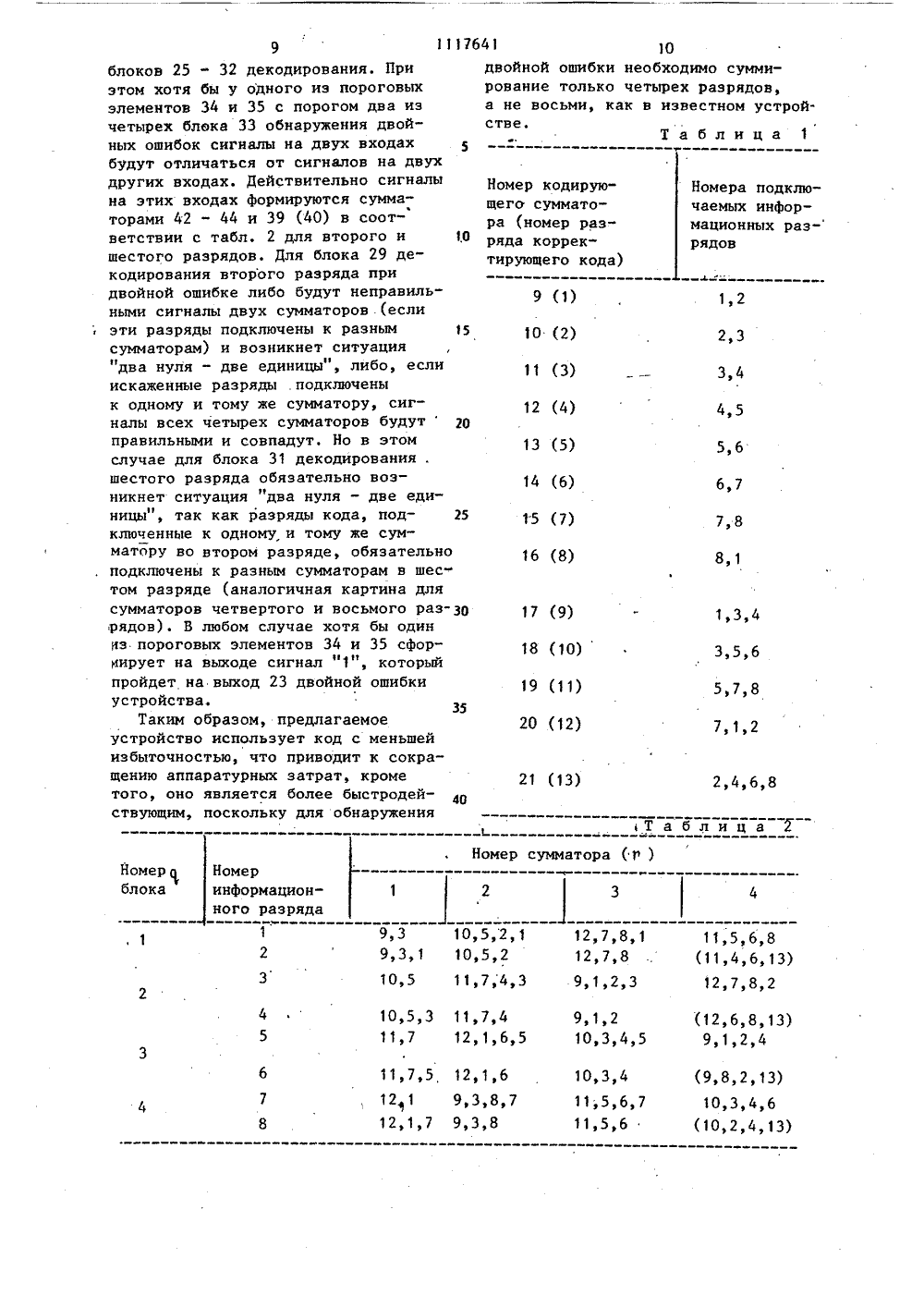

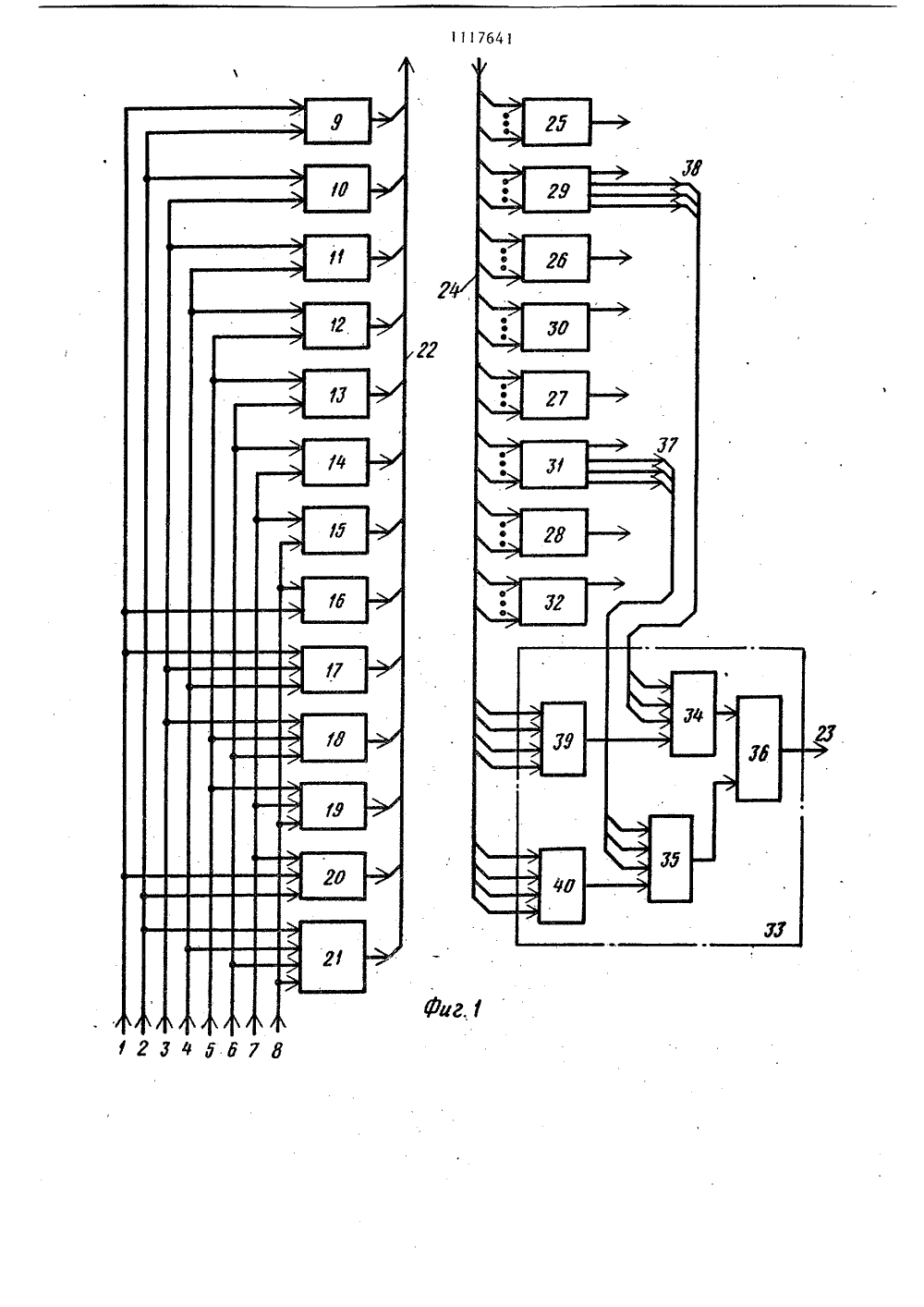

(56) 1. ХетагуровПовышение надежноройств методами ивания, М., "Энергрис. 2-2, с. 54,2. Патент СШАкл. 340-146.1, оптип). В 37И. Заровск А.Я. и др, сти цифровых уст збыточного кодир ия", 1974, с. 53 рис. 2-3, с.37-3 У 3601798, ублик, 1971 ( прот ОсудАРстВенный кОмитет сссР ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ ОРСКОМ,Ф СВИДЕТЕЛЬСТ(54)(57) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ, содержащее группу из тринадцати кодирующих сумматоров по модулю два группу блоков декодирования нечетных разря" дов, группу блоков декодирования четных разрядов, блок обнаружения двойных ошибок, причем выходы кодирующих сумматоров по модулю два группы являются выходом кодированной информации устройств, первые входы-х кодирующих;. сумматоров по модулю два группы (1( 1 ь 8) образуют вход кодирующей информации устройства, о т л и ч.а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, каждый блок декодирования нечетных разрядов группы содержит четыре сумматора по модулю два, четыре элемента И и элемент ИЛИ, каждый блок декодирования четных разрядов содержит три сумматора по модулю два и мажоритарный элемент, блок обнаружения двойных ошибок содержит два сумматора по модулю два, элемент НИЯф- Ъ ИЛИ и два пороговых элемента с порогом два из четырех, причем в каждом блоке декодирования нечетных разрядов выход первого сумматора по модулю4 ,два соединен спервыми входами первого, второго и третьего элементов И, выход второго сумматора по модулю два соединен с вторым входом первого элемента И и первым входом четвертого элемента И, выход третьего .сумматора по модулю два соединен с вторыми входами второго и четвертого элементов И, выход четвертого сумматора по модулю два соединен с вторым входом третьего элемента И и третьимР входом четвертого элемента И, выхо- а ды первого, второго, третьего и чет" вертого элементов И соединены с входами элемента ИЛИ, выход которого является выходом соответствующего нечетного разряда декодированной информации устройства, в каждом блоке декодирования четных разрядов группы выходы сумматоров по модулю два сое" динены с входами мажоритарного эле" ффффф мента, выход которого является вы ходом соответствующего четного раз- ф) ряда декодированной информации уст- ф ройства, в блоке обнаружения двой- ы ных ошибок выходы первого и второго сумматоров по модулю два соединены соответственно. с первыми входами первого и второго пороговых элементов с порогом два из четырех, выходы ф которых соединены с входами элемента ИЛИ, выход которого является выходом двойной ошибки устройства, второй вход каждого 1 -го кодирую- щего сумматора по модулю два группы (14 8) соединен с входом 1 ++ (1)вод 81 - го разряда кодируемой информации устройства, 6 -й вход каждого (9 + 1 )-го кодирующего сумматора по модулю два группы (1 6 1 й 3; О1 4 3) соединен с входои 1 + (О + 2 )ппос 81-го разряда кодируемой информации устройства (О = 0; О 2 2; д = 3), входы триЬ надцатого кодирующего сумматора по модулю два группы соединены с входами всех четных разрядов кодируемой информации устройства, в каждом ( -м блоке декодирования нечетных рязрядов группы (16 44) первый вход каждого 1 -го сумматора по моду 3 по два (1 ф4) соединен с входом 9 + + (Ь + )вой 4-го разряда декодируемой информации устройства ( Ь 13; Ъ 2 = 0 Ь = 2 Ъ, = 1), 8 -й вход каждого г -го сумматора по мо- дулю два ( б = 2 для г = 1 и 24 5 ь 4 для 2г4) соединен с входом 1 + + (Сг + 2 с)по 3 81-го разряда декодируемой информации устройства (С 1 = 0 С 2 = 2; С.2 = 7 С 4 - 6 с 2= 4; С= 5; Сз 4= б; С 4= 2; С = 3; С = 5), в каждом-м бло 1 44ке декодирования четных разрядов группы первый вход кажцого И -го сумматора по модулю два (1 й 6 3) соеИзобретение относится к цифровой вычислительной технике и передаче информации и может быть использовано, например, в быстродействующих ЭВМ с защитой информации от искажений при хранении или передаче корректирующим кодом.Известно устройство для кодирования и декодирования по коду Хэммин. га, содержащее на кодирующей стороне сумматоры по модулю два, соединенные с соответствующими входными шинами, и содержащее на декодирующей стороне блок декодирования, дешифратор, группу сумматоров по модулю два и дешифратор для вычисления двойных ошибок 1 .СОНедостатком этого устройства является большая задержка, возникаю. щая на декодирующей стороне из-за динен с входом 9 + (ЬЧ )лют 41-го разряда декодируемой информацииустройства ( Ь = 3 Ъ = 0; Ь =. 2),, П -й вход каждого О -го сумматорапо модулю два (2 6 О 1 б 3) соединен свходом+ (С + 2)обад 8-го разряда декодируемой информации устройства (С 2= 0; С 1= 6 С= О,С,1= 7 С 3= 4 С= 5), первый,второй, третий и четвертый входыпервого сумматора по модулю два блока обнаружения двойных ошибок соединены соответственно с входами четвертого, шестого, одиннадцатого и тринадцатого разрядов декодируемойинформации устройства, первый, второй, третий и четвертый входы второго сумматора по модулю два блокаобнаружения двойных ошибок соединенысоответственно с входами второго,восьмого, девятого и тринадцатогоразрядов декодируемой информации устройства, второй, третий и четвертый входы первого и второго пороговых элементов с порогом два из четырех соединены с выходамипервого,второго и третьего сумматоров по мо-:дулю два первого и третьего блоковдекодирования четных разрядов группы.соответственно. последовательного включения блоков при декодировании.Наиболее близким к предлагаемому по техническойсущности и достигаемому результату является устройство для обнаружения и коррекции ошибок, содержащее на кодирующей стороне сумматоры по модулю два, а на декодирующей стороне - блок обнаружения двойных ошибок и блоки декодирования информационных разрядов, содержащие сумматоры по модулю два, выходы которых подключены к входам мажоритарного элемента, выход которого соединен с выходной шиной соответствующего информационного разряда причем на кодирующей стороне входы сумматоров по модулю два подключены к входным шинам информационных разрядов так, что каждый инФормационный разряд подключен к двум сумматорам, причем никакая пара информационных разрядов не подкЛюче" на к одной и той же паре сумматоров, а входы одного (дополнительного) сум матора подключены ко всем информационным разрядам. На декодирующей стороне в каждом узле декодирования выходного информационного разряда один вход мажоритарного элемента 1 О подключен к входной шине корректирую щего кода, соответствующей этому информационному разряду, а входы сумматоров по модулю два подключены к входным шинам соответствующего кон трольного и всех тех информационных разрядов, которые входят вместе с информационным разрядом в соответствующее проверочное соотношение.Известное устройство обнаружива ет все двойные ошибки и обладает меньшей кодовой избыточностью; код (14,8) исправляет одиночные и обнаруживает двойные ошибки; является достаточно быстродействующим на де- . 25 кодирующей стороне (не считая. узла обнаружения двойных ошибок) 2 .Недостатком известного устройства является кодовая избыточность (14 разрядов кода вместо 13 в устрой- З 0 стве Я) и значительная величина задержки формирования дополнительного контрольного разряда на кодирующей стороне, вызываемая необходимостью суммировать все информацион 35 ные разряды.Целью изобретения является сокраще- ние аппаратурных затрат.Поставленная цель достигается тем, что в устройстве для кодирова ния и декодирования информации, содержащем группу из тринадцати кодирующих сумматоров по модулю два группу блоков декодирования нечетных разрядов, группу блоков декодирования 45 четных разрядов, блок обнаружения двойных ошибок, причем выходы кодирующих сумматоров по модулю два груп" пы являются выходом кодированной информации устройства, первые входы 50 1 -х кодирующих сумматоров по модулю два группы (1 4ь 8) образуют вход кодирующей информации устройства, каждый блок декодирования нечетных разрядов группы содержит четыре 55 сумматора по модулю два, четыре элемента И и элемент ИЛИ, каждый блок декодирования четных разрядов со 7641 4держит три сумматора по модулю два и мажоритарный элемент блок обнаружения двойных ошибок содержит два сумматора по модулю два, элемент ИЛИ и два пороговых элемента с порогом два из четырех, причем в каждом блоке декодирования нечетных разрядов выход первого сумматора по модулю два соединен с первыми входами первого, второго и третьего элементов И, выход второго сумматора по модулю два соединен с вторым входом первого элемента И и первым входом четвертого элемента И, выход третьего сумматора по модулю два соединен с вторыми входами второго и четвертого элементов И, выход четвертого сумматора по модулю два соединен с вторым входом третьего элемента И и третьим входом четвертого элемента И, выходы первого, второго, третье го и четвертого элементов И соединены с входами элемента ИЛИ, выход которо-. го является выходом соответствующего нечетного разряда декодированной информации устройства, в каждом блоке декодирования четных разрядов группы выходы сумматоров по модулю два соединены с входами мажоритарногоэлемента, выход которого является выходом соответствующего четного разряда декодированной информации устройства, в блоке обнаружения двойных ошибок выходы первого и второгосумматоров по модулю два соединенысоответственно с первыми входами первого и второго пороговых элемен" тов с порогом два из четырех выхо) ды которых соединены с входами элемента ИЛИ, выход которого являетсявыходом двойной ошибки устройства, второй вход каждого 1 -го кодирую" щего сумматора по модулю два груп.пы (1 4 1 6 8) соединен с входом 1 + + ( )вод 83-го разряда кодируемой информации устройства, 1 -й вход каждого (9+ 1 )-го кодирующего сумматора по модулю два группы (1 Е 8 й 3; О 4 6 3) соединен с входом 1 + (а +21)Ъод 8-го разряда кодируемой информации устройства (О,= О; а = 2; О 3), входы тринадцатого кодирующего сумматора по модулю два группы соединены с входами всех четных разрядов кодируемой информации устройства, в каждом-м блоке декодирования нечетных разрядов группы (1 ьа 4) первый вход111764 ветственно с входами второго, восьмого,. девятого и тринадцатого разрядов декодируемой информацииустройства, второй, третий и четвертый входы 40первого и второго пороговых элементов с порогом два из четырех соединены с выходами первого, второго итретьего сумматоров по модулю двапервого и третьего блоков декодирования четных разрядов группы соот"ветственно. каждого Р -го сумматора по модулю два (15 р 6 4) соединен с входом 1.9 + (Ь + )аос 1 41-го разряда декодируемой информации устройства ( Ь 13; Ь " 0 Ь 3 ф 2 Ъ 4 1), б -й 5 вход каждого г "го сумматора по модулю два ( 52 для 1 1; 2с 4 для 2 й 1 й 4) соединен с входом 1 + (Сг + 2 с)ва 3 8 Д-го разряда декодируемой информации устройства12 ф 7123 ф 24 = 6; С 2- 4; С 11= 5 С Ц 6; С 4 2; С 4 Зр С 44 5), в каждом42( -м блоке декодирования четных раз. рядов группы первый вход каждого 1 и -го сумматора по модулю два (1 4 й 4 3) соединен с входом 9 + + (Ъ + Я )вод 41 -го разряда декрдируемой информации устройства (Ь,=з; Ъ,=О; Ъ,=2),т-й го вход каждого п "го сумматора по модулю два (2 ба 4 3) соединен с входом 1 + (Сп + 20)вод 81-го разряда декодируемой информации устройства (С 2= О; С = 6; С = О; . 25 С 2 7; С.32= 4; С= 5), первый, второй, третий и четвертый входы , первого сумматора по модулю два блока обнаружения двойных ошибок соединены соответственно с входами чет 1 вертого, шестого, одиннадцатого и тринадцатого разрядов декодируемой информации устройства, первый, второй, третий и четвертый входы второго . сумматора по модулю два блока обнаружения двойных ошибок соединены соотНа фиг. 1 приведена структурная. схема устройства для кодирования 50 и декодирования. информации, на фиг2. - функциональная схема блока декодирования четных разрядов группы; на фиг. 3 - функциональная схема блока декодирования нечетных разрядов группы; на фиг. 4 - функциональная схема порогового элемента с порогом два из четырех. Устройство для кодирования и декодирования информации (фиг. 1) содер"жит входы 1 - 8 кодируемой информации устройства, группу кодирующихсумматоров 9 - 21 по модулю. два,выход 22 кодированной информацииустройства, выход 23 двойной ошибкиустройства, вход 24 декодируемой информации устройства, группу блоков25 - 28 декодирования нечетных разрядов и группу блоков 29 - 32 декодирования четных разрядов, блок 33обнаружения двойных ошибок, содержащий пороговые элементы 34 и 35 спорогом два из четырех, элементИЛИ 36, входы 37 и 38 пороговыхэлементов с порогом два из четырехи сумматоры 39 и 40 по модулю два.Блок 29 декодирования четных разрядов (фиг. 2) содержит мажоритарныйэлемент 41 и сумматоры 42 - 44 помодулю два,Блок 25 декодирования нечетныхразрядов (фиг, 3) содержит элементы И 45 - 48, элемент ИЛИ 49, сумматоры 50 - 53 по модулю два.Пороговый элемент 34 с порогомдва из четырех (фиг.,4) содержитсумматоры 54 и 55 по модулю два,элемент ИЛИ 56, элементы НЕ 57 и 58и элемент И 59.Подключение входов кодирующихсумматоров 9 - 21 по модулю два квходам 1 - 8 кодируемой информацииустройства приведено в табл. 1Подключение входов сумматоровблоков 25 - 32 декодирования четныхи нечетных разрядов с номеромк входам 24 разрядов декодируемой информации устройства приведено втабл. 2. В графе "Номер (,блока"приведен номер блока декодирования"Номер информационного разряда" приведены номера разрядов декодированнойинформации, соответствующие блокамдекодирования. В графе "Номер, сумматора .1 " приведены входы разрядов де.кодируемой информации устройства,с которыми соединены входы соответствующих сумматоров в каждом блокедекодирования. В графе. 4 для блоковдекодирования четных разрядов (вскобках) приведены входы разрядовдекодируемой информации устройства,с которыми соединены входы сумматоров по модулю два блока 33 обна, ружения двойной ошибки для получе1176 ния на их выходе значения соответствующего четного разряда,Устройство для кодирования и декодирования информации работает следующим образом. 5На кодирующей стороне при поступлении на входы 1-8 устройства коди- . руемой информации сумматоры 9 - 21 формируют 13-разрядный корректирующий код в соответствии с табл. 1 и1 О выдают его навыход 22 кодированной информации устройстваДекодируемая информация поступает на выход 23 устройства. При отсутствии в коде искажений все сумматоры по модулю два блоков 25 - 32 декодирования четных и нечетных разрядов (фиг. 2 и 3) Формируют пра вильные значения соответствующих информационных разрядов, которые передаются на выходы декодированной информации устройства. Сумматоры 39 и 40 блока 33 обнаружения дврйных ошибок формируют значения второго и шестого разрядов, которые вместе с тремя такими же значениями, сфор-мированными в соответствующих бло- ках 26 и 30 декодирования этих раз-; рядов, поступают на входы пороговых элементов 34 и 35 с порогам два из четырех, Так как .сигналы на всех входах каждого порогового элемента 34 и 35 совпадают, на их выходах и на выходе элемента ИЛИ 36 сигнал двойной ошибки отсутствует. 35 При наличии в поступившем на вход 24 устройства корректирующем коде одиночной ошибки в любом разряде, . кроме тринадцатого, устройство работает следующим образом.В блоках 29 - 32 декодирования четного разряда группы (фиг.2) в соответствии с табл, .2 одиночная ошибка может вызвать. появление неправильного результата на выходе не более чем одного. сумматора 42 - 44 по модулю два, так как эти сумматоры не имеют общих входов, и на выходе мажоритарного элемейта 41 формируется правильное значение информационного декодированного разряда. В блоках 25 - 28 декодирования нечетного разряда группы (фиг. 3) в этом случае возможны три ситуации, которые рассмотрим применительно к узлу декодиро 55 вания первого разряда 25 (табл. 2).Может оказаться искаженным выходной сигнал первого .сумматора 50 по 41 8модулю два (при искажении разрядов 9 или 3 кода), а выходы остальных сумматоров 51 - 53. искажены не будут так как их входы не подключены к входам искаженных разрядов. В этом случае на выходах первого 45, второг 46 и третьего 47 элементов И сигнал будет равен нулю, а на выходе четвертого 48 элемента И он будет равен правильному значению данного информационного разряда (из-за совпадения сигналов сумматоров 51 - 53), которое и появится на выходе элемента ИЛИ 49.Может оказаться искаженным выходной сигнал одного из сумматоров 51 53 из-за ошибки в разрядах, 2, 6, 7, 10, 11 и 12. В этом случае на выходе четвертого элемента И 48 и одного иэ элементов И 45 - 47.сигнал будет равен нулю, а два других элемента И сформируют правильное значение выходного разряда (вследствие совпадения сигналов на выходах первого 50 и двух из остальных 51 - 53 сумматоров), которое появится на выходе элемента ИЛИ 49.Могут оказаться искаженными сигна. лы двух сумматоров 51 - 53 иэ-эа ошибки в разрядах 1, 5 и 8. При этом выходной сигнал первого сумматора будет правильным и вместе с неискаженным сигналом одного из сумматоров 51 - 53 сформирует на выходе одного соответствующего элемента И 45, 46 или 47 и элемента ИЛИ 49 правильное значение. Сигналы на выходах двух остальных элементов И 45 - 47 и четвертого элемента И 48 будут равны нулю. При искажении 13-го разряда кодавсе блоки декодирования работают также, как и при неискаженном коде.В блоке 33 обнаружения двойныхошибок при наличии одиночной ошибки на входах каждого порогового злемента 34 и 35 с порогом два из четырех один из сигналов, сформированных сумматорами 39 и 40 блока 33обнаружения двойных ошибок и тремясумматорами 42 - 44 соответствующегоблока 26 и блока 30 декодирования,будет отличаться от трех других.и на,выходе элемента ИЛИ 36 и навыходе 23 двойной ошибки устройствасигнал будет отсутствовать,При возникновении двойной.ошибки возможна неправильная работаНомер кодирую- щего сумматора (номер раз О ряда коррек"тирующего кода) Номера подключаемых информационных раз-рядов двойной ошибке либо будут неправильными сигналы двух сумматоров .(если эти разряды подключены к разным 15 сумматорам) и возникнет ситуация "два нуля - две единицы", либо, если искаженные разряды подключены к одному и тому же сумматору, сигналы всех четырех сумматоров будут2 О правильными и совпадут. Но в этом случае для блока 31 декодирования . шестого разряда обязательно возникнет ситуация "два нуля - две единицы , так как разряды кода, под ключенные к одному и тому же сумматору во втором разряде, обязательно подключены к разным сумматорам в шестом разряде (аналогичная картина для сумматоров четвертого и восьмого раз-Зо рядов). Б любом случае хотя бы одиняз пороговых элементов 34 и 35 сформирует на выходе сигнал "1", которыйпройдет на выход 23 двойной ошибки устройства,Таким образом, предлагаемое устройство использует код с меньшей избыточностью, что приводит к сокращению аппаратурных затрат, крометого, оно является более быстродействующим, поскольку для обнаружения 9 (1) 1,2 10 (2) 2,3 11 (3) 3,4 4,5 12 (4) 13 (5) 5,6 14 (6) 6,7 15 (7) 16 (8) 7,8 17 (9) 1,3,4 3,5,6 5,7,8 18 (10) 19 (11) 20 (12) 7,1,2 21 (13) 2,4,6,8Т а б л и ц а Номер сумматора (Р ) 23 9,39,3,1 11,5,6,84 9 1 блоков 25 " 32 декодирования. При этом хотя бы у одного из пороговых элементов 34 и 35 с порогом два из четырех блока 33 обнаружения двойных ошибок сигналы на двух входах будут отличаться от сигналов на двух других входах. Действительно сигналы на этих входах формируются сумматорами 42 - 44 и 39 (40) в соответствии с табл. 2 для второго и шестого разрядов, Для блока 29 декодирования второго разряда при НомерНомерблока информационного разряда 117641 Одвойной ошибки необходимо суммирование только четырех разрядов, а не восьми, как в известном устройстве.Таблица 1 5Составитель В, ГречневЦицина Техред 3,Палий Корректор В. кто з 7221 ое 1 Патент", г. Ужгород, ул. Проектная, 4 филиал НИИПИ Гос по делам 35 Москв Тираж 698 Подлдарственного комитета .СССРизобретений и открытий

СмотретьЗаявка

3613420, 29.06.1983

ВОЕННАЯ АКАДЕМИЯ ИМ. Ф. Э. ДЗЕРЖИНСКОГО

ЕЩИН КОНСТАНТИН КОНСТАНТИНОВИЧ, ЗАРОВСКИЙ ВИТАЛИЙ ИВАНОВИЧ, МАСЛЮКОВ ЕВГЕНИЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: декодирования, информации, кодирования

Опубликовано: 07.10.1984

Код ссылки

<a href="https://patents.su/9-1117641-ustrojjstvo-dlya-kodirovaniya-i-dekodirovaniya-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования и декодирования информации</a>

Предыдущий патент: Устройство для контроля дискретных систем

Следующий патент: Устройство для управления подключением резерва

Случайный патент: Шнековый конвейер