Устройство для вычисления экспоненциальной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1057944

Автор: Баранов

Текст

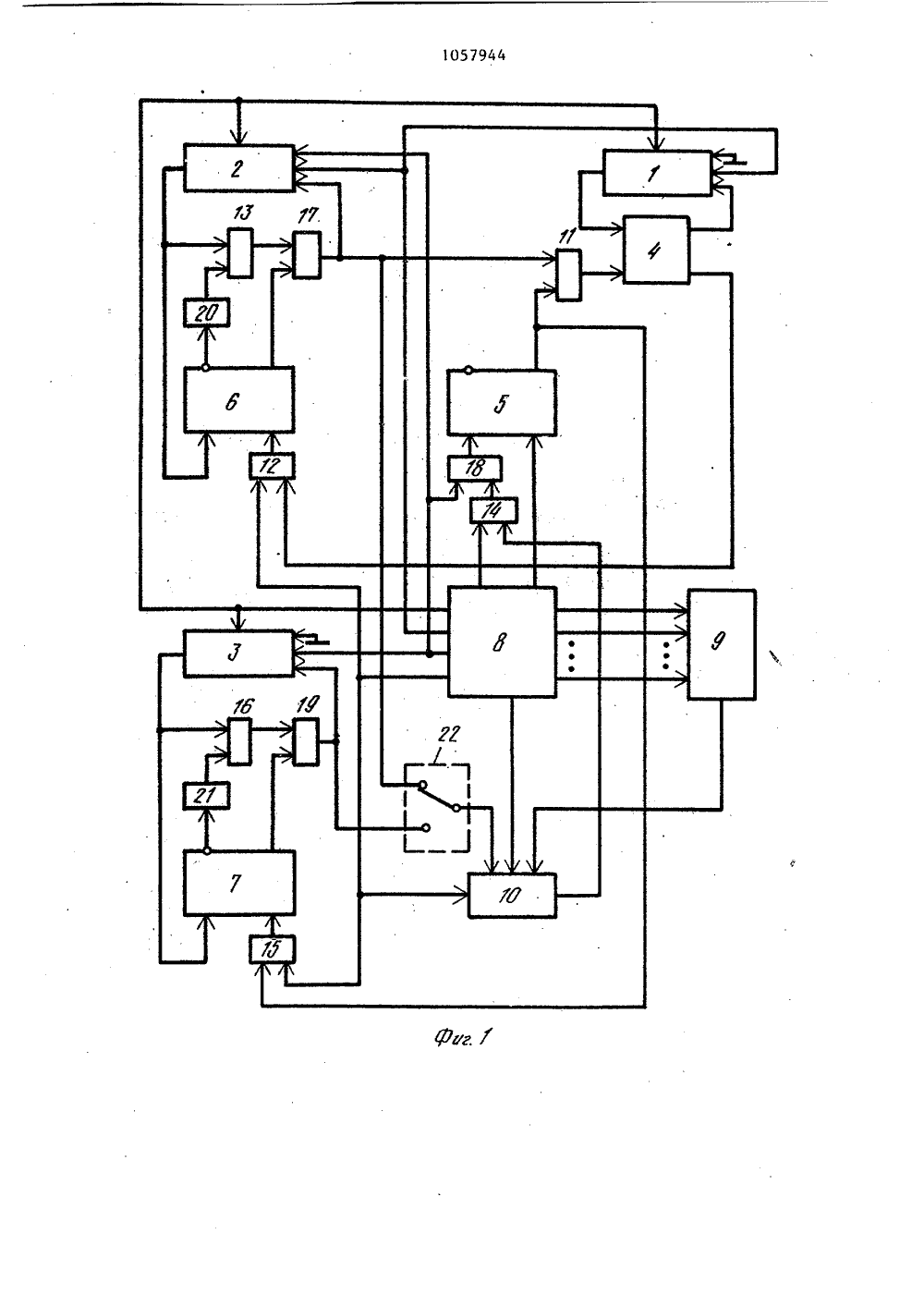

ОЮЗ СОВЕТСКИХОЦИАЛИСТИЧЕСНИЕСПУБЛИК,(19) (И) А а) С 06 Г 7 556 ИСАНИЕ ТОРСНОМУ С ОБРЕТЕНИ ТЕПЬСТВУ ельство ССС4, 1980 и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРЯО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 611 896619(71) Ордена Ленина институт кибернетики АН Украинской ССР(54)(57) 1. устРОйство для вычисле- НИЯ ЭКСПОНЕНЦИАЛЬНОЙ ФУНКЦИИ по авт.св. У 896619, о т л и ч а ю - щ е е с я тем, что, с целью расширения класса решаемых задач путем дополнительного вычисления логарифмической функции, в него введены блок управления, третий регистр сдви-. , га, регистр аргумента, второй и третий элементы ИЛИ, четвертый, пятый и шестой элементы И, второй элемент задержки, третий триггер, коммутатор и схема сравнения, причем первый выход блока управления соединен с входом регистра аргумента, выход которого соединен с первым информационным входом схемы сравнения, вход синхронизации которой соединен с вторым выходом блока управления, тре тий выход которого подключен к первому входу первого триггера, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом схемы сравнения, второй информационный вход которой соединен с выходом коммутатора, первый информационный вход которого соединен с информационным входом третьего регистра сдвига и выхо-, дом третьего элемента ИЛИ, первый вход которого соединен с прямым выходом третьего триггера, первый .вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выходом первого триггера, входы синхронизации первого, второго и третьего регистров сдвига соединены с четвертым выходом бло. ка управления, пятый выход которого соединен с вторым входом четвертого элемента И, шестой выход блока управления соединен с вторыми входами второго и пятого элементов И и вхо дом сброса схемы сравнения, седьмой выход блока управления соединен с входами записи первого и второго ре- С гистров сдвига, восьмой выход блока управления соединен с входами ввода данных второго и записи третьего ре гистров сдвига и вторым входом второго элемента ИЛИ, входы ввода дан ных первого и третьего регистров сдвига соединены с входом нулевого . потенциала устройства, вход задания режима которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом первого элемента ИЛИ, выход третьего регистра сдвига соединен с первым входом шестого элемента И и вторым входом третьего триггера, инверсный выход которого соединен через второй элемент задержки с вторым входом шестого элемента И, выход которого соед - нен с вторым входом третьего элемента ИЛИ,44 105792. Устройство по п, 1, о т л ич а ю щ е е с я тем, что, блок управления содержит генератор импульсов,распределитель импульсов, элементНЕ, элемент ИЛИ-НЕ, элемент И, ключ, 11генератор одиночных импульсов, коммутатор, триггер и элемент ИЛИ,причем выход генератора импульсовсоединен с входом распределителяимпульсов и через элемент НЕ - с.первыми входами элементов ИЛИ-НЕ и И,вторые входы которых соединены соответственно с первым и вторым выходами распределителя импульсов, выходы которого соединены с первым выходом блока управления, первый выходраспределителя импульсов подключенк первому входу элемента ИЛИ, выходэлемента И соединен с первыми входамитриггера и генератора одиночных импульсов, второй вход и выход которого соединены соответственно с выходом ключа и информационным входом коммутатора, управляющий вход которого является входом задания режи" ма блока управления, управляющий и информационный входы ключа соединены соответственно с входом начального запуска и входом нулевого потенциала блока управления, первый выход коммутатора соединен с вторым входом триггера, выход которого соединен с вторым входом элемента ИЛИ, выходы с второго по восьмой блока управления соединены соответственнои с выходом элемента ИЛИ-НЕ, вторым выходом коммутатора,выходом генератора импульсов, выходом элементаИ,первым выходом распределителя импульсов, в ыходом элемента ИЛИ и выходом триггера.Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных устройствах и устройствах дискретной автоматики для вычисления экспонен циальной или логарифмической функции.По основному авт,св. Р 896619 известно устройство, содержащее два регистра сдвига, сумматор, два триггера, три элемента И, элемент ИЛИ и элемент задержки, причем первый выход сумматора соединен через первый регистр сдвига с его первым входом, первый вход и прямой выход первого триггера соединены соответственно с входной шиной устройства и с пербым входом первого элемента И, выход которого соединен с вторым входом20 сумматора, второй выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом второго триггера, второй вход которого подключен к выходу второго регистра сдвига и к первому входу третьего элемента И, второй вход которого через первый элемент задержки соединен с инверсным выходом второго триггера, прямой выход которого подключен к первому входу30 первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И и с вторым входом первого элемента Ы, подключенного вторым входом к входу вторс 1 го регистра сдвига 111.Недостаток устройства заключается в ограниченных функциональных возможностях.Цель изобретения - расширение класса решаемых задач путем дополнительного вычисления логарифмической функции,Поставленная цель достигается тем, что в устройство дпя вычисления экспоненциальной функции дополнительно введены блок управления, третий регистр сдвига, регистр аргумента, второй и третий элементы ИЛИ, четвертый, пятый и шестой .лементы И, второй элемент задержки, третий триггер коммутатор и схема сравнения, причем первый выход блока управления соединен с входом регистра аргумента., выход которого соединен с первым информационным входом схема сравнения, вход синхронизации которой соединен с вторым выходом блока управления, третий выход которого подключен к первому входу1057944 10 5 20 25 30 40 35 50 55 первого триггера, второй вход кото-.рого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элементаИ, первый вход которого соединен свыходом схемы сравнения, второй информационный вход которой соединенс выходом коммутатора, первый информационный вход которого соединен синформационным входом третьего регистра сдвига и выходом третьего элемента ИЛИ, первый вход которого соедииен с прямым выходом третьего триггера, первый вход которого соединен с выходом пятого элемента И, первый вход которого соединен с прямым выходом первого триггера, входы синхронизации первого, второго и третьегорегистров сдвига соединены с четвертым выходом блока управления, пятый выход которого соединен с вторым входом четвертого .элемента И, шестой выход блока управления соединен с вторыми входами второго и пятого элементов И и входом сброса схемы сравнения, седьмой выход блока управления соединен с входами записи первого и второго регистров сдвига, восьмой выход блока управления соединенс входами ввода данных второго и записи третьего регистров сдвига ивторым входом второго элемента КПИ,входы ввода данных первого и третьего регистров сдвига соединены с входом нулевого потенциала устройства,вход задания режима которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом первого.элемента ИЛИ, выход третьего регистрасдвига соединен с первым входом шестого элемента И и вторым входом третьего триггера, инверсный выход ко-,торого соединен через втсрои элемент задержки с вторым входом шестого эле 45мента И, выход которого соединен свторым входом третьего элемента ИЛИ,Причем блок управления содержит генератор импульсов, распределитель импульсов, элемент НЕ, элемент ИЛИНЕ, элемент И, ключ, генератор одиночных импульсов, коммутатор, триггер и элемент ИЛИ, причем выход генератора импульсов соединен с входом распределителя импульсов и через элемент НЕ - с первыми входами элементов ИЛИ-НЕ и И, вторые входы которых соединены соответственно с первым и вторым выходами распределителя импульсов, выходы которого соеди". иены с первым выходом блока управления, первый выход распределителяимпульсов подключен к первому входу элемента ИЛИ, выход элемента И соединен с первыми входами триггера игенератора одиночных импульсов, второй вход и выход которого соединенысоответственно с выходом ключа иинформационным входом коммутатора,управляющий вход которого являетсявходом задания режима блока управления, управляющий и информационныйвходы ключа соединены соответственно с входом начального запуска и входомнулевого потенциала блока управления,первый выход коммутатора соединенс вторым входом триггера, выход которого соединен с вторым входом элемента ИЛИ, выходы с второго по восьмой блока управления соединены соответственно с выходом элемента ИЛИНЕ, вторым выходом коммутатора,выходом генератора импульсов, выходом элемента И, первым выходом распределителя импульсов, выходом элемента ИЛИ и выхоцом триггера.На фиг. 1 представлена блок-схема устройства; на фиг, 2 - блок-схема блока управления и регистра аргумента; на фиг. 3 - поясняющие работу устройства диаграммы.Устройство для вычисления экспоненциальной функции содержит регистры 1-3 сдвига, сумматор 4, триггеры5-7, блок 8 управления, регистр 9аргумента, схему 10 сравнения, элементы И 11-16 элементы ИЛИ 17-19,элементы 20 и 21 задержкии коммутатор 22,Блок управления содержит генератор 23 импульсов, распределитель 24импульсов, генератор 25 одиночных импульсов, ключ 26, коммутатор 27,триггер 28, элемент ИЛИ 29, элементИЛИ-НЕ 30, элемент И 31, элементНЕ 32, выходы 33-39 блока управления.Регистр аргумента содержит коммутатор 40 элемент ИЛИ 41 и выходрегистра 42,Устройство для вычисления экспоненциальной функции работает следующим образом.Генератор 23 тактовых импульсов блока 8 управления вырабатывает последовательность импульсов, пз кото 1057944рых распределитель 24 импульсов на и каналов (где и " количество разря" дов регистров 1-3 сдвига) формирует и последовательностей импульсов длилтельностью (=(где Г - тактовая чал стота генератора 23) с периодом Т=пь и сдвинутых друг относительно друга на время (лС помощью коммутатора 40, который может быть выполнен в виде п"разряд ного клавишного переключателя, набирают дополнительный двоичный код отрицательного значения аргумента дпя вычисления экспоненциальной функции либо прямой двоичный код положительного значения аргумента цля вычисления логарифмической функции. Коммутатор 40 подключает в единичных разрядах соответствующие выходы распределителя 24 импульсов к входам 20 элемента ИЛИ 41, на выходе которого формируется последовательный и"разрядный двоичный код набранного значения аргумента.В исходном состоянии коммутатором 27 блока 8 управления подключают выход генератора 25 одиночных импульсов к второму входу триггера 28. Затем с помощью ключа 26 запускают генератор 25 одиночных импульсов, 30 на вход которого поступает последовательность импульсов с выхода элемента И 31, которая формируется из инвертированных элементом НЕ 32 тактовых импульсов и сигналов и 1 го 3 выхода распределителя 24 импульсов,Выходной сигнал генератора 25 одиночных импульсов устанавливает .триггер 28 в единичное состояние,40 в котором он находится до следующего импульса, действующего на выходе элемента И 3. Единичный сигнал прямого выхода триггера 28 поступает по шине 39 ва восьмой выход блока 8 управления и далее на вход вво 45 да данных регистра 2 сдвига, вход .записи регистра 3 сдвига и через элемент ИЛИ 18 на второй вход триггера 5, сбрасывая его в нулевое состояние. Одновременно единичный сигнал триггера 28 через элемент ИЛИ 29 поступает по шине 38 наседьмой выход блока 8 управления и далее на входы записи регистров 1 и 2 сдвига, Так как входы ввода данных регистров 55 1 и 3 сдвига соединены с шиной логического нуля, то под действием тактовых импульсов четвертого ныхода блока 8 управления в разряды регистров 1 и 3 сдвига записываются нулевые коды. Поскольку на вход ввода данных регистра 2 сдвига поступает единичный сигнал в течение п тактов с седьмого выхода блока 8 управления, то под действием тактовых импульсов четвертого выхода блока 8 управления во все разряды регистра 2 сдвига записываются единичные коды. В процессе сдвига с выходов регистров 2 и 3 информации, сформированного в результате предшествующей работы уст" ройства, триггеры 6 и 7 устанавли" ваются в нулевое состояние, так как элементы И 12 и 15 блокированы нулевыми сигналами выхода переноса сумматора 4 и прямого выхода триггера 5 соответственно.Таким образом, в исходном состояф нии в регистрах 1 и 3 сдвига во всех разрядах содержится нулевой код, а в регистре 2 сдвига во всех разрядах единичный код, кроме старшего п-го, так как после сброса триггера 28 на входе ввода данных регистра 2 сдвига действует нулевой сигнал, а на вход записи регистра 2 сдвига в каждом и-ом такте через элемент ИЛИ 29 поступает единичный сигнал и-го выхода распределителя 24 импульсов. По этой же причине в и-ом разряде кода, формируемого в процессе вычислений в регистре .1 сдвига, всегда записан ноль.После установки устройства в исходное состояние коммутатором 27 подключают выход генератора 25 одиночных импульсов к шине 34, которая соединена с первым входом триггера 5. Затем коммутатором 22 устанавливают режим работы устройства. Коммутатор 22 подключает второй информационный вход блока 10 сравнения к выходу элемента ИЛИ. 9 в режиме вычисления экспоненциальной функции либо к выходу элемента ИЛИ 17 в режиме вычисления логарифмической функции.В режиме вычисления функции у=е " от начальных условий уо=1, хо=О в регистрах 2 и 3 сдвига формируются двоичные коды функции и аргумента соответственно. В режиме вычисления функции у=Ьх от начальных условий у=О, х( =1 двоичные кодь( функции и аргумента формируются в регистрах 3 и 2 сдвига соответственно,Работа устройства в режимах вычисле ния экспоненциальной и логарифмической функций аналогична.Запуск процесса вычислений осуществляется кнопочным переключате лем, который запускает генератор 25 одиночных импульсов блока 8 управ ления. Выходной импульс генератора 25 одиночных импульсов поступает с третьего выхода блока 8 управления О на первый вход триггера 5, устанавливая его в единичное состояние, в котором сигнал прямого выхода триггера. 5 снимает блокировку элементов И 1 и 15, 5После установки триггера 5 в единичное состояние первый импульс последовательности, синхронизирующей и-е такты работы устройства, поступает с шестого выхода блока 8 уп равления через элемент И 15 на пер" вый вход триггера 7 и устанавливает его в единичное состояние,в котором он находится и тактов, так как с выхода регистра 3. сдвигаются нуле вые сигналы. Единичный сигнал прямого выхода триггера 7 через элемент ИЛИ 19 поступает на информационный вход регистра 3 сдвига, во все разряды которого под действием тактовых 30 импульсов записываются единичные коды, что соответствует дополнительному коду единицы младшего разряда.1Второй импульс последовательности шестого выхода блока 8 управления, 35 поддерживает триггер 7 в единичном состоянии в течение .очередного и-го такта, что обеспечивает запись в и-й разряд кода регистра 3 сдвига единичного сигнала отрицательного 40 знака. В следующем такте единичный сигнал первого разряда кода, сдвигаемого, с выхода регистра 3, сбрасывает триггер 7 в нулевое состояние. Элемент 21 задержки на такт поддер живает на выходе в течение этого так та нулевой сигнал инверсного выхода триггера 7 его предыдущего состояния, что обеспечивает блокировку элемента И 6 и стирание единицы в 50 первом разряде кода, сдвигаемого с выхода регистра 3 сдвига, так как на первом и втором входах элемента ИЛИ 19 действуют нулевые сигналы выхода элемента И 16 и прямого выхо да триггера 7. К моменту сдвига с выхода регистра 3 второго разряда ко;. да на выходе элемента 21 задержки устанавливается единичный сигнал, который снимает блокировку элемента И 16, что обеспечивает подключе" ние выхода регистра 3 сдвига к его информационному входу через элементы И 16 и ИЛИ 19. Таким образом, после второго шага вычислений в ре-. гистре 3 сдвига формируется дополнительный двоичный код 11110,.На последующих шагах в регистре 3 сдвига формируется аналогичным образом дополнительный двоичный код отрицательного значения аргумента экспоненциальной функции или отрицательного значения логарифмической функции,Рассмотрим процесс формирования кодов в регистрах 1 и 2 сдвига с момента установки триггера 5 в единичное состояние. В это время единич" ный сигнал инверсного выхода триггера 6 через элемент 20 задержки на такт действует на втором входе элемента И 13, а на первом входе элемента ИЛИ 17 действует нулевой сигнал прямого выхода триггера 6. Начальный двоичный код 01 11 сдвигается с выхода регистра 2 через элемент И 13, ИЛИ 17 и И 11 на второй вход сумматора 4 и с его первого выхода суммы поступает на информационный вход регистра 1 сдвига и записывается в него на время и тактов под действием тактовых импульсов четвертого выхода блока 8 управления, В следующие и тактов (на втором шаге вычислений) на первый вход сумматора 4 с выхода регистрасдвигается двоичный код 0111,,1, а на второй вход сумматора ч поступает с выхода регистра 3 сдвига через элементы И 13, 1 ЛИ 17 и И 11 такой же двоичный код 01111, В результате суммирования последовательным двоичным сумматором 4 на его втором выходе формируется сигнал переноса в и-й разряд, который приводит к срабатыванию элемента И 12 в момент и"го такта, Триггер 6 устанавливается в единичное состояние и поддерживается в нем в течение и-го такта, В это время на входе записи регистров 1 и 2 сдвига действует импульс п-го такта с седьмого выхода блока 8 управления, который блокирует запись .единичного сигнала в и-е разряды кодов регистрови 2 сдвига. Триггер 6 сбрасывается в нулевое состояние единичным сигналом перво 1057944го разряда кода, сдвигаемого с выхода регистра 2. Элемент 20 задержки на такт поддерживает на выходе в течение такта нулевой сигнал инверсного выхода триггера 6 его предыдущего состояния, что обеспечивает блокировку элемента И 13 во время сдвига первого разряда кода с выхода регистра 2 сдвига, На нервом и втором входах элемента ИЛИ 17 действу- О ют нулевые сигналы прямого выхода триггера 6 и выхода элемента И 13 соответственно, Нулевой сигнал выхода элемента ИЛИ 17 обеспечивает запись нуля в первом разряде кода, 15 сдвигаемого в регистре 2, К моменту сдвига с выхода регистра 2 второго разряда кода на выходе элемента 20 задержки устанавливается единичный сигнал, который открывает элемент 20 И 13. Таким образом, остальные разряды кода, начиная с второго разряда поступают с выхода регистра 2 сдвига на его информационный вход через элементы И 13 и ИЛИ 17 без 25 изменения. В регистр 2 сдвига записывается двоичный код 0111,10, который также с выхода элемента ИЛИ 17 через элемент И 11 поступает на нторой вход сумматора 4, на первый вход которого сдвигается содержимое регистра 1 сдвига, Дальнейшие вычисления выполняются аналогичным образом, причем за время и тактов производится каждый последующий шаг вычислений.В режиме вычисления экспоненциальной Функции вычисление выполняется до тех пор пока на выходе элемента ИЛИ 19 не сформируется дополнительный последовательный двоичный код аргумента, который равен заданномуна коммутаторе 40 задатчика 9 значению аргумента. В этом случае срабатывает блок 10 сравнения, на выходе которого Формируется единичный сигнал,открывающий элемент И 14. Импульсныйсигнал пятого выхода блока 8 управления проходит через элементы И 14 иИЛИ 18 на второй вход триггера 5 исбрасывает его в нулевое состояние,в котором сигнал его прямого входаблокирует элементы И 11 и 15. В регистрах 2 и 3 сдвига фиксируются динамическим способом двоичный кодэкспоненциальной функции и дополнительный код отрицательного значенияаргумента,В режиме вычисления логарифмической функции вычисления выполняются до тех пор, пока на выходе элемеита ИЛИ 17 не сформируется двоичныйкод аргумента, который равен заданному на задатчике 9 значению аргумента. В этом случае аналогичнымобразом срабатывает. блок 10 сравнения, триггер 5 сбрасывается в нулевое состояние, элементы И 11 и 5блокируются сигналом прямого выходатриггера 5, а в регистрах 3 и 2 сдвига фиксируются динамическим способомдополнительный код отрицательногозначения логарифмической функциии прямой код положительного значенияаргумента соответственно.На Фиг, 3 приведена временнаядиаграмма для случая вычисления логарифмической Функции при п=4. Положительный уровень соответствует единичному значению сигнала. Заданноезначение аргумента равно 0.100, гдеточкой отделен знаковый разряд.

СмотретьЗаявка

3412196, 24.03.1982

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, функции, экспоненциальной

Опубликовано: 30.11.1983

Код ссылки

<a href="https://patents.su/9-1057944-ustrojjstvo-dlya-vychisleniya-ehksponencialnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления экспоненциальной функции</a>

Предыдущий патент: Устройство для возведения в квадрат импульсных сигналов

Следующий патент: Генератор случайных чисел

Случайный патент: Волноводный аттенюатор