Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

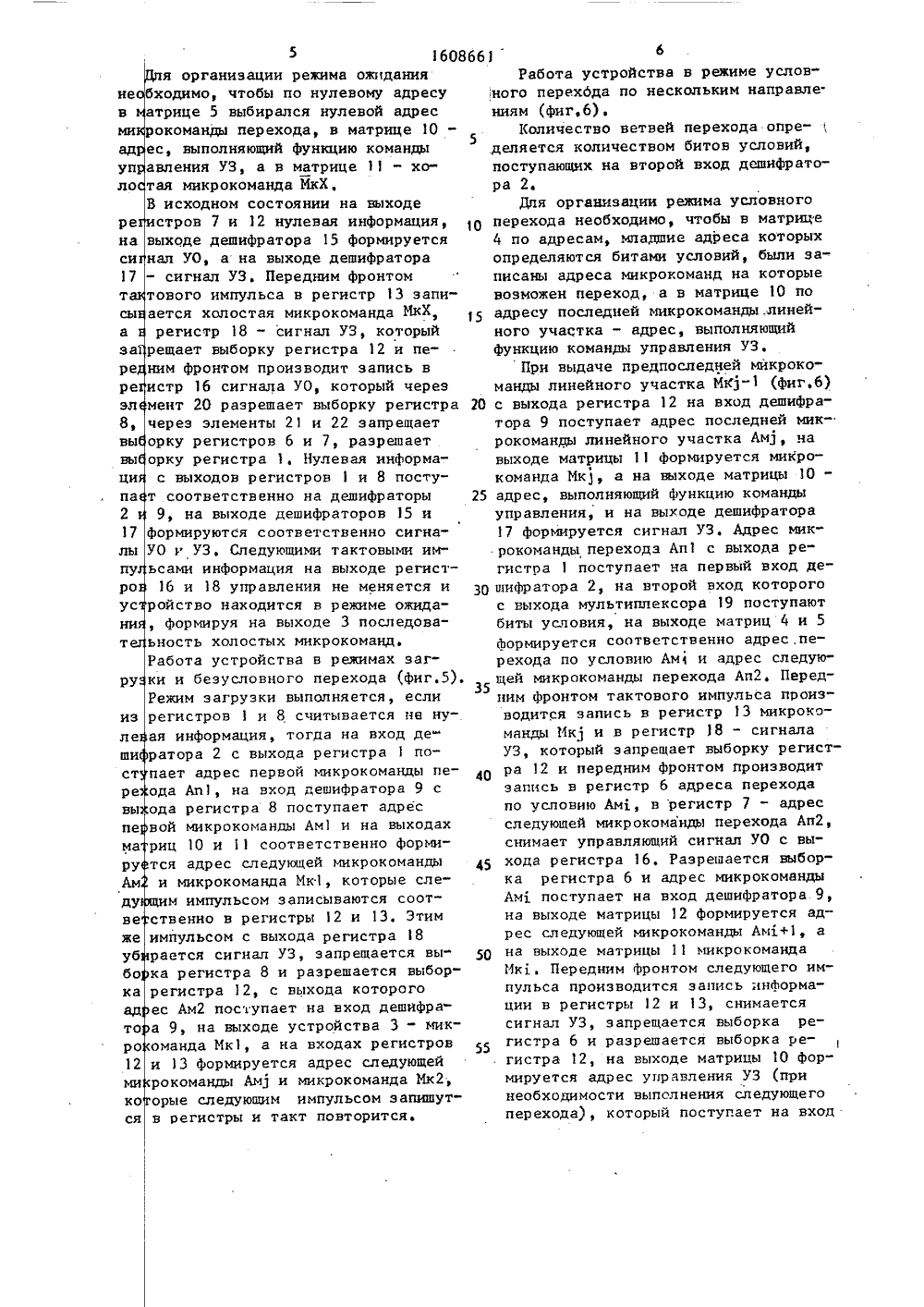

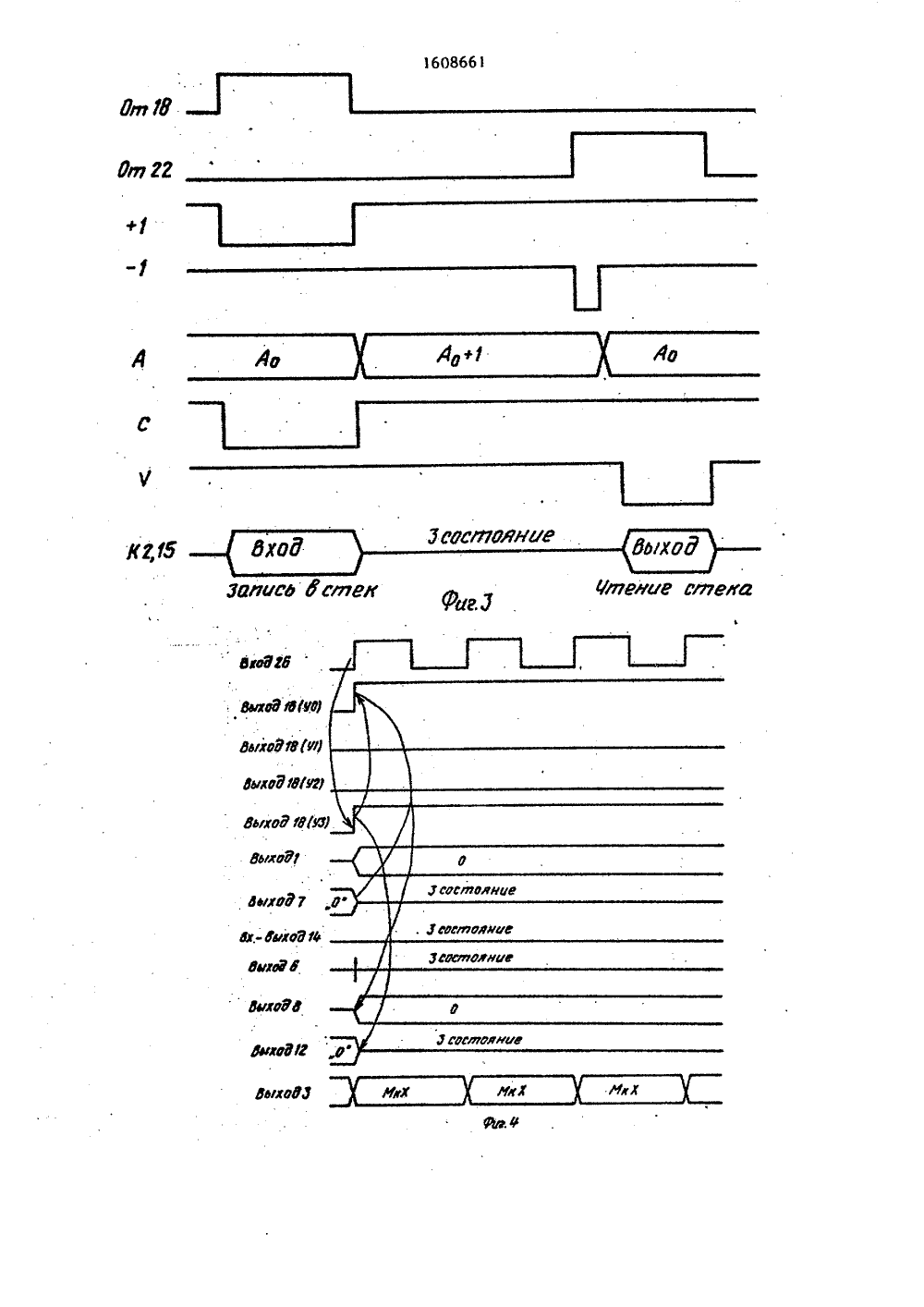

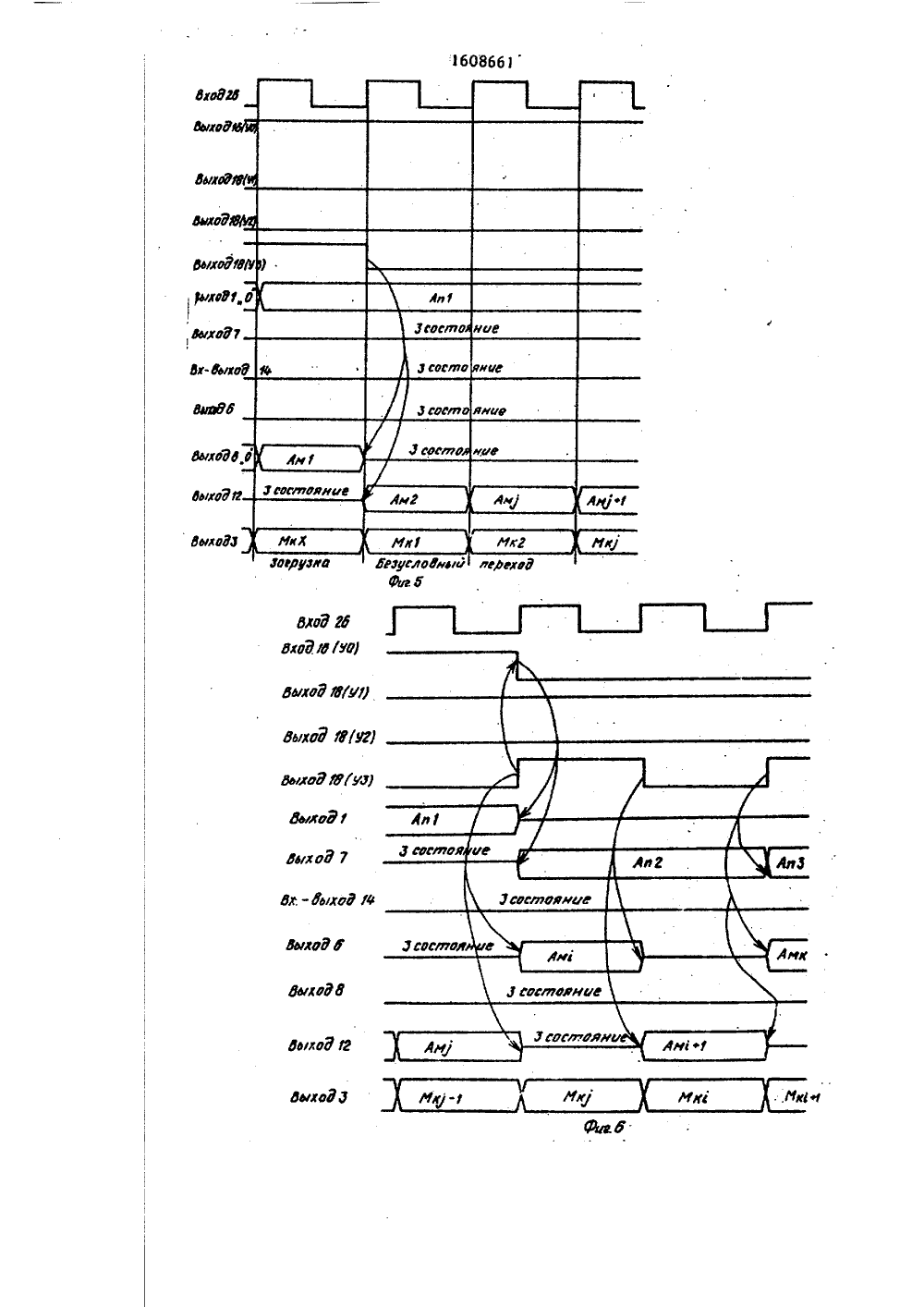

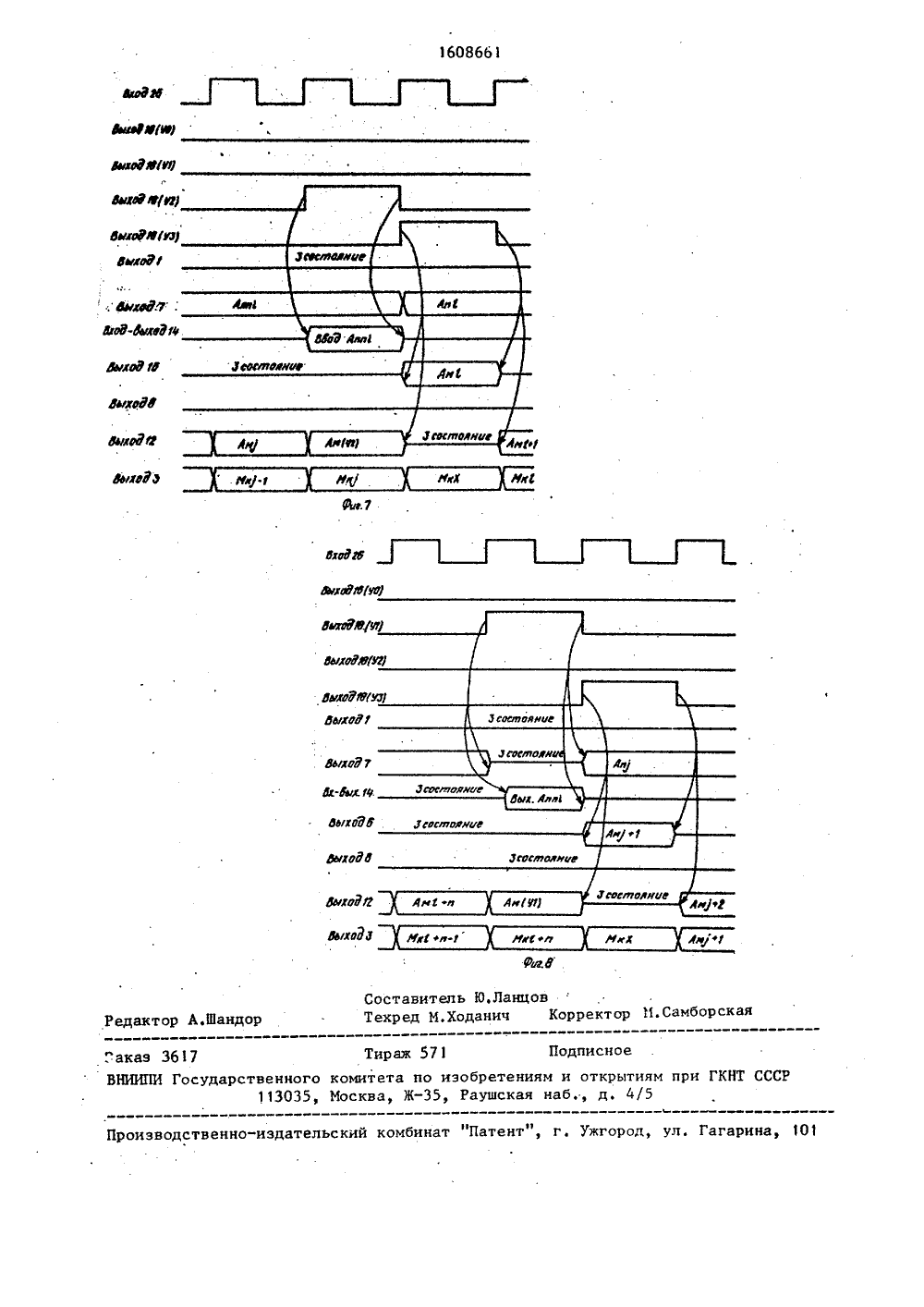

1) 4627923)24-242) 28.12,886) 23,11.90. Бюл, У 432) З.П.Вербицкий, А,А,МазуП.О,Симкив3) 681.32(088.8)6) Авторское свидетельство1117637, кл. С 06 Р 9/22,Еол. сов В.Г, и др. Проеке узлов и систем автоматикслительной техники. - Л,:омиздат, 1983, с,49-51, ри4) УСТРОЙСТВО МИКРОПРОГРАК"ВЛЕ 1 ПЬЧ У ССС 983 ваи вы- нерго 2-20 НОГО У ке и может быпрограммных учислительных ь использовано в тройствах управл ашин, Цель изобр аппаратных затр и е- и уменьшени 7) Изобретение относится к цифрой вычислительной технике и автома-. расширение области грименения, Дляэтого устройство микропрограммногоуправления содержит первый регистрадреса 1, первый дешифратор адреса 2,запоминающую матрицу 4 стандартныхпереходов, первую запоминающую матри-,цу переходов 5, регистр 6 стандартного перехода, первый регистр перехода7, второй регистр адреса 8, второйдешифратор адреса 9, вторую запоминающую матрицу переходов 10, запоминающую матрицу 11 микроопераций, второй регистр перехода 12, регистр 13микрокоманд, стековую память 14, первый дешифратор управления 15, первыйрегистр управления 16, второй дешифратор управления 17, второй региструправления 18, мультиплексор 19, псрвый 20 и второй 21 элементы И и элемент ИЛИ-ИГ 22. 8 ил.Изобретение относится к цифровойвычислительной технике и автоматикеи может быть использовано в микропрограммных устройствах управлениям5вычислительных машин.Целью изобретения является уменьшение аппаратных затрат и расширениеобласти применения за счет реализации возможности анализа логическихусловий.На Фиг,1 приведена Функциональнаясхема устройства; на фиг.2 - функциональная схема стека; на Фиг.З. - временная диаграмма работы. стека; нафиг.4 - временная диаграмма работыустройства в режиме ожйдания; наФиг,5 в . временная диаграмма загрузкии безусловного перехода; на Фиг,б -временная диаграмма условного, .перехода по нескольким направлениям; нафиг.7 - временная диаграмма переходана микроподпрограмму; на Фиг,8 - временная диаграмма возврата из микроподпрограммы. 25Устройство микропрограммного управления содержит первый регистр 1,адреса, первый дешифратор 2 адреса,выход 3, запоминающую матрицу 4 стандартных переходов, первую запоминающую матрицу 5 переходов, регистр 6.стандартного перехода, первый регистр7 перехода, второй регистр 8 адреса,второй дешифратор 9 адреса, вторуюзапоминающую матрицу 1 О переходов,запоминающую матрицу 11 микроопераций, второй регистр 12 перехода, регистр 13 микрокоманд, стековую память 14, первый дешифратор 15 управления, первый регистр 16 управления,40второй дешифратор 17 управления, второй регистр 18 управления, мульти-.плексор 19, первый 20 и второй 21элементы И, элемент ИЛИ-НЕ 22, первый 23 и второй 24 входы кода команды, вход 25 логических условий и тактовый вход 26,Стековая память (фиг.2) содержитформирователь 27 импульсов, реверсивный счетчик 28, блок 29 регистров,элемент 30 задержки и элемент НЕ 31.50Устройство представляет собойдвухуровневое устройство микропро-,граммного управления, в каждом уровне которого используется метод принудительной адресации, конвейерностьпри формировании адресов и управляющих команд. В устройстве используется раздельная адресация микрокоманд,микрокоманд перехода в первом уровне,микрокоманд линейных участков во втором уровне.В первом уровне матрица 4 и регистр 6 служат для формирования адреса перехода (возврата) к микроподпрограммам, матрица 5 и регистр 7 служатдля формирования следующего адресамикрокоманды перехода, В поле адресовмикрокоманд перехода выделен нулевойадрес, выполняющий функцию командыуправления, при формировании которогона выходе дешифратора 15 возникаетуправляющий сигнал (УО), который осуществляет загрузку адресов и регистров 1 и 8 адреса,Во втором уровне матрица 10 и регистр 12 служат для формирования адреса следующей микрокоманды, матрица11 и регистр 13 - для формированиясамой микрокоманды, В поле адресовмикрокоманд выделены три адреса, выполняющие функцию команд управления,при Формировании которых на выходедешифратора 17 появляются управляющие сигналы. Первый сигнал (У 1) производит запись в стек адреса микро-команды перехода, второй (У 2) производит чтение из стека адреса микрокоманды перехода, третий (УЗ) осуществляет переход на новую ветвь микропрограммы.Иультиплексор 19 имеет два управляющих входа, при подаче сигнала ло"гической единицы на первый управляющий вход на выходе появляется нулеваяинформация, при подаче сигнала логической единицы на второй управляющийвход на выходе появляется единица,при подаче .логических нулей на обауправляющих входа на выходе - битыусловий. Регистры и стековая память имеютдва управляющих входа, по входу Спроизводится запись информации по переднему фронту управляющего импульса,по входу 7 логической единицей производится выборка регистра (стека),а логическим нулем установка выходовв высокоимпедансное состояние,Устройство работает в следующихрежимах: ожидания, загрузки, безусловного перехода, условного переходапо нескольким направлениям, вызовамикроподпрограммы.Работа устройства в режиме ожида"ния (фиг.4).5 1608661я организации режима ожиданиябходимо, чтобы по нулевому адресуатрице 5 выбирался нулевой адресрокоманды перехода, в матрице 10 -ес, выполняющий функцию командыавления УЗ, а в матрице 11 - хотая микрокоманда ИкХ,В исходном состоянии на выходестров 7 и 12 нулевая информация,выходе дешифратора 15 формируетсянап УО, а на выходе дешифраторасигнал УЗ. Передним фронтомтового импульса в регистр 13 запиается холостая микрокоманда МкХ,регистр 18 " сигнал УЗ, которыйрешает выборку регистра 12 и пеним фронтом производит запись вистр 16 сигнала УО, который черезмент 20 разрешает выборку регистрачерез элементы 21 и 22 запрещаеторку регистров 6 и 7, разрешаеторку регистра 1, Нулевая информас выходов регистров 1 и 8 постут соответственно на дешифраторы9, на выходе дешифраторов 15 иформируются соответственно сигнаУО и УЗ. Следующими тактовыми имьсами информация на выходе регист 16 и 18 управления не меняется иройство находится в режиме ожидаформируя на выходе 3 последова"ьность холостых микрокоманд.Работа устройства в режимах загки и безусловного перехода (фиг.5),Режим загрузки выполняется, еслирегистров 1 и 8 считывается не нуая информация, тогда на вход дератора 2 с выхода регистрапопает адрес первой микрокоманды пеода Ап 1, на вход девифратора 9 сода регистра 8 поступает адресвой микрокоманды Ам 1 и на выходахриц 10 и 11 соответственно формится адрес следующей микрокомандыи микрокоманда Мк 1, которые слем импульсом записываются соотственно в регистры 12 и 13, Этимимпульсом с выхода регистра 18рается сигнал УЗ, запрещается вы"ка регистра 8 и разрешается выборрегистра 12, с выхода которогоес Ам 2 поступает на вход дешифраа 9, на выходе устройства 3 - микоманда Мк 1, а на входах регистрови 13 Формируется адрес следующейрокоманды Ам и микрокоманда Мк 2,орые следующим импульсом эапишутв регистры и такт повторится. не ад уп ло ре на си 17 т а за ре ре эл 8, вы ци па 2 17 лы пу ро ус РУ из ле ст ре вы пе ма РУ Ам ду ве же уб бо ка ад то ро 12 ко ся Работа устройства в режиме услов"ного перехбда по нескольким направлениям (Фиг,б).51(оличество ветвей перехода опре.деляется количеством битов условий,поступающих на второй вход дешифратора 2,Для организации режима условногоперехода необходимо, чтобы в матрице4 по адресам, младшие адреса которыхопределяются битами условий, были записаны адреса микрокоманд на которыевозможен переход, а в матрице 10 по15 адресу последней микрокоманды .линейного участка - адрес, выполняющийфункцию команды управления УЗ.При выдаче предпоследней микрокоманды линейного участка М 4-1 (Фиг,б)20 с выхода регистра 12 на вход дешифратора 9 поступает адрес последней микрокоманцы линейного участка АмЗ, навыходе матрицы 11 формируется микрокоманда Мк, а на выходе матрицы О 25 адрес, выполняющий Функцию командыуправления, и на выходе дешифратора17 формируется сигнал УЗ. Адрес мик"рокоманды перехода Ап с выхода ре"гистра 1 поступает на первый вход де 30 шифратора 2, на второй вход которогос выхода мультиплексора 19 поступаютбиты условия, на выходе матриц 4 и 5формируется соответственно адрес,перехода по условию Ам 1 и адрес следую 35щей микрокоманды перехода Ап 2, Передним Фронтом тактового импульса производится запись в регистр 13 микрокоманды Ик и в регистр 18 - сигналаУЗ, который запрещает выборку регист 40 ра 12 и передним фронтом производитзапись в регистр 6 адреса переходапо условию Амд, в регистр 7 - адресследующей микрокоманды перехода Ап 2,снимает управляющий сигнал УО с выхода регистра 16. Разрешается выборка регистра б и адрес микрокомандыАм 1. поступает на вход дешифратора 9,на выходе матрицы 12 формируется адрес следующей микрокоманды Амд+1, а50 на выходе матрицы 11 микрокомандаИк 1. Передним фронтом следующего импульса производится запись информации в регистры 12 и 13, снимаетсясигнал УЗ, запрещается выборка регистра 6 и раэрепается выборка регистра 12, на выходе матрицы 10 формируется адрес управления УЗ (принеобходимости выполнения следующегоперехода), который поступает на входдешифратора 17,. и в следующем такте появляется управляющий сигнал УЗ, по которому происходит следующий переход по условию.Для организации перехода на микро- подпрограмму и возврата из нее в поле матрицы 5 для каждой микроподпрограммы выделен адрес Апп и адреса перехода на микроподпрограмму и возврата из нее записаны в матрице 4 соответственно по адресам, старшая часть которых Апп 1, а младшая 1 либо О,Работа устройства в режиме перехода на микроподпрограмму (Фиг.7).Для организации перехода на микро- подпрограмму необходимо, чтобы по адресу последней микрокоманды линейного участка Ам 1 в матрице 1 О был записан адрес, выполняющий функцию коман ды управления У 2, по которому в матрице 10 записан адрес, выполняющий Функцию команды управления УЗ, а в матрице 11 " холостая микрокоманда.Передним Фронтом импульса в ре гистр 12 записывается адрес Ам 1 и на выходе дешифратора 17 формируется сигнал У 2. Передним фронтом следующего импульса в регистр 18 записы" вается сигнал У 2, который производит запись в стек адреса микроподпрограммы Аптп (фиг.3) и поступает на второй управляющий вход мультиплексора 19, на выходе которого появляется единица. На выходе матрицы 4 формируется адрес первой микрокоманды микроподпрограммы Ам 1, а н выходе матрицы 5 формируется адрес первой микрокоманды перехода микроподпрограммы Ап 1. В регистр 12 записывается адрес, вы полняющий Функцию команды У 2, поступающий на вход дешифратора 9, а на выходе матриц 11 и 10 формируются соответственно холостая микрокоманда ИкХ и адрес, выполняющий функпию ко манды УЗ, Передним фронтом следующего импульса в регистр 13 записывается холостая микрокоманда МкХ, а в регистр 18 - сигнал УЗ (снимается сигнал У 2) и далее осуществляется пе О реход на микроподпрограмму.Работа устройства в режиме возврата из микроподпрограммьГ(фиг,8) 1Для выполнения возврата из микроподпрограммл необходимо, чтобы по адресу последней микрокоманды микроподпрограммы управления У 1, по которому в матрице 10 был записан адрес, вы- полняющий функцию команды управления УЗ, а в матрице 11 " холостая микро" команда ИкХ.Передним фронтом импульса в регистр 12 записывается адрес последней микрокоманды микроподпрограммы Ам 1+п и на выходе дешифратора 17 формируется сигнал У 1, Передним фронтом следующего импульса в регистр 12 запи" сывается адрес, выполняющий функцию команды У 1, в регистр 13 - последняя микрокоманда микроподпрограммы Мк 1+и, в регистр 18 - сигнал У 1, который запрещает выборку регистра 7, поступает на первый управляющий вход мультиплексора 19, на выходе которого появляется нулевая информация, производит ,чтение стековой памяти 14, с выхода которого адрес микроподпрограммы поступает на первый вход дешифратора 2, на выходе матрицы 4 формируется адрес микрокоманды возврата Ам 1+1, а на выходе матрицы 5 - адрес следующей микрокоманды перехода Ап 1.Передним фронтом следующего импульса в регистр 13 записывается холостая микрокоманда МкХ, а в регистр 18 - сигнал УЗ (снимается сигнал У 2) и далее происходит переход на продолжение микроподпрограммы.Формула изобретения Устройство микропрограммного управления, содержащее первый и второй регистры адреса, первую и вторую запоминающие матрицы переходов, запоминающую матрицу стандартных переходов, регистр стандартного перехода, первый и второй регистры перехода, запоминающую матрицумикроопераций первый и второй дешифраторы адреса первый вход кода ко)манды устройства является информационным входом первого регистра адреса, выход которого соединен с первым входом дешифратора адреса, выходы которого соединены с входами первой запоминающей матрицы перехо" дов и запоминающей матрицы стандартных переходов, выход которой соединен с информационным входом регистра стандартного перехода, выход первой запоминающей матрицы переходов соединен с.информационным входом перво" го регистра перехода, второй вход кода команды устройства соединен с информационным входом второго регистра адреса, выход которого соединен с входом второго дешифратора адреса, выходы которого соединены с выходамиР р г э л с и д к Р д в апоминающей матрицы микроопераций и торой запоминающей матрицы перехо" ов, выход которой соединен с инфор" ационным входом второго регистра пе 5 ехода, о т л и ч а ю щ е е с я тем, то, с целью уменьшения аппаратурных атрат и расширения области применея за счет реализации воэможности налива логических условий, оно соержитстековую память, регистр микокоманд, первый и второй дешифрато-управления, первый и второй рестры управления, первый и второйементы И, элемент ИЛИ-НЕ и мультиексор, информационный вход которог соединен с входом логических усвий устройства, выход мультиплекра соединен с вторым входом первогоифратора адреса, первый управляюй вход мультиплексора соединен срвым входом элемента ИЛИ-НЕ, с вхом выборки стековой памяти и с пером выходом второго регистра управлея, второй выход которого соединен 25вторым управляющим входом мультиексора и с входом записи стековойти, информационный вход-выходторого соединен с выходом первогогистра перехода, с первым входом 3 ррвого дешифратора адреса и с вхом первого дешифратора управления,од которого соединен с информаонным входом первого регистра управлення, выход которого соединен свходом выборки первого регистра адреса с первым входом первого элемента И, с инверсным входом второго элемента И и с вторым входом элементаИЛИ-НЕ, выход первого элемента И соединен с входом выборки второго регистра адреса, выход элемента ИЛИ-НЕсоединен с входом выборки первого регистра перехода, выход второго элемента И соединен с входом выборкирегистра стандартного перехода, выход которого соединен с входом второго дешифратора адреса и выходомвторого регистра перехода, вход выборки которого соединен с входамизаписи первого регистра перехода нпервого реги тра управления, с вторым выходом первого н прямым входомвторого элементов И и с третьим выхо"дом втоРого регистра управления, информационный вход которого соединенс выходом второго дешифратора управления, вход которого соединен с выходом второй запоминающей матрицыперехода, тактовый вход устройствасоединен с входами записи второго регистра управления, второго регистраперехода и регистра микрокоманд, информационный вход которого соединенс выходом запоминающей матрицы микроопераций, а выход является выходомустройства.1608661 Рву 22 215 од дюЮ ЬЭФ и) дыпЮФЖ ыход ФМЬгхюдр Ж- АаИ ФФЮюааУФ дихИ Галиа Успею." акаВНИИПИ ного комитета035, Москва,ри ГКНТ СС открытия д. 4/5 о изобретениям 35, Раушская н осударств 1

СмотретьЗаявка

4627923, 28.12.1988

ПРЕДПРИЯТИЕ ПЯ В-2667

ВЕРБИЦКИЙ ВИКТОР ПАВЛОВИЧ, МАЗУРУК АЛЕКСАНДР АНТОНОВИЧ, СИМКИВ ПАВЕЛ ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.11.1990

Код ссылки

<a href="https://patents.su/8-1608661-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для вычисления позиционных характеристик модулярного кода

Следующий патент: Многоканальное устройство переменного приоритета

Случайный патент: Полупроводниковый стабилизатор напряжения