Способ определения сопротивления изоляции электрических сетей и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

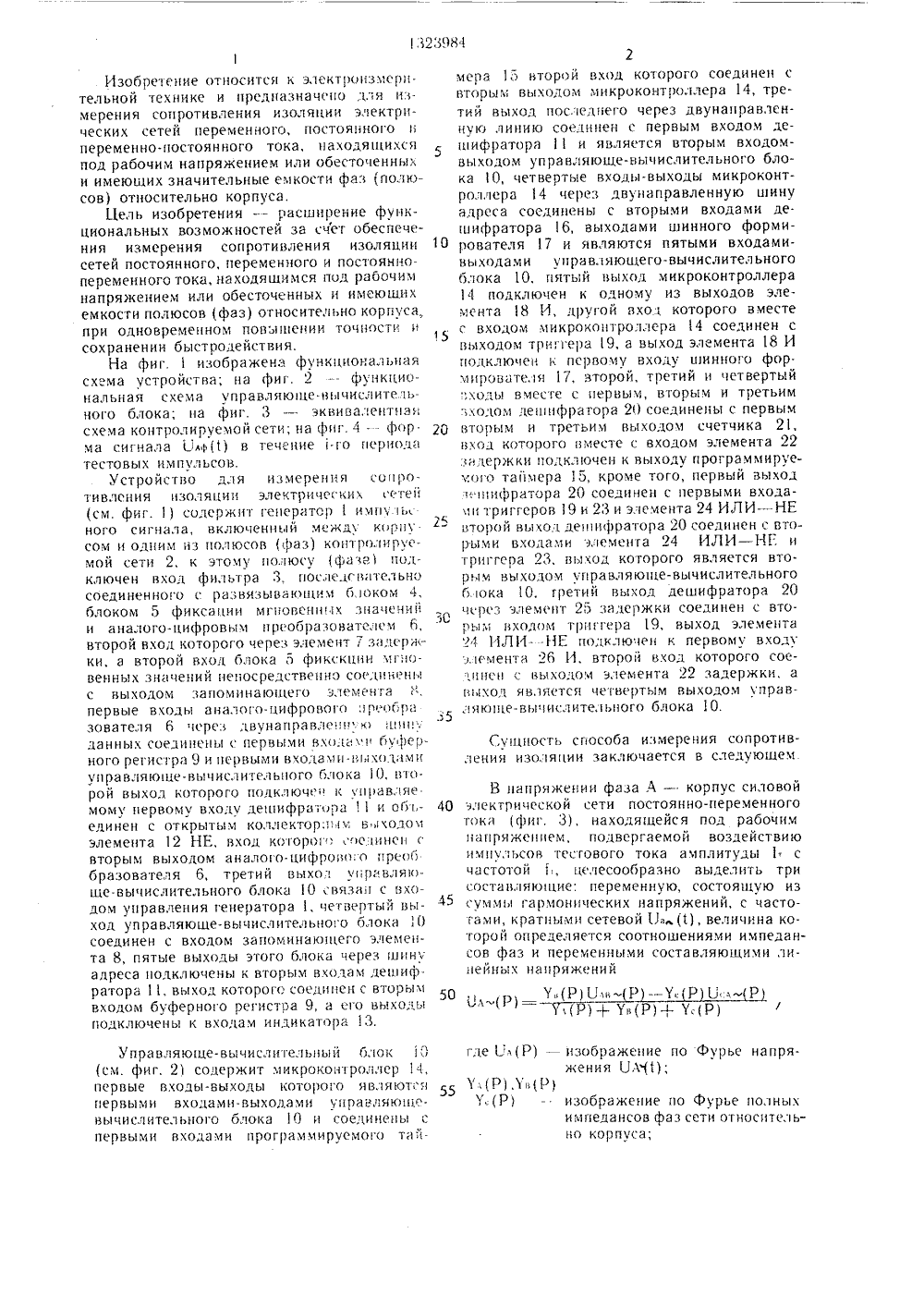

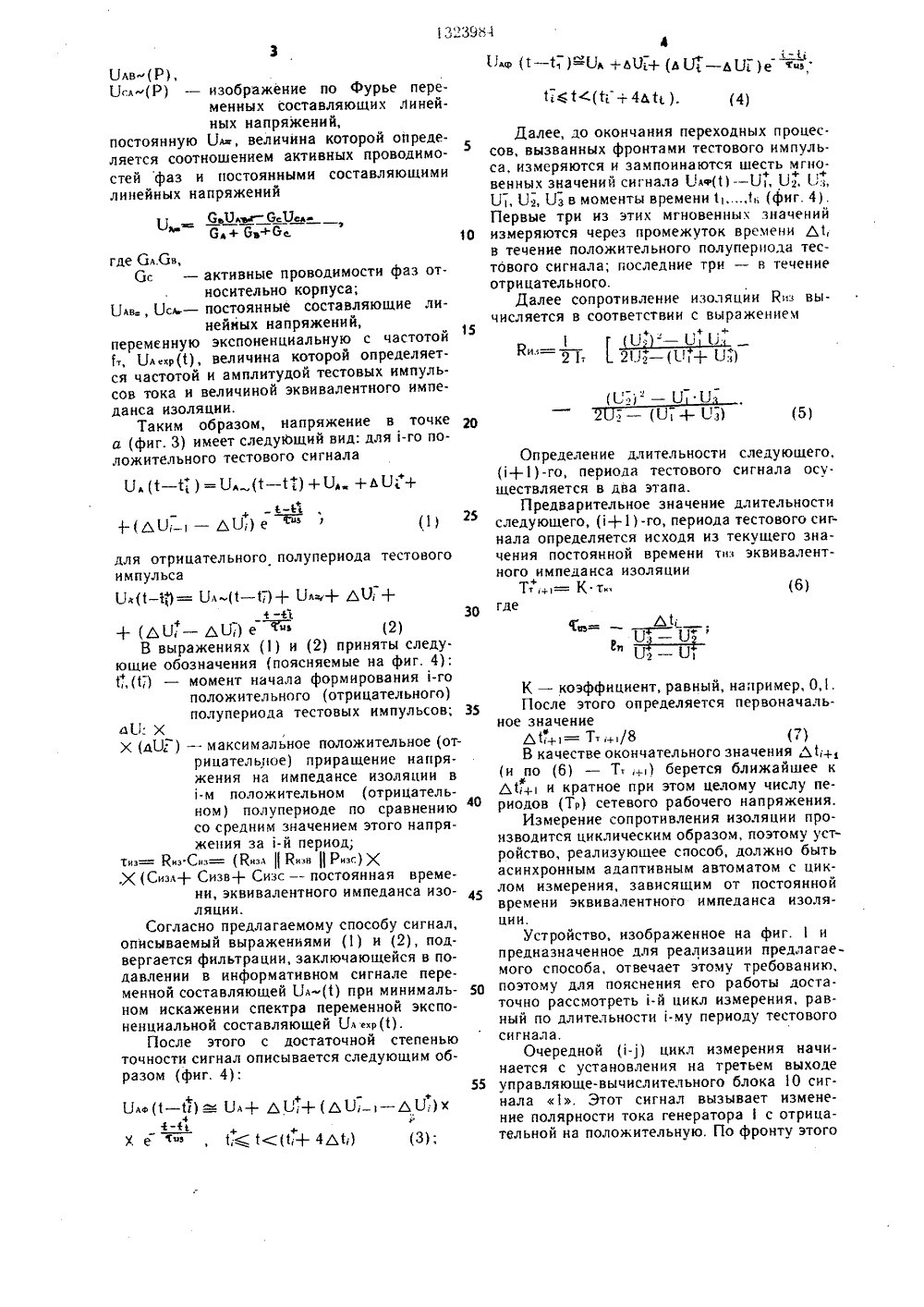

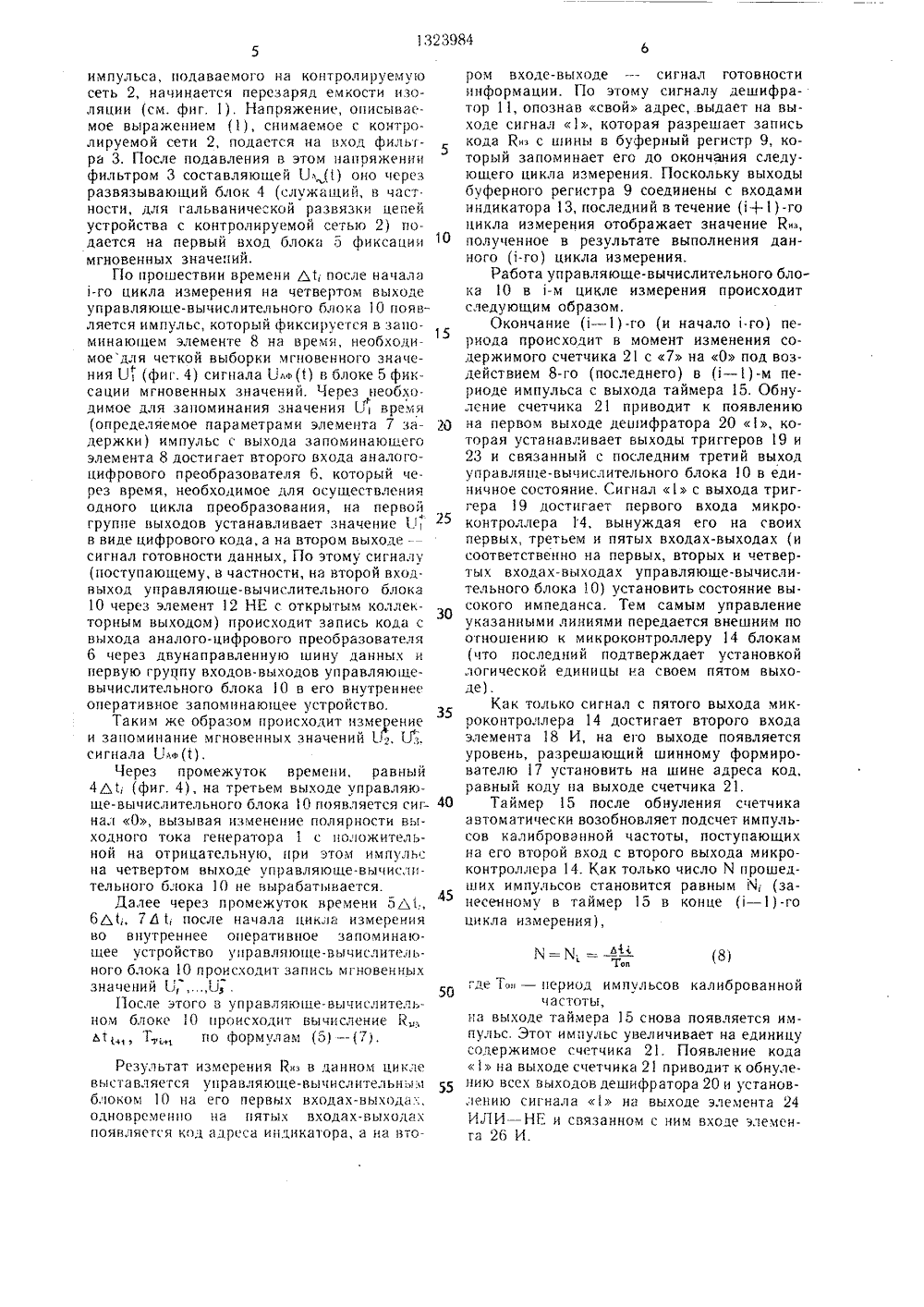

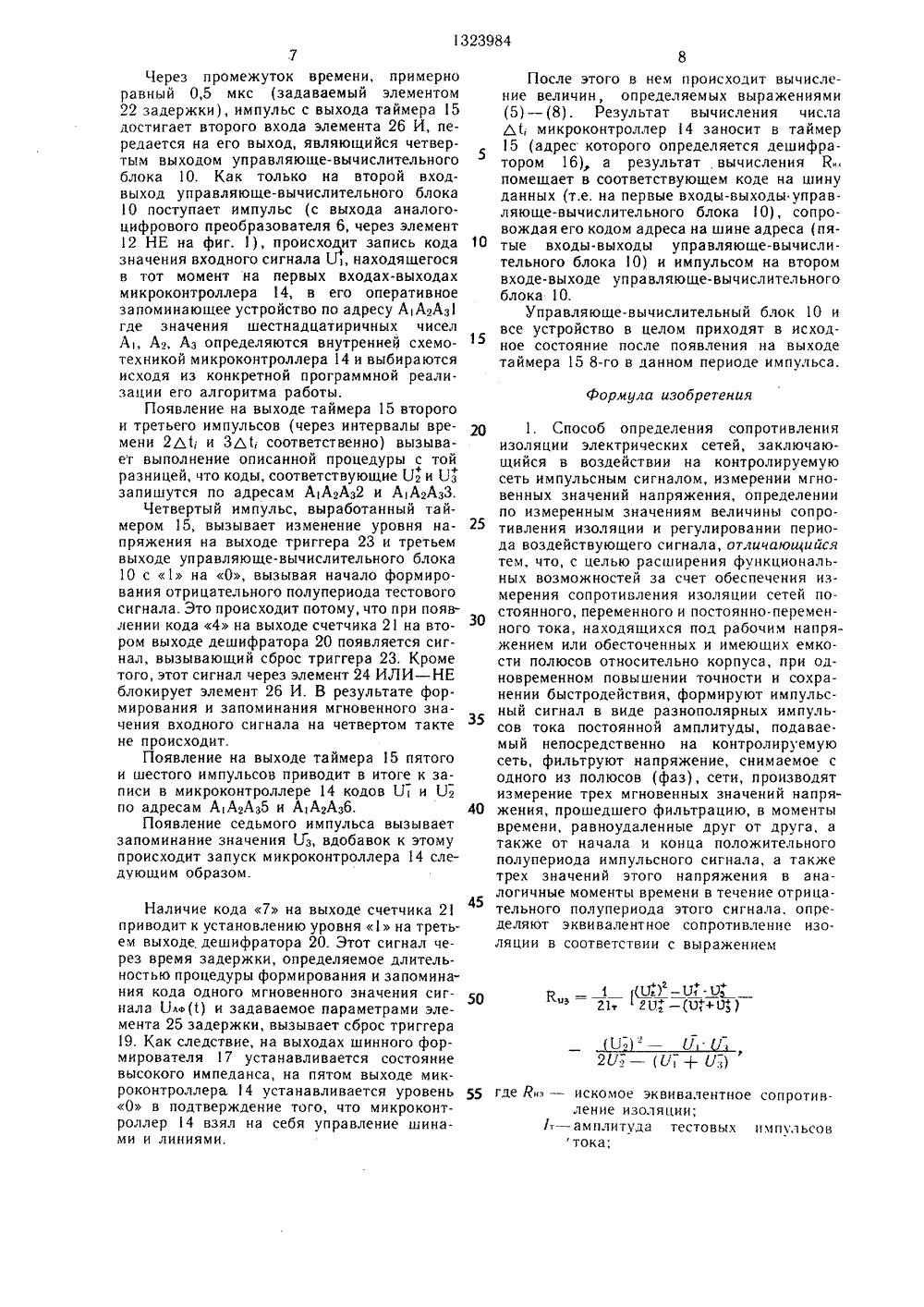

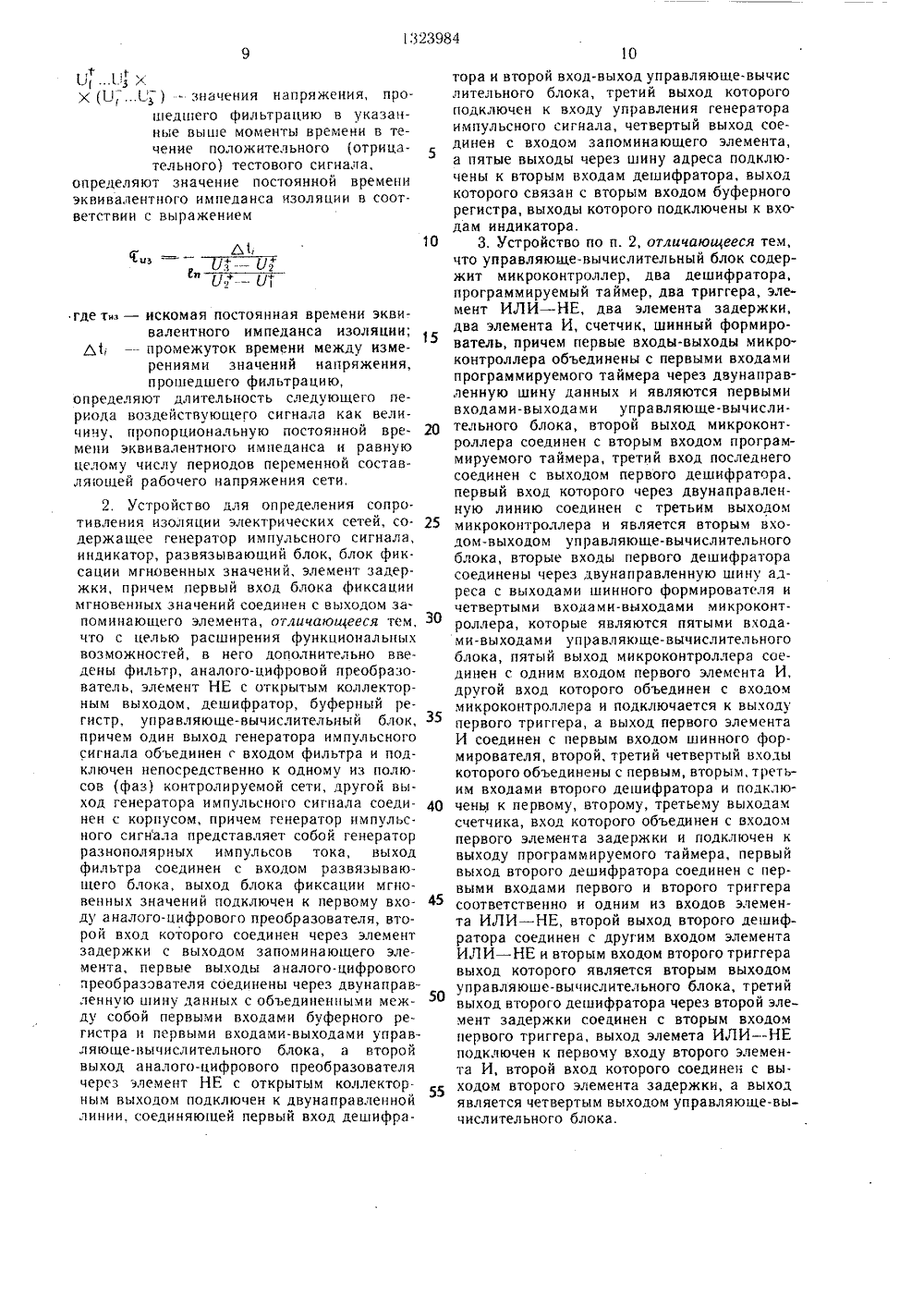

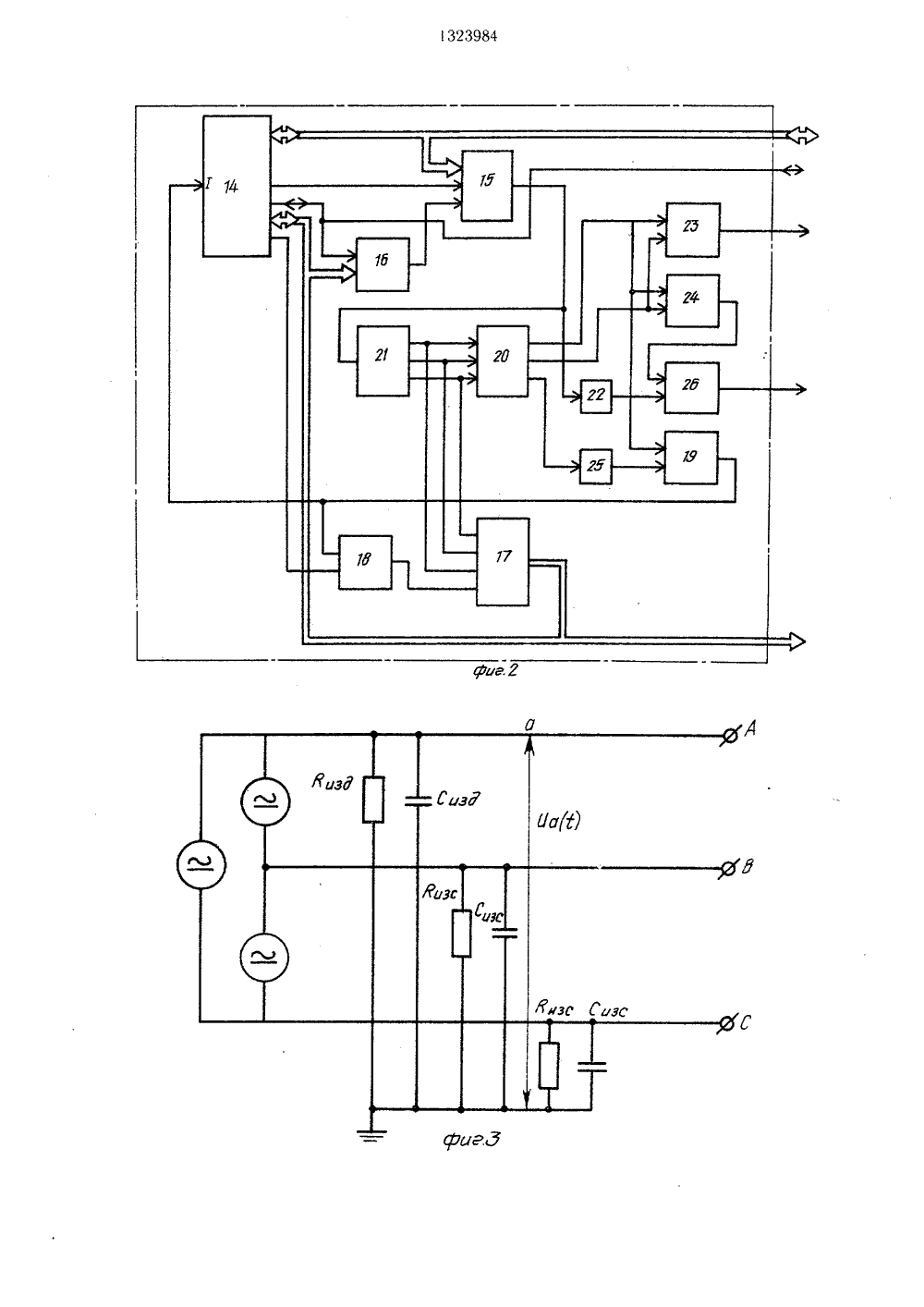

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 8 1) 4 ( 01 й 27/18 ОПИСАНИЕ ИЗОБРЕТЕНИ ЕТЕЛЬСТВУ К АВТОРСКОМУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(56) Заявка ФРГ21758,кл. б 01 й 27/18, 198,Карниловский Л. И, Импульсный способизмерения сопротивления изоляции сетейпостоянного тока и обесточенных сетей. Вопросы судостроения, Сер. Судовая электроника и связь, Л.: Судостроение, 1977, вып. 16.Авторское свидетельство СССР1067451, кл, б 01 К 27/18, 1983.(54) СПОСОБ ОПРЕДЕЛЕНИЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ(57) Изобретение относится к электроизмерительной технике. Цель изобретения - расширение функциональных возможностей и повышение точности работы устройства. Устройство содержит генераторимпульсного сигнала, развязывающий блок 4, блок 5 фиксации мгновенных значений, элемент 7 задержки, запоминающий элемент 8 и индикатор 13. В устройство введены фильтр 3, аналого-цифровой преобразователь 6, буферный регистр 9, управляюгце-вычислительный блок 10, дешифратор 11 и элемент НЕ 12. Кроме того, в описании представлена функциональная схема управляюще-вычислительного блока 1 О. 2 с. и 1 з.п. ф-лы, 4 ил.Изобретение относится к электроизмс рцтельной технике и предназначено для измерения сопротивления изоляции электрических сетей переменного, постоянного ипеременно-постоянного тока, находящихсяпод рабочим напряжением или обесточенныхи имеющих значительные емкости фаз (полксов) относительно корпуса,Цель изобретения - расширение функциональных возможностей за счет обеспецения измерения сопротивления изоляциисетей постоянного, переменного и постояннопеременного тока, находящимся под рабочимнапряжением или обесточенных и имеюшихемкости полюсов (фаз) относительно корпуса,при одновременном повышении точности исохранении быстродействия.На фиг. 1 изображена функциональцаясхема устройства; на фиг. 2 - функциональная схема управляюще-вычислительного блока; ца фиг, 3 - эквивалецтцаисхема контролируемой сети; на фиг. 4форма сигнала 1)р в тецение 1.го периодатестовых импульсов.Устройство для измерения сопротивленияя изоляции электрических с стей(см. фиг. ) содержит генераторимпу ьсного сигнала, включенный между ксрнусом и одним из полюсов (фаз) кон 1 ролируемой сети 2, к этому полюсу (фав) подключен вход филь ра 3, послелс вительносоединенного с развязывакщим б оком 4,блоком 5 фикса 1 н 1 и мгповенц 1 х значенийи аналого-цифровым преобразователем 6,второй вход которого через элемент 7 задержки, а второй вход блока 5 фикскции мгновенных значений ценосредствецно соединеныс выходом запоминающего элемента с,первые входы аналого-цифрового арсис,разователя 6 через двуцаправлецц к ш 1 цуданны.с соединены с первыми вхсла ц гуферного регистра 9 и первыми входами-выходамиуправляюгце-выцислительцого блока 10, второй выход которого подключсн к управляемому первому входу дешифратора1 и обивединец с открытым коллектора:1 ъ; всодомэлемента 12 НЕ, вход ксторог; сседицсц свторым выходом аналого-цифроьцсо пресббразователя 6, третий выход управлянще-выцислительцого блока О;вязан с входом управления генератора 1, четвертый выход управляюще-вычислительного блока 1 Осоединен с входом запоминакщего элемента 8, пятые выходы этого блока через шинуадреса подключены к вторым входам дешифратора 11, выход которого соединен с вторымвходом буферного регистра 9, а его выходыподключены к входам индикатора 13.Управляюще-вычислительцый блок 1 О(см. фиг. 2) содержит микроконтроллер 14, первые входы-выходы которого являются первыми входами. выходами управлякщевь 1 числительцого блока 10 и соединены с первыми входами программируемого тай 2мера 15 второй вхсд которого соединен с вторым выходом микроконтроллера 14, третий выход последнего через двунацравленнук линию соединен с первым входом дешифратора 1 и является вторым входом- выходом управляюще-вычислительного блока О, четвертые входь 1-выходы микроконтроллера 14 через двунаправленную шину адреса соединены с вторыми входами дешифратора 6, выходами шинного форми О рователя 17 и являются пятыми входамивыхсдами управляющего-вычислительного блока 10, пятый выход микроконтроллера 4 подключен к одному из выходов элемента 8 И, другой вход которого вместе 15с входом микроко 1 проллера 14 соединен с выходом три:гера 9, а выход элемента 18 И подклкчец и первому входу шинного фор.мировате.1 я 17, второй, третий и четвертый -,ходы вместе с первым, вторым и третьим ;ходом дешифратора 20 соединены с первым 20 вторым и третьим выходом счетчика 21,вход которого вместе с входом элемента 22 задержки подключен к выходу программируе".ого таймера 15, кроме того, первый вь 1 хол с ц 1 цфратора 20 соединен с первыми входагщ триггеров 19 и 23 и элемента 24 ИЛИ - НЕ второй выход деццфратора 20 соединен с вторыми входами элемецга 24 ИЛИ - НГ и триггера 23, выход которого является вторым выходом управляюще-вычислительного б ока 10, гретий выход дешифратора 20 через элемс цт 25 задержки соединен с вторым входом тр 11 ггера 19, выход элемента 24 ИЛИ- -НЕ подключен к первому входу элемента 26 И, второй вход которого сое,ицсц с выходом элемента 22 задержки. а выход является четвертым выходом управлякще-вы:1 ислительцого блока 10..5Сущность способа измерения сопротивления изо.1 яции заключается в следуюгцем.В наприкении фаза А - корпус силовой 40 электрицеской сети постоянно-переменноготска (фиг. 3), находящейся под рабочим напряжением, подвергаемой воздействию импульсов тестового тока амплитуды 1. с частотой 1 ц целесообразно выделить три составляюсцие: переменную, состоящую из 45 суммы гармонических напряжений, с частотами, кратными сетевой ). ), величина которой определяется соотношениями импедансов фаз и переменными составляюгцими линейны:с напряжений; (Р) ( )Г(Р)+ У (Р) - У;(Р) где 1.(Р) - изображение по Фурье напряжения (.),Ч);55У. (Р) - изображение по Фурье полныхимпедансов фаз сети относительно корпуса;импульса, подаваемого ца контролируемуюсеть 2, начинается перезаряд емкости изоляции (см. фиг. 1). Напряжение, описываемое выражением (1), снимаемое с контролируемой сети 2, подается на вход фильтра 3. Г 1 осле подавления в этом напряжениифильтром 3 составляющей Г).оно черезразвязывающий блок 4 (служащий, в частности, для гальванической развязки цепейустройства с контролируемой сетью 2) подается на первый вход блока 5 фиксациимгновенных значений.Г 1 о прошествии времени 1; после начала1-го цикла измерения на четвертом выходеуправляюще-вычислительного блока 10 появляется импульс, который фиксируется в зано.минающем элементе 8 на время, необходимоедля четкой выборки мгновенного значения1 (фиг. 4) сигнала 3 лф(1) в блоке 5 фиксации мгновенных значений. Через необходимое для запоминания значения Ь время(определяемое параметрами элемента 7 за ддержки) импульс с выхода запоминающегоэлемента 8 достигает второго входа аналогоцифрового преобразователя 6, который через время, необходимое для осуществленияодного цикла преобразования, на первойгруппе выходов устанавливает значениев виде цифрового кода, а на втором выходе -сигнал готовности данных, По этому сигналу(поступающему, в частности, на второй входвыход управляюще-вычислительного блока10 через элемент 12 НЕ с открытым коллекторным выходом) происходит запись кода свыхода аналого-цифрового преобразователя6 через двунаправленную шину данных нпервую группу входов-выходов унравляющевычислительного блока 10 в его внутреннееоперативное запоминаюгцее устройство,Таким же образом происходит измерениеи запоминание мгновенных значений 1., Б,;.сигналаф(1).Через промежуток времени, равный4 Л 1; (фиг. 4), на третьем выходе управляюще-вычислительного блока 10 появляется сиг Онал 0, вызывая изменение полярности выходного тока генератора 1 с положительной на отрицательную, нри этом импульсна четвертом выходе управляюще-вычислительного блока 10 не вырабатывается.Далее через промежуток времени 5 Ь 16.1;, 7 й 1; после начала цикла измеренияво внутреннее оперативное запоминающее устройство унравлпюще-вычислительного блока 10 происходит запись мгновенныхзначений Ь 1-з 50После этого в управляюще вычислительном блоке 10 происходит вычисление К.,ьх, Тпо формулам (5) - (7),Результат измерения Р; в данном цикле выставляется унравляюще-вычислительным 5 блоком 10 на его первых входах-выходах, одновременно ца пятых входах-выходах появляется код адреса индикатора, а ца цто д Топ(8 где Т - период импульсов калиброваннойчастоты,на выходе таймера 15 снова появляется импульс. Этот импульс увеличивает на единицу содержимое счетчика 21. Появление кода 1 на выходе счетчика 21 приводит к обнулению всех выходов дешифратора 20 и установлению сигналана выходе элемента 24 ИЛИ - НЕ и связанном с ним входе элемента 26 И,ром входе-выходе - сигнал готовности информации. По этому сигналу дешифратор 11, опознав свой адрес, выдает на выходе сигнал 1, которая разрешает запись кода Киз с шины в буферный регистр 9, который запоминает его до окончания следующего цикла измерения. Поскольку выходы буферного регистра 9 соединены с входами индикатора 13, последний в течение (+1) -го цикла измерения отображает значение К полученное в результате выполнения данного (1-го) цикла измерения.Работа управляюще-вычислительного блока 1 О в 1-м цикле измерения происходит следующим образом.Окончание (1 - 1)-го (и начало 1-го) периода происходит в момент изменения содержимого счетчика 21 с 7 на 0 под воздействием 8-го (последнего) в ( - 1)-м периоде импульса с выхода таймера 15. Обнуление счетчика 21 приводит к появлению на первом выходе дешифратора 20 1, которая устанавливает выходы триггеров 19 и 23 и связанный с последним третий выход управляще-вычислительного блока0 в единичное состояние. Сигнал 1 с выхода триггера 19 достигает первого входа микроконтроллера 14, вынуждая его на своих первых, третьем и пятых входах-выходах (и соответственно на первых, вторых и четвертых входах-выходах управляюще-вычислительного блока 10) установить состояние высокого импеданса. Тем самым управление указанными линиями передается внешним по отношению к микроконтроллеру 14 блокам (что последний подтверждает установкой логической единицы на своем пятом выходе),Как только сигнал с пятого выхода микроконтроллера 14 достигает второго входа элемента 18 И, на его выходе появляется уровень, разрешающий шинному формирователю 17 установить на шине адреса код, равный коду ца выходе счетчика 21.Таймер 15 после обнуления счетчика автоматически возобновляет подсчет импульсов калиброванной частоты, поступающих на его второй вход с второго выхода микроконтроллера 14. Как только число М прошедших импульсов становится равным М; (занесенному в таймер 15 в конце ( - 1)-го цикла измерения), 13239847Через промежуток времени, примерно равный 0,5 мкс (задаваемый элементом 22 задержки), импульс с выхода таймера5 достигает второго входа элемента 26 И, передается на его выход, являющийся четвертым выходом управляюще-вычислительного блока 10. Как только на второй вход- выход управляюще-вычислительного блока О поступает импульс (с выхода аналогоцифрового преобразователя 6, через элемент 12 НЕ на фиг. 1), происходит запись кода значения входного сигнала 1 Г 1, находящегося в тот момент на первых входах-выходах микроконтроллера 14, в его оперативное запоминающее устройство по адресу ААзАз где значения шестнадцатиричных чисел А, Аь Аз определяются внутренней схемотехникой микроконтроллера 14 и выбираются исходя из конкретной программной реализации его алгоритма работы.Появление на выходе таймера 15 второго и третьего импульсов (через интервалы времени 2 Л 1; и ЗЬ 1; соответственно) вызывает выполнение описанной процедуры с той разницей, что коды, соответствующие 112 и .)з запишутся по адресам АА 2 Аз 2 и АА 2 АзЗЧетвертый импульс, выработанный таймером 15, вызывает изменение уровня напряжения на выходе триггера 23 и третьем выходе управляюще-вычислительного блока 10 с 1 на 0, вызывая начало формирования отрицательного полупериода тестового сигнала. Это происходит потому, что при появлении кода 4 на выходе счетчика 21 на втором выходе дешифратора 20 появляется сигнал, вызывающий сброс триггера 23. Кроме того, этот сигнал через элемент 24 ИЛИ - НЕ блокирует элемент 26 И. В результате формирования и запоминания мгновенного значения входного сигнала на четвертом такте не происходит.Появление на выходе таймера 15 пятого и шестого импульсов приводит в итоге к записи в микроконтроллере 14 кодов Б и 12 по адресам АА 2 Аз 5 и АА 2 Аз 6Появление седьмого импульса вызывает запоминание значения Яз, вдобавок к этому происходит запуск микроконтроллера 14 следующим образом. Наличие кода 7 на выходе счетчика 2 приводит к установлению уровняна третьем выходе, дешифратора 20. Этот сигнал через время задержки, определяемое длительностью процедуры формирования и запоминания кода одного мгновенного значения сигнала (3 Аф(1) и задаваемое параметрами элемента 25 задержки, вызывает сброс триггера 9. Как следствие, на выходах шинного формирователя 17 устанавливается состояние высокого импеданса, на пятом выходе микроконтроллера 4 устанавливается уровень 0 в подтверждение того, что микроконтроллер 14 взял на себя управление шинами и линиями.8После этого в нем происходит вычисление величин, определяемых выражениями (5) - (8). Результат вычисления числа 1; микроконтроллер 4 заносит в таймер5 (адрес которого определяется дешифратором 16), а результат вычисления К. помещает в соответствующем коде на шину данных (т.е. на первые входы-выходы управляюще-вычислительного блока0), сопровождая его кодом адреса на шине адреса (пятые входы-выходы управляюще-вычислительного блока 10) и импульсом на втором входе-выходе управляюще-вычислительного блока 10.Управляюще-вычислительный блок 10 и все устройство в целом приходят в исходное состояние после появления на выходе таймера 15 8-го в данном периоде импульса. формула изобретения 50 2 Г+ (/з опротивквивалентнзяции; 55 искомоезение изоамплитудтока; тестовых ьс 20 1, Способ определения сопротивленияизоляции электрических сетей, заключающийся в воздействии на контролируемую сеть импульсным сигналом, измерении мгновенных значений напряжения, определении по измеренным значениям величины сопротивления изоляции и регулировании периода воздействующего сигнала, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения измерения сопротивления изоляции сетей постоянного, переменного и постоянно-переменного тока, находящихся под рабочим напряжением или обесточенных и имеющих емкости полюсов относительно корпуса, при одновременном повышении точности и сохранении быстродействия, формируют импульсный сигнал в виде разнополярных импульсов тока постоянной амплитуды, подаваемый непосредственно на контролируемую сеть, фильтруют напряжение, снимаемое с одного из полюсов (фаз), сети, производят измерение трех мгновенных значений напря жения, прошедшего фильтрацию, в моментывремени, равноудаленные друг от друга, а также от начала н конца положительного полупериода импульсного сигнала, а также трех значений этого напряжения в аналогичные моменты времени в течение отрицательного полупериода этого сигнала, определяют эквивалентное сопротивление изоляции в соответствии с выражением3Х (11;1,з ) - значения напряжения, прошедшего фильтрацию в указаннь:е выше моменты времени в течение положительного (отрицательного) тестового сигнала, определяют значение постоянной времени эквивалентного импеданса изоляции в соответствии с выражением где т - искомая постоянная времени эквивалентного импеданса изоляции;-- промежуток времени между измерениями значений напряжения, прошедшего фильтрацию,определяют длительность следующего периода воздействующего сигнала как величину, пропорциональную постоянной времени эквивалентного импеданса и равную целому числу периодов переменной составляюгцей рабочего напряжения сети,2. Устройство для определения сопротивления изоляции электрических сетей, содержащее генератор импульсного сигнала, индикатор, развязывающий блок, блок фиксации мгновенных значений, элемент задержки, причем первый вход блока фиксации мгновенных значений соединен с выходом запоминающего элемента, отличающееся тем, что с целью расширения функциональных возможностей, в него дополнительно введены фильтр, аналого-цифровой преобразователь, элемент НЕ с открытым коллекторным выходом, дешифратор, буферный регистр, управляюще-вычислительный блок, причем один выход генератора импульсного сигнала объединен е входом фильтра и подключен непосредственно к одному из полю.сов (фаз) контролируемой сети, другой выход генератора импульсного сигнала соединен с корпусом, причем генератор импульсного сигнала представляет собой генератор разнополярных импульсов тока, выход фильтра соединен с входом развязывавшего блока, выход блока фиксации мгновенных значений подключен к первому входу аналого. цифрового преобразователя, второй вход которого соединен через элемент задержки с выходом запоминающего элемента, первые выходы аналого. цифрового преобразователя сОединены через двунаправ пеннуо шину данных с объединенными между собой первыми входами буферного регистра и первыми входами-выходами управ ляюще-вычислительного блока, а второй выход аналого-цифрового преобразователя через элемент НЕ с открытым коллекторным выходом подключен к двунаправленной линии, соединяющей первый вход дешифра 5 10 15 20 25 30 35 40 45 50 55 тора и второй вход-выход управляюще-вычис лительного блока, третий выход которого подключен к входу управления генератора импульсного сигнала, четвертый выход соединен с входом запоминающего элемента, а пятые выходы через шину адреса подключены к вторым входам дешифратора, выход которого связан с вторым входом буферного регистра, выходы которого подключены к вхо. дам индикатора.3. Устройство по п. 2, отличающееся тем, что управляюще-вычислительный блок содержит микроконтроллер, два дешифратора, программируемый таймер, два триггера, элемент ИЛИ - НЕ, два элемента задержки, два элемента И, счетчик, шинный формирователь, причем первые входы-выходы микроконтроллера объединены с первыми входами программируемого таймера через двунаправленную шину данных и являются первыми входами-выходами управляюще-вычислительного блока, второй выход микроконтроллера соединен с вторым входом программируемого таймера, третий вход последнего соединен с выходом первого дешифратора, первый вход которого через двунаправленную линию соединен с третьим выходом микроконтроллера и является вторым входом-выходом управляюще-вычислительного блока, вторые входы первого дешифратора соединены через двунаправленную шину адреса с выходами шинного формирователя и четвертыми входами-выходами микроконтроллера, которые являются пятыми входа. ми-вьходами управлякще-вычислительного блока, пятый выход микроконтроллера соединен с одним входом первого элемента И, другой вход которого объединен с входом микроконтроллера и подключается к выходу первого триггера, а выход первого элемента И соединен с первым входом шинного формирователя, второй, третий четвертый входы которого объединены с первым, вторым, третьим входами второго дешифратора и подключеныы к первому, второму, третьему выходам счетчика, вход которого объединен с входом первого элемента задержки и подключен к выходу программируемого таймера, первый выход второго дешифратора соединен с первыми входами первого и второго триггера соответственно и одним из входов элемента ИЛИ - НЕ, второй выход второго дешифратора соединен с другим входом элемента ИЛИ - НЕ и вторым входом второго триггера выход которого является вторым выходом управляюше-вычислительного блока, третий выход второго дешифратора через второй элемент задержки соединен с вторым входом первого триггера, выход элемета ИЛИ - НЕ подключен к первому входу второго элемента И, второй вход которого соединен с выходом второго элемента задержки, а выход является четвертым выходом управляюще-вычислительного блока.Составитель Н. МихалевРедактор Е. Копча 1 ехред И, Верес Корректор А. ТяскоЗаказ 2962/50 Тираж 730 ПодписноеВНИИПИ Государственного комитета СССР по делам изобретений и открытий13035, Москва. Ж - 35, Раушская наб., д. 4/5Троизводственно.полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

4036940, 29.01.1986

ВСЕСОЮЗНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЭЛЕКТРОИЗМЕРИТЕЛЬНЫХ ПРИБОРОВ

ЛЫСЕНКО АЛЕКСЕЙ ЛЕОНОВИЧ, МАШЕНКОВ ВАЛЕРИЙ МИХАЙЛОВИЧ, ПОТАПКИН ВЛАДИМИР КОНДРАТЬЕВИЧ

МПК / Метки

МПК: G01R 27/18

Метки: изоляции, сетей, сопротивления, электрических

Опубликовано: 15.07.1987

Код ссылки

<a href="https://patents.su/8-1323984-sposob-opredeleniya-soprotivleniya-izolyacii-ehlektricheskikh-setejj-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ определения сопротивления изоляции электрических сетей и устройство для его осуществления</a>

Предыдущий патент: Устройство для измерения сопротивления изоляции электрических сетей постоянного тока

Следующий патент: Цифровой измеритель коэффициента передачи четырехполюсника

Случайный патент: Грохот