Элемент вычислительной средыо r-i о ( i »э. hfsur q; r rtjton. vulil idgt; amp; y; i: r isjfs

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 419887

Автор: Мишин

Текст

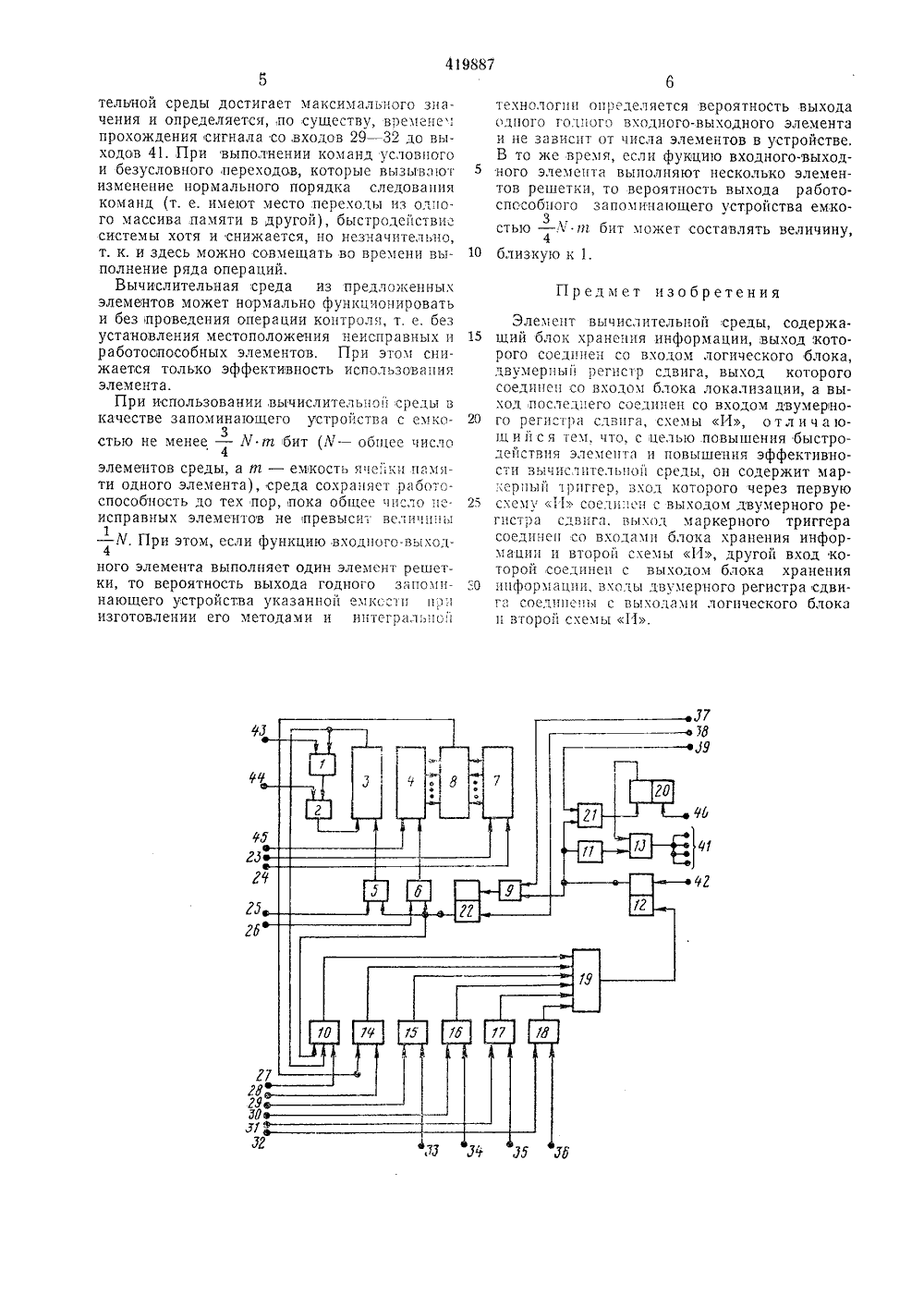

щ 49887 ОП И САНИ Е ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик(51) М. Кл. 6 061 7/00 Государственный комитет Совета Министров СССР оо делам изооретений и открытий(72) Авторизобретения А. И. Мишин Институт математики Сибирского отделения АН СССР(54) ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ ислительнои среды из реды, с блоблок тома- правИзобретение относится к области автоматики и вычислительной техники и предназначено для использования в качестве базового элемента универсальных вычислительных сред(однородных структур).Известен элемент вычислительной с содержащий двумерный регистр сдвига ком локализации, логический блок и хранения информации, позволяющий ав тически осуществлять локализацию неис ных элементов вычислительной среды,Предложенное устройство отличается тем, что содержит маркерный триггер, вход которого через первую схему И соединен с выходом двумерного регистра сдвига; выход маркерного триггера соединен,со входами блока хранения информации и второй схемы И, другой вход которой соединен с выходом блока хранения информации, входы двумерного регистра сдвига соединные с выходами логического блока и второй схемы И.Это позволяет повысить быстродействие элемента (и следовательно - среды в целом) за счет того, что ввод и вывод информации с элемента вьечислительной среды осуществляются с максимально возможной скоростью - со скоростью работы двумерного регистра сдвига, а также повысить эффективность вычислительной среды за счет более эффективной локализации неисправных элементов. Схема элемента выч ображепа на чертеже.Элемент вычислительной среды содержитблок хранения информации, выполненный на 5 схемах И 1, ИЛИ 2, регистрах сдвига 3,4, схемах И 5, 6; логический блок, выполненный на регистре сдвига 7 и схеме сравнения 8; схемы И 9 и 10; двумерный регистр сдвига, выполненный на элементе задержки 10 11, триггера активности 12, схемах И 13 -18, ИЛИ 19; блок локализации, выполненный на триггере локализации 20 и схеме И 21; маркерный триггер 22.Вход 23 предназначен для подачи кодового 15 слова для записи в регистр сдвига 7, а вход24 - для подачи управляющих сдвигающих импульсов; входы 25, 26 предназначены для подачи управляющих сдвигающих импульсов в регистры 3 ц 4 соответственно (управление 20 прохождением этих сигналов через схемы И5, 6 осуществляется маркерным триггером 22.Вход 27 предназначен для управления считыванием информации с регистра 3; вход 28 - для управления считыванием сигнала, выра батываемого схемой сравнения 8 (эта схемавырабатывает сигнал единица тогда, когда кодовое слово, поступающее в,регистр 7,по входу 23, совпадает с кодовым словом, хранящимся в регистре 4). Входы 29 - 32 предназ пачепы для приема сигналов с выходов соседпих элементв; входы 33 -36 прелпазначены дл 51,пода 111 сиг,1 алв о выборе направлений приема сигналв, пос 1 упающих в элемент по входам 2932. Бхол 37 служит для управления установкой в сл 1 шицу маркерного триггера 22; усхапвка эгго триггера в единицу сущсс 1 вляетс 51 151)11 условии, что триггер актпгшсти 12 находится в состоянии единица, Вход 38 служит для установки триггера 22 в состояние пуль, вход 39 - для управления записью сигналов неисправности в триггер локализации 20, Вход 40 предназначен для установки в елиницу триггера локализации 20, Выходы 41 явля 1 отся выходными пОлюсами эле,1 еп 1 а, сигпагы с кОтОрых пО- ступают на входы 29 - 32 соседних элементов; вход 42 предназначен лля подачи управляющих и сдвигающих сигналов в триггер активности 12,Вход 43 предназначен для регенерации информации, считываемой через схему И 10 с регистра сдвига 3; вход 44 предназначен для подачи сигалов, подлежащих записи в регистр 3 (управляющие сдвигающие импульсы вырабатывает лля регистра 3 схема И 5); вход 45 предпазпачеп лля подачи сигналов, подлежащих записи в регистр сдвига 4 (управляющие сдвигающие импульсы для этого регистра вырабатывает схема И 6).Входы 23 - 28, ЗЗ - 40, 42 - 45 являются управляющими и подключаются к общим управляющим шинам среды (активным или пассивным), количество которых не зависит от числа элементов в вычислительной среде и определяется числом управляющих входов у одного элемента.Основными режимами функционирования вычислительной, среды являются:а) локализация неисправных элементов; б) ввод информации;в) вычисление;,г) вывод информации.Режим локализация предназначен для устранения влияния неисправных элементов вычислительной среды па исправные. Локализация неисправных элементов осуществляется без обнаружения их местоположения в среде, т. е. автоматически. Если неисправность отказавщего элемента опасна, т. е, может распространяться,по:вычислительной среде, то триггер локализации 20 этого элемента устанавливается в состояние пуль (через вход 39), и тем самым запрещается передача сигналов неисправности на выходы 41. В зависимости от вида неисправности, локализагция ее производится либо с помощью блока локализации неисправного элемента (если исправны схемы И 13, 21 и триггер 20), либо блоками локализации соседних элементов (если в отказавшем элементе неисправны, схемы 13, 21 или триггер 20). Локализация неисправных элементов вычислительной среды осуществляется путем подачи соответствующих наборов 1 сигналов на управляющие воды вычислительной среды (на вход 39 нужно, подать 5 10 15 20 25 30 35 40 45 50 55 60 65 сиги 1 л елипица) . Возможность локализации неисправных элементов вычислительной срелы без установления их местоположения в среде обусловлена тем, что управление вычислительной средой осуществляется с помо 1 ць 1 упрэв ч 5 1 Оцих,входов ОлпОГО элемента.После выполнеия локализации неисправных элементов производится ввод информа. ции в срелу. В процессе настройки в блоки хранения информации элементов вычислительной среды вводятся исходные данные и программа работы системы в целом.В данном случае при установке в единицу триггера активности 12 производится и установка в единицу маркерного триггера 22, с помощью которого и осуществляется управление записью (считыванием) информации в регистры 3, 4. Для этого подаются соответствующие сигналы по входам 25, 26, 44, 45.В режиме вычисление на управляющие входы вычислительной среды подается информация, подлежащая обработке, а с выхода вычислительной среды снимается, результат обработки. В качестве примера рассмотрим считьивание информации с одного элемента. Пусть триггеры 12 и 22 всех элементов среды находятся в состоянии нуль и требуется вы. брать элемент с определе 1 ным адресом (именем). Для этого нужно по входу 23 подать соответствующее кодовое слово, а по входу 24 - управляющие сдвигающие импульсы. На выходе схемы сравнения 8 выбранного элемента появится сигнал единица, с помощью которого может быть осуществлена установка в единицу триггера активности 12 (на вход 28 нужно подать сигнал единица). Далее, путем подачи сигнала единица на вход 37 осуществляется установка в единицу маркерного триггера 22, после чего триггер активности 12 устанавливается в состояние пуль (по вхолу 42). Считывание информации с элемента производится путем подачи слвигающих импульсов на вход 25 (если требуется произвести считывание без разрушения, то на вход 43 нужно подать сигнал единица), Сигналы, считы 1 ваемые с регистра 3, поступают на вход двумерного регистра сдвига (через схему И 10) и далее передаются этим регистром на выходы элементов, расположенных при,периферии вычислительной среды.Считывание информации осуществляется, таким образом, со скоростью работы двумерного регистра сдвига. После считывания (или до считывания) может быть произведена запись информации в регистры 3, 4 путем подачи соответствующих сигналов на входы 25, 26, 44. Отметим, что параллельно с,выполнением операции считывания (записи) может осуществляться выборка следующего элемента среды. Это означает, что в случае, когда команды следуют одна за другой по порядку (номер команды, соответствует порядковому номеру элемента, 1 где хранится содержание данной команды), быстродействие вычисли тельной среды достигает максимального значения и определяетсяпо существу, времене: прохождения сигнала со,входов 29 - 32 до выходов 41. При выполнении команд условного и безусловного переходов, которые вызывают изменение нормального порядка следования команд (т. е. имеют место перехолы из одного массива памяти в другой), быстродействие системы хотя и снижается, но незначительно, т. к, и здесь можно совмещать во времени выполнение ряда операций.Вычислительная среда из предложенных элементов может нормально функционировать и без проведения операции контроля, т, е. без установления местоположения неисправных и работоспособных элементов. При этом снижается только эффективность использования элемента.При использовании, вычислительной среды в качестве запоминающего устройства с смкозстью не менее - У т бит (Л - общее число4элементов среды, а и - емкость ячски памяти одного элемента), среда сохраняет работоспособность до тех пор, пока общее число неисправных элементов не превысит величины 1- М. При этом, если функцию входного-выхолного элемента выполняет один элемент решетки, то вероятность выхода годного запоминающего устройства указанной емкосп при изготовлении его методами и интегральной технологии определяется вероятность выхода одного голного входного-выходного элемента и не зависит от числа элементов в устройстве.В то же время, если фукцию входного-выход ного элемента выполняют несколько элементов решетки, то вероятность выхода работоспособного запоминающего устройства емкостью - Л ог бит может составлять величину,410 близкую к 1. Предмет изобретенияЭлемент вычислительной среды, содержа.15 щий блок хранения информациивыход которого соединен со входом логического блока,двумерный регистр сдвига, выход которогосоединен со входом блока локализации, а выход последнего сослинен со входом двумерно 20 го регистра слвига, схемы 1 Л, о т л и ч а ющ и й с я тем, что, с целью повышения быстролействия элемента и повышения эффективности вычислительной среды, он содержит мар: ерныйриггер, вхол которого через первую25 схему И соелн:;он с выходом двумерного регистра сдвига. выхол маркерного триггерасоединен со входами блока хранения информации и второй схемы И, другой вход которой соединен с выходом блока храненияБО информации, вхолы двумерного регистра сдвига соединены с выхолами логического блокаи второй схемы И,

СмотретьЗаявка

1739273, 14.01.1972

А. И. Мишин Институт математики Сибирского отделени СССР

МПК / Метки

МПК: G06F 7/00

Метки: hfsur, idgt, isjfs, rtjton, vulil, вычислительной, средыо, элемент, э•«•

Опубликовано: 15.03.1974

Код ссылки

<a href="https://patents.su/3-419887-ehlement-vychislitelnojj-sredyo-r-i-o-i-eh-hfsur-q-r-rtjton-vulil-idgt-amp-y-i-r-isjfs.html" target="_blank" rel="follow" title="База патентов СССР">Элемент вычислительной средыо r-i о ( i »э. hfsur q; r rtjton. vulil idgt; amp; y; i: r isjfs</a>

Предыдущий патент: Дешифратор

Следующий патент: Устройство для возведения чисел в квадрат

Случайный патент: Прессконвейер для вулканизации резиновых изделий