Преобразователь синусно-косинусных сигналов в последовательность импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

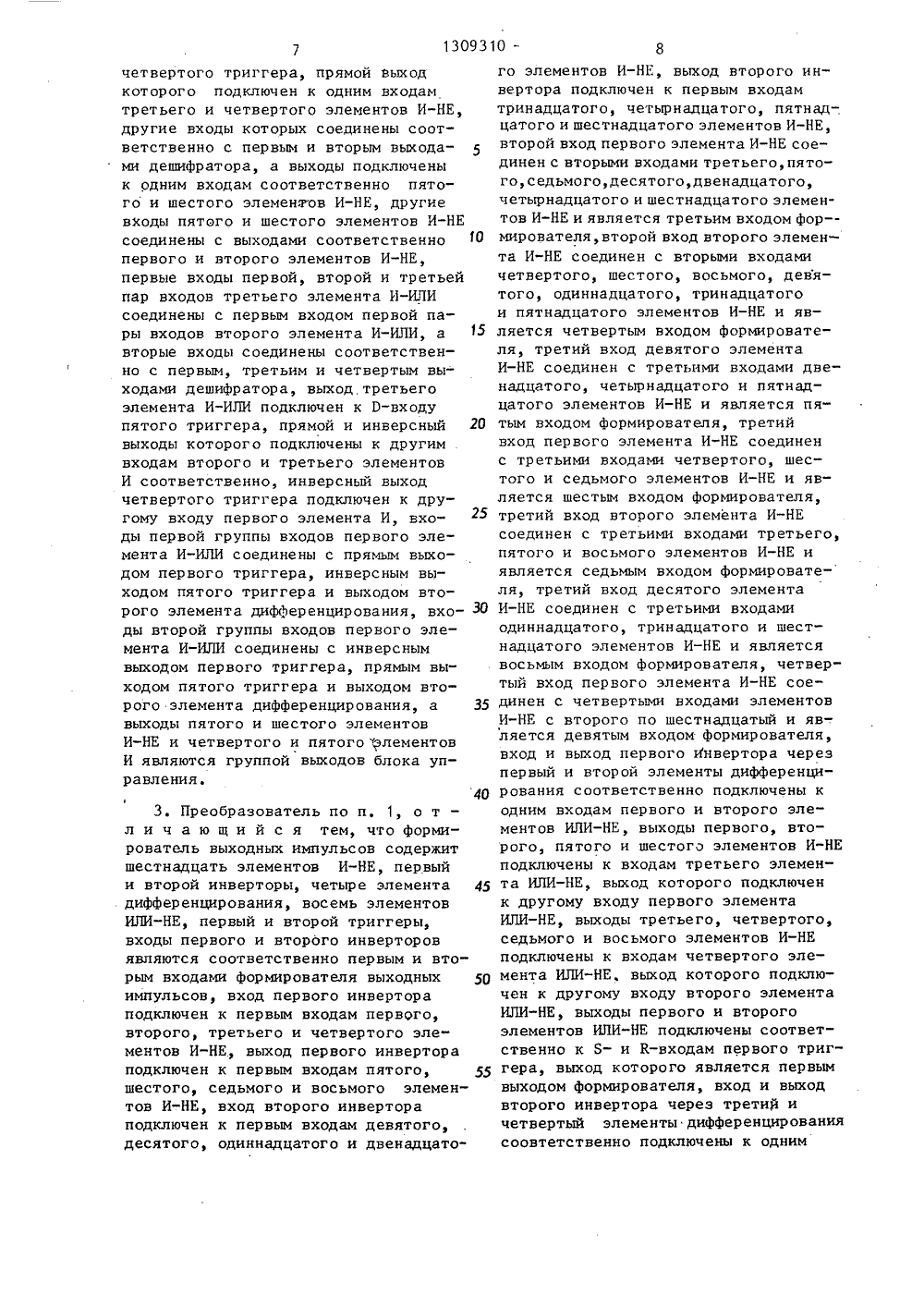

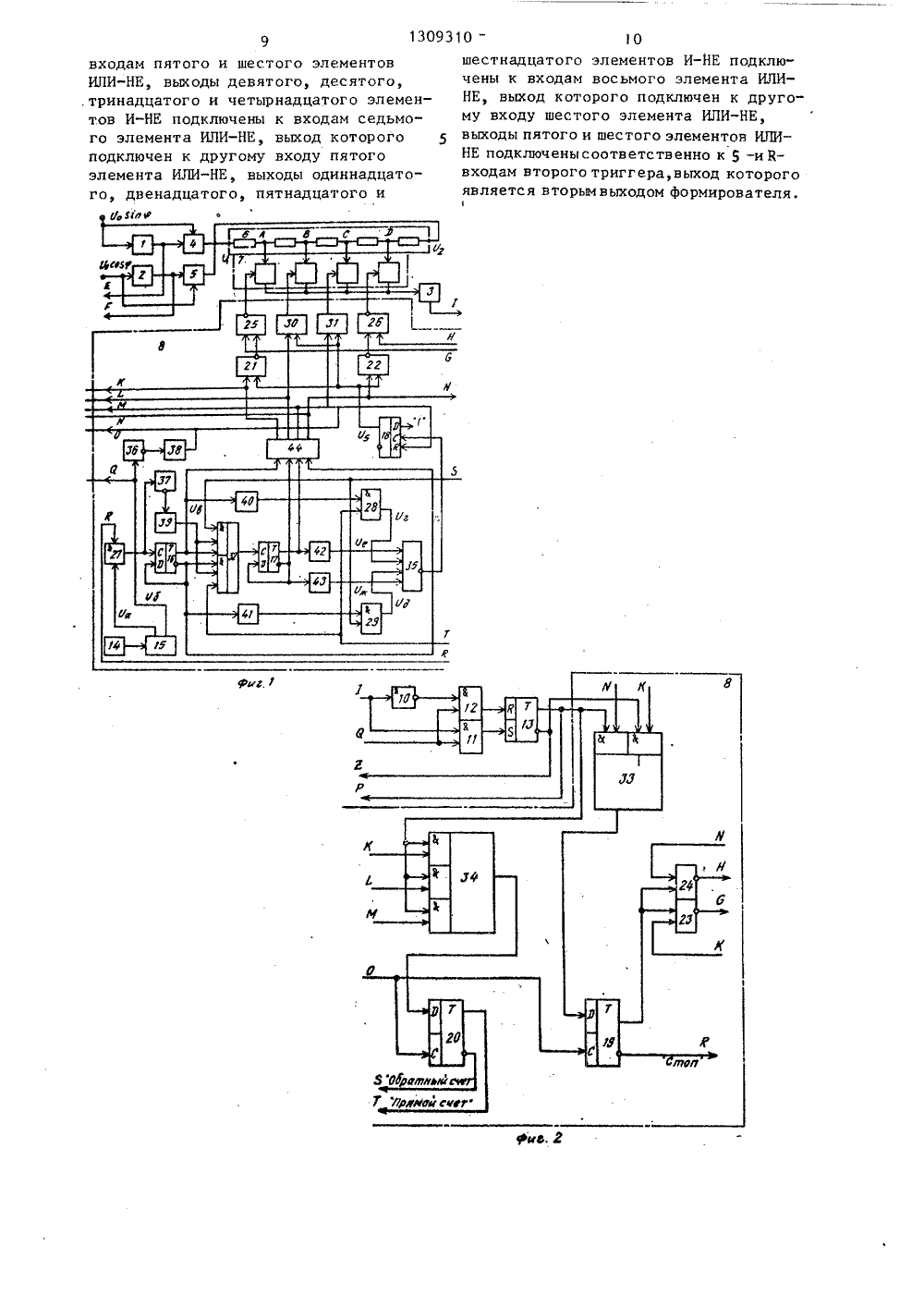

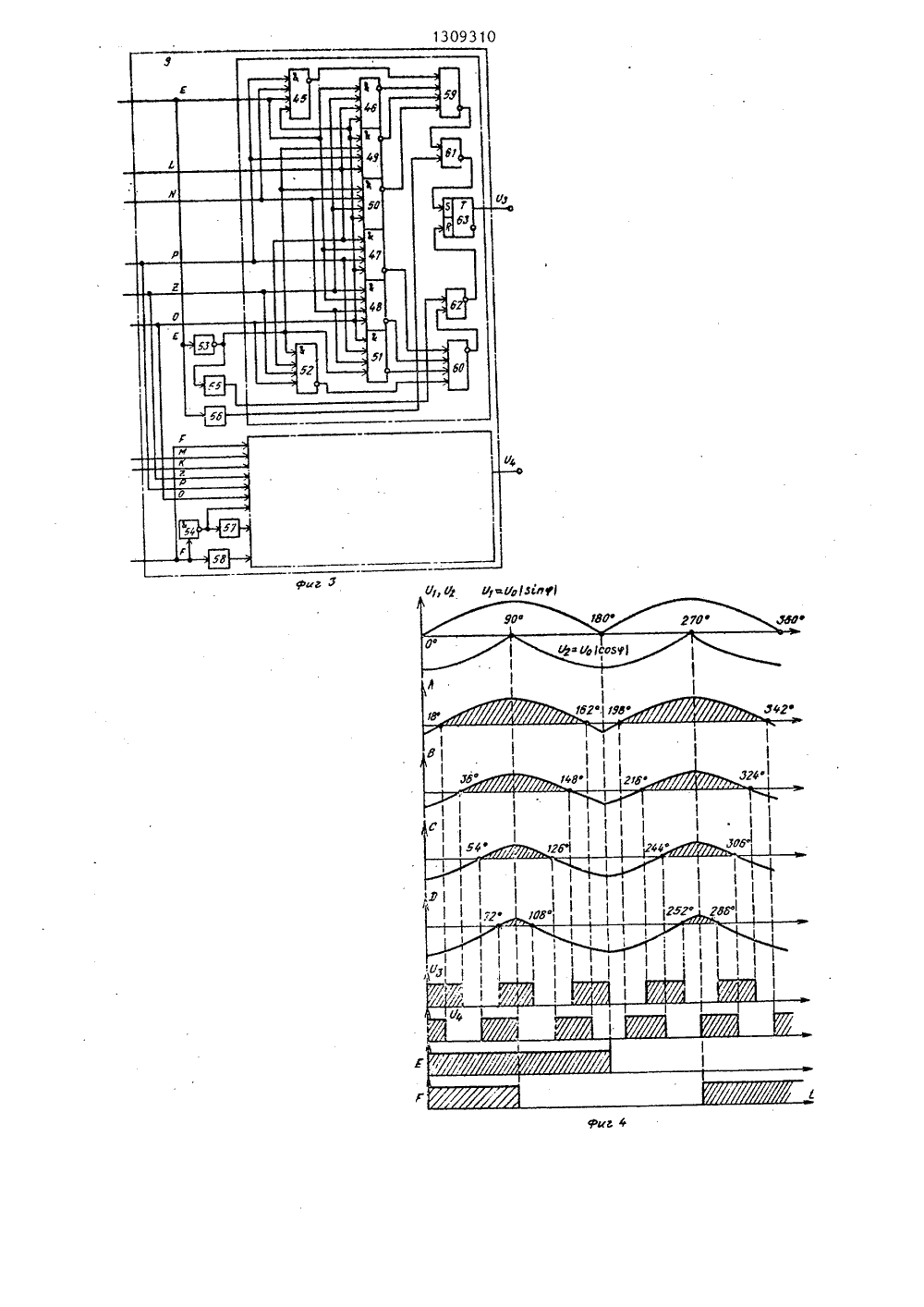

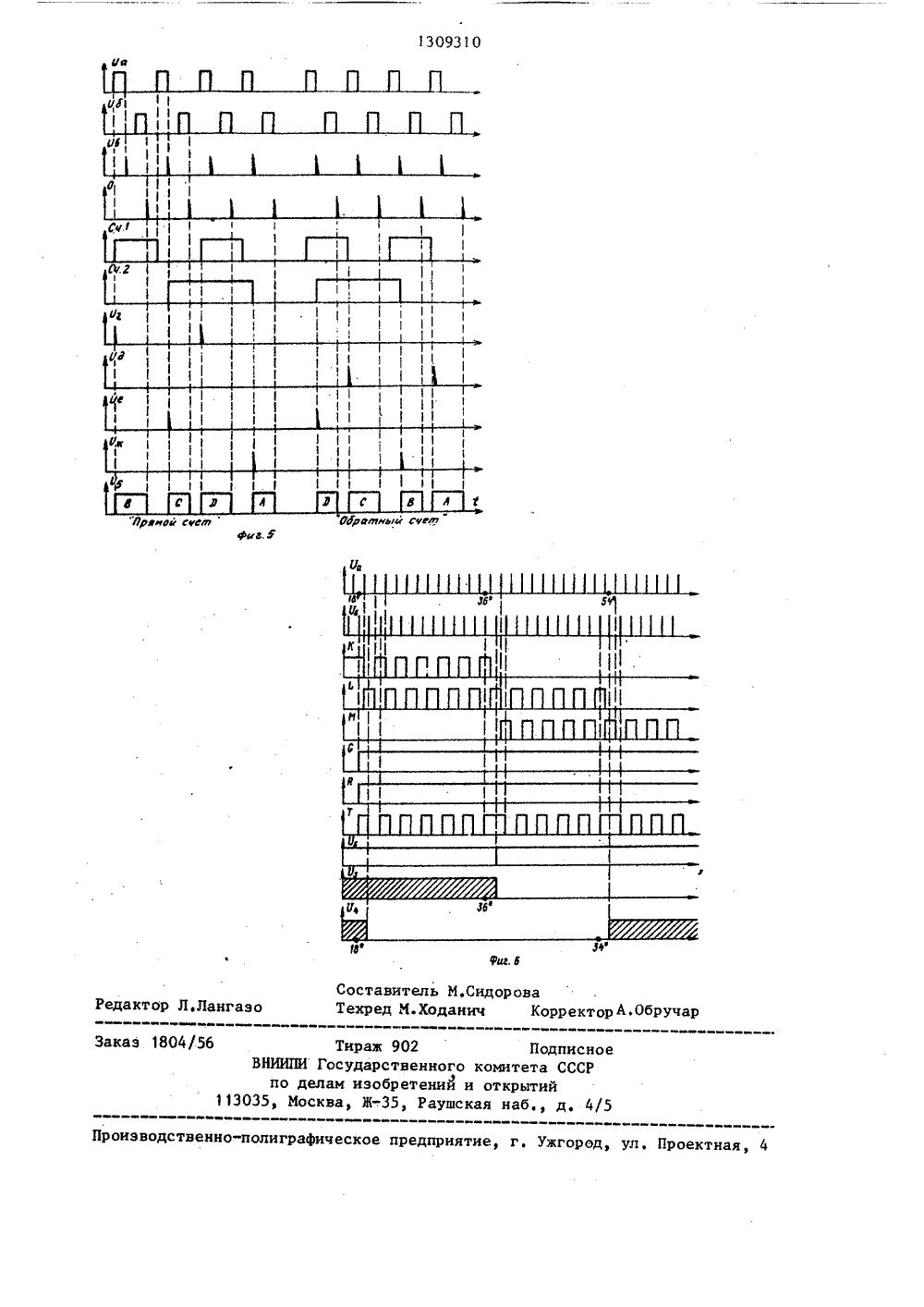

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) (И 1 0 4 Н 03 М 1/30 ПИСАНИЕ РЕТЕНИ с.1 ЕЛЬСТВ К АВТОРСКОМУ С г свидетельство ССС08 С 9/06, 1974.1945206,блик. 1973. о ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразователях перемещения в код. С целью повышения точности преобразователя путем уменьшения погрешности формирования опорного напряжения в преобразователь синусно-косинусных сигналовв последовательность импульсов, содержащий первый и второй нуль-органы,входы которых являются соответственно первым и вторым входами преобразователя и подключены к информационным входам первого и второго выпрямителей, а выкоды первого и второгонуль-органов подключены соответственно к первому и второму входам фор"мирователя выходных импульсов, резистивный делитель напряжения, третий нуль-орган, введены блок ключей,блок управления, инвертор, иервый ивторой элементы И, триггер. Блок управления содержит генератор импульсов, формирователь импульсов, шестьэлементов И-НЕ, пять элементов И,три элемента И-ИЛИ, элемент ИЛИ-НЕ,два инвертора, шесть элементов дифференцирования, дешифратор. Формирователь выходных импульсов содержитшестнадцать элементов И-НЕ, два инвертора, четыре элемента дифференцирования, восемь элементов ИЛИ-НЕ идва триггера. Первый и второй нульорганы формируют код квадранта. Выходное напряжение выпрямителей посту- дпает на входы резистивного делителяЮнапряжений, который работает в режимефазорасщепителя. В зависимости отсоотношений между амплитудами вход- Сных сигналов преобразователя срабатывают определенные ключи, в блокеуправления формируются единичные сигналы на определенных выходных шинах. маИз выходных сигналов первого и второ- (фго нуль-органов, триггера и блокауправления в формирователе выходныхимпульсов формируются две последовательности импульсов с дискретностью,соответствующей числу градаций в резистивном делителе напряжения внутриквадранта. 2 з.п. ф-лы, 6 ил.1 13093 Изобретение относится к автоматике и Вычислительной технике и может быть использовано в преобразователях перемещения в код.Целью изобретения является повышение точности преобразователя путем исключения формирователей опорного напряжения.На фиг. 1-3 представлена структурная схема преобразователя; на фиг,46 - временные диаграммы его работы.Преобразователь содержит первый 1, второй 2 и третий 3 нуль-органы, первый 4 и второй 5 выпрямители, резистивный делитель 6 напряжения, блок 7 15 ключей, блок 8 управления, Формирователь 9 выходных импульсов, инвертор10, первый 11 и второй 12 элементыИ и триггер 13,Блок 8 управления содержит генера тор 14 импульсов, формирователь 15 импульсов, первый 16, второй 17, третий 18, четвертый 19 и пятый 20 триггеры, первый 21, второй 22, третий 23, четвертый 24, пятый 25, шестой 26 элементы И-НЕ, первый 27, второй 28, третий 29, четвертый 30 и пятый 31 элементы И, первый 32, второй 33 и третий 34. элементы И-ИЛИ, элемент 35 ИЛИ, первый 36 и второй 37 инверторы, первый 38, второй 39, третий40, четвертый 41, пятый 42 и шестой43 элементы дифференцирования, дешифратор 44,Формирователь 9 выходных импульсов содержит элементы И-НЕ 45-52,первый 53 и второй 54 инверторы,элементы 55-58 дифференцирования,элементы ИЛИ-НЕ 59-62, триггер 63.Остальные восемь элементов И-НЕ, четыре элемента ИЛИ-НЕ и триггер (непоказаны) соединены аналогично элементам 45-52, 59-63.Преобразователь работает следующим образом. 45Входные напряжения П зпи Усовпреобразуются в прямоугольные импульсы первым 1 и вторым 2 нуль-органами (фиг. 1 и 4, Е, Р). Эти им.пульсы управляют первым 4 и вторым 5ключевыми выпрямителями, представляю-щими собой усилители с изменяемымзнаком усиления. На выходах ключевыхвыпрямителей 4 и 5 формируются напряжения Пып 4 и -Псоз у(Фиг. 4,П, П), которые питаот резистивныйделитель 6 напряжения, составляющийфазовращатель, Номиналы резистороввыбираются таким образом, что нулевые 10 2напряжения в общих точках резисторов соответствуют фазе входного сигнала,1 кратной дискрете перемещения, например 18 (фиг, 4, А, В, С, Р), На выходе преобразователя Формируются две последовательности импульсов (фиг.4,13), фронть которых Формируются при фазе входного сигнала, кратнойо18, Таким образом, выходные сигналы преобразователя являются результатом интерполяции входных сигналов.Нахождение точки с напряжением, близким к нулевому, и слежение за ней осуществляется с помощью блока 7 ключей и третьего нуль-органа 3.Алгоритм управления ключами блока 7 заключается в следующем, Если напряжение во всех точках делителя 6 больше нуля, то в результате переключения ключей блока 7 и опроса третьего нуль-органа 3 замыкается на нуль-орган 3 точка В. Если все напряжения меньше нуля, то к нуль- органу 3 в конечном счете подключается точка А. В остальных случаях при неизменном напряжении на выводах делителя 6 поочередно подключаются две соседние точки делителя 6 к нуль- органу, напряжение на которых противоположно по знаку, например при Фазе входного сигнала в пределах 36- о54 поочередно подключаются к нуль- органу точки В и С. Частота переключений должна быть достаточно высокой для слежения за парой точек, напряжение на которых противоположно по знаку. Исходное состояние ключей блока 7 не имеет значения, так как алгоритм управления ключами замкнутый и осуществляется в двух направлениях.Синхронизация устройства осуществляется тактовым генератором 14, подключенным к формирователю 15 синхроимпульсов, на выходе которого формируются две последовательности импуль- сОВ (Фиг5, П,(, ПБ), сдВинутых ВО времени.В основе счетчика устройства лежат два триггера 16 и 17, представляющие собой тактируемые Э-триггеры в счетном включении за счет обратной связи. Этот счетчик работает в трех режимах - остановки, прямого счета и обратного счета. Счетными импульсами являются импульсы с первого выхода формирователя 15 синхроимпульсов (П),которые при остановке блокируются на элементе И 27. Первый триг 13093 13гер 16 переключается по переднему фронту Б , а триггер 17 - по заднему фронту этого импульса, который вьщеляется с помощью инвертора 37 и элемента 39 дифференцирования (фиг, 5, Б). Все элементы дифференцирования устройства выделяют положительные перепады напряжения на их входах, Такое временное разделение счетных импуль-, сов для триггеров 16 и 17 счетчика 10 позволяет производить изменение направления счета сигналами на элементе 32, исключая срабатывание счетчи.ка. Прямые и инверсные выходы триггера 17 управляют работой дешифра тора 44, выходы которого соединены с входами управления ключами блока 7.Из-за неодновременного срабатывания триггеров 16 и 17 на выходе дешифратора 44 появляются ложные сиг калы, например при переходе триггеров 16 и 17 счетчика из состояния (1,0) в состояние (О, 1) на выходе дешифратора 44 возможно формирование сигнала соответствующего состоянию (0,0). Для исключения этого элемен- ты 40-43 дифференцирования выделяют положительные перепады напряжений, которые фильтруются элементами 28, 29 (фиг. 5, Бе, Б,ь, Б, Бх) и 30 поступают на тактовый вход третьего триггера 18, записывая в него логическую "1" с Э-входа. В результате триггер 18 переключается тогда, когда в счетчике устанавливается очеред ное новое состояние после срабатывания либо триггера 16, либо триггера 17, либо после их совместного срабатывания. Триггер 18 возвращается в исходное состояние по заднему фронту импульса П, выделяемом инвертором 36 и элементом 38 дифференцирования (фиг. 5, 0) . Последовательность импульсов на выходе триггера 18 в режиме прямого и обратного счета изоб ражена на фиг. 5 (П)1Таким образом, ключ блока 7 замыкается на время между передним и задн фронтами Пр и Б, а при выполненни условия А ( 0 или 0 7 0 ключи остаются замкнутыми сигналами 6 и Н, поступающими на элементы И-НЕ 25 и 26. Опрос состояния нуль-органа 3 производится сигналом П(Я), фиксирующем это состояние в триггере 13 через элементы 11 и 12. Условие АО, Р ) 0 выявляется элементом И-ИЛИ 33 и фиксируется в триггере 19 по зад 0 4нему фронту П(0). По этому фронту триггер 20 формирует сигнал "Прямой счет" (Т), если А, В, С ) О, в противном случае выдается сигнал Обратный счет" (Я), не играющий роли при наличии сигнала "Стоп" (к) с триггера 19.Функционирование устройства (фиг,6) происходит следующим образом.При у ( 18 О триггеры 16 и 17 счетчика останавливаются сигналом К, а точкаподключается к нуль-органу 3 сигналом С. При 18 с у с 36производится последовательное подключение точек А, В, а при 36 с чс 54 точек В, С сигналами с дешифратора 44 (К, Ь,М,М)Выходные сигналы устройства П и ц формируются формирователем 9, Инверторы 53, 54, элементы 55-58 дифференцирования вьщеляют фронты импульсов с первого 1 и второго 2 нуль-органов. При этом, есии г= 0 то триггер 63 устанавливается в "1", а при Ч= 180 в "0" при движении датчика перемещений, формирующего входные сигналы преобразователя, в одну сторону и в противоположные состояния при движении в другую сторону. Аналогичная установка другого триггера формирователя 9 производится при фазах 90 ф и 270 (фиг. 4, П, П). Остальные переключения триггеров формирователя 9 производятся по заднему фронту сигнала Пб (фиг, 5, О; фиг3) при выполнении условий переключения (фиг. 4). П принимает значение "1" при выоплнении условий Е ) О, Р ) 0; В ( О, Е 1 0; В ) О, Е ( 0; 0 ( О, Е ( 0При переходе фаозы через значение 36 выполняется условие В Ъ 0 (Е ) 0), и на выходе элемента И-НЕ 47 появится короткий отрицательный импульс (фиг. 6, П) . устанавливающий триггер 63 в нулевое состояние. Если при включении устройства на входе имеет место состояние А ( 0 или Р ъ О, то триггер 63 может установиться в произвольное состояние, которое принимает требуемое значение после изменения входных сигналов в результате перемещения датчика положения. Практически это имеет место, так как перед измерениями перемещений производится начальная установка системы (поиск, например, сигнала начала отсчета).5 13093Формула изобретения 1. Преобразователь синусно-косинусных сигналов в последовательность импульсов, содержащий первый и второй нуль-органы, входы которых являются соответственно первым и вторым входами преобразователя и подключены к информационным входам соответственно первого и второго выпрямителей, а вы р ходы первого и второго нуль-органов подключены соответственно к первому и второму входам формирователя выходных импульсов, резистивный делитель напряжения, третий нуль-орган, о т л и ч а ю щ и й с я тем, что, с целью повышения точности преобразователя, в него введены блок ключей, блок управления, инвертор, первый и второй элементы И, триггер, выходы первого ивторого нуль-органов подключены к управляющим входам первого и второго выпрямителей соответственно, выходы которых подключены к входам резистивного делителя напряжения, 25 выходы резистивного делителя напряжения подключены к соответствующим входам блока ключей, выходы блока ключей соединены между собой и подключены к входу третьего нуль-органа, Зр выход которого подключен к одному входу первого элемента И и через инвертор - к одному входу второго элемента И, выходы первого и второго элементов И подключены соответственно к Б- и К-входам триггера, выходы триггера подключены соответственно к третьему и четвертому входам формирователя выходных импульсов и к первому и второму входам блока уп О равления, группа выходов которого подключена к управляющим входам ключей, первый выход блока управления подключен к другим входам первого и второго элементов И, а второй, тре тий, четвертый, пятый и шестой выходы блока управления подключены соответственно к пятому, шестому, седьмому, восьмому и девятому входам формирователя выходных импульсов.2. Преобразователь по п, 1, о т - л и ч а ю щ и й с я тем, что блок управления содержит. генератор импульсов, формирователь импульсов, пять триггеров, шесть элементов И-НЕ, пять элементов И, три элемента И-ИЛИ, элемент ИЛИ, первый и второй инверторы, шесть элементов дифференцирования, дешифратор, выход генератора 10 6импульсов подключен к входу формирователя импульсов, первый выход которого подключен к одному входу первого элемента И, а второй выход является первым выходом блока управления и через первый инвертор подключен к входу первого элемента дифференцирования, выход первого элемента И подключен к С-входу первого триггера и через второй инвертор - к входу второго элемента дифференцирования, прямой выход первого триггера подключен к первому входу дешифратора и через третий элемент дифференцирования - к одному входу второго элемента И, инверсный выход первого триггера подключен к его Р-входу, второму входу дешифратора и через четвертый элемент дифференцирования - к одному входу третьего элемента И, выход первого элемента И-ИЛИ подключен к С"входу второго триггера, прямой выход которого подключен к третьему входу дешифратора и к входу пятого элемента дифференцирования, а инверсный выход - к Р-входу второго триггера, к четвертому входу дешифратора и к входу шестого элемента дифференцирования, выходы второго, третьего элементов И, пятого, шестого элементов дифференцирования подключены к соответствующим входам элемента ИЛИ, выход которого подключен к С-входу третьего триггера, В-вход которого соединен с шиной единичного потенциала, а выход подключен к одним входам первого и второго элементов И-НЕ и к одним входам четвертого и пятого элементов И, первый, второй, третий, четвертый выходы дешифратора подключены к другим входам соответственно первого, второго элементов И-НЕ, четвертого и пятого элементов И и являются соответственно вторым, третьим, четвертым и пятым выходами блока управления, выход первого элемента дифференцирования является шестым выходом блока управления и подключен к К-входу третьего триггера и к С- входам четвертого и пятого триггеров, первые входы первой и второй пар входов второго элемента И-ИЛИ являются соответственно первым и вторым входами блока управления, вторые входы первой и второй пар входов второго элемента И-ИЛИ соединены соответственно с вторым и первыми выходами дешифратора, а выход второго элемента И-ИЛИ подключен к Э-входучетвертого триггера, прямой выходкоторого подключен к одним входамтретьего и четвертого элементов И-НЕ,другие входы которых соединены соответственно с первым и вторым выходами дешифратора, а выходы подключенык одним входам соответственно пятого и шестого элементов И-НЕ, другиевходы пятого и шестого элементов И-НЕсоединены с выходами соответственно 10первого и второго элементов И-НЕ,первые входы первой, второй и третьейпар входов третьего элемента И-ИЛИсоединены с первым входом первой пары входов второго элемента И-ИЛИ, авторые входы соединены соответственно с первым, третьим и четвертым выходами дешифратора, выход третьегоэлемента И-ИЛИ подключен к Р-входупятого триггера, прямой и инверсный 20выходы которого подключены к другимвходам второго и третьего элементовИ соответственно, инверсный выходчетвертого триггера подключен к другому входу первого элемента И, входы первой группы входов первого элемента И-ИЛИ соединены с прямым выходом первого триггера, инверсным выходом пятого триггера и выходом второго элемента дифференцирования, входы второй группы входов первого элемента И-ИЛИ соединены с инверснымвыходом первого триггера, прямым выходом пятого триггера и выходом второго элемента дифференцирования, а 35выходы пятого и шестого элементовИ-НЕ и четвертого и пятого флементовИ являются группой выходов блока управления. 403. Преобразователь по п, 1, о т - л и ч а ю щ и й с я тем, что формирователь выходных импульсов содержит шестнадцать элементов И-НЕ, первый и второй инверторы, четыре элемента 45 дифференцирования, восемь элементов ИЛИ-НЕ, первый и второй триггеры, входы первого и второго инверторов являются соответственно первым и вторым входами формирователя выходных 50 импульсов, вход первого инвертора подключен к первым входам первого, второго, третьего и четвертого элементов И-НЕ., выход первого инвертора подключен к первым входам пятого, 55 шестого, седьмого и восьмого элементов И-НЕ, вход второго инвертора подключен к первым входам девятого, десятого, одиннадцатого и двенадцатого элементов И-НЕ, выход второго инвертора подключен к первым входамтринадцатого, четырнадцатого, пятнадцатого и шестнадцатого элементов И-НЕ,второй вход первого элемента И-НЕ соединен с вторыми входами третьего,пятого,седьмого, десятого, двенадцатого,четырнадцатого и шестнадцатого элементов И-НЕ и является третьим входом фор мирователя,второй вход второго элемента И-НЕ соединен с вторыми входамичетвертого, шестого, восьмого, девятого, одиннадцатого, тринадцатогои пятнадцатого элементов И-НЕ и является четвертым входом формирователя, третий вход девятого элементаИ-НЕ соединен с третьими входами двенадцатого, четырнадцатого и пятнадцатого элементов И-НЕ и является пятым входом формирователя, третийвход первого элемента И-НЕ соединенс третьими входами четвертого, шестого и седьмого элементов И-НЕ и является шестым входом формирователя,третий вход второго элемента И-НЕсоединен с третьими входами третьего,пятого и восьмого элементов И-НЕ иявляется седьмым входом формирователя, третий вход десятого элементаИ-НЕ соединен с третьими входамиодиннадцатого, тринадцатого и шестнадцатого элементов И-НЕ и являетсявосьмым входом формирователя, четвертый вход первого элемента И-НЕ соединен с четвертыми входами элементовИ-НЕ с второго по шестнадцатый и яв-.ляется девятым входом формирователя,вход и выход первого инвертора черезпервый и второй элементы дифференцирования соответственно подключены к одним входам первого и второго элементов ИЛИ-НЕ, выходы первого, второго, пятого и шестого элементов И-НЕподключены к входам третьего элемента ИЛИ-НЕ, выход которого подключенк другому входу первого элементаИЛИ-НЕ, выходы третьего, четвертого,седьмого и восьмого элементов И-НЕподключены к входам четвертого элемента ИЛИ-НЕ, выход которого подключен к другому входу второго элементаИЛИ-НЕ, выходы первого и второгоэлементов ИПИ-НЕ подключены соответственно к Б- и К-входам первого триггера, выход которого является первымвыходом формирователя, вход и выходвторого инвертора через третий ичетвертый элементы дифференцированиясоовтетственно подключены к одним.тринадцатого и четырнадцатого элементов И-НЕ подключены к входам седьмого элемента ИЛИ-НЕ, выход которого 5подключен к другому входу пятогоэлемента ИЛИ-НЕ, выходы одиннадцатого, двенадцатого, пятнадцатого и 1 Ошестнадцатого элементов И-НЕ подключены к входам восьмого элемента ИЛИНЕ, выход которого подключен к другому входу шестого элемента ИЛИ-НЕ, выходы пятого и шестого элементов ИЛИ - НЕ подключенысоответственно к 5 -и В- входам второго триггера, выход которого является вторым выходом формирователя. (лтныи СУСЛ Фи СМл оставитель М.Сидехред М.Ходанич аКорректор А,Обручар актор Л.Лангаз Заказ 1804/56 Тираж 902 Подписно ВНИИПИ Государственного комитета СССР по делам изобретении и открытий 3035, Москва, Ж, Раушская наб., д. 4/

СмотретьЗаявка

3993157, 17.12.1985

ПРЕДПРИЯТИЕ ПЯ Г-4710

ЯРУХИН АЛЕКСАНДР ИВАНОВИЧ, ЛЯНГ ВАСИЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 1/30

Метки: импульсов, последовательность, сигналов, синусно-косинусных

Опубликовано: 07.05.1987

Код ссылки

<a href="https://patents.su/8-1309310-preobrazovatel-sinusno-kosinusnykh-signalov-v-posledovatelnost-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь синусно-косинусных сигналов в последовательность импульсов</a>

Предыдущий патент: Способ формирования счетных импульсов в преобразователе перемещения в код и устройство для его осуществления

Следующий патент: Преобразователь перемещения в код

Случайный патент: Локализатор взрыва