Устройство для вычисления свертки функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 742969

Автор: Осипенко

Текст

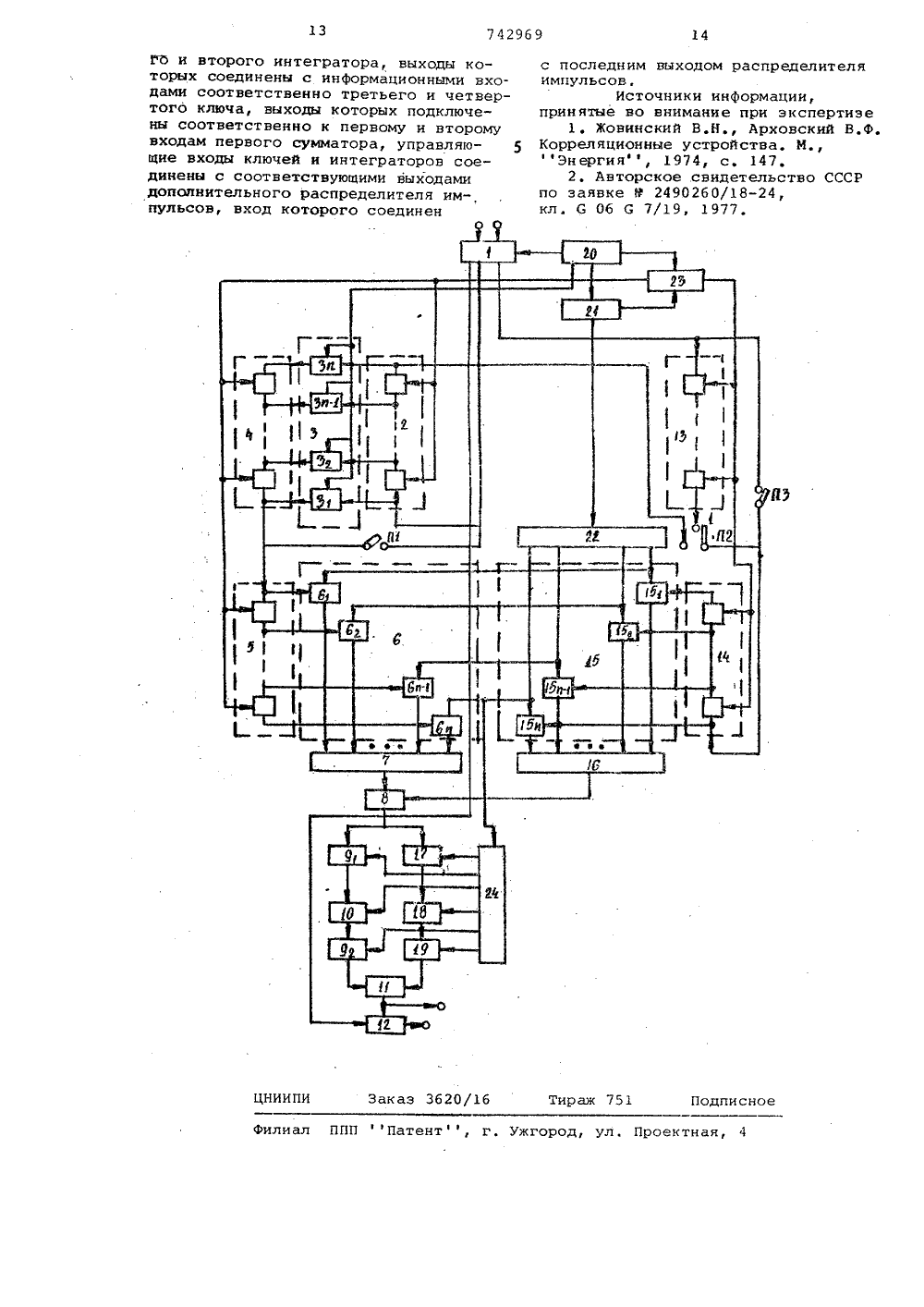

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОУСКОМУ СВИДЕТИЛЬСТВУ Союз Советских Социалистических Республик(22) Заявлено 060378 (21) 2587586/18-24 С. 06 С 7/19 с присоединением заявки Мо 2616085/18-24 Государственный комитет СССР по делам изобретений и открытий(72) Автор изобретения В.Г.Осипенко Таганрогский радиотехнический институт им. В,Д.Калмыкова(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СВЕРТКИ ФУНКЦИЙ преобразования частоты, линии задержки, блоки умножения, распределитель импульсов, блоки памяти почислу блоков умножения, рециркуляторы и интегратор 2),Недостатком известного устройстваявляется:неинвариантность к времениприхода сигналов, а также невозможность вычисления корреляционных Функций общего вида.Цель изобретения - расширениефункциональных воэможностей путемвычисления корреляционных функций.Для достижения указанной цели вустройство для вычисления сверткифункций, содержащее масштабный блок,первый и второй входы. которого являются соответствующими входами устройства, а первый выход соединен совходом первой линии задержки с последовательно соединенными ячейками памяти, блок управления, первый выходкоторого соединен со входом генератора импульсов, первый выход которогоподключен к управляющим входам ячеекпамяти первой линии задержки, распределитель импульсов, блок умножения,первый сумматор, выход которого соединен с первым входом блока преобразоИзобретение относится к специали=ированной вычислительной техникеи может быть использовано в радиотехнике, связи, радиоавтоматике, из.мерительной технике, радионавигации,радиолокации, гидролокации, радиоуправлении, диагностической аппаратуре, авторегулировании, автоконтроле и других областях для вычислениясвертки Функций и корреляционногоанализа принимаемых известных и неизвестных сигналов и измерения ихпараметров и характеристик; а такжедля обнаружения и опознавания сигналов и источников их излучения,Известно устройство для корреляционного анализа, содержащее аналогоцифровой преобразователь, линии задержки, блоки умножения и блоки усреднения 1),Недостатком устройства являетсясложность аналого-циФровых блоковумножения и необходимость многоканальной линии задержки.25Известно также устройство длявычисления свертки функций, содержащее функционально связанные междусобой масштабный блок, блок управления,генератор импульсов, блоквания частоты, введены генератортактовых импульсов, четыре линии задержки с последовательно соединеннЫми ячейками памяти, три блока ключей, два сумматора, два интегратора, четыре ключа, дополнительныйраспределитель импульсов и три переключателя, при этом информационныевкоды первого блока ключей соединеныс выходами соответствующих ячеекпервой линии задержки, а управляющиевходы - со вторым выходом блока управ Оления, третий и четвертый выходыкоторого подключены соответственноко входу генератора тактовых импульсов и к третьему входу масштабногоблока, второй выход которого соединен с первым входом блока преобразования частоты, первый и третий выходы масштабного блока подключенысоответственно к неподвижным контактам соответственно первого и второго щопбреключателей, подвижные контактыкоторых подключены соответственно кн 4 ходу второй и ко входу третьей линйи задержки, ко входУ четвертойлинии задержки и к подвижному контакту третьего переключателя, первыйи второй неподвижные контакты которого соединены соответственно с ны-,ходом первой и пятой линий задержки,,вход последней подключен к третьемувыходу масштабного блока; выходыгенератора тактовых импульсов соединены соответственно со входом распределителя импульсов и со вторым входомгенератора импульсов, второй выходкоторого подключен к управляющим входам ячеек четвертой и пятой линий задержки, выходы первого, второго итретьего блока ключей соединены ссоответствующими входами ячеек второй линии задержки, второго сумма Отора и с соответствующими входамитретьего сумматора, выходы распредЕлителя импульсов подключены к соответствующим упранляющим входам второгои третьего блоков ключей, информа зционные входы которых соединены свЫходами соответствующих ячеектретьей и четвертой линий задержки,вЫходы второго и третьего сумматорапОдключены к соответствующим входамбпока умножения, выход которого соединен с информационными входами первого и второго ключей, выходы которьх подключены соответственно ковходам первого и нторбго интеграторов, выходы которых соединены с информационными входами соответственнотретьего и четвертого ключей, выходыкоторых подключены соответственнок первому.и второму нходам первогосумматора., управляющие входы ключейи интеграторов соединены с соответствующими выходами дополнительногораспределителя импульсов, вход которбго соединен с последним выходом распределителя импульсов. На чертеже приведена структурная схема предлагаемого устройства.Устройство содержит соединенные последовательно масштабный блок 1, входы которого являются входами устройства, линию 2 задержки, состоящую иэ последовательнО соединенных ячеек памяти, выход каждой из которых является выходом линии задержки и соединен со входом последующей ячейки памяти, блок 3 аналоговых ключей, у которых сигнальные входы являются сигнальными входами блока и подключены н прямом порядке к соответствующим выходам линии 2 задержки, выходы являются выходами блока, а управляющие входы соединены вместе и образуют управляющий нход блока, линию 4 задержки, состоящую иэ последовательно соединенных ячеек памяти, выход каждой из которых является входом линии задержки и соединен со входом последующей ячейки памяти, и подключенную своими входами в обратном порядке к выходам третьего блока 3 аналоговых ключей, линию 5 задержки, состоящую из последонательно соединенных ячеек памяти, выход каждой из которых является выходом линии задержки и соединен со нходом последующей ячейки памяти, первый блок б аналоговых ключей, у которых сигнальные нходы являются входами блока и соединены в прямом порядке с выходами первой линии 5 задержки, управляющие входы являются управля- ющими нходами блока, а ныходы - выходами блока, сумматор 7, блок 8 умножения, аналоговый ключ 9, инте,гратор 10 со схемой сброса, аналоговый ключ 9 сумматор 11, выход кото,рого является первым выходом устройства, и блок 12 преобразования частоты, у которого выход янляется вторым выходом устройства, а дополнительный вход соединен с дополнительным ныходом масштабного блока 1, соединенные последовательно линию .13 задержки, подключенную входом к второму выходу масштабного блока 1 и состоящую из последовательносоединенных ячеек памяти, выход каждой из которых соединен со входом последующей ячейки памяти, второй переключатель П 2, линию 14 задержки, состоящую иэ последовательно соединенных ячеек памяти, выход каждой из которых является выходом линии задержки и соединен со входом последующей ячейки памяти, блок 15 аналоговых ключей, у которых сигнальные входы янляются сигнальными входами блока и подключены в обратном по- рядке к выходам второй линии 14 задержки,управляющие.входы являются управляющими входами,а выходы - выходами блока,и сумматор 1 б,выход которого соединен со вторым входом блока 8 умножения, последовательно соеди 74296 9ненные третий аналоговый ключ 17,сигнальный вход которого еоединен ссигнальным входом первого аналогового ключа 9( и подключен к выходублока 8 умножения, интегратор 18со схемой сброса и аналоговый ключ 519, выход которого соединен со вторымвходом сумматора 11, последовательно соединенный блок 20 управления,у которого дополнительный выход соединен с дополнительным входом масштаб ного блока 1, а третий выход - суправляющим входом бчока 3 аналоговыхключей, генератор 21 тактовых импульсов и распределитель 22 импульсовпоследовательного действия, выходы 5которого подключены к соответствующим попарно соединенным управляющимвходам первого и второго блоков би 15 аналоговых ключей, генератор23 импульсов, у которого вход соединен со вторым выходом блока 20 управления, дополнительный вход - с дополнительным выходом генератора 21тактовых импульсов, первые выходыподключены к управляющим входам каждой ячейки памяти линии 5, 2 и 4задержки, а вторые выходы - к управляющим входам каждой ячейки памятилиний 13 и 14 задержки, дополнительный распределитель 24 импульсовуправления, у которого вход соединен с последними управляющими входами блоков б и 15 аналоговых ключейи подключен к последнему выходураспределителя 22 импульсов, а соответствующие выходы подсоединены к 35управляющим входам аналоговых ключей 9, 9, 17 и 19 и интеграторов10 и 18 со схемами сброса, первыйпереключатель П 1, соединяющий входлинии 5 задержки с первым выходом 40масштабного блока 1, переключательП 2, соединяющий вход линии 14 задержки через первое положение с выходомпятой линии 13 задержки и через втоРое положени - с выходом третьей 45линии 2 задержки, и третий переключатель П 3, соединяющий вход второйлинии 14 задержки со вторым выходоммасштабного блока 1,Масштабный блок 1 состоит из двух(при вычислении взаимной свертки двухфункций и взаимокорреляционной Функции между двумя сигналами) или изодного канала (при вычислении автосвертки и автокорреляционной функциисигнала) и содержит, в частности,перестраиваемые по частоте входныецепи со ступенчатыми делителями напряжения, смесители, перестраиваемыйпо частоте гетеродин (или гетеродины)и усилители с регулируемыми коэффициентами усиления, При необходимости каналы дополнительно могутсодержать автоматические схемы перестройки (или подстройки) частотгетеродинов и автоматические схемы 65 регулировки амплитуд выходных напряжений.Каждая ячейка памяти дискретйеаналоговых линий 2, 4, 5, 13 и 14задержки состоит из двух аналоговыхзапоминающих схем, работающих подвухтактному принципу, и выходногосогласующего усилителя.Блок 12 преобразования частотысостоит, например,из смесителя, ккоторому дополнительно подводитсяколебание гетеродина масштабногоблока 1 и выходного усилительноготракта.Блок 20 управления предназначен дляввода в режим работы масштабного блока 1, отпирания через каждый интервал времени Т- д =(и) д на длительность даналоговых ключей блока 3, ввода в режим работы генератора 21 тактовых импульсов и генератора23 импульсов и автоматического изменения частоты повторения вырабатываемых этими генераторами импульсов.Блок 20 состоит, например, из функционально связанных между собой задающего генератора и схем управленияна элементах дискретной техники.Генератор 23 импульсов предназначен для выработки двух серий импульсов, сдвинутых относительно другдруга на интервал времени -д 1 (гдеь - интервал отсчета по Котельникову)кбторые управляют работой дискретноаналоговых линий 2, 4., 5, 13 и 14задержкии состоит например, изгенератора тактовых импульсов сперестраиваемой частотой, работа которого непрерывно синхронизируетсяимпульсами, поступающими с дополнительного выхода генератора 21 тактовых импульсов на дополнительныйвход генератора 23 импульсов, и четырехканального распределителя импульсов последовательного действия,длительность имгльсов на выходахкоторого равна - д 1 и выходы которо 2го подсоединены к первым выходам непосредственно и со сдвигом иа-ь 1ко вторым выходам генератора 23 импульсов (на чертеже подводка управляющих импульсов к ячейкам памятилиний 2, 4, 5 и 13, 14 задержкисимволически показана одной линией),Блок 24 предназначен для поочередного отпирания аналоговых ключей9, 19 и 9, 17 и управления сбросоминтеграторов 18 и 10Устройство работает следующимобразом,В момент времени 1 = 0 первыйблок 20 управления вводит в режимработы масштабный блок 1, генератор 21 тактовых импульсов, которыйначинает вырабатывать запускающиеимпульсы.с периодом повторения4 Г =вд, и генератор 23 импульсов.В результате этого на выходах оас -импульсы, которые мгновенно сбрасывают на нуль интегратор 10 и открывают аналоговые ключи 9 и 19. В результате этого значениедЭ(п) ). (-, д)5 с выхода интегратора 18 через аналоговый ключ 19 и сумматор 11 в течение интервала д действует на пергвом выходе устройства и на входе блока 12 преобразования частоты. ОВ этот же момент 1 = 1+ дС на выходах к+2, к+1. ,., 2, 1-ом линии 5 задержки появляются на интервал времени д 1 соответственно вы-.борки Э(и) д т )Э(и - 2)дМ) юф й.(и-)с) дС), й.э(и-)с - 2) дЦ сигнала ГЭ(Т-О, которые в обратном порядке за интервал времени - д 1 через аналоговые ключи 61, бг 6 к+ 6 +г блока 6 и сумматор 7 подводятся последовательно во времени на 203интервал - дС к первому входу блокаг8 умножения, ко второму входу которого в течение этого же интервала - дс через аналоговые ключи 15 к+ 15, , 15, , 15 блока 15 25 и сумматор 16 подводятся последовательно во времени на интервал АС соответственно выборки В сигнала Е 4 (Ц с выходов к+1, к 2, 1-го линии 14 задержки. При этом на 30 выходе блока 8 умножения образуются последовательно во времени результатый (и) д 1) Е,( г д),(и) д )(а)длительностями дТ;, которые через открытый аналоговый ключ 9( поступают на вход интегратора 10, в результате чего на его выходе обра эуется значениедс 1 (и)д 1 д 1+ Ж)Ы Г дВ момент времени 1 = 1+фд 1 под 45 воздействием канального импульса с и-го выхода распределителя 22 импульсов блок 24 управления вырабатывает импульсы, которые мгновенно сбрасывают на нуль интегратор 18 и откры вают аналоговые ключи 9 г и 17, в результате чего значение дГЬЪд 1- д 1 +Е Ж)дУ% 55с выхода интегратора 10 через аналоговый ключ 9 г и сумматор 11 в течение интервала г 1 дс воздействует на первом выходе устройства и на входе блока 12 преобразования частоты.В этот же момент времени 1 = С а на выходах к+2, к+1,2, 1-ом линии 14 задержки появляются интервал времени д 1 соответственно выборки И В гкэг сигнала Й 4 (С), которые в прямом порядке за интервал времени вдС через аналоговые ключигблока 15 и сумматор 16 подводятся последовательно во времени на интервал д Г ко второму входу блока 8 умножения, к первому входу которого в течение этогоже интервала где через аналоговые ключи блока 6 и сумматор 7 подводятся последовательно во времени на интервалдГсоответственно выборки Е,1(п-)с)а 1), ГЭ(п - )с) д ГЭ(п - 2) д, ЙЭ(и - 1) д 13 сигнала Е (Т-,1) с выЭходов 1, 2, , к+1, (к+2)-го линии 5 задержки. При этом на выходе блока 8 умножения образуются последовательно во времени результаты,О,-.ьф,(- ь) Ф-афер)1 з( -1 Ы 142 Ьдлительностями,дГ, которые через открытый аналоговый ключ 17 поступают на вход интегратора 18, в результате чего на его выходе образуется зна 1 ениедГ т (пп-Ыд 1 -д 1+ й-Од т - аЮ++Яд-а) и,(-, )В момент времени С = 1 2 д 1 по описанной выае методике значение дс 1 (п-ыЫ д 1 - д 1 + (п-г)М,-а +Е (и)д 1 1 - а с выхода интегратора 18 через аналоговый ключ 19 и сумматор 11 в течение интервала 1/2 д 1 действует на первом выходе устройства и на входе блока 12 преобразования частоты.Из приведенного описания работы устройства видно, что, начиная с момента времени= 1- д 1, через каждый интервал 1/2 , на первом выходе устройства и навходе блока 12 преобразования частоты появляется и существует в течение длительности времени 1/2 д 1 значение вычисленного результата вэаимокорреляционной функции между сигналами Г,э и й 4 , которое описывается выражениемн 1 аГ е 1 и-О-Яу-м-ж),где Ф.,( Ф"-дС1 2 Т - г Д 1(0 у 2 п 2; 0 ю и - 1 Т 2 Тнаибольшая длительность сигналовйи Есовпадающим с точностью до постоянного множителя с результатом, полученным после вычисления корреляционного интегралапо формуле прямоугольников или трапеций, если только в последнем в двараЗа уменьшить масштаб по оси 1,а следовательно,. и по оси)После восстановления прежнего (илизаданного) значения средней частотыспектра сигнала у в блоке 12 преобразования частоты на втором выходеустройства образуется следующееокончательное значение результатау 1 = А Е Е (и-М -1)ь 1(3 +1) д(АО)который является приближенным вычислением корреляционного интегралауж) =." Г(Т-У;).,( -Г) аР,если тдлько в последйем в два разауменьшить масштаб по осям т. иПриведенное описание работы устройства справедливо и тогда, когда= -",(-).При выполнении условия й (1)- й 2(1) = Г можно соедийить междусобой входы масштабного блока 1,а также его первый и второй выходыи переключатель П 2 поставить в положение два.При вычислении интеграла сверткиу( О = Х й(с) г (к-.с) . аснЕобходимо разомкнуть переключательП 2 и замкнуть переключателИ П 1 иП 3,Таким образом, введение новыхэлементов и блоков, устанонлениенОвых связей выгодно отличаетпредлагаемое устройство от известных, таккак дает возможность наряду с вычислением интеграла свертки обеспечитьвычисление корреляционных функций,и,сЛедовательно, расширить функциональные возможности устройства и, классрешаемых с его помощью задач. Врезультате существенно расширяетсяобласть применения и отпадает необходимость в разработке целого рядаодноканальных и многоканальных устройств, с помощью которых могут бытьрешены только частные задачи, чтоулучшает технико-экономические показатели при изготовлении и эксплуатации устройства.формула изобретенияУстройство для вычисления свертки функций, содержащее масштабный блок, первый и второй нходы которого являются соответствующими входами устройства, а первый выход соединен со входом первой линии задержки, выполненной в виде последовательно соеди-. ненных Ячеек памяти, блок управления, первый выход которого соединен со вхо дом генератора импульсов, первый выход которого подключен к управляюим входам ячеек памяти первой линииадержки, распределитель импульсон,блок умножения, первый сумматор, ныход которого соединен с первым входом блока преобразования частоты, 5 о т л и ч а ю щ е е с я тем, что, сцелью расширения функциональных возможностей за счет вычисления корреляционных функций, в устройство введены генератор тактовых импульсов,четыре линии задержки, выполненныев виде последовательно соединенныхячеек памяти, три блока ключей, двасумМатора, два интегратора, четыреключа, дополнительный распределительимпульсов и три переключателя, приэтом информационные входы первогоблока ключей соединены с выходамисоответствующих ячеек первой линиизадержки, а управляющие входы первого блока ключей соединены со нто рымвыходом: блока управления, третий и четвертый выходы которого подключены соответственно ко нходу генератора тактовых импульсов и ктретьему входу масштабного блока, 25 второй выход которого соединен с первым входом блока преобразованиячастоты, первый и третий выходы масштабного блока подключены соответственно к неподвижным контактам соотрет стненно первого и второго переключателей, подвижные контакты которыхподключены соответственно к выходувторой и ко входу третьей линии задержки, ко входу четвертой линии заЗ 5 держки и к подвижному контакту третьего переключателя, первый и второйнеподвижные контакты которого соединены соответственно с выходом первойи пятой линий задержки, вход последней подключен к третьему выходу масштабного блока, выходы генераторатактовых импульсов соединены соответственно со входом распределителяимпульсов и со вторым входом генератора импульсов, второй выход котоф 5 рого подключен к управляющим входамячеек четвертой и пятой линий задержки, выходы первого, второго и третьего блока ключей соединены соответственно с соответствующими входами50 ячеек второй линии задержки с соответстнующими входами второго сумматора и соответствующими входами третьего сумматора,ныходы распределителя импульсов подключены к соответствующим 55 управляющим входам второго и третьего блоков ключей, информационные входы которых соединены с выходами соответстнующих ячеек третьей и четвертой линии задержки, выходы второго60 и третьего сумматора подключены ксоответствующим входам блоков умножения, выход которого соединен с информационными входами первого и второго ключа, выходы которых подклю 65 чены соответственно ко входам перво13 742969 14 Заказ 3620/16 И 1 Подписно ул. Проектная,го и второго интегратора, выходы которых соединены с информационными входами соответственно третьего и четвертого ключа, выходы которых подключены соответственно к первому и второмувходам первого сумматора, управляющие входы ключей и интеграторов соединены с соответствующими выходамидополнительного распределителя им-,пульсов, вход которого соединен лиал ППП Патентф, г. У с последним выходом распределителяимпульсов.Источники информации,принятые во внимание при экспертизе1. Жовинский В,Н., Арховский В.ф.Корреляционные устройства. И.,Энергия, 1974, с. 147.2, Авторское свидетельство СССРпо заявке 9 2490260/1 В,кл. 6 06 С 7/19, 1977.

СмотретьЗаявка

2587586, 06.03.1978

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ОСИПЕНКО ВИКТОР ГАВРИЛОВИЧ

МПК / Метки

МПК: G06G 7/19

Метки: вычисления, свертки, функций

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/7-742969-ustrojjstvo-dlya-vychisleniya-svertki-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления свертки функций</a>

Предыдущий патент: Коррелятор

Следующий патент: Логарифмический усилитель

Случайный патент: Роторный пленочный испаритель