Специализированный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

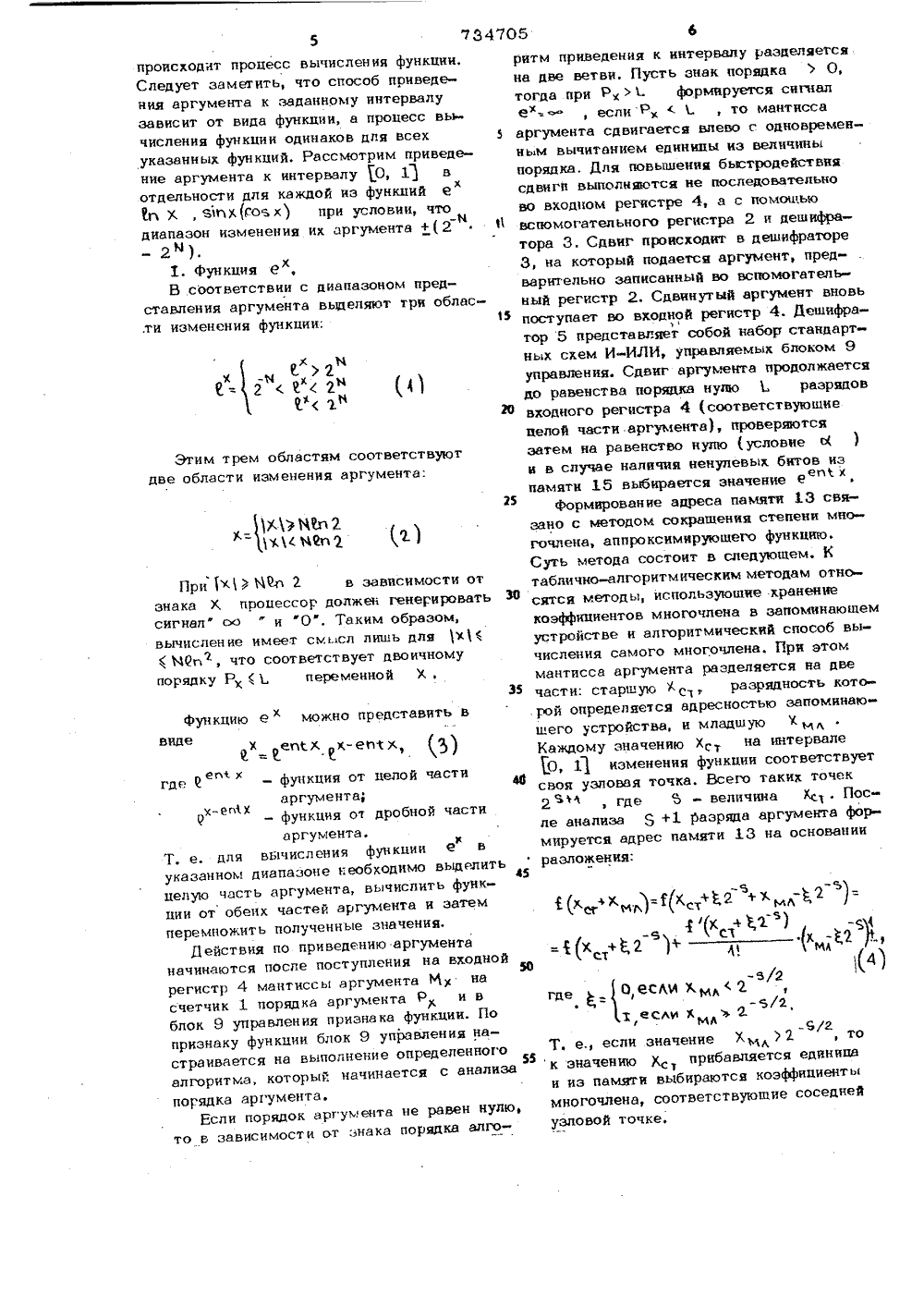

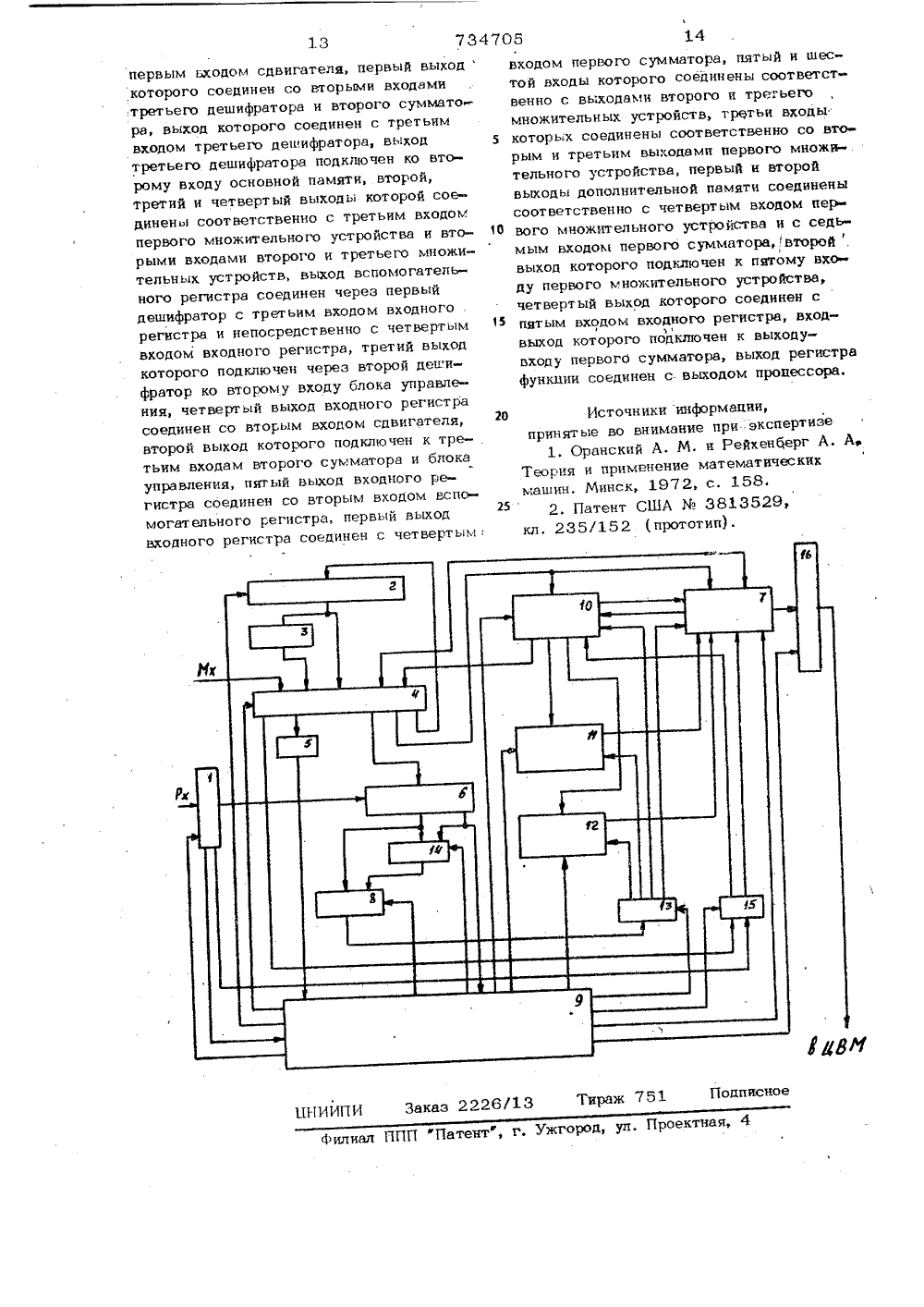

Союз СоветскихСоциалистическихРеспубтткк ОП ИСАНИ ЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Дополнительное к авт. свил-ву 22)Заявлено 14.12.77 (21) 2553887/18 24(51) М 6 Г 15/3 присоединением заявки ВщдэфстиюньЮ кемвте ССь.Р делам лзебретеллй и втарнтлй3) Ррнорите Д 1( 681.1 88,8) Опубликовано 15.05.80. Бюллетень1 Дата опубликования описания 18.05,802) Авторы изобретен ский орден В. И. Уль ин) Заявитель 54) СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕСС ост Изобретение относится к вычислительной технике и может быть использованокак в качестве автономного функционального преобразователя, так и в качествепериферийного устройства спепивлизиро,ванных и универсальных ЦВМ для вычисления функций: еф, Ьз к, Мох,Известны процессоры для вычисленияэлементарных функпий табличного типана основе постоянного запоминаюшегоустройства (ПЗУ), в состав которых вхотОдит регистр аргументе, в качестве которого используется регистр числа ПЗУ 1Недостаток известного пропессора -значительный объем памяти,1 БНаиболее близким по технической сущи и к изобретению является спепивлизированный процессор для вычисления элементарных функций (цифровой интерполятор высокого порядка), содержащий вход Оной регистр, на первую группу входовкоторого подается аргумент, первая группа выходов входного регистра связанас первой группой входов множительного ина электротехнический инстит (Ленина) устройства, вторая группа выходов входного регистра связана со входами постоянного звпомннвюшего устройства (ПЗУ) в котором хранятся значения узловых точек функпии, сумматор, первая группа входов которого связана с выходами множительного устройства, вторая группа входов множительного устройства связана с выходами второй группы вентилей выходы сумматора соединены с первой группой входов регистра функции, выходы ПЗУ связаны со входами второй группы вентилей, регистр функции, выходы которого соединены с первой группой входов первой группы вентилей, с второй группой входов выходного буфера, выходной буфер, выход которого соединен со входом ЦВМ, блок управления, выходы которого связаны со входами регистра функции, первой, второй групп вентилей, входного регистра выходного буфера 21 .Недостаток этого процессора - низкое быстродействие, связанное с тем, что вычисление функции ведется ио схеме3 7347Горнера. Такой способ вычисления функпии требует число умножений равнымстаршей степени многочлена. Поэтомупри повышенных требованиях к точностивычисления (50-60 двоичных разрядови более) время нахождения функции становится недопустимо большим.Цель изобретения - повышение быстродействия.Поставленная пель достигается тем, 10что в специализированный процессор, содержащий входной регистр, первое множительное устройство, первый сумматор,основную память, регистр функции, счетчик порядка, причем первый выход первого сумматора соединен с первым входом регистра функции, второй вход которого подключен к первому выходу блокауправления, первый вход счетчика порядкасоединен со входом процессора, первый 20выход входного регистра соединен с первым входом первого множительного устройства, первый выход которого соединенс первым входом первого сумматора,второй вход которого подключен к первому выходу основной памяти вход процессора соединен с первым входом входного регистра, второй вход которого подключен к второму выходу блока управления,введены вспомогательный регистр, деши 30фраторы, сдвигатель, второй сумматор,второе и третье множительные устройства,дополнительная память, причем третийвыход блока управления соединен с третьим входом первого сумматора, четвер 35тый и пятый выходы - соответственно спервыми входами основной и дополнительной памяти, шестой, седьмой и восьмойвыходы - соответственно с первыми входами второго и третьего множительных 40устройств и со вторым входом первогомножительного устройства, девятый и десятый выходы - соответственно с первы-,ми входами второго сумматора и третьегодешифратора, одиннадпатый выход - с45первым входом вспомогательного регистра,двенадцатый выход - с вторым входомсчетчика порядка, первый выход которогосоединен с первым входом блока управления, второй выход счетчика порядка сое 50динен со вторым входом дополнительнойпамяти, третий вход которой подключенко второму выходу входного регистра,третий выход счетчика порядка соединенс первым входом сдвигателя, первый55выход которого соединен со вторыми входами. третьего дешифратора и второго сумматора, выход которого соединен с тре 05 атьим входом третьего дешифратора, выход третьего дешифратора подключен ковторому входу основной памяти, второй,третий и четвертый выходы которой соединены соответственно с третьим входомпервого множительного устройства и вторыми входами второго и третьего множительных устройств, выход вспомогательного регистра соединен через первыйдешифратор с третьим входом входногорегистра и непосредственно с четвертымвходом входного регистра, третий выходкоторого подключен через второй дешифратор ко второму входу блока управления,четвертый выход входного регистра соединен со вторым входом сдвигателя,второй выход которого подключен к третьим входам второго сумматора и блокауправления, пятый выход входного регистра соединен со вторым входом вспомогательного регистра, первый выходвходного регистра соединен с четвертымвходом первого сумматора, пятый и шестой входы которого соединены соответственно с выходами второго и третьегомножительных устройств, третьи входы которых соединены соответственно со вторым и третьим выходами первого множительного устройства, первый и второйвыходы дополнительной памяти соединенысоответственно с четвертым входом первого множительного устройства и сседьмьм входом первого сумматора, вто-.рой вьход которого подключен к пятомувходу первого множительного устройства,четвертый выход которого соединен спятым входом входного регистра, входвыход которого подключен к выходувходу первого сумматора, выход регистрафункции соединен с выходом процессора.Блок схема специализированного процессора представлена на чертеже.Процессор содержит счетчик 1 порядка,вспомогательный регистр 2, первый дешифратор 3, входной регистр 4, второйдешифратор 5, сдвигатепь 6, первыйсумматор 7, третий дешифратор 8, блок9 управления, первое 10, второе 11 итретье 12 множительные устройства,основная память 13, второй сумматор14, деполнительная память 15, регистр16 функпии,Процессор работает следующим образом,Вычисление функции в процессоре разделяется на два этапа. На первом этапедиапазон изменения аргумента функциисводится к интервалу 0, 11, Затемпроисходит процесс вычисления функции,Следует заметить что способ приведения аргумента к заданному интервалузависит от вида функции, а процесс вььчисления функции одинаков для всех 5указанных функций, Рассмотрим приведение аргумента к интервалу 0 11 вотдельности для каждой из функций ЕЬ Х, бюх(Со х) при условии, что-Ндиапазон изменении их аргумента + (22 М)1. функция Е",В соответствии с диапазоном представления аргумента выделяют три облас.ти изменения функции:35Этим трем областям соответствуютдве области изменения аргумента:25При Ьэ ЙЬ 2 в зависимости отзнака Х процессор должен генерировать ЗОсигнал" оои "0". Таким образом,вычисление имеет смысл лишь для х( ЙРо, что соответствует двоичномупорядку Р 1. переменной Х .35Функцию е можно представить вео, - е и,где Ремх- функция от целой частиМаргумента;Р - функция от дробной частиХ Харгумента.Т. е. для вычисления функции е в указанном диапазоне необходимо выдлить45 целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные значения.Действия по приведению аргумента начинаются после поступления на входной регистр 4 мантиссы аргумента йх на счетчик 1 порядка аргумента Рх и в блок 9 управления признака функции. По признаку функции блок 9 управления настраивается на выполнение определенного алгоритма, который начинается с анализа порядка аргумента.Если порядок аргумента не равен нулю, то в зависимости от знака порядка алгоритм приведения к интервалу разделяетсн на две ветви, Пусть знак порядка ) О, тогда при Р- формируется сигнал ех если Рто мантисса аргумента сдвигаетса влево с одновременным вычитанием единицы из величины порядка. Для повышения быстродействия сдвиги выполнаютса не последовательно во входном регистре 4, а с помощью вспомогательного регистра 2 и дешифратора 3. Сдвиг происходит в дешифраторе 3, на который подаетса аргумент, предварительно записанный во вспомогательный регистр 2, Сдвинутый аргумент вновь поступает во входной регистр 4. Дешифратор 5 представляет собой набор стандартных схем И-ИЛИ, управляемых блоком 9 управления. Сдвиг аргумента продолжаетса до равенства порядка нулю 1. разрядов входного регистра 4 соответствующие целой части аргумента, проверяются затем на равенство нулю (условие о ) и в случае наличия ненулевых битов из памяти 15 выбирается значение 6ео хФормирование адреса памяти 13 связано с методом сокрашении степени многочлена, аппроксимирующего функцию, Суть метода состоит в следующем. К таблично-алгоритмическим методам относятся методы, использующие хранение коэффициентов многочлена в запоминающем устройстве и алгоритмический способ вычисления самого многочлена. При этом мантисса аргумента разделяется нв две части: старшую Хс., разрядность кото.рой определяется адресностью запоминаю щего устройства, и младшуюКаждому значению Хс на интервале 0, 11 изменения функции соответствует своя узловая точка. Всего таких точек 2 "где Ь - величина ХсПосле анализа Я +1 5 азряда аргумента формируетса адрес памяти 13 на основании разложения: х .:Г(к 2 . -2 ). --62Т. е., если значение Х ) 1 , ток значению Х прибавляется единицати из памяти выбираются коэффициентымногочлена, соответствующие соседнейузловой точке,734705 симируются рядом Тейлора одинаковойстепени. Последовательность действийпо вычислению многочлена может бытьизбрана разная,Для повышения быстродействия в предлагаемом процессоре используются еше дополнительно два малоразрядных множительных устройства. Зтопозволяет распараллелить, процесс вычисления функции. Последовательностьдействий по вычислению многочлена пя Отой степени: Специализированный процессор, содерждший входной регистр, первое множительное устройство, первый сумматор, основную память, регистр функции, счетчикпорядка, причем первый выход первогосумматора соединен с первым входом регистра функции, второй вход которогоподключен к первому выходу блока управления, первый вход счетчика порядкасоединен со входом процессора, первыйвыход входного регистра соединен с первым вкодом первого множительного устройства, первый выход которого соединенс порвьм входом первого сумматора, второй вход которого подключен к первомувыходу основной памяти, вход процессорасоединен с первым входом входного регистра, второй вход которого подключенк второму выходу блока управленияо тл и ч а ю ш и й с я тем, что, с цельюповышения быстродействия, в процессорвведены вспомогдтельн й регистр, дешифрдторы, сдвигатель, второй сумматор,второе и гретье множительные устройства,дополнительная память, причем третийвыход блока управления соединен с третьимвходом перво го с умматора, чет верт ый ипятый выход - соответственно с первымивходами основной и доголцительной памяти, шестой, седьмой и восьмой выходы -соответственно с первь.ми входами второго и третьего множительного устройстви со вторым входом первого множительного устройства, девятый и десятый выходы - соответственно с первыми входами второго сумматора и третьего дещифрдтора, одиннадцатый выход с первым входом вспомогательного регистра, двенадцдтйй выход - со вторь м входом счетчика порядка, первый выход которого соединен с первым входом блока управления, второй выход счетчика порядка соединен со вторь,м входом дополнительной памяти, третий вход которой подключен ко второму выходу входного регистра, третий выход счетчика порядка соединен с где Е (,х) - вычисляемая функция;Ь Ь , Ь - коэффициент, многочленд;о,Х - аргумент,Степень многочлена выбрана из требований по точности вычисления 1 (.х)(разрядность аргумецтд 50-60 разрядов) .Сначала на первом множительном2устройстве вычисляется значение х ипараллельно с ним на втором множительном устройстве 11 значение Ь Х, На двтором этапе вычисления работают параллельно все множительнь,е устройства ивторой сумматор 14: на первом множительном устройстве 10 вычисляется3ца втором 11 - Ь, х, на третьем 12 - що2.4на втором сумматоре 14 - сумма Ь+ Ь к,3 атем одновременно находятся значения Ь х на нервом множительном3устройстве 10, Ьбх ца третьем множительном устройстве 12 ЬЬХ Ь ХЬвЧ,на втором сумматоре 14.Причем первь;й сумматор 7 формируетсумму во время работь первого множительного устройства 10, Последуюдую Фоработу процессора составляет нахождениевсей суммы в скобке формулы ( 18), ееумножение на Х в первом множительном устройстве 10 и вычислснпе окопчательного результата. 45Так как первое множительное у тройство 10 обрабатывает огердндь, полной разрядности, д остдльн. е мцожигельн. е устройства малордзрядцые и работают параллельно с первым, то время умцожения определяется только временем работь.первого множительного устройства 10.Время вычисления функции в предлагаемом процессоре составляет Сигналы для управления работой Всехблоков процессора поступают из блока 9 управления, который представляет собой конечный автомат Мили или Мура,Уменьшение времени вычисления в предла гаемом процессоре составляет 1,1 мкс или около 50% по отношению времени вычисления функции в известном при увеличен ни а и пдрат урн ых затрат н а 15-20%. Формула изобретен ия734705 13 первым входом сдвигателя, первый выходкоторого соединен со вторыми входами;третьего дешифратора и второго сумматора, выход которого соединен с третьимвходом третьего дешифратора, выходтретьего дешифратора подключен ко второму входу основной памяти, второй,третий и четвертый выходы которой соединены соответственно с третьим входомпервого множительного устройства и вторыми входами второго и третьего множительных устройств, выход вспомогательного регистра соединен через первыйдешифратор с третьим входом входногорегистра и непосредственно с четвертымвходом входного регистра, третий выходкоторого подключен через второй дешифратор ко второму входу блока управления, четвертый выход входного регистрасоединен со вторым входом сдвигателя,второй выход которого подключен к третьим входам второго сумматора и блокауправления, пятый выход входного регистра соединен со вторым входом вспомогательного регистра, первый выходвходного регистра соединен с четвертым; 14входом первого сумматора, пятый и шестой входы которого соединены соответственно с выходами второго и трегьегомножительных устройств, третьи входы 5 которых соединены соответственно со вторым и третьим выходами первого множи-.тельного устройства, первый и второйвыходы дополнительной памяти соединенысоответственно с четверть 1 м входом пер О вого множительного устройства и с седьмым входом первого сумматоравторойвыход которого подключен к пятому входу первого множительного устройства,четвертый выход которого соединен спятым входом входного регистра, вход 1выход которого подключен к выходувходу первого сумматора, выход регистрафункции соединен с. выходом процессора,20 Источники информации,принятые во внимание при экспертизе1. Оранский А. М, и Рейхенберг А, АТеория и применение математическихмашин, Минск, 1972, с, 158.2. Патент США3813529,кл. 235/152 (прототип),

СмотретьЗаявка

2553887, 14.12.1977

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, ВОДЯХО АЛЕКСАНДР ИВАНОВИЧ, НЕГОДА ВИКТОР НИКОЛАЕВИЧ, ПУЗАНКОВ ДМИТРИЙ ВИКТОРОВИЧ, ШАЛЯПИН ВЛАДИМИР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 17/10, G06F 19/00

Метки: процессор, специализированный

Опубликовано: 15.05.1980

Код ссылки

<a href="https://patents.su/7-734705-specializirovannyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Специализированный процессор</a>

Предыдущий патент: Устройство для перебора сочетаний

Следующий патент: Цифровой синтезатор синусоидальнокосинусоидальных сигналов

Случайный патент: Автомат для сборки и сварки угловых швов деталей таврового сечения