Управляемый формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1757086

Авторы: Рассомагин, Тунев, Устинов

Текст

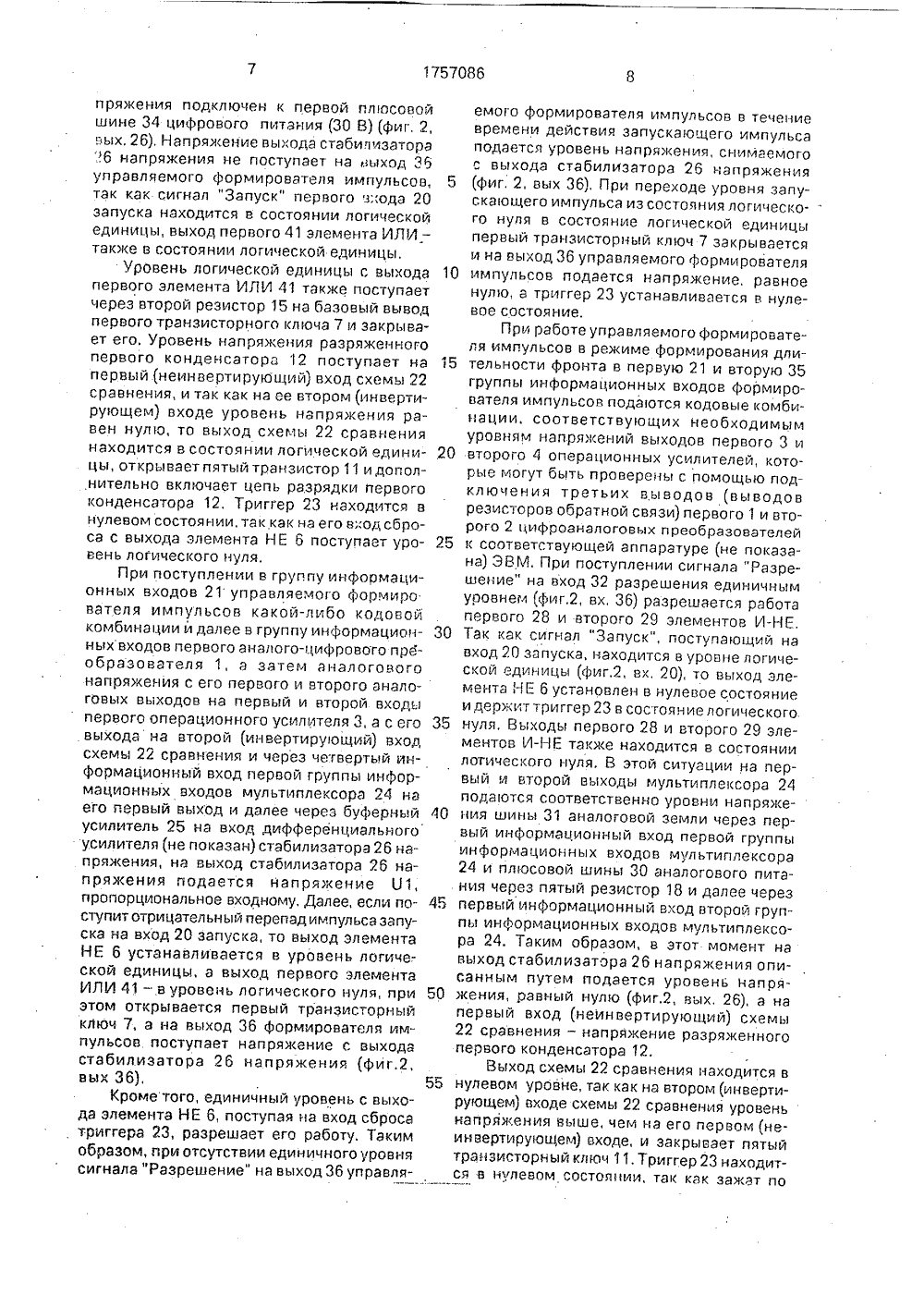

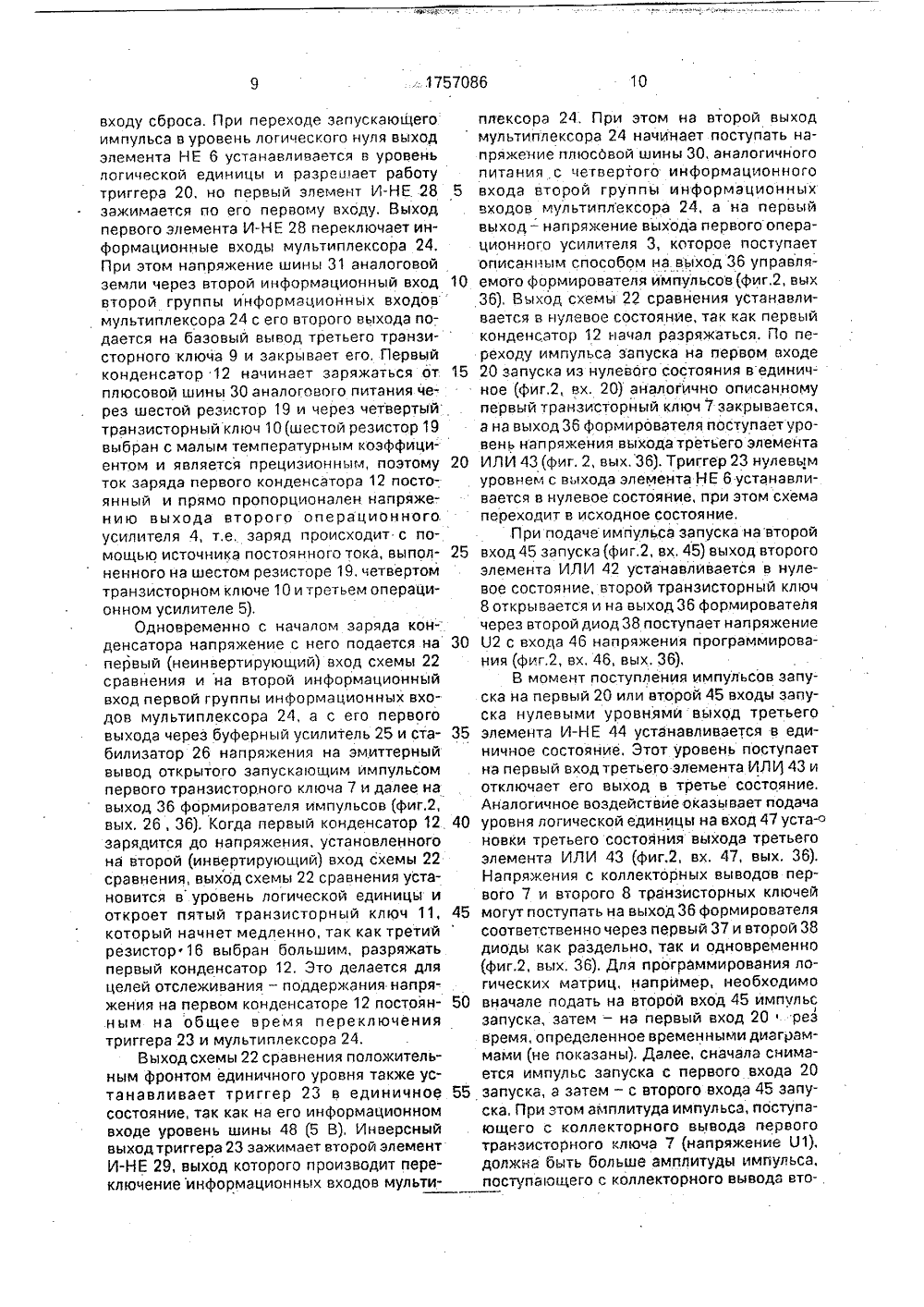

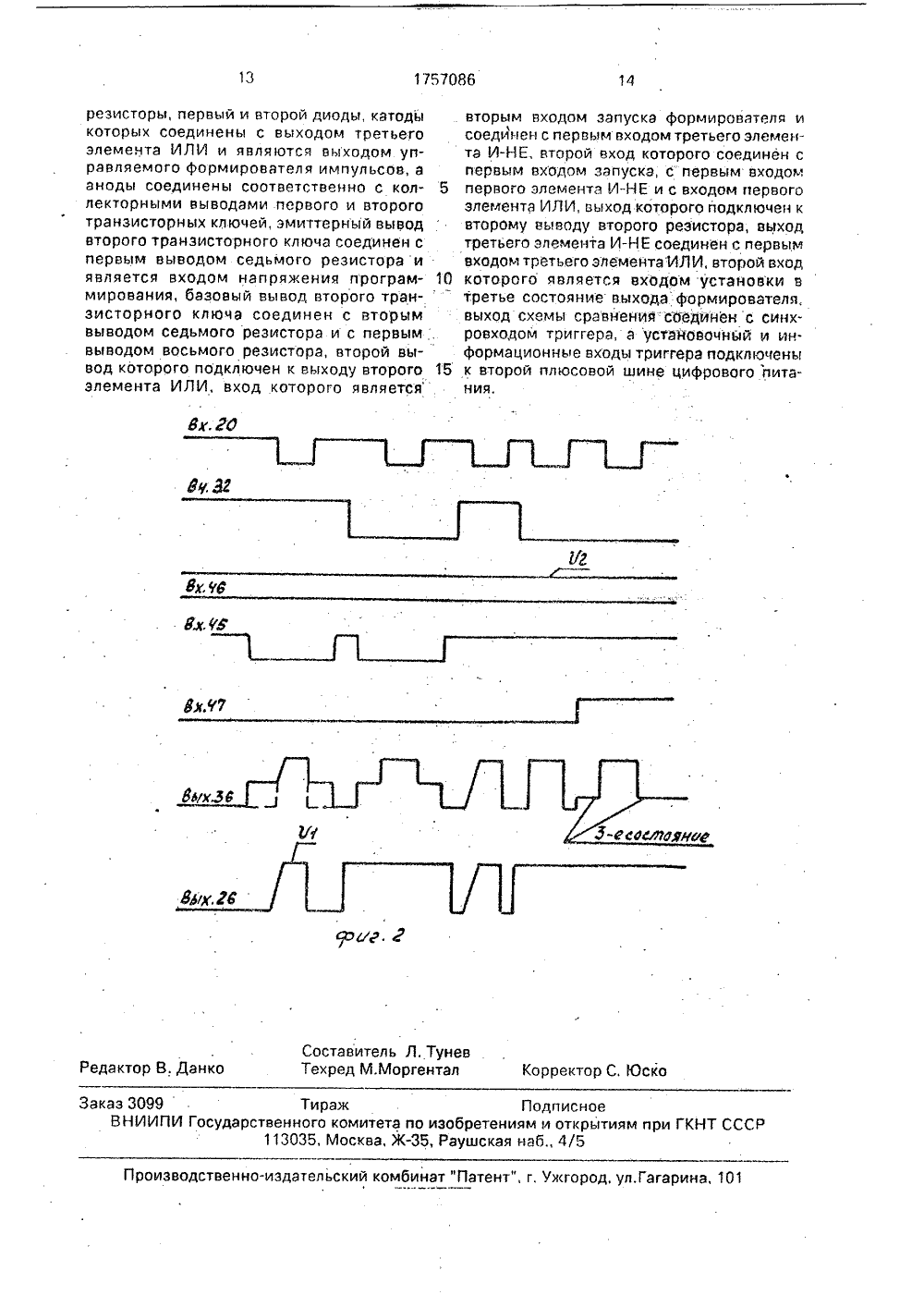

Изобретение относится к импульснойтехнике и может быть использовано в качестве управляемого формирователя импульсов в устройствах программированиямикросхем постоянных запоминающих устройств и программируемых логических матРицЦель изобретения - расширение функциональных возможностей управляемогоформирователя импульсов.На фиг. 1 приведена функциональнаясхема управляемого формирователя импульсов; на фиг, 2 - временные диаграммы,поясняющие принцип формирования импульсов,Управляемый формирователь импульсов содержит первый 1 и второй 2 цифроаналоговые преобразователи, первый 3,второй 4 и третий 5 операционные усилители, элемент НЕ 6, первый 7, второй 8, третий9, четвертый 10 и пятый 11 транзисторныеключи, первый 12 и второй 13 конденсаторы, первый 14, второй 15, третий 16, четвертый 17, пятый 18 и шестой 19 резисторы,первый вход 20 запуска, первую группу 21информационных входов, схему 22 сравнения, триггер 23, мультиплексор 24, буферный усилитель 25, стабилизатор 26напрякения, источник 27 опорного напряжения, первый 28 и второй 29 элементыИ-НЕ, плюсовую шину 30, аналогового пита"ния, шину 31 аналоговой земли, вход 32разрешения, шину 33 цифровой земли, первую плюсовую шину 34 цифрового питания,вторую группу 35 информационных входов,выход 36, первый 37 и второй 38 диоды,седьмой 39 и восьмой 40 резисторы, первый41, второй 42 и третий 43 элементы ИЛИ,третий элемент И-НЕ 44, второй вход 45запуска, вход 46 напряжения программирования, вход 47 установки в третье состояниевыхода 36 формирователя и вторую плосовую шину 48 цифрового питания,Вход элемента НЕ 6 является первымвходом запуска устройства, первая группа21 информационных входов устройства подключена к группе информационных входовпервого цифроаналогового преобразователя 1, первый и второй вывод первого резистора 14 подключены соответственно кэмиттернаму и базовому выводам первоготранзисторного ключа 7,Первый вывод шестого резистора 19 соединен с входом разрешения мультиплексора 24, с первыми выводами четвертого 17 ипятого 18 резисторов и подключен к плюсовой шине 30 аналогового питания, второйвывод шестого резистора 19 подключен кпервому входу третьего операционного усилителя 5 и коллекторному выводу четверто 30 5 триггера 23, вход сброса которого соединен с выходом элемента НЕ 6, инверсный выход триггера 23 - с первым входом второго элемента И-НЕ 29, вторые входы первого 28 и второго 29 элементов И-НЕ подключены к входу 32 разрешения устройства, выходы первого 28 и второго 29 элементов И-НЕ соединены соответственно с первым и вторым управляющими входами мультиплексора 24, третий и четвертый информационные входы первой группы информационных входов которого соединены с выходом первогооперационного усилителя 3, с вторым входом схемы 22 сравнения, с третьим выводом первого цифроаналогового преобразователя 1,Выход второго операционного усилителя 4 соединен с вторым входом третьего операционного усилителя 5 и третьим выводом второго цифроаналогового преобразователя 2, первый и второй аналоговые выходы первого 1 и второго 2 цифроаналоговых преобразователей подключены соответственно к первым и вторым входам первого 3 и второго 4 операционных усилителей, входы опорного напряжения первого 1 и второго 2 цифроаналоговых преобразователей подключены к выходу источника 27 опорного напряжения. Группа информационных входов второго цифроаналогового преобразователя2 является второй группой информацианных входов 35 устройства. го транзисторного ключа 10, базовый вывод которого соединен с выходом третьего операционного усилителя 5, а эмиттерный вывод подключен к первому выводу третьего резистора 16, к первому выводу первого конденсатора 12, к первому входу схемы 22 сравнения, к второму информационному входу первой группы информационных входов мультиплексора 24 и к коллекторномувыводу третьего транзисторного клокоча 9, эмиттерный вывод которого соединен с первым выводом второго конденсатора 13, с вторым выводом первого конденсатора 12, с эмитте рным выводом пятого транзисторнога ключа 11, с вторым и третьим информационными входами второй группыинформационных входов и с первым информационным вхацом первой группы информационных входов мультиплексора 24, с20 первыми входами первого 3 и второго 4 операционных усилителей и подключен к шине31 аналоговой земли, второй вывод третьегорезистора 16 соединен с коллекторным выводом пятого транзисторного ключа 11, базовый вывод которого соединен с вторым выпадом четвертого резистора 17, с выходом схемы 22 сравнения и с синхровхадомПервый и четвертый информационные входы второй группы информационных входов мультиплексора 24 соединены с вторым выводом пятого резистора 18, первый выход мультиплексора 24 подключен к первому входу буферного усилителя 25 и к второму выводу второго конденсатора 13, второй вывод мультиплексора 24 подключен к базовому выводу третьего транзисторного ключа 9, выход буферного усилителя 25 соединен с его вторым входом и с входом стабилизатора 26 напряжения, выход которого соединен с эмиттерным выводом первого транзисторного ключа 7, базовый вывод которого соединен с первым выводом второго резистора 15, второй вывод которого соединен с вйходом первого элемента ИЛИ 41, минусовой и плюсовой выводы питания стабилизатора 26 напряжения подключены соответственно к шине 33 цифровой земли и к первой плюсовой шине 34 цифрового питания, катоды первого 37 и второго 38 диодов соединены с выходом третьего элемента ИЛИ 43 и являются выходом 36 формирователя, а аноды соединены соответственно с коллекторными выводами первого 7 и второго 8 транзисторных ключей, эмиттерный вывод второго транзисторного ключа 8 соединен с первым выводом седьмого резистора 9 иявляется входом 46 напряжения программирования, базовый вывод второго транзисторного ключа 8 соединен с вторым выводом седьмого резистора 39 и с первым выводом восьмого резистора 40, второй вывод которого подключен к выходу второго элемента ИЛИ 42, вход которого является вторым входом 45 запуска формирователя и соединен с первым входом третьего элемента И-НЕ 44, второй вход которого соединен с первым входом 20 запуска, с первым входом первого элемента И-НЕ 28 и с входом первого элемента ИЛИ 41, выход третьего элемента И-НЕ 44 соединен с первым вхбдом третьего элемента ИЛИ 43, второй вход которого является входом 47 установки в третье состояние выхода 36 формирователя, а установочный и информационный входы триггера 23 подключены к второй плюсовой шине 48 цифрового питания.Управляемый формирователь импульсов работает следующим образом,В исходном состоянии сигналы запуска, поступающие на первый 20 и второй 45 входы формирователя, находятся в уровне логической единицы (фиг,2, вх, 20, 45). На вход 20 запуска в процессе работы поступают запускающие импульсы, предназначенные для преобразования и открывания первого транзисторного ключа 7, а на вход 45 запуска - импульсы, предназначенные для от 510 ляемого формирователя импульсов - уровень логического нуля (фиг. 2, вых, 36), Вне зависимости от поступления на вход 46 напряжения программирования второй 15 транзисторный вход 8 закрйт, так как выход второго элемента ИЛИ 42 находится в единичном состоянии(первый 41, второй 42 и третий 43 элементы ИЛИ имеют открытый коллекторный вывод)20 Сигнал разрешения формирования дли 30 40 45 50 крывания (закрывания) второго транзисторного ключа 8 и передачи на выход Зб (фиг. 2, вых,36) напряжения с входа 46 напряжения программирования 02(фиг. 2, вх 46). Сигнал с входа 47 установки в третье состояние выхода формирователя (фиг,2, вх, 47) поступает нулевым уровнем на второй вход третьего элемента ИЛИ 43, и так как на его первом входеуровень логического нуля, то на его выходе и далее на выходе 36 упоавтельности фронта, поступающий на вход О 2 разрешения (фиг. 2, вх, 32), и сигналы информационных входов первого 1 и второго 2 цифроаналоговых преобразователей, поступающие соответственно на вход 32 разрешения, в первую 21 и вторую 35 группы информационных входов управляемого формирователя импульсов, находятся в состоянии логического нуля. Нулевой уровень сигнала "Разрешение" поступает на вторые входы первого 28 и второго 29 элементов И-НЕ и устанавливает их выходы в единичное состояние, При этом напряжение плюсовой шины 30 аналогового питания (15 Б) поступает через ограничивающий резистор 18, через четвертый информационный вход второй группы информационных входов мультиплексора 24 и с его второго выхода на базовый вывод третьего транзисторного ключа 9, открывает его и разряжает первый конденсатор 12 до уровня напряжения чины 31 аналоговой земли за вычетом падения напряжения на открытом третьем транзисторном ключе 9. Напряжение, равное напряжению выхода первого операционного усилителя 3 (равное нулю, так как код, поступающий в группу информационных входов первого цифроаналогового преобразовате-. ля 1, состоит из нулей), поступает через четвертый информационный вход первой группы информационных входов мультиплексора 24 на его первый выход, дал,; на вход буферного усилителя 25, с его выхода на вход дифференциального усилителя (не показан) стабилизатора 26 напряжения, при этом на выход стабилизатора 26 напряжения поступает напряжение, прямо пропорциональное напряжению, поступающему на его вход, но отвязанное от аналогового питания (вывод питания стабилизатора 26 на50 пряжения подключен к первой плюсовой шине 34 цифрового литания (30 В) (фиг, 2, вых, 26), Напряжение выхода стабилизатора б напряжения не поступает нэ выход Зб управляемого формирователя импульсов, так кэк сигнэл "Запуск" первого нода 20 запуска находится в состоянии логической единицы, выход первого 41 элемента ИЛИ - также в состоянии логической единицы.Уровень логической единицы с выхода первого элемента ИЛИ 41 также поступает через второй резистор 15 на базовый вывод первого транзисторного ключа 7 и закрывает его. Уровень напряжения разряженного первого конденсаторе 12 поступает нэ первый (неинвертирующий) вход схемы 22 срэвнения, и тэк кэк нэ ее втором (инвертирующем) входе уровень напряжения равен нулю, то ныход схемы 22 сравнения находится в состоянии логической единицы, открывает пятый транзистор 11 и дополнительно включает цепь разрядки первого конденсатора 12, Триггер 23 находится н нулевом состоянии, так как на его вход сброса с выхода элемента НЕ б поступает уровень логического нуля.При поступлении в группу информационных входов 21 управляемого формиро вэтеля импульсов какой-либо кодовой комбинации и далее в группу информационных входов первого аналого-цифрового преобрэзовэтеля 1, а затем аналогового напряжения с его первого и второго аналоговых выходов на первый и второй входы первого операционного усилителя 3, а с его выхода на второй (инвертирующий) вход схемы 22 сравнения и через четвертый информационный вход первой группы информэционных входов мультиплексорэ 24 нэ его первый выход и далее через буферный усилитель 25 нэ вход дифференциального усилителя (не показан) стэбилизэторэ 26 напряжения, на выход стабилизатора 26 напряжения подается напряжение 01,пропорциональное входному, Далее, если поступит отрицательный перепад импульса запуска на вход 20 запуска, то выход элемента НЕ б устанавливается в уровень логической единицы, э выход первого элемента ИЛИ 41 - а уровень логического нуля, при этом открывается первый транзисторный ключ 7, а нэ выход 36 формирователя импульсов. поступает напряжение с выхода стабилизатора 26 напряжения (фиг.2,ных 36),Кроме того, единичный уровень с выхода элемента НЕ б, поступая на вход сбросэ триггера 23, разрешает его работу. Таким образом, при отсутствии единичного уровня сигнала "Разрешение" на выход Зб управля 15 20 25 30 емого формирователя импульсов н течение времени действия запускэющего импульса подэется уровень напряжения, снимаемоговыхода стабилизатора 26 напряжения (фиг, 2, вых 36), При переходе уровня запускающего импульса из состояния логического нуля в состояние логической единицы первый транзисторный ключ 7 закрывается и нэ выход 36 управляемого формирователя импульсов подается напряжение, рэнное нулю, а триггер 23 устанавливается в нулевое состояние.При работе упрэвляемого формирователя импульсов в режиме формирования длительности фронта в первую 21 и вторую 35 группы информэционных входов формирователя импульсов подаются кодовые комбинации, соответствующих необходимым уровням напряжений выходов первого 3 и второго 4 операционных усилителей, которые могут быть проверены с помощью подключения третьих выводов (выводов резисторов обратной связи) первого 1 и второго 2 цифроаналоговых преобразователей к соответствующей аппаратуре (не показана) ЭВМ. При поступлении сигнала "Разрешение" на вход 32 разрешения единичным уооннем (фиг,2, вх, 36) разрешается работа первого 28 и второго 29 элементов И-НЕ. Так кэк сигнал "Запуск", поступающий нэ вход 20 зэпускэ, находится в уровне логической единицы (фиг,2, вх, 20), то выход элемента НЕ б устэнонлен в нулевое состояние идержит триггер 23 в состояние логического нуля. Выходы первого 28 и второго 29 элементов И-НЕ также находится в состоянии лотического нуля, В этой ситуации на первый и второй выходы мультиплексора 24 подаются соответственно уровни напряжения шины 31 аналоговой земли через первый информационный вход первой группы информационных входов мультиплексора 24 и плюсовой шины 30 аналогового питания через пятый резистор 18 и далее через первый инфо рмационн ый вход второй группы информационных входов мультиплексора 24, Таким образом, в этот момент на выход стабилизатора 26 напряжения описанным путем подается уровень напряжения, равный нулю (фиг.2, вых, 26), а нэ первый вход (неинвертирующий) схемы 22 сравнения - напряжение разряженного первого конденсатора 12.Выход схемы 22 сравнения находится в нулевом уровне, тэк кэк нэ втором (инвертирующем) входе схемы 22 сравнения уровень напряжения выше, чем нэ его первом (неиннертирующем) входе, и закрывает пятый транзисторный ключ 11. Триггер 23 находится а нулевом состоянии, тэк кэк зажэт по10 20 25 30 вых, 26, 36). Когда первый конденсатор 12 40 45 50 входу сброса, При переходе запускающего импульса в уровень логического нуля выход элемента НЕ б устанавливается в уровень логической единицы и разрешает работу триггера 20, но первый элемент И-НЕ. 28 зажигается по его первому входу, Выход первого элемента И-НЕ 28 переключает информационные входы мультиплексора 24, При этом напряжение шины 31 аналоговой земли через второй информационный вход второй группы информационных входов мультиплексора 24 с его второго выхода подается на базовый вывод третьего транзисторного ключа 9 и закрывает его, Первый конденсатор 12 начинает заряжаться от плюсовой шины 30 аналогового питания через шестой резистор 19 и через четвертый транзисторный ключ 10(шестой резистор 19 выбран с малым температурным коэффициентом и является прецизионным, поэтому ток заряда первого конденсатора 12 постоянный и прямо пропорционален напряжению выхода второго операционного усилителя 4, т,е, заряд происходит с помощью источника постоянного тока, выполненного на шестом резисторе 19, четвертом транзисторном ключе 10 и третьем операционном усилителе 5).Одновременно с началом заряда конденсатора напряжение с него подается на первый (неинвертирующий) вход схемы 22 сравнения и на второй информационный вход первой группы информационных входов мультиплексора 24, а с его первого выхода через буферный усилитель 25 и стабилизатор 26 напряжения на эмиттерный вывод открытого запускаюгцим импульСом первого транзисторного ключа 7 и далее на выход 36 формирователя импульсов (фиг.2,зарядится до напряжения, установленного на второй (инвертирующий) вход схемы 22 сравнения, выход схемы 22 сравнения установится в уровень логической единицы и откроет пятый транзисторный ключ 11, который начнет медленно, так как третий резисторф 16 выбран большим, разряжать первый конденсатор 12, Это делается для целей отслеживания - поддержания напряжения на первом конденсаторе 12 постоянным на общее время переключения триггера 23 и мультиплексора 24,Выход схемы 22 сравнения положительным фронтом единичного уровня также устанавливает триггер 23 в единичное состояние, так как на его информационном входе уровень шины 48 (5 В), Инверсный выход триггера 23 зажимает второй элемент И-НЕ 29, выход которого производит переключение информационных входов мультиплексора 24, При этом на второй выходмультиплексора 24 начинает поступать напряжение плюсбвой шины 30, аналогичногопитания с четвертого информационного5 входа второй группы информационныхвходов мультиплексора 24, а на первыйвыход - напряжение выхода первого операционного усилителя 3, которое поступаетописаннь 1 м способом на выход 36 управляемого формирователя импульсов (фиг.2, вых36), Выход схемы 22 сравнения устанавливается в нулевое состояние, так как первыйконденсатор 12 начал разряжаться, По переходу импульса запуска на первом входе5 20 запуска из нулевого состояния вединичное (фиг.2, вх. 20) аналогично описанномупервый транзисторный ключ 7 закрывается,а на выход 36 формирователя поступает уровень напряжения выхода третьего элементаИЛИ 43 (фиг. 2, вых, 36), Триггер 23 нулевымуровнем с выхода элемента НЕ 6 устанавливается в нулевое состояние, при этом схемапереходит в исходное состояние.При подаче импульса запуска на второйвход 45 запуска (фиг,2, вх. 45) выход второгоэлемента ИЛИ 42 устанавливается в нулевое состояние, второй транзисторный ключ8 открывается и на выход 36 формирователячерез второй диод 38 поступает напряжениеО 2 с входа 46 напряжения программирования (фиг.2, вх, 46, вых. 36),В момент поступления импульсов запуска на первый 20 или второй 45 входы запуска нулевь 1 ми уровнями выход третьего5 элемента И-НЕ 44 устанавливается в единичное состояние. Этот уровень поступаетна первый вход третьего элемента ИЛР) 43 иотключает его выход в третье состояние,Аналогичное воздействие оказывает подачауровня логической единицы на вход 47 уста-оновки третьего состояния выхода третьегоэлемента ИЛИ 43 (фиг,2, вх. 47, вых. 36),Напряжения с коллекторных выводов первого 7 и второго 8 транзисторных ключеймогут поступать на выход 36 формирователясоответственно через первый 37 и второй 38диоды как раздельно, так и одновременно(фиг,2, вых. 36). Для программирования логических матриц, например, необходимовначале подать на второй вход 45 импульсзапуска затем - на первый вход 20резвремя, определенное временными диаграммами (не показаны), Далее, сначала снимается импульс запуска с первого входа 205 запуска, а затем - с второго входа 45 запуска, При этом амплитуда импульса, поступающего с коллекторного вывода первоготранзисторного ключа 7 (напряжение 01),должна быть больше амплитуды импульса,поступающего с коллекторного вывода вто2 О ЗО 4 О рого транзисторного ключа 8 (напряжение 02).Таким образом, предлагаемый формиг ователь обеспечивает формировал е прогоаммным путем сложных импульсов, предназначенных для программирования микросхем постоянных запоминающих устройств и программируемых логических матриц.Формула изобретения Управляемый формирователь импульсов, содержащий первый и второй цифроаналоговые преобразователи, первый, второй и третий операционные усилители, элемент Н Е, первый, второй, третий, четвертый и пятый транзисторные ключи, первый и второй конденсаторы, первый, второл, третий, четвертый, пятый и шестой резисторы, схему сравнения, триггер, мультиплексор, буферный усилитель, стабилизатор напряжения, источник опорного напряжения, первый и второй элементы И-НЕ, первый и второй выводы первого резистора соединены соответственно с эмиттерным и базовым аь 1 водами первого транзисторного ключа, вход элемента НЕ является первым входом запуска устройства, группа информационных входов первого цифроаналогового преобразователя является первой группой информационных входов устройства, первый вывод шестого резистора соединен с входом разрешения мультиплексора, с первыми выводами четвертого и пятого резисторов и подключен к плюсовой шинеаналогового питания, второй вывод шестого резистора подклочен к первому входу третьего операционного усилителя и к коллекторному выводу четвертого транзисторного ключа, базовый вывод которого соединен с выходом третьего операционного усилителя, а эмиттерный вывод подключен к первому выводу третьего резистора, к первому выводу первого конденсатора, к первому входу схемы сравнения, к второму информационному входу первой руппы информационных входов мультиплексора и к коллекторному выводу третьего транзисторного ключа, эмиттерный вывод которога соединен с первым выводом второго конденсатора, с вторым выводом первого конденсатора, с эмиттерным выводом пятого транзисторного ключа, с вторым и третьим информационными входами второй группы информационных входов мультиплексора и с первым информационным входом первой группы информационных входоа мультиплексора, с первыми входами первого и второго операционных усилителей и подключен к шине аналоговой земли, второй вывод третьего резистора соединен с коллекторным выводом пятого транзисторного ключа, базовый вывод которого соединен с вторым выводом четвертого резистора, с выходом схемы сравнения, вход сброса триггера подключен к выходу элемента НЕ, инверсный выход триггера соединен с первым входом второго элемента И-НЕ, вторые входы первого и второго элементов И-НЕ подключены к входу разрешения устройства, а выходы соединены соответСтвенно с первым и вторым упрааляющлми входами мультиплексора, третлй и четвертый информационные входы первой группы информационных входов которого соединены с выходом первого операционного усилителя, вторым входом схемы сравнения и третьим выводом первого цифроаналогового преобразователя, выход второго операционного усилителя соединен с вторым входом третьего операционного усигителя и с третьим выходом второго цифроаналогового преобразователя, первый и второй аналоговые аь,ходы второго цифроаналогового преобразователя подключены соответственно к первому и второму входам второго о "ерационного усилителя, первый ивторой аналоговые выходы первого цифроаналогового преобразователя подключены соответственно к первому и второму аыходам первого операционного усилителя, входы опорного напряжения первого и второго цифроаналоговых преобразователей подключены к выходу источника опорного напряжения, группа информацлонных входов второго цифроаналогового преобразоаателя является второй группой информационных входов устройства, первый и четвертый информационные входы второй группы информационных входов мультиплексора соединены с вторым выводом пятого резистора, первый выход мультиплексора подключен к первому входу буферного усилителя и к второму выводу второго конденсатора, второй выход мультиплексора подключен к базовому выводу третьего тоанзисторного ключа., выход буферного усилителя соединен с его вторым входом и с входом стабилизатора напряжения, выход которого соединен с эмиттерным вьаодом первого транзисторного ключа, базовый вывод которого соединен с первым выводом второго резистора, минусовой и плюсовой выводы питания стабилизатора напряжения соединены соответственно с шиной цифроаой земли и с первой плюсовой шинол цифроаого питания, о т л и ч а ю щ и й с я тем,что, с целью расширения функциональных,возможностей, а него дополнительно введены первый, второй и третий элементы ИЛИ,третий элемент И-НЕ, седьмой и восьмой13 Составитель Л. ТуневРедактор В. Данко Техред М.Моргентал Корректор С, Юско Заказ 3099 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., 4/5 роизводственно-издательский комбинат " нт", г, Ужгород, ул.Гагарина, 1 резисторы, первый и второй диоды, катоды которых соединены с выходом третьего элемента ИЛИ и являются выходом управляемого формирователя импульсов, а аноды соединены соответственно с коллекторными выводами первого и второго транзисторных ключей, эмиттерный вывод второго транзисторного ключа соединен с первым выводом седьмого резистора и является входом напряжения программирования, базовый вывод второго транзисторного ключа соединен с вторым выводом седьмого резистора и с первым выводом восьмого резистора, второй вывод которого подключен к выходу второго элемента ИЛИ, вход которого является вторым входом запуска формирователя и соединен с первымвходом третьего элемента И-НЕ, второй вход которого соединен с первым входом запуска, с первым входом 5 первого элемента И-НЕ и с входом первогоэлемента ИЛИ, выход которого подключен к второму выводу второго резистора, выход третьего элемента И-НЕ соединен с первым входом третьего элемента ИЛИ, второй вход 10 которого является входом установки втретье состояние выхода формирователя, выход схемы сравйения соединен с синхровхоцом триггера, а устайовочнйй и информационные входы триггера подключены 15 к второй плюсовой шине цифрового питания.

СмотретьЗаявка

4797420, 08.01.1990

ПЕРМСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ПАРМА"

РАССОМАГИН ВАСИЛИЙ РАДИОНОВИЧ, ТУНЕВ ЛЕОНИД ВАСИЛЬЕВИЧ, УСТИНОВ СЕРГЕЙ ЮРЬЕВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: импульсов, управляемый, формирователь

Опубликовано: 23.08.1992

Код ссылки

<a href="https://patents.su/7-1757086-upravlyaemyjj-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Управляемый формирователь импульсов</a>

Предыдущий патент: Многоканальный программируемый генератор импульсов

Следующий патент: Формирователь импульсов

Случайный патент: Способ производства сварных профилей из цветных металлов