Цифровой приемник дельта-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1732499

Автор: Охлобыстин

Текст

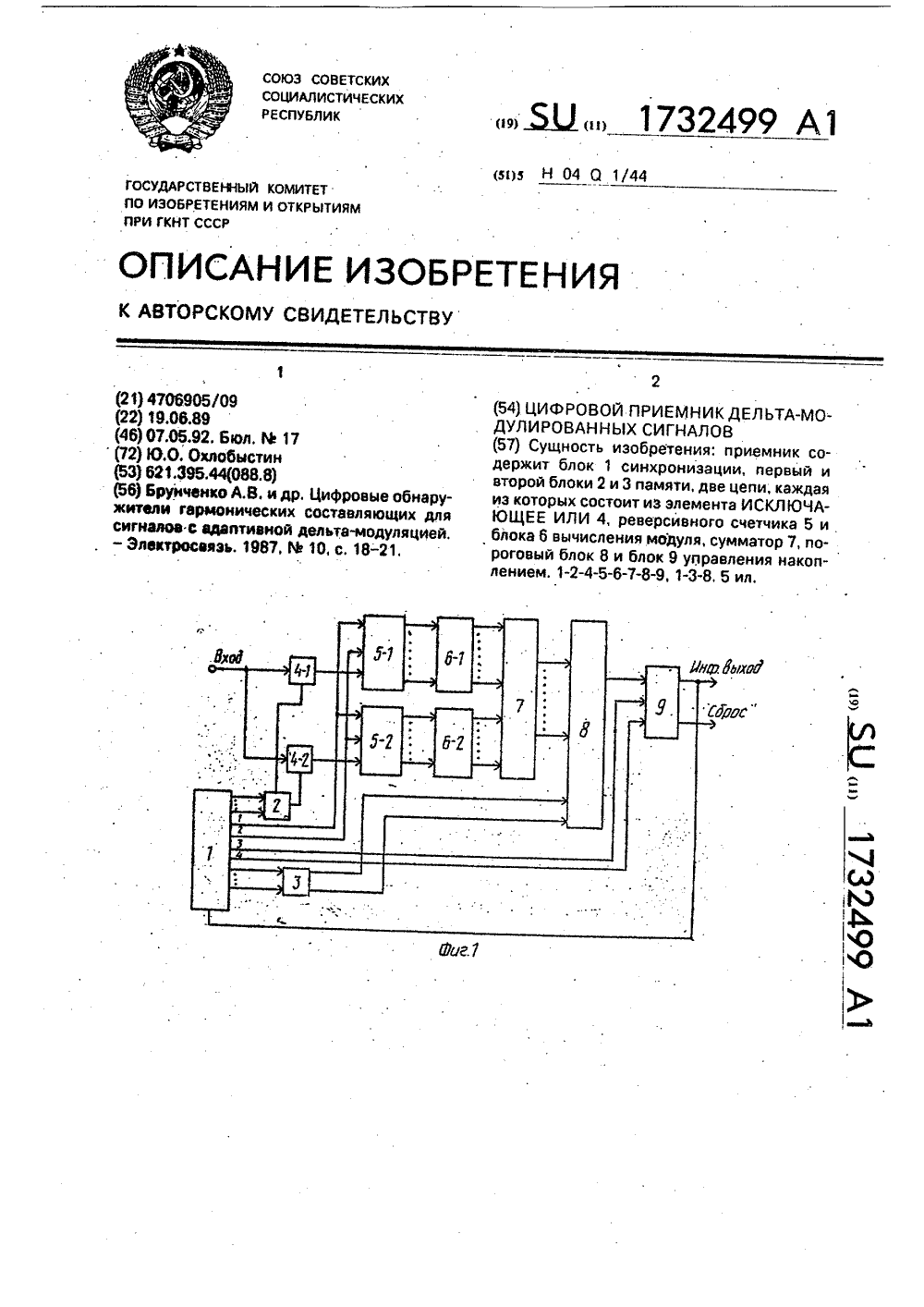

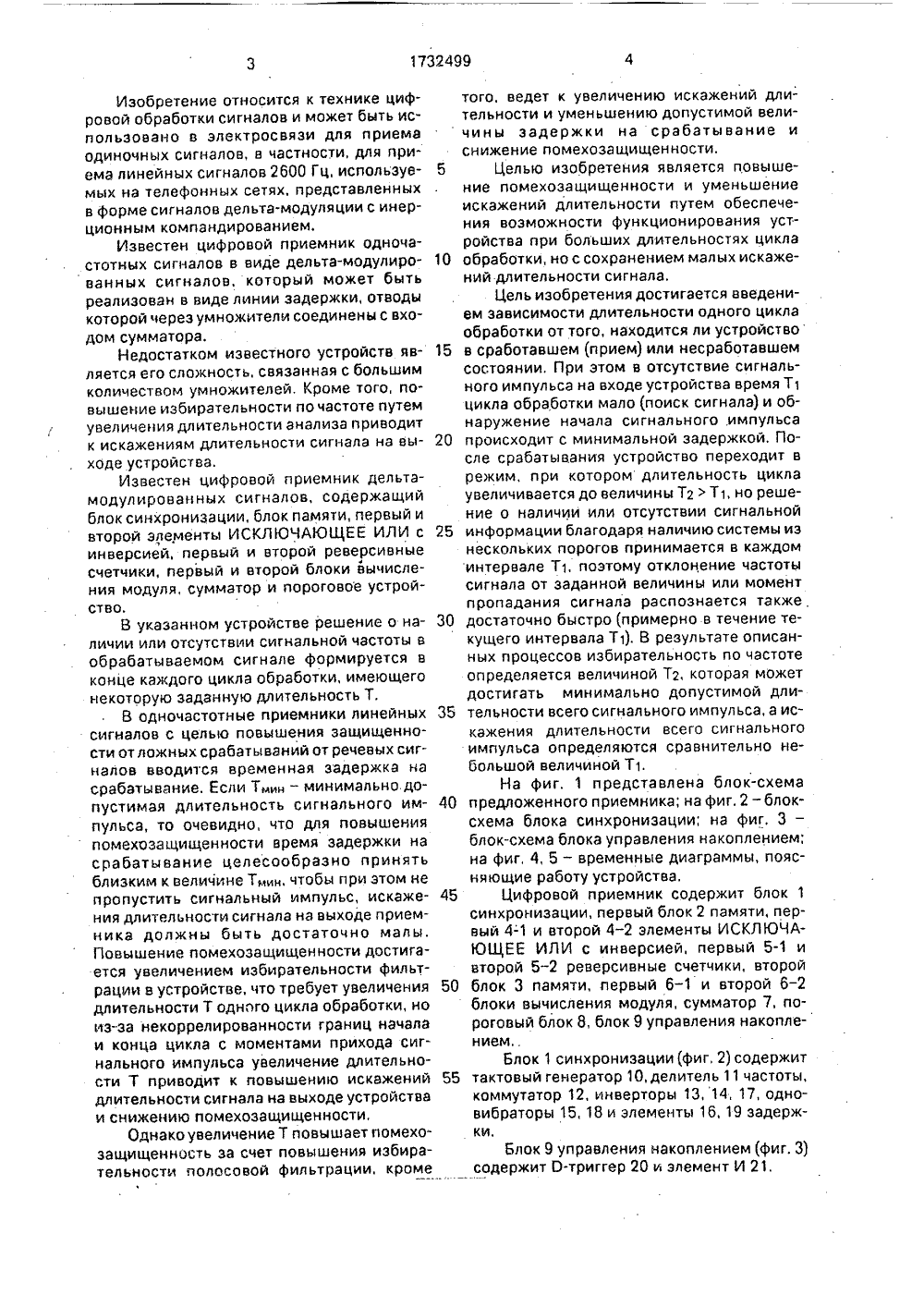

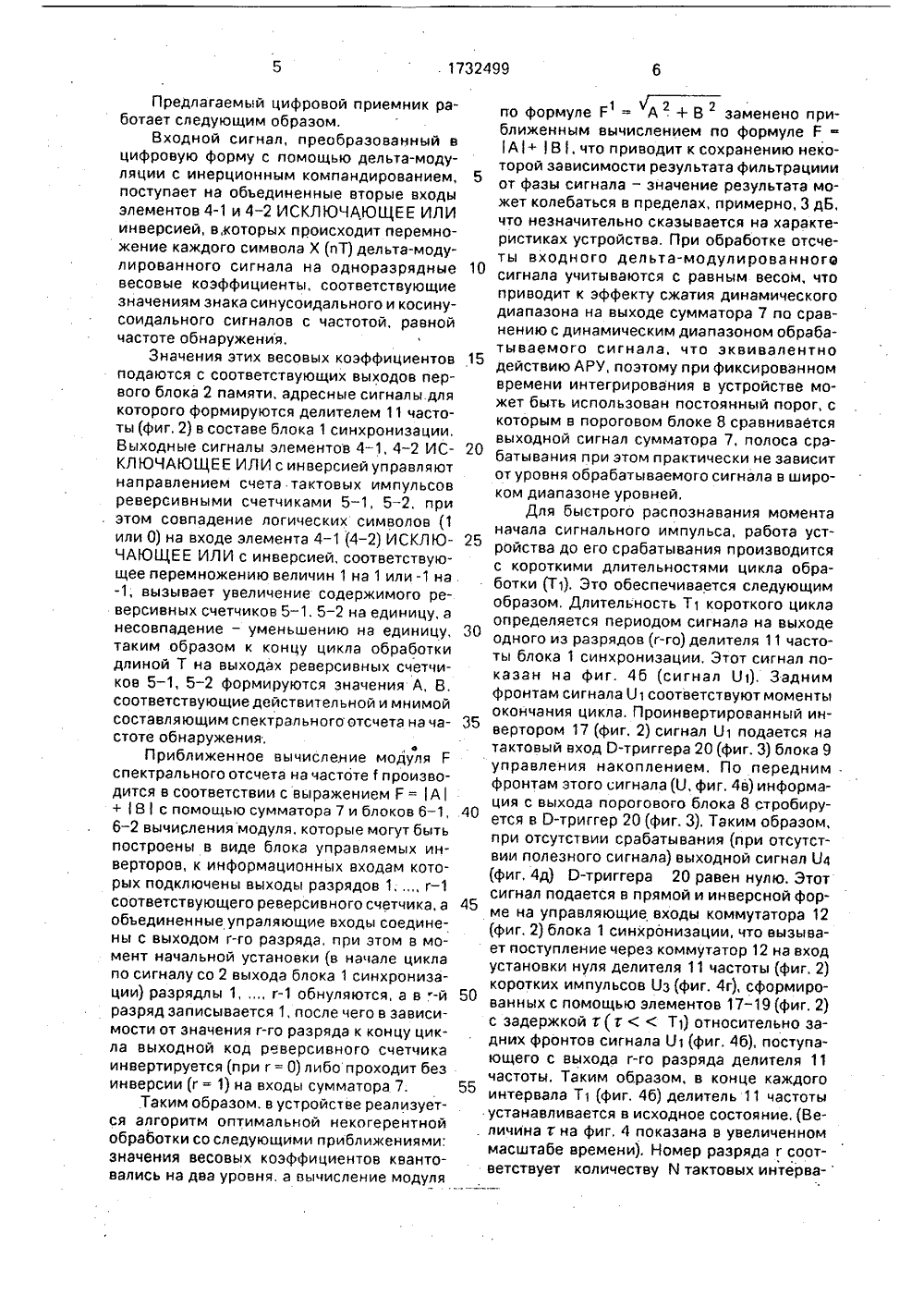

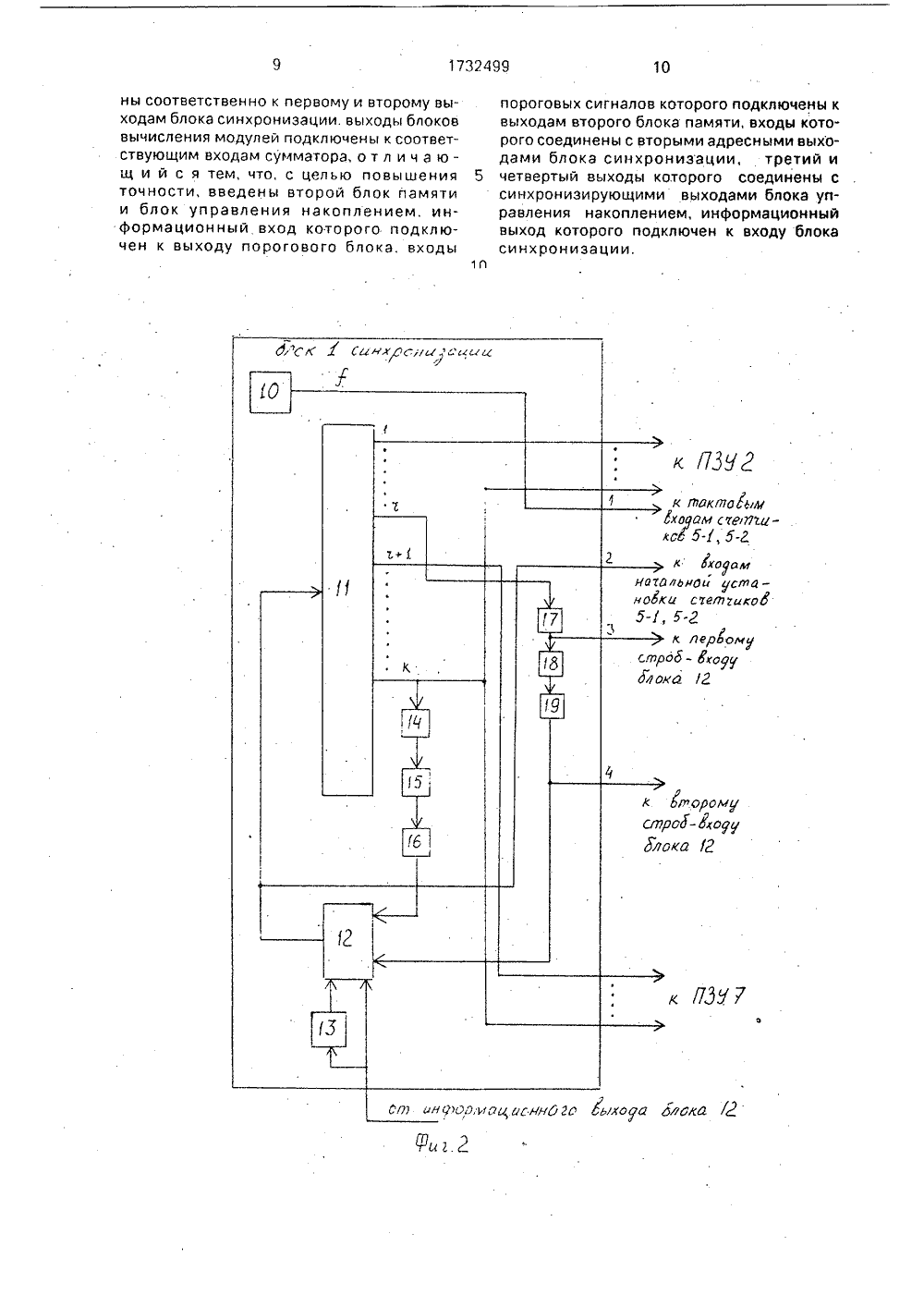

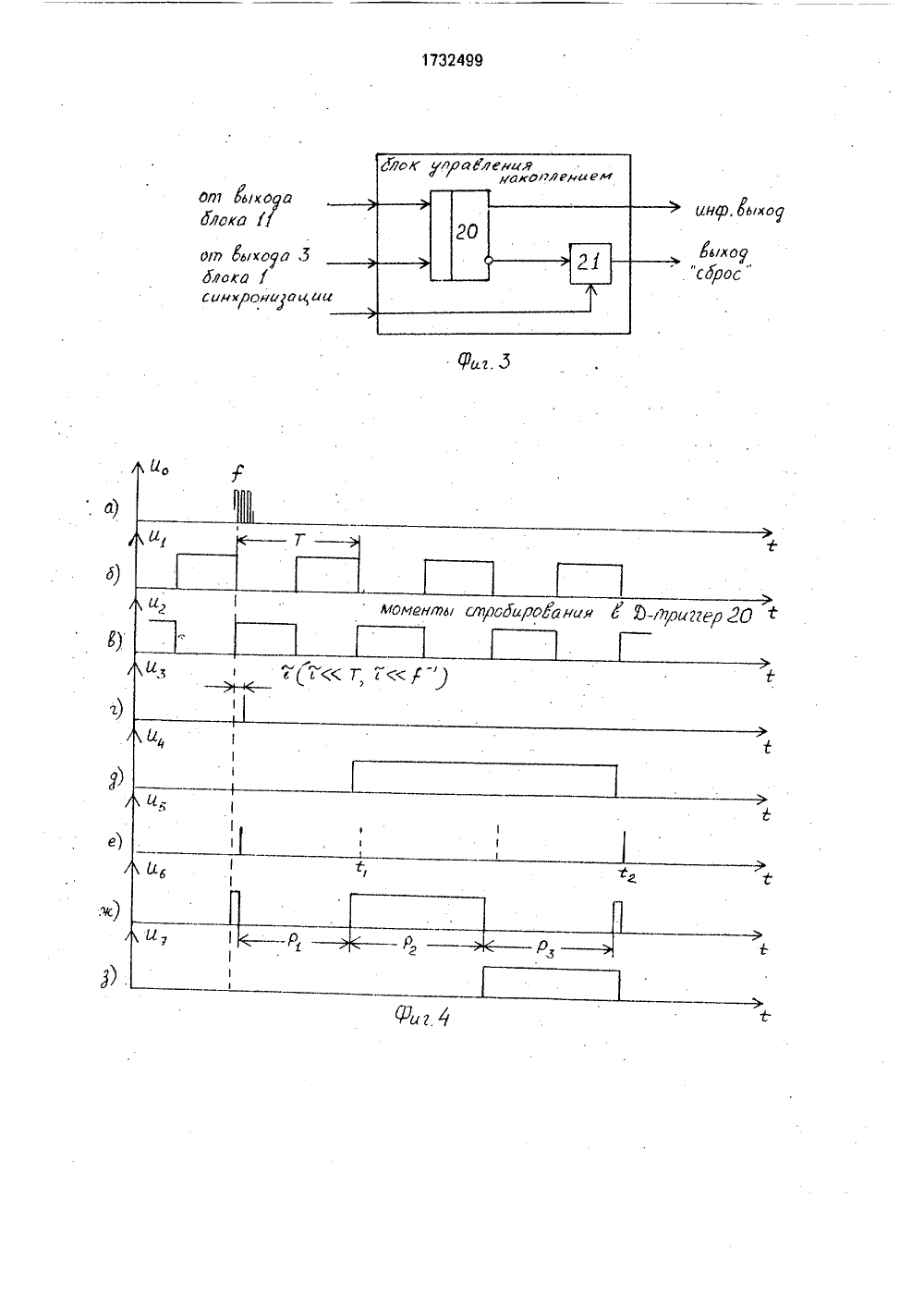

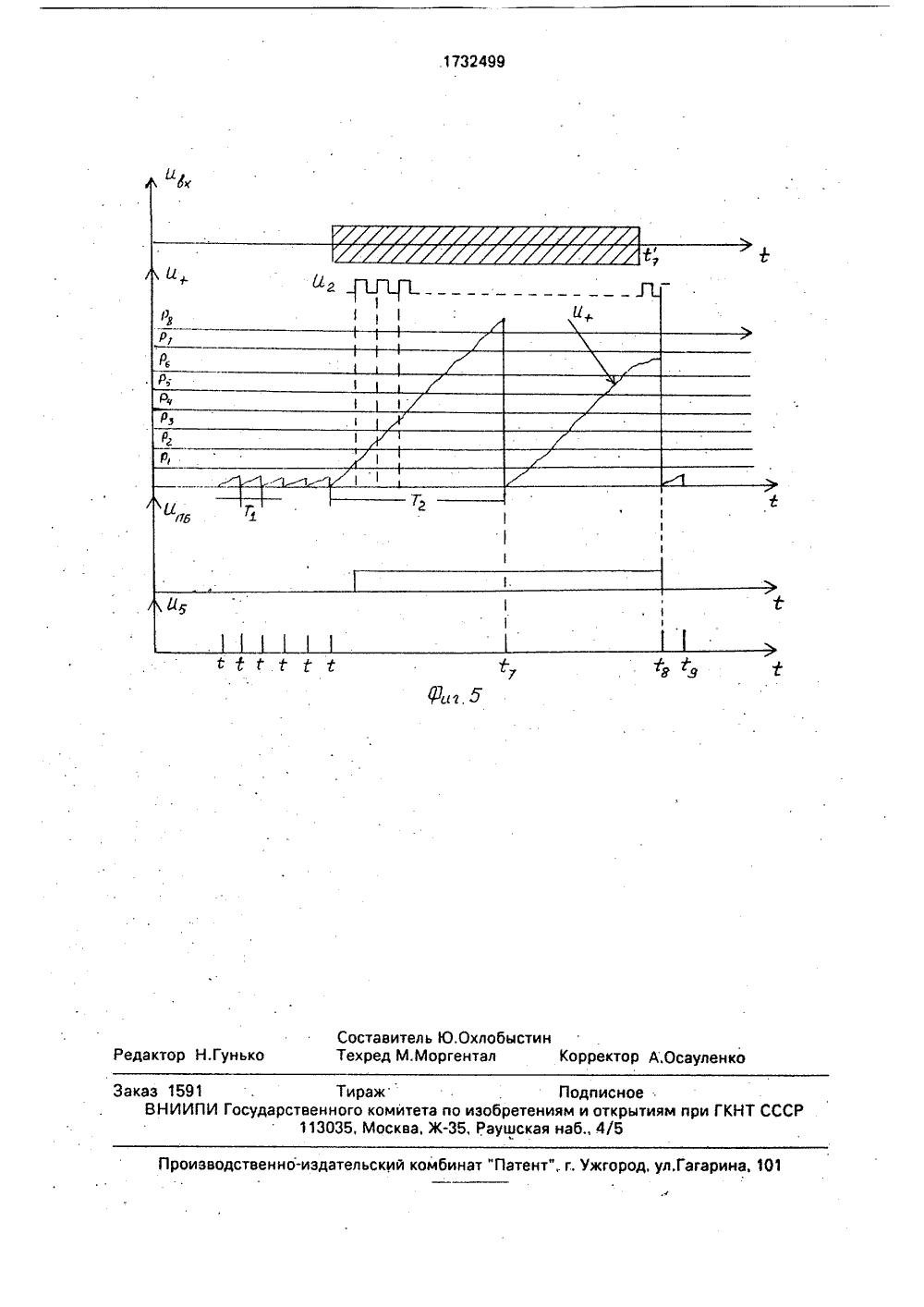

(505 Н 04 а 1/44 ЕТЕНИЯ ифровые обнаруставляющих для льта-модуляцией О, с. 18-21. ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Ьруйчеико А.В. и др. Цжители Гщжонических ссигиаюв с адаптивной де- Электросвязь. 1987, Ь 1 1732499 А(57) Сущность изобретения: приемник содержит блок 1 синхронизации, первый и второй блоки 2 и 3 памяти, две цепи, каждая из которых состоит из элемента ИСКЛ ЮЧАЮЩЕЕ ИЛИ 4, реверсивного счетчика 5 и блока 6 вычисления модуля, сумматор 7, пороговый блок 8 и блок 9 управления накоплением. 1-2-4-5-6-7-8-9, 1-3-8. 5 ил.Изобретение относится к технике цифровой обработки сигналов и может быть использовано в электросвязи для приемаодиночных сигналов, в частности, для приема линейных сигналов 2600 Гц, используемых на телефонных сетях, представленныхв форме сигналов дельта-модуляции с инерционным компандированием.Известен цифровой приемник одночастотных сигналов в виде дельта-модулированных сигналов. который может бытьреализован в виде линии задержки, отводыкоторой через умножители соединены с входом сумматора.Недостатком известного устройств является его сложность, связанная с большимколичеством умножителей. Кроме того, повышение избирательности по частоте путемувеличения длительности анализа приводитк искажениям длительности сигнала на выходе устройства.Известен цифровой приемник дельтамодулированных сигналов, содержащийблок синхронизации, блок памяти, первый ивторой элементы ИСКЛЮЧАЮЩЕЕ ИЛ И с 25инверсией, первый и второй реверсивныесчетчики, первый и второй блоки вычисления модуля, сумматор и пороговое устройство.В указанном устройстве решение о наличии или отсутствии сигнальной частоты вобрабатываемом сигнале формируется вконце каждого цикла обработки, имеющегонекоторую заданную длительность Т,В одночастотные приемники линейных 35сигналов с целью повышения защищенности отложных срабатываний от речевых сигналов вводится временная задержка насрабатывание. Если Тин - минимально.допустимая длительность сигнального импульса, то очевидно, что для повышенияпомехозащищенности время задержки насрабатывание целесообразно принятьблизким к величине Т 1 ин, чтобы при этом непропустить сигнальный импульс, искажения длительности сигнала на выходе приемника должны быть достаточно малы,Повышение помехоэащищенности достигается увеличением избирательности фильтрации в устройстве, что требует увеличения 50длительности Т одного цикла обработки, ноиз-эа некоррелированности границ началаи конца цикла с моментами прихода сигнального импульса увеличение длительности Т приводит к повышению искажений 55длительности сигнала на выходе устройстваи снижению помехозащищенности,Однако увеличение Т повышает помехозащищенность за счет повышения избирательности полосовой фильтрации, кроме того. ведет к увеличению искажений длительности и уменьшению допустимой величины задержки на срабатывание иснижение помехоэащищенности.Целью изобретения является повышение помехоэащищенности и уменьшение искажений длительности путем обеспечения возможности функционирования устройства при больших длительностях цикла обработки, но с сохранением малых искажений длительности сигнала.Цель изобретения достигается введением зависимости длительности одного цикла обработки от того, находится ли устройствов сработавшем (прием) или несработавшем состоянии, При этом в отсутствие сигнального импульса на входе устройства время Т 1 цикла обработки мало (поиск сигнала) и обнаружение начала сигнального импульсапроисходит с минимальной задержкой. После срабатывания устройство переходит в режим, при котором длительность цикла увеличивается до величины Т 2Т 1, но решение о наличии или отсутствии сигнальной информации благодаря наличию системы из нескольких порогов принимается в каждом интервале Т 1, поэтому отклонение частотысигнала от заданной величины или моментпропадания сигнала распознается также, достаточно быстро (примерно в течение текущего интервала Т 1). В результате описанных процессов избирательность по частоте определяется величиной Т 2, которая может достигать минимально допустимой длительности всего сигнального импульса, а искажения длительности всего сигнального импульса определяются сравнительно небольшой величиной Т 1На фиг, 1 представлена блок-схемапредложенного приемника; на фиг. 2- блоксхема блока синхронизации; на фиг. 3 - блок-схема блока управления накоплением;на фиг, 4, 5 - временные диаграммы, поясняющие работу устройства.Цифровой приемник содержит блок 1 синхронизации, первый блок 2 памяти, первый 4-1 и второй 4 - 2 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, первый 5-1 ивторой 5-2 реверсивные счетчики, второй блок 3 памяти, первый 6 - 1 и второй 6-2блоки вычисления модуля, сумматор 7, пороговый блок 8, блок 9 управления накоплением,. Блок 1 синхронизации (фиг, 2) содержит тактовый генератор 10, делитель 11 частоты,коммутатор 12, инверторы 13, 14, 17, одновибраторы 15, 18 и элементы 16, 19 задержБлок 9 управления накоплением (фиг. 3)содержит О-триггер 20 и элемент И 21.Предлагаемый цифровой приемник работает следующим образом.Входной сигнал, преобразованный вцифровую форму с помощью дельта-модуляции с инерционным компандированием,поступает на объединенные вторые входыэлементов 4-1 и 4-2 ИСКЛЮЧАЮЩЕЕ ИЛИинверсией, в,которых происходит перемножение каждого символа Х (пТ) дельта-модулированного сигнала на одноразрядныевесовые коэффициенты, соответствующиезначениям знака синусоидального и косинусоидального сигналов с частотой, равнойчастоте обнаружения,Значения этих весовых коэффициентовподаются с соответствующих выходов первого блока 2 памяти, адресные сигналы.длякоторого формируются делителем 11 частоты (фиг. 2) в составе блока 1 синхронизации.Выходные сигналы элементов 4-1, 4-2 ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией управляютнаправлением счета тактовых импульсовреверсивными счетчиками 5 - 1, 5 - 2, при. этом совпадение логических символов (1или О) на входе элемента 4-1 (4-2) ИСКЛ ЮЧАЮЩЕЕ ИЛИ с инверсией, соответствующее перемножению величин 1 на 1 или -1 на .-1, вызывает увеличение содержимого реверсивных счетчиков 5 - 1. 5 - 2 на единицу, анесовпадение - уменьшению на единицу,таким образом к концу цикла обработкидлиной Т на выходах реверсивных счетчиков 5-1, 5 - 2 формируются значения А, В,соответствующие действительной и мнимойсоставляющим спектрального отсчета на частоте обнаружения,ЮПриближенное вычисление модуля Рспектрального отсчета на частоте 1 производится в соответствии с выражением Г = А+Вс помощью сумматора 7 и блоков б - 1,6 - 2 вычисления модуля, которые могут бытьпостроены в виде блока управляемых инверторов, к информационных входам которых подключены выходы разрядов 1. г - 1соответствующего реверсивного счетчика, аобъединенные упраляющие входы соединены с выходом г-го разряда, при этом в момент начальной установки (в начале циклапо сигналу со 2 выхода блока 1 синхронизации) разрядлы 1, ., гобнуляются, а в;-йразряд записывается 1, после чего в зависимости от значения г-го разряда к концу цикла выходной код реверсивного счетчикаинвертируется (при г = О) либо проходит безинверсии (г - 1) на входы сумматора 7.Таким образом, в устройстве реализуется алгоритм оптимальной некогерентнойобработки со следующими приближениями:значения весовых коэффициентов квантовались на два уровня, а вычисление модуля по формуле Г = А л В заменено при.ближенным вычислением по формуле ГА+В , что приводит к сохранению неко 5торой зависимости результата фильтрациииот фазы сигнала - значение результата может колебаться в пределах, примерно, 3 дБ,что незначительно сказывается на характеристиках устройства. При обработке отсчеты входного дельта-модулированногосигнала учитываются с равным весом, чтоприводит к эффекту сжатия динамическогодиапазона на выходе сумматора 7 по сравнению с динамическим диапазоном обраба 15тывавмого сигнала. что эквивалентнодействию АРУ, поэтому при фиксированномвремени интегрирования в устройстве может быть использован постоянный порог, скоторым в пороговом блоке 8 сравнивается20выходной сигнал сумматора 7, полоса срабатывания при этом практически не зависитот уровня обрабатываемого сигнала в широком диапазоне уровней,Для быстрого распознавания момента25начала сигнального импульса, работа устройства до его срабатывания производитсяс короткими длительностями цикла обработки (Т 1). Это обеспечивается следующимобразом, Длительность Т 1 короткого цикла30определяется периодом сигнала на выходеодного из разрядов (г-го) делителя 11 частоты блока 1 синхронизации, Этот сигнал показан на фиг. 46 (сигнал О 1), Заднимфронтам сигнала О 1 соответствуют моменты35окончания цикла. Проинвертированный инвертором 17 (фиг, 2) сигнал 01 подается натактовый вход О-триггера 20 (фиг. 3) блока 9управления накоплением. По передним .фронтам этого сигнала (О, фиг. 4 в) информа 40ция с выхода порогового блока 8 стробируется в О-триггер 20 (фиг. 3), Таким образом,при отсутствии срабатывания (при отсутствии полезного сигнала) выходной сигнал О 4(фиг, 4 д) О-триггера 20 равен нулю. Этот45сигнал подается в прямой и инверсной форме на управляющие входы коммутатора 12(фиг. 2) блока 1 синхронизации, что вызывает поступление через коммутатор 12 на входустановки нуля делителя 11 частоты (фиг. 2)50коротких импульсов Оз (фиг, 4 г), сформированных с помощью элементов 17-19 (фиг. 2)с задержкой г(г ( ( Т 1) относительно задних фронтов сигнала О 1(фиг. 4 б), поступающего с выхода г-го разряда делителя 11частоты, Таким образом, в конце каждого55интервала Т 1 (фиг. 4 б) делитель 11 частотыустанавливается в исходное состояние, (Ве. личина х на фиг, 4 показана в увеличенноммасштабе времени). Номер разряда г соответствует количеству ч тактовых интерва 1732499лов Т 1, укладывающихся на цикле обработки длительностью Т 1(М 2"). Поскольку в младший адресный разряд второго блока 3 памяти сигнал подается с (г +1)-го разряда делителя 11 частоты, на интервале Т 1 код адреса на входе этого блока памяти остается неизменным, равным нулю, При этом иэ второго блока 3 памяти на пороговый блок 8 считывается наименьшее из пороговых значений (Р 1, фиг. 5). Выходным сигналом коммутатора 12 (фиг, 2) блока 1 синхронизации производится также и начальная установка (обнуление значащих разрядов) реверсивных счетчиков 5 - 1, 5-2, к началу каждого цикла обработки Т 1, в связи с чем обнуляется и выходной сигнал О+ (фиг. 5) сумматора 7,При появлении сигнального импульса (О,) на входе устройства выходной сигнал сумматора 7 (О+, фиг, 5) в текущем интервале Т 1 превЫсит значение порога Р 1, что к концу данного цикла переведет О-триггер 20 (фиг.3) в единичное состояние (04, фиг, 4 д) и изменит сигналы на управляющих входах коммутатора 12 (фиг. 2) на противоположные. при этом очередной импульс (О 5, фиг.4, момент времени т 1) с выхода элемента 19 задержки (фиг. 2) на вход установки нуля счетчика делителя 11 частоты (фиг. 2) не поступит и устройство перейдет в режим обработки с длительным циклом Т 2 Т 1, В процессе работы делителя 11 частоты (фиг.2) в каждом интервале Т 1 меняется двоичный код,подаваемый на адресные входы ПЗУ 3, Примеры сигналов на двух адресных входах, снимаемых с (г. + 1) и (г+ 2)-го разрядов делителя 11 частоты, показаны на фиг, 5. В течение интервалов г(величина задержки элементов 16, 19, фиг. 2) после каждого цикла имеет место искажение адресных сигналов, что, однако, не скажется на работе . устройства, поскольку величина т крайнемала,Последовательная смена кода на адресных входах второго блока 3 памяти вызовет смену пороговых значений (Р 1, Рр,.), снимаемых с его выхода на пороговый блок 8, Значение порогов рассчитывается таким образом, что при нахождении частоты сигнального импульса в заданных пределах выходной сигнал сумматора.7 в каждом текущем интервале Т 1 в пределах цикла обработки Т 2 должен быть обязательно выше текущего значения порога Р. при этом О- триггер 20 непрерывно удерживается в единичном состоянии. В конце цикла Т происходит сброс делителя 11 частоты (фиг, 2) и реверсивных счетчиков 5-1, 5-2 коротким импульсом, формируемым элементами14 - 16 (фиг, 2) с задержкой относительно задних фронтов выходного сигнала К-го разряда делителя 11 частоты. (При нахождении О-триггера 20 в единичном состоянии именно этот импульс проходит через коммута гор 12 (фиг. 3). Номер К разряда соответствует количеству циклов Ть укладывающихся надлительности цикла Т 2, Нужно отметить, что длительность цикла Т 2 может быть выбрана 10 минимально допустимого значения длительности сигнального импульса с соответствующим повышением помехоустойчивости, Помимо системного сброса по заднему фронту выходного сигнала К-го раз 15 20 25 3035 4045 5055 ряда делителя 11 частоты сброс реверсивных счетчиков 5-1, 5-2 может произойти и при отклонении спектральной структуры сигнала от заданной (сосредоточенной в окрестности заданной сигнальной частоты) или.при пропадании полезного сигнала. В этом случае в текущем интервале Т 1 в пределах цикла Тг выходной сигнал сумматора 7 (О+) не превысит текущего значения порога (порог. Р 7), в связи с чем передним фронтом сигнала О (фиг, 4 е, момент т 2) с выхода элемента 19 задержки (фиг. 2), устанавливающий реверсивные счетчики 5, - 1, 5 - 2 и сумматор 7 в исходное состояние, Через элемент И 21 такой же импульс пройдет на выход "Сброс" блока 9 и может быть использован. например, для обнуления внешнего накопителя. Во внешнем накопителе вводится временная задержка на срабатывание, повышающая защищенность от ложных срабатываний.Внешний накопитель может быть выполнен, например. в виде интегратора со сбросом,Из фиг, 4-5 видно, что длительность выходного сигнала 0-триггера 20 (фиг. 3) примерно соответствует длительности огибающей сигнального импульса (точность определяется длительностью Т 1 наиболее короткого цикла обработки).Формула изобретения Цифровой приемник дельта-модулированных сигналов, содержащий блок синхронизации, к первым адресным входам которого подключен первый блок памяти, последовательно соединенные сумматор и пороговый блок, две цепи, состоящие из последовательно включенных элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, реверсивного счетчика и блока вычисления модуля, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией обьединены, а вторые их входы подключены к соответствующим выходам первого блока памяти, тактовые входы и входы сброса реверсивных счетчиков попарно обьединены и подключе1732499 10 к лакауаЬщ о аи лемм-1, 5 СЕЙ иг к лерамБ- Аоууа /2 8 л орому оХ-диоду ны соответственно к первому и второму выходам блока синхронизации. выходы блоков вычисления модулей подключены к соответствующим входам сумматора, о т л и ч а ющ и й с я тем, что, с целью повышения точности, введены второй блок памяти и блок управления накоплением. информационный вход которого подключен к выходу порогового блока, входы пороговых сигналов которого подключены к выходам второго блока памяти, входы которого соединены с вторыми адресными выходами блока синхронизации, третий и 5 четвертый выходы которого соединены ссинхронизирующими выходами блока управления накоплением, информационный выход которого подключен к входу блока синхронизации,1 п.1732499 Составитель Ю.ОхлобыстинРедактор Н,Гунько Техред М. Моргентал Корректор А.Осаулен ательский комбинат "Патент",. г. Ужгород. ул,Гагари роизводственн Заказ 1591 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4706905, 19.06.1989

ПРЕДПРИЯТИЕ ПЯ Р-6609

ОХЛОБЫСТИН ЮРИЙ ОЛЕГОВИЧ

МПК / Метки

МПК: H04Q 1/44

Метки: дельта-модулированных, приемник, сигналов, цифровой

Опубликовано: 07.05.1992

Код ссылки

<a href="https://patents.su/7-1732499-cifrovojj-priemnik-delta-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой приемник дельта-модулированных сигналов</a>

Предыдущий патент: Устройство управления стереоскопической телевизионной камерой

Следующий патент: Приемник градиента акустического давления

Случайный патент: Планетарный вибровозбудитель