Оптоэлектронное устройство для вычитания десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1697069

Авторы: Имнаишвили, Кобесашвили, Натрошвили

Текст

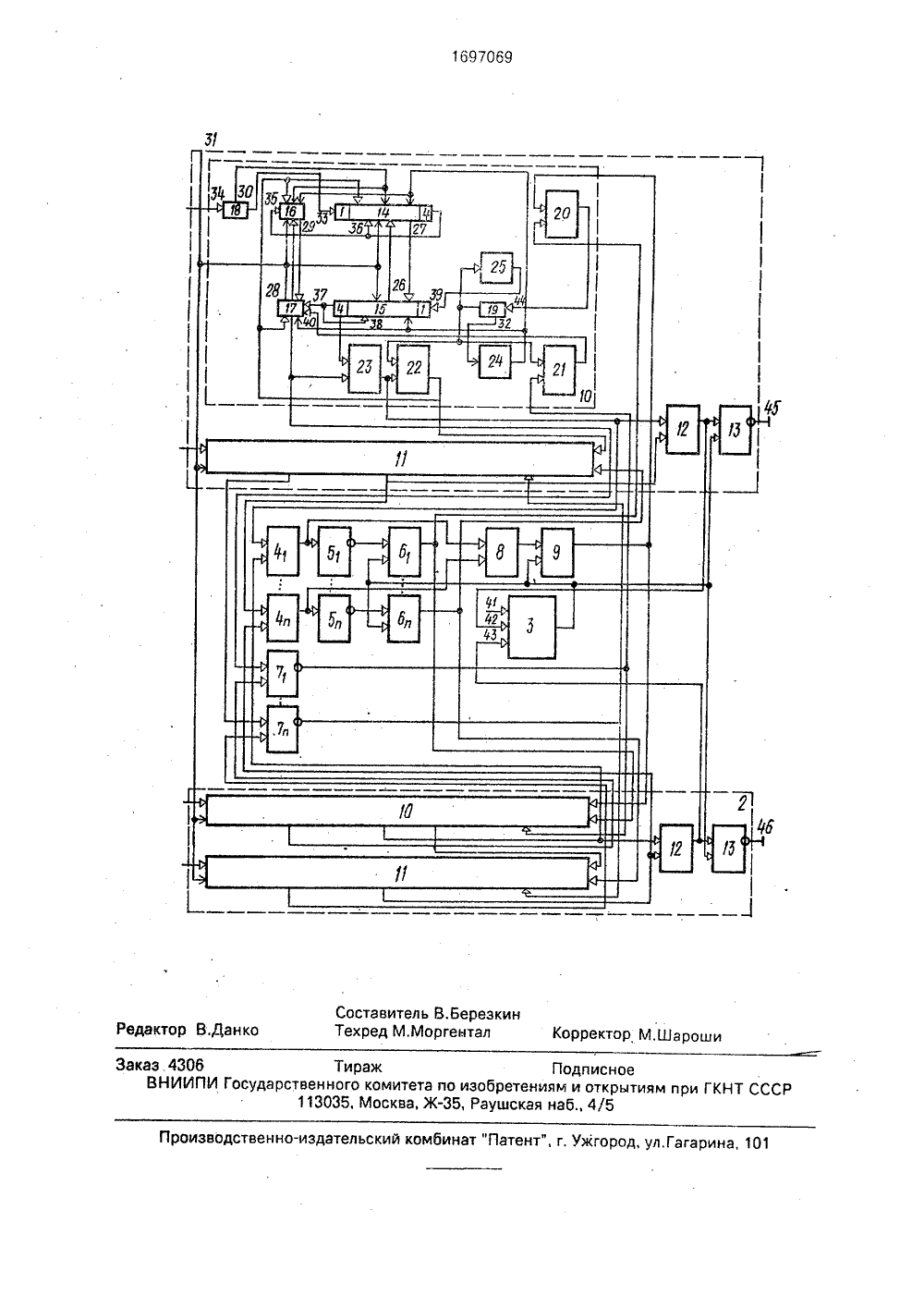

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 97069 51)5 6 1/О Е ИЗОБРЕ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Грузинский политехнический институт (72) О.Г,Натрошвили, Л.Ш.Имнаишвили и З,К.Кобесашвили(56) Авторское свидетельство СССР М 1136157, кл. 0 06 Р 7/56, 1983.Авторское свидетельство СССР М 1539754, кл. 6 06 Е 1/04, 1987.(54) ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано для организации операций вычитания десятичных чисел в логико-временных средах, Цель изобретения - повышение быстродействия устройства. Изобретение позволяет повысить быстродействие устройства за счет уменьшения количества двоичных знаков в единичном коде разрядов слагаемых, при котором сокращается разрядность модуля и, следовательно, уменьшается время Изобретение относится к вь 1 числительной технике и может быть использовано для организации операций вычитания десятичных чисел в логиковременных средах.Цель изобретения - повышение быстродействия устройства.На чертеже представлена схема оптоэлектронного устройства для вычитания десятичных чисел.Оптоэлектронное устройство для вычитания содержит два оптоэлектронных регисдвига информации в разрядных ячейках.Устройство содержит два оптоэлектронных регистра, регенеративный бистабильный оптрон, группу оптоэлектронных элементов ИЛИ, группу оптоэлектронных элементов НЕ, группу оптоэлектронных элементов И, группы оптоэлектронных элементов ИЛИ - НЕ и два оптоэлектронных элемента И, Каждый оптоэлектронный регистр содержит оптоэлектронный элемент И, оптоэлектронный элемент ИЛИ - НЕ и разрядные ячейки, каждая из которых содержит два четырехразрядных оптоэлектронных квантующих модуля, два одноразрядных оптоэлектронных квантующих модуля, два модулятора, оптоэлектронный элемент з ИЛИ, три оптоэлектронных элемента И и два элемента задержки. Запись операндов в оптоэлектронных регистрах осуществляется параллельно по разрядам в новой Форме единично-нормального кода, Вычитание выполняется путем параллельного сдвига операндов во всех разрядных ячейках обоих регистров. 1.ил,стра 1 и 2 операндов А и В соответственно, регенеративный бистабильный оптрон 3 группу 4 оптоэлектронных элементов ИЛИ группу 5 оптоэлектронных элементов НЕ, группу 6 оптоэлектронных элементов И, группу 7 оптоэлектронных элементов ИЛИНЕ, оптоэлектронные элементы И 8 и 9. Каждый оптоэлектронный регистр представлен двумя разрядными ячейками 10 и 11, оптоэлектронным элементом И 12 и оптоэлектронным элементом ИЛИ - НЕ 13, а каждая разрядная ячейка регистров 1 и 2 содержитдва четырехразрядных оптоэлектронных квантующих модуля 14 и 15, два одноразрядных оптоэлектронных квантующих модуля 16 и 17, два модулятора 18 и 19, оптоэлектронный элеен ИЛИ 20, тои оптоэлектронных элемента И 21-23, два элемента 24 и 25 задержки, В каждой . разрядной ячейке реглан;тров 1 и 2 модуль 14 оптически соединен с выходом 26 модуля 15, который оптически соединен с выходом 27 модуля 14, модуль 16 оптически соединен с выходом 28 модуля 17, который оптически соединен с выходом 29 модуля 16, Электрические входы модулей 14 и 16 соединены с электрическим выходом 30 модулятора 18 и с шиной 31 питани., а электрические входы модулей 16 и 17 - с шиной 31 питания и с выхоцом перього элемента 24 задержки, вход которого соединен с электрическим выходом 32 модулятора 19, модули 14 и 16 электрически соединены также с выходом первого элемента 24 задержки,Оптический вход 33 модуля 14 соединен с оптическим выходом модулятора 18, оптический вход 34 которого является оптическим входом каждой разрядной ячейки 10 и 11 регистров 1 и 2. Выход четвертого двоичного разряда модуля 14 опти 1 ески соединен с оптическим входом 35 модуля 16 и оптическим входом 36 модуля 14, а выход четвертого двоичного разряда модуля 15 оптически соединен с оптическим входом 37 модуля 17 и оптическим входом 38 модуля 15, Первые входы оптоэлектронных элементов И 21, 22 и вход второго элемента 25 задержки оптически соединены с оптическим выходом модулятора 19, Выход второго элемента 25 задержки оптически соединен с оптическим входом 39 модуля 15, выход первого оптоэлектронного элемента И 21 - с оптическим вхбдом 40 модуля 17, а выход второго оптоэлектронного элемента И 22 - с оптическими входами модулей 14, 16 и 17. Оптические выходы модуля 17 и четвертого двоичного разряда модуля 15 соединены соответственно с первым и вторым входами третьего оптоэлектронного элемента И 23, выход которого соединен с вторым входом второго элемента И 22,В обоих оптоэлектронных регистрах 1 и 2 выход третьего элемента И 23 каждой разрядной ячейки оптически соединен с соответствующим входом элемента И 12, выход . которого оптически соединен с первым входом элемента ИЛИ - НЕ 13, второй вход которого оптически соединен с выходом регенеративного бистабильного оптрона 3, единичный оптический вхоц 41 которого соединен с входом запуска устройства, Нулевые оптические входы 42 и 43 регенера 20 25 30 35 40 БО 55 тивного бистабильного оптрона 3 соединены с выходом элемента И 12 соответственно регистров 1 и 2. Выходтретьего элемента И 23 одноименных разрядных ячеек обоих ре. гистров 1 и 2 оптически соединеН с соответствуюшим входом соответствующего элемента ИЛИ группы 4, Каждый элемент ИЛИ группы 4 через соответствующий элемент НЕ группы 5 оптически соединен с первым входом соответствующего элемента И группы 6, а второй вход каждого элемента И группы 6 оптически соединен с выходом регенеративного бистабильного оптрона 3, Выход каждого элемента И группы 6 оптически соединен с первым входом оптоэлектронного элемента ИЛИ 20 соответствующей разрядной ячейки обоих регистров 1 и 2.Выход каждого элемента ИЛИ группы 4 оптически соединен с соответствующим входом элемента И 8, выход котороо оптически соединен с первым входом элемента И 9, второй вход которого оптически соединен с выходом регенеративного бистабильного оптрона 3. Выход элемента И 9 оптически соединен с вторым входом элемента ИЛИ 20 в первой разрядной ячейке 10 обоих регистров 1 и 2, а второй вход элемента ИЛИ 20 в каждой разрядной ячейке кроме первой 10, каждого оптоэлектронного регистра соединен с выходом второго элемента И 22 . предыдущей разрядной ячейки. Выход элемента ИЛИ 20.в каждой разрядной ячейке обоих регистров 1 и 2 соединен с оптическим входом 44 модулятора 19. Выход модуля 17 одноименных разрядных ячеек обоих регистров 1 и 2 оптически соединен с соответствующим входом соответствующего элемента ИЛИНЕ группы 7, Каждый элемент ИЛИ-НЕ группы 7 оптически соединен с вторым входом первого элемента И 21 соответствующей разрядной ячейки обоих регистров 1 и 2, Вьха,ц элемента ИЛИ - НЕ 13 в регистре 1 соединен с оптическим выходом 45 признака присутствия разности в регистре 1, а в регистре 2 - с оптическим выходом 46 признака присутствия разности в регистре 2,Врем задержки элементов 24 и 25 определяется как г, где г - среднее время задержки си, налов в логических элементах.Деся ичные цифры представляются следующим образомаф 1 %Д/ЙО - 0 О О О О1 - О 1 О О О2 - О 1 1 О О3. - О 1 1 1 04 - О 1 1 1 15-1 О О О О8 в 1 О О О7 - 1 11 0 О8 - 111009 - 1 1 1 1где й- признак цифры;Р 1 Р 2 Рэ Р 4- - мантисса цифры,Оптоэлектронное устройство для вычитания десятичных чисел работает следующим образом.Работу оптоэлектронного устройства проиллюстрируем на примере выполнения операции вычитания над двумя десятичными числами, Предположим, что от десятичного числа А - 834 (первый операнд) следует вычесть десятичное число В - 763 (второй операнд). В применяемой форме кодирования эти числа представляются следующим образом834 7634 - 0 1 1 1 1 3 - 0 1 1 1 0 3 - 0 1 1 1 0 6 - 1 1 О 0 0 8 - 1 1 1 1 0 7 - 1 1 1 О О В процессе вычитания в одноименных разрядах этих чисел производится пошаговое убавление единиц мантисс и признаков (если в признаках кодов цифр одновременно находится единица) параллельна до обнуления одного из двух мантисс. Для нашего примера после трех ша в вычитания имеем следующие числа 0 - 0 0 0 О 0 5 - 1 0 О 0 0 0 - О О 0 О 0 1 - 01000 2 - О 1 1 О 0 1-01000 Если в каждом из полученных чисел имеется ненулевой разряд с нулевой мантиссой и одноименный разряд другого числа отличается от нуля, то производится обнуление признака и установление двоичных разрядов мантиссы в единичное состояние данного разряда первого числа. Одновременно с этим в одноименном разряде другого операнда обнуляется один двоичный разряд мантиссы, Для нашего примера имеем 1 - 0 1 О 0 0 0 - О 0 О О О 1 - 01.0004 - 01111 1-0 1 О О О 0 - 0 О О О О В дальнейшем при необходимости процесс обнуления одного из двух мантисс одноименных разрядов чисел повторяется. В этом случае для нашего примера имеем1 - О 1 0 0 00 - 0 0 О 0 0 О - О 0 О 0 0 3 - О 1 1 1 0 1 - О 1 О 0 О 0 - О 0 0 О 0Если полученные числа отличаются атнуля, то производится процесс заема. Процесс заема начинается с младших разрядов.При этом в необнуленном младшем разряде5 одного числа производится уменьшение содержимого на один, а одноименный обнуленнь,й разряд второго числа переводится вединичное состояние (в признаке и двоичных раэаядах мантиссы записываются еди 10 ницы), Следовательно, в последующемразряде второго числа производится уменьшение содержимого на единицу, если данный разрядотличэется от нуля. Если данныйразряд равен нулю, то процесс заема рэс 15 пространяется до разряда второго числа, ькотором находится хотя бы одна единица,Для нашего примера имеем,О - 0 0 0 О О200 - О ОООО 1 - 0 1 0 0 0 9 - 1 1 1 1 1 2 - О 1 1 0 О 0-0 О О 0 0 После осуществления описанного про 30 цесса для нашего примера имеем 1 - 0 1 0 0 0 О - 0 0 0 0 0 7 - 1 1 1 0 0 0 - 0 0 0 0 0 О - 0 0 О О О 0 - 0 0 0 0 0 35 Процесс вычитания заканчивается обнулением всех разрядов одного числа.Рассмотренный процесс вычитания наустройстве реализуется следующим обра 40 зом,По оптическому входу 34 модулятора 18во всех разрядных ячейках регистров 1 и 2происходит запись соответствующих операндов А и В параллельно па разрядам в45 новой форме единично-нормального кода; врегистр 1 записывается операнд А, в регистр 2 - операнд В. Причем в модулях 14 и16 каждой разрядной ячейки 10 и 11 обоихрегистров 1 и 2 записывается соответствую 50 щая цифра в прямом коде, а в модулях 15 и17 - в дополнительном до девяти коде зэсчет оптической связи по выходам 27 и 29соответственна модулей 14 и 16. Например,цифра 7 записывается в следующем виде: в55 модулях 16 и 14 соответственно 1 и 1100, вмодулях 17 и 15 соответственно 0 и 0011,Если в модулях 16 и/или 14 некоторыходноименных разрядных ячеек обоих регистров 1 и 2 находится хотя по единице, тотретьи элементы И 23 данных разрядных Аналогично вышесказанному, на следующем этапе имеем25 9 - 1 1 1 1 1 8-1 1 1 1 О9 - 1 1 1 1 1 2 - 0 1 1 0 0 О - 0 0 0 0 0 0 - 0 0 0 О 0ячеек закрыты и, следовательно, на первыйвход соответствующего элемента И группы6 поступает логическая единица,. При этом,если в модулях 16 соответствующих одноименных разрядных ячеек Обоих регистров 51 и 2 одновременно находятся единицы тос выхода соответствуОщег зле:ента ИЛ;1 -НЕ группы 7 логическая ециница поступаетна ВТО)ь 8 ВхОДы п 8 рвых элементов И 21данных разрядных ячеек. 10При поступлении запуска 5 ощега оптическОГО сиГнала длительностьО Г 1 где хвремя срабатывания регенеративного бистабильного Оптрана) на входе 41 регенеративнбго бистабильнога аптрона 3 15прОисходит срабатывание паследн 8 га и появление на его выходе аптическогс единичного сигнага, который поступает на второйвход каждого оптоэлектронного элемета ИГруппы б, СледавстельО, эткрывается тзт Оэлемент И Группы б, на п 8 рвом Входе кОгорага присутствует логическая единица, Единица с выхода этага элемента И группы б,через элементы ИЛИ 20 в соответствующихразрядных ячейках регистров 1, 2 запускает 25модуляторы 19. В каждом иэ двух одноименных разрядных ячеек оптический единчный сигнал с выхода модулятора 19 черезвторой элемент 25 задержки поступает наоптическлй вход 39 модуля 5 и увеличивает 30заг:исанное в этом модуле количествс единиц. Сл 8 давательна, ОэнулЯютсй саатветгтВующие двоичные разряды модуля 14 черезоптическую связь на выходе 26 модуля 15.Оптический единичный сигнал с выхода модулятара 9 пос:гупает также на пеовьйвход первого злсмента И 21 и при присутствии логической единицы на ега второмвходе открь.Вает последний, Единлца с выхода первого элементе И 2поступает на 40ОпГический ВХОД 40 моДуля 17 и Выэывсетзапись единицы в этом модуле,Следовательно, обнуляется мадупьбчерез оптическую связь на вьходе 28 мг,гуля 17,Оптический единичный сигнал с выхода модуляторе 19 поступае- на первьй входвторого элемента И 22, не вызывает сраба. тыВани 8 последнеГО, так как на ВьходетретьегО элемента И 23 присутствует ло. ический нуль. Увеличение количества единиц 50в модулях 15 одноименных разрядных ячеекпроисходит до тех пор, пока в четвертомдвоичном разряде одного из двух модулей15 не появится единица, свидетельствуОщая о том, что соответствующий модуль 14 55обнулен. С появлением единиць В четвертом двоичном оазряде модуля 15, если модуль 17 данной разрядной ячейки обнулен,и В модуле 14 однолмен ной разрядной ячейки другао регистра находится хотя бы одна единица, единичный сигнал поступает на оптический вход 37 модуля 17, переводя ега ь единичное состоЯние, и на вход 38 модулЯ 15, обнуляя ега.Следовательно, обнуляется модуль 16 данной разрядной ячейки через оптическую сВЯзь;а ВыхОД 828 мадугЯ 17 и перевадитсг в единичное сосэтояние весь модуль 14 через оптическую связь на Вь;ходе 26 модуля 15, После этого, если модуль 14 одноименной разаядной ячейки другога регистра не обнуляется, Огда аналогичным Образам производигся увеличение количества еди ниц в молулях "15 дачных Однаим 8 нных разрядных ячеек, Процесс продалкается до тех.пор, пока в четвертом двоичном разряде одного из двух разрядных ячеек не появится 8 ДИНИЦВЬ СВИДВТВЛЬСТВУЮГЦЭ 5 О ТОМ, ЧТЭ Са" ответствующий модуль 14 обнулен, т.е, дс тех пор, пока одна из одноименных разряд" ных ячеек регистров 1 и 2 не Обнулится, Таким образом, во всех одноименных разрядных ячейках регистров 1 и 2 происходит Сдвиг информации до тех пар, пока не обнулятся адул 14 и 16 ОДОй из Двух Одно.именных разрядных ячеек,Б это время В соответствующих абнуленных разрядных ячейках регистров 1 и 2 открываются логические элементы И 23, В каждом реплстре единицы с выхода этих элементов поступают на соответствующие входы элемента И 12. Если все разрядные ячейки каждого реглстра не обнулень., тогда элементы И 12 не открьты и регенеративный бистальный оптран 3 остается в единич- Н ОМ СОСТОЯ Н И,Послс зткрьггия третьих элементов И 23 всех обнуленных разрядных ячеек регистров 1 и 2 на выходе каждого элемента ИЛИ группы 4 Одновременно появляются логические единицы,Следовательно, аткрываОтся элементы И 8 и 9, г оскольку на Втором входе последнего с выхода регенеративнаго бистабильнагэ ог;трона 3 прлсутствует логическая единица, Единица с выхода элемента И 9 через элементы ИЛИ 20 в первых разрядных ячейках 10 Обоих ре истров 1 и 2 запускает модуляторь 19. Оптицеский единичный сигнал с Выхода модулятора ,9 в этих разрядных Ячейках через второй элемент 25 заДержки гОстугает на оптический ВХОД 39 модуля 15. При этом в необнуленной разрядной ячейке 10 и раисходит уменьшение содержимого на единицу, В обнуг:.енной разрядной ячейке 10 обнуляется весь модуль 15 по оптическому входу 38, Одновре менно оптический единичный сигнал с выхода модулятора 19 поступает на первый вход в горого элемента И 22 и аткрьВает его,так как на втором входе присутствует логи - ческая единица с выхода третьео элемента И 23. Единица с выхода вараго элемента И 22 поступает ка оптические ьходы модулей 17, 16 и 14 данной разрядной ячейки,Следовательно, модуль 17 обнуляется, а модули данной разрядной ячейки 16 и 1 переводятся в единичное состояние, Одновременно с этим единица с выхода второго элемента И 22 также поступает в последующую разрядную ячейку данного рсгистаа и уменьшает его содержимое на едини у,В дальнейшем присутствие оптического 10 единичного сигнала на выходе регенератиеного бистабильного оптрона 3 аналогична осуществляет процесс обнуления мсдулей 16 и 14 каждой разрядной ячейки обоих регистров 1 и 2 до тех пор, пока в четвертом двоичном разряде модуля 15 и в модуле 17 каждой разрядной ячейки одного из регистров не появится единица.Если с выхода третьего элемента И 23 каждой разрядной ячейки регистра 1 или регистра 2 на соответствующий вход элемента И 12 одновременно поступает оптический единичный сигнал, это свидетельствует о том, что информация, записанная в соответствующем регистре, равна нулю, тогда единичный оптический сигнал на выходе элемента И 12 регистров 1 и 2 вызывает обнуление регенеративного бистабильного оптрона 3. При этом прекращается поступление оптического, единичного 25 30 сигнала через оптоэлектронные элементы И группы 6 и И 9 на входы модуляторов 19 каждой разрядной ячейки регистров 1 и 2, что необходимо для предовращения установки в единичное состояние модулей 16 и 35 Таким образом; один из регистров 1 или 2 является обнуленным, а в другом записана разность операндов А и В, Отом, что разность находится, например, в регистре 1, свидетельствует наличие оптического сигнала на выходе 45 признака присутствия разности е регистре 1, в противком случае оптический сигнал присутствует на выходе 46 признака присутствия разности е регистре 2,Формула изобретения Оптоэлектронное устройство для вычитания десятичных чисел, содержащее регекеративный бистабильный оптрон, группу элементов ИЛИ, группу элементов НЕ, группу элементов И, деа элемента И и. первый и второй оптоэлектронные регистры, содержащие элемент И, элемент ИЛИ - НЕ и разрядные ячейки по числу десятичных разрядов, каждая из которых содержит два че 50 14 и обнуления модулей 17 и 15 соответствующих разрядных ячеек регистра 1 или 2. 40 тыоехразрядньх оптоэлектронных кванту;ощих модуля, деа мадулчтара и элемент ИЛИ, причем е каждой разрядной ячейке обоих оптоэлектронных регистров первые эгектри.еские еходь первого и второго четырехразрядных оптоэлектронных кеантующих модулей подключены к шине питания стройстеа, второй электрический вход первого четырехразрядного оптоэлектронного кеантующего модуля соединен с электрическим еьходом первого модулятора, первый оптический вход первого четырехразрядкога оптоэлектронного квантующего модуля соединен с выходом второго четырехразряднаго оптоэлектронного квантующего модуля, первый оптический вход которого соединен с выходом первого четь рехразряднога оптоэлектронного кеантующего модуля, оптические входы первых модуляторов разрядных ячеек пеоваго и еторсго оптоэлектронных регистров соединены с соатветству:ащими разрядами входов соответственно первого и второго операндов .устройства, етоаой оптический вход первого четырехразрядного оптоэлектронного квантуюшега модуля е каждой разрядной ячейке обоих оптоэлектронных регистров соединен с оптическим вьходом первого модулятора, е каждом оптоэлектронном регистре выход элемента И оптически соединен с первым входом элемента ИЛИ - НЕ, второй вход которого оптически соединен с еьхада регенератиенога бистабил ьк о го оп трона, единичный оптический вход которого соединен с входом запуска стройстеа, первый и второй нулэе,;е оптические входы регенеративного бистабильнога оптрана соединены с выходами эеенов И соответственно первого и второго оптоэлектронных регистров, выход элемента ИЛИ - НЕ каждого оптоэлектронного регистра соединен с оптическим выходом признака присутствия разности в соответствующем оптоэлектронном регистре, одноименные входы элементсе И обоих оптоэлектронных регистров соединены соответственно с первым и вторым входами соответствующего элемента ИЛИ группы, выход каждого элсмента ИЛ И груп и ы через соответствующий элсмект НЕ группы оптически соединен с первым входом соответствующего элемента И группы, второй вход которого оптически соединен с еьходом регенеративного бистабильного аптрона, выход каждого элемекта И группы оптически соединен с первым входом элемента ИЛИ е соответствующей разряднсй ячейке кгкдого оптоэлектронного регистра, выход каждогоэлемента ИЛИ группы оптически соединенс соответствующим входом первого элем 8 нта И, ВыхОД котороГО оптич 8 ски соединен с первым входом второго элемента И,Второй ВхОд котороГО Оптически соединен с 5выходом регенеоативного бистабильнегоОптрона, выход втооого элемента И оптически соединен с вторым входом элементаИЛИ В перВой разрядной ячейке кажДогооптоэлектронного регистра, выход элемента ИЛИ В каждой. разряд, ой ячейке каждогооптоэлектронного регистра спти 1 ески соединен с входом второго модулятора, о т л ич а ю щ е е с я тем, что, с цель О повышениябыстродействия, в устройство введена 15группа оптоэлектронны: элементов И.Г 1 ИНЕ, а в каждую разрядную ячейку обоихоптоэлектронных регистров введены двадополнительных одноразрядных оптоэлектронных квантующлх модуля, три эл: 20мента И и два элемента задержки, причемВ каждой разрядной яч 8 йке ОЬОИ: ОптО,": -лектронных регистров первгяе электрич-:ские входы обоих одноразрядныхоптоэлектронных квантующих модулей 25подключены к шине питания, второй электрический вход первого одноразрядногооптоэлектронного квантующего модулясоединен с электрическим выходом первсго модулятора, первый оп"ический вход ЗГ 1первого одноразрядного огтозлектронного кванту:ощего модуля соединен с первым оптическим вьходом второгоодноразрядного Оптоэлектронного квантующего модуля, перьый оптический вход 35которого соединен с оптическим выходомпервого одноразрядного оптозле 1 гронного квантующего модуля, вторые электрические входы вторых однооазрядного ичеты рехразрядногс ог тоэлектоон ных 4 Оквантующих модулей и третьи электрические входы первыходноразрядного и четы рехразрядн ого оптоэлектронныхквантующих модулей соединены с выходом первогс элемента заде,.:.Кки, вход которОГО соедин 8 Н с электрическимвыходом Второго модулятора, оптическийвыход которого соединен с первыми вхо.Дами первого и второго элементов И ивходом второго элемента задержки, выход 5 ОкоторОГО Оптически соединен С втОРцм Оп" тическим входом второго четырехразрядного оптоэлектронного квантующего модуля, первые оптичес.ие выходы четвертых двоичных разрядов первого и второо четцрехразрядных оптоэлектронных квднтующих модулей соединены с вторыми оптическими входами соотве"ственно первого и второго одноразрядных оптоэлек, Оонныхквантующих модулей и с третьими оптическими Входами соответственнопервого и второго четырехразрядных оптоэлектронных квантующих моулей., третий оп 1 ический вход второго одноразрядного оптоэлектронного квантующео модуля соединен с выходом первого элемента И, вторые оптические выходы втсрого одноразрядного оптоэлектронного квантующего модуля и четвертого двоичного разряда второго четырехразрядного оптоэлектронного квантующего модуля соединены соответствен о с первым и вторым входами третьего элемента И, выход которого соединен с вторым входом второго элемента И, выход которого в каждой разряд: ой ячейке обоих оптоэлектронных регистров соединен с четвертыми оптическими входами второго одноразрядного и первого четырехразрядного оптоэлектронных квантующих модулей и с третьим оптическим входом первого одноразрядного оптоэлектронного квантующего модуля, выход третьего элемента И каждой разрядной ячейки оптически соединен с соответствующим входом элемента И соответствующего оптоэлектронного регистра, выход второго элемента И каждой разрядной ячей,и, кроме последней, оптическ соединен с втор.м входом элемента ИЛИ последующей разрядной ячейки соот- ВетствующеГО оптоэле:тооннОГО реГистра, вторые оптические выходы вторых одноразрядных оптоэлектронных квантующих модулей Одноименньх разрядных ячеек обоих оптоэлектронных регистров соединены соответстсенно с первым и вторым входами соответствующего элемента ИЛИ-НЕ группы, выход каждого элемента ИЛИ-НЕ группы оптически соединен с вторым ВХОДом перВОГО элемента И в соотвеествующей яч 8 йке каждОГО опгоэлектрОннОГО рвГистра.1697069Составитель В.Березкин едактор В.Данко Техред М.Моргентал Корректор М.Шарош каз.4306 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб., 4/5Производственно-издательский комбинат "Патент", г. Ужгород, ул,Га

СмотретьЗаявка

4769079, 11.12.1989

ГРУЗИНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

НАТРОШВИЛИ ОТАР ГЕОРГИЕВИЧ, ИМНАИШВИЛИ ЛЕВАН ШОТАЕВИЧ, КОБЕСАШВИЛИ ЗУРАБ КАСПОЛОВИЧ

МПК / Метки

МПК: G06E 1/04

Метки: вычитания, десятичных, оптоэлектронное, чисел

Опубликовано: 07.12.1991

Код ссылки

<a href="https://patents.su/7-1697069-optoehlektronnoe-ustrojjstvo-dlya-vychitaniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Оптоэлектронное устройство для вычитания десятичных чисел</a>

Предыдущий патент: Регулятор реактивной мощности

Следующий патент: Генератор ортогонально противоположных сигналов

Случайный патент: Способ тепловой изоляции нагнетательной скважины