Способ обработки цифровых сигналов по типу предпочтительно адаптивного трансверсального фильтра и устройство для его осуществления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1655309

Автор: Хайнрих

Текст

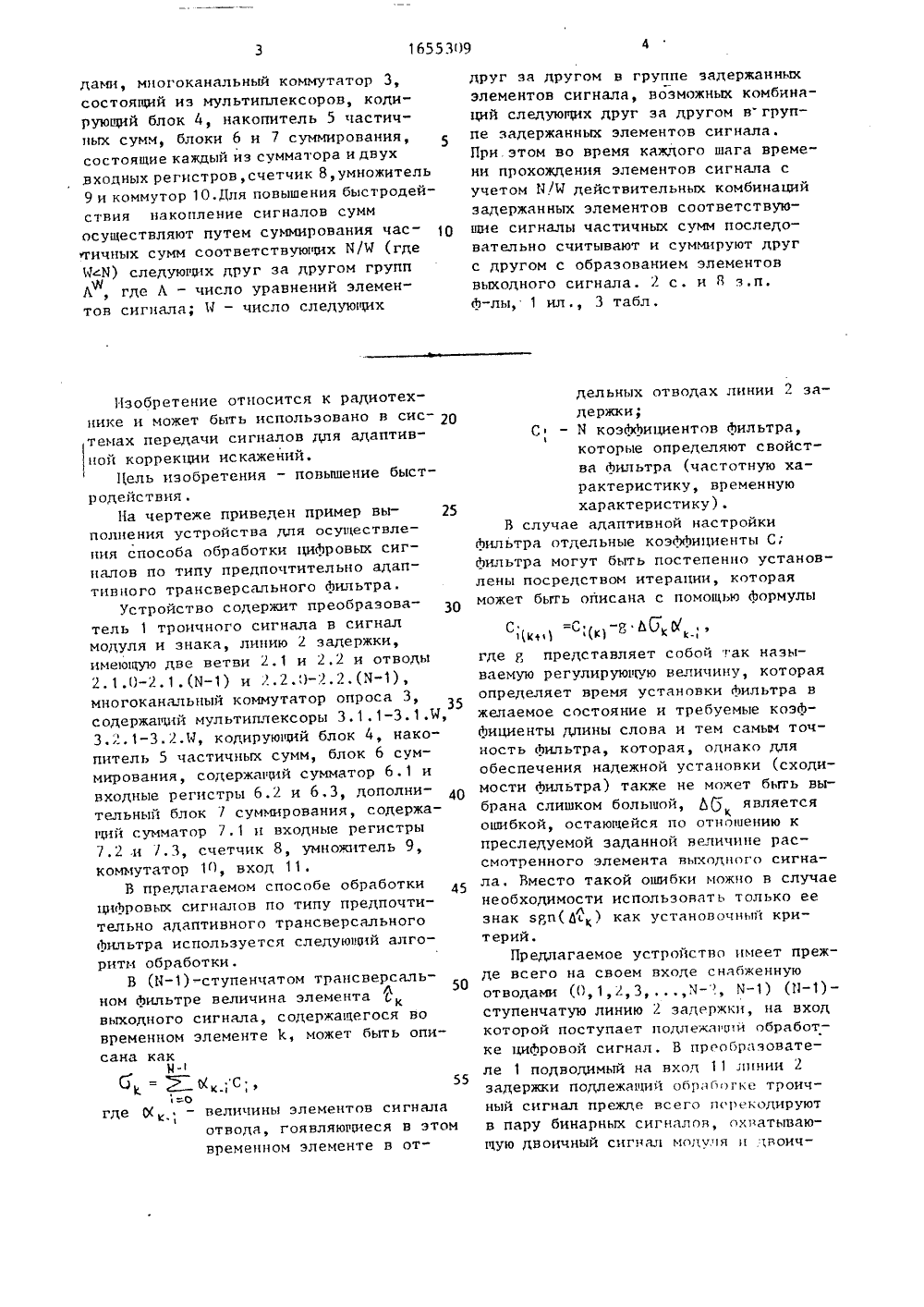

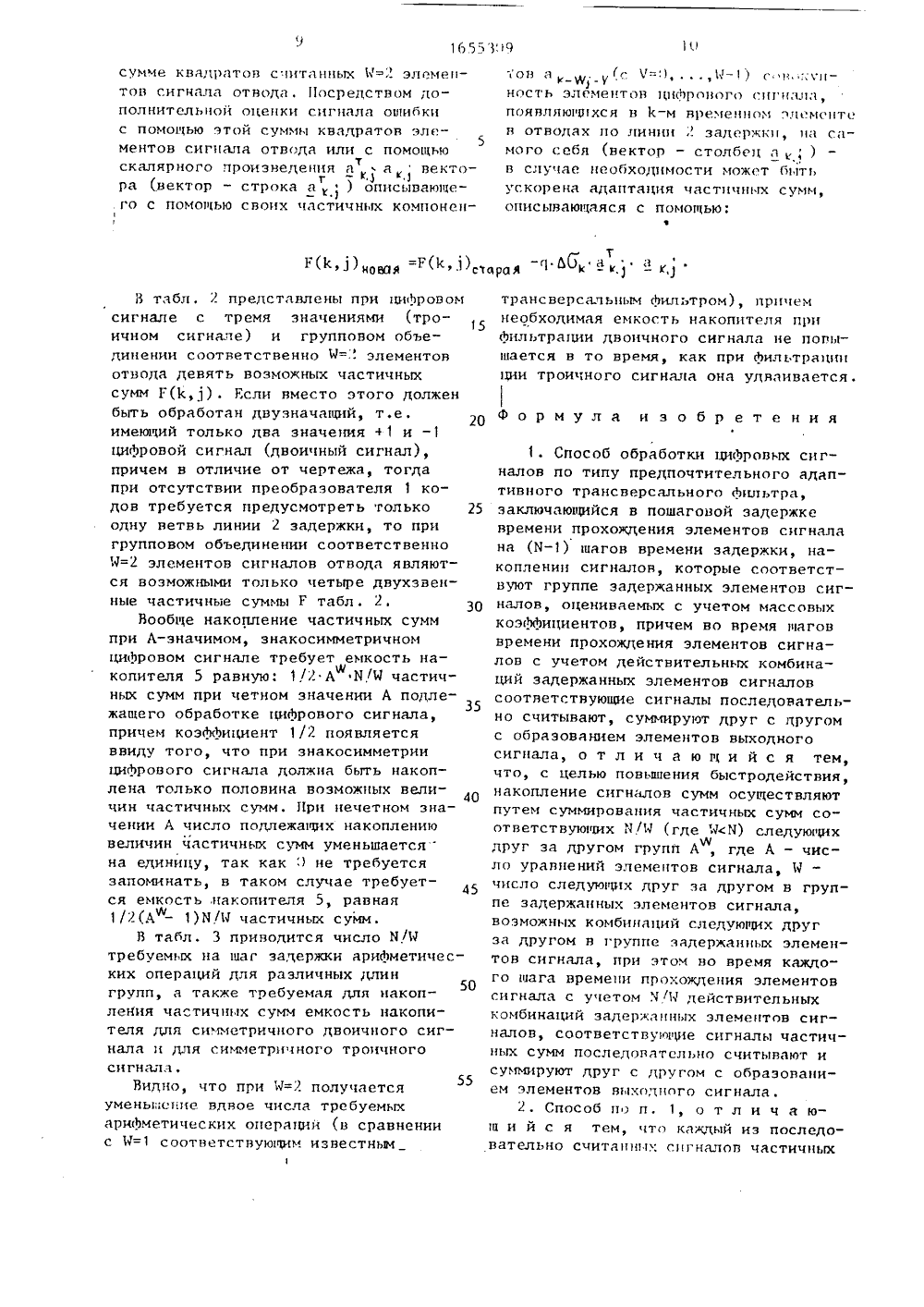

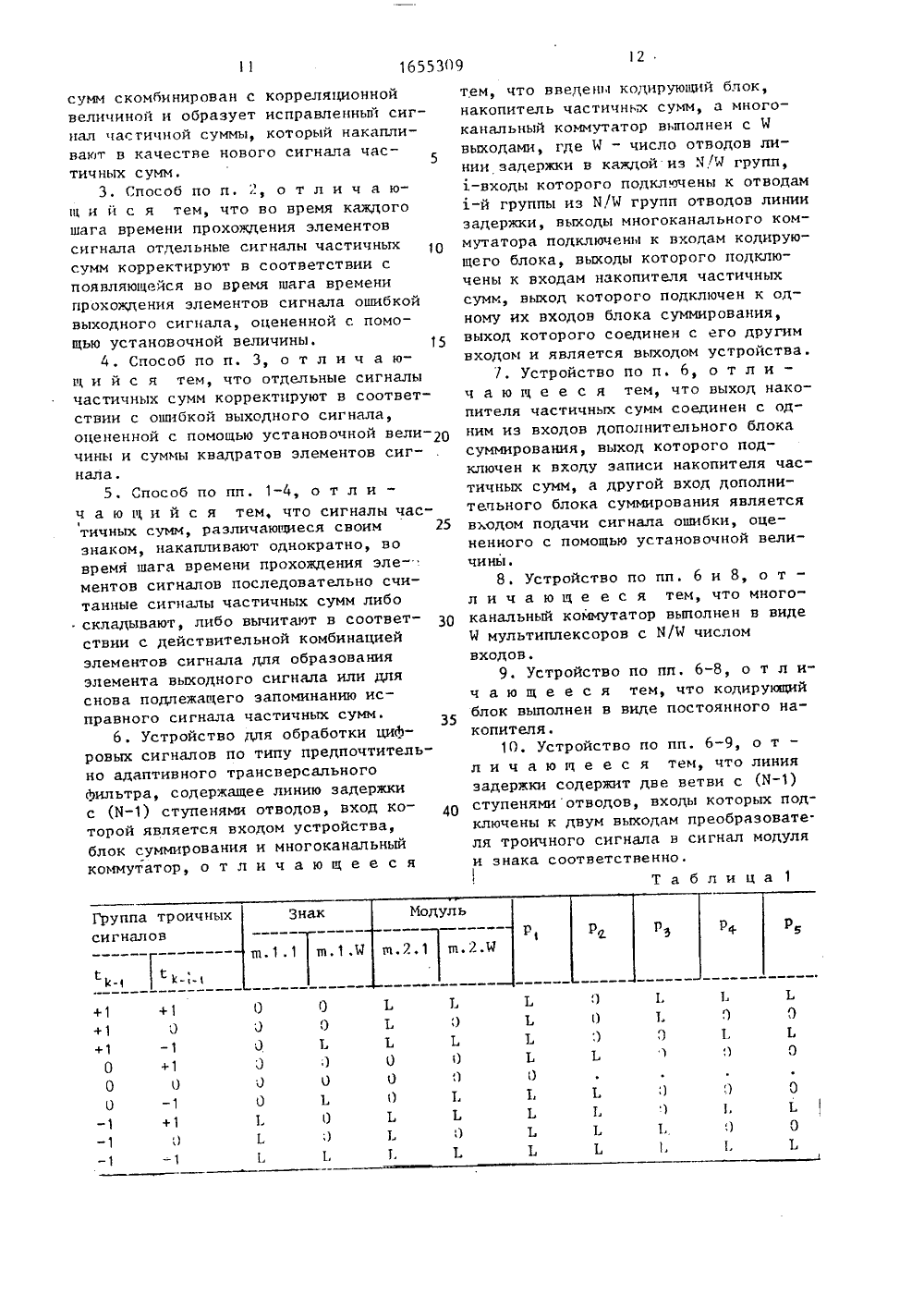

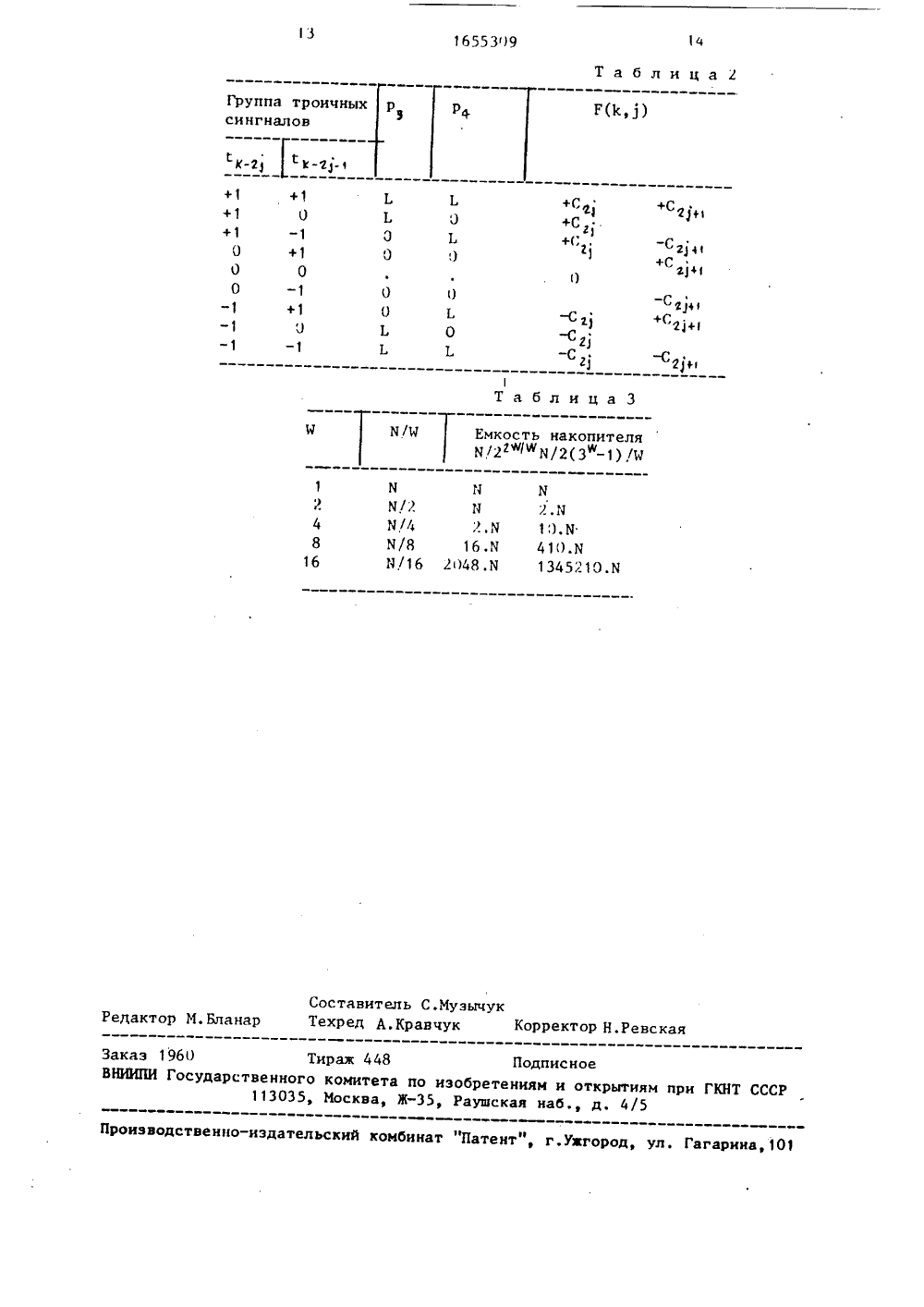

(51)5 Н )3 Н 2170 ОПИСАНИЕ ИЗОБРЕТЕНИЯК ПАТЕНТУ РЛ РРР ГР 5 РР(Ф-(уФ 7 Д 1 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССРУ 898592, кл . Н )3 Н 1 704, 4 . 12 .79,2(54) СПОСОБ ОБРАБОТКИ ЦИФРОВЬ)Х СИГНА-ЛОВ ПО ТИПУ ПРЕДПОЧТИТЕЛЬНО АДАИТИВ" . НОГО ТРАНСВЕРСАЛЬНОГО фИЛЬТРАИ УСТРОЙСТВО ДЛЯ ЕГО ОСУЦЕСТВЛЕНИЯ(57) Изобретение относится к радиотехнике. Пель изобретения - повышение быстродействия. Для осуществления способа обработки цифровых сигналов используется устройство, содержащее преобразователь 1 троичного сигнала в сигнал модуля и знака, линию задержки "., имеющую две ветви с отво3 1655309 4 10 дагпг, многоканальный коммутатор 3,состоящий из мультиплексоров, кодирующий блок 4, накопитель 5 частичных сумм, блоки 6 и 7 суммирования,состоящие каждый из сумматора и двухвходных регистров, счетчик 8, умножитель9 и коммутор 10.Для повышения быстродействия накопление сигналов суммосуществляют путем суммирования частичных сумм соответствуюг 1 гих И/Ч (гдеИЮ) следующих друг за другом группЛ , где А - число уравнений элементов сигнала; И - число следующих Изобретение относится к радиотехнике и может быть использовано и системах передачи сигналов для адаптивной коррекции искажений.Цель изобретения - повышение быстродействия.На чертеже приведен пример выполнения устройства для осуществления способа обработки циАровых сигналов по типу предпочтительно адаптивного трансверсального Аильтра.Устройство содержит преобразователь 1 троичного сигнала в сигналмодуля и знака, линию 2 задержки,имеющуи две ветви 2.1 и 2.2 и отводы2.1.0-2.1. (г 1-1) и 2.2.)-2.2. (М),многоканальный коммутатор опроса 3,содержащий мультиплексоры 3.1.1-3.1.Ч,3,2,1-3.2,И, кодирующий блок 4, накопитель 5 частичных сумм, блок 6 суммирования, содержащий сумматор 6,1 ивходные регистры 6.2 и 6,3, дополнительный блок 7 суммирования, содержащий сумматор 7.1 и входные регистры7.2 и 7.3, счетчик 8, умножитель 9,коммутатор 1 г 1, вход 11.В предлагаемом способе обработки 45циАровых сигналов по типу предпочтительно адаптивного трансверсальногоАильтра используется следующий алгоритм обработки.В (Б)-ступенчатом трацсверсаль 50ном Аильтре величина элементавыходного сигнала, содержащегося вовременном элементе 1, может быть описана какй-6551:огде Ж - величины элементов сигналак.,отвода, гоявляющиеся в этомвремецном элементе в отдруг за другом в группе задержанныхэлементов сигнала, возможных комбинаций следующих друг эа другом в группе задержанных элементов сигнала.При этом во время каждого шага времени прохождения элементов сигнала сучетом И/И действительных комбинацийзадержанных элементов соответствующие сигналы частичных сумм последовательно считывают и суммируют другс другом с образованием элементоввыходного сигнала . 2 с . и 8 з.п.А-лы, 1 ил ., 3 табл,дельных отводах линии 2 задержки;С - М коэВЬициентов Аильтра,которые определяют свойства Аильтра (частотную характеристику, временнуюхарактеристику).В случае адаптивной настройки Аильтра отдельные коэААициенты С; Аильтра могут быть постепенно установлены посредством итерации, которая может быть описана с помощью Аормулы лС к 1 "(к 1 8к ,где 8 представляет собой так называемую регулирующую величину, которая определяет время установки Аильтра в желаемое состояние и требуемые коэААициенты длины слова и тем самым точность Аильтра, которая, однако для обеспечения надежной установки (сходи- мости Аильтра) также не может быть выбрана слишком большой, Ь являетсякошибкой, остающейся по отношению к преследуемой заданной величице рассмотренного элемента выходного сигнала. Вместо такой ошибки можцо в случае необходимости использовать только еелзнак зВп(6 к) как Устацовочцыц кРитерий.Предлагаемое устройство имеет прежде всего на своем входе снабженную отводами (О 1 р 2 Зр М 2 М 1) (11 1) - ступенчатую линию 2 задержки, на вход которой поступает подлежащий обработ - ке циАровой сигнал, В преобразователе 1 подводимый на вход 11 линии 2 задержки подлежащий обрдбогке троичный сигнал прежде всего ггпу рекодируют в пару бинарных сигналов, охватывающую двоичный сигнал модуля ц,гвоич 1655.3) 95 1 О 15 20 25 ЗО 35 40 45 50 ный сигнал зцака. Линия 2 задержки имеет (3-1)-ступенчатую ветвь 2.1, в которую поступает двоичцыц сигнал знака, и (И)-ступенчатую ветвь в которую поступает двоичцыц сигнал модуля . Кащая группа из И друг за другом следующих отводов линии 2 задержки, имеющей И/И групп отводов, соединена с группой входов, соответствующих этой группе отводов, многоканального коммутатора 3, имеющего И/И групп входов. Многоканальный коммутатор 3 может иметь для каждой ветви 2.1, 2,2 линии задержки соответственно Ы синйазно управляемых с помощью спетчика 8 мультиплексоров 3. 1. 1-3. 1.И, 3. 2. 1-3. У с М/У входами, соответствующие входы которых подсоединены к соответствующим друг другу отводам отдельных групп отвопов. В примере исполнения, в котором 0=2 друг за другом следующих отводов объединены в группу, при этом образующие такую группу отводы .1.0, 2.1.1, имеющие 11 Ф=И,/2 таких групп отводов 2.1,0-.,1.(И) ветви 2.1 линии 2 задержки, соединены с соответствующими этой группе отводов первыми входами обоих мультиплексоров 3.1.1 и 3.1 Л, а следующая группа обоих отводов 2.1.2 и 2.1.3 соединена с вторыми входами этих мультиплексоров и т,д., отводы 2.1.(И) и 2.1(И - 1), образующие последнюю группу отводов, соединены с послед - ними входами обоих мультиплексоров 3.1.1 ц 3.1,У.Подобным образом соединены отводы второй ветви 2.2 линии задержки с входами мультиплексоров 3.2.1-3.2,И.Многоканальный коммутатор 3, образованный посредством четырех мультиплексоров 3.1.1-3.2.И, может быть в И/У раз быстрее, чем линия 2 задержки, так что на каждый шаг задержки, т.е. в каждый временной элемент, считываются все отводы линии задержки.Выходы мультиплексоров 3.1.1 - 3.2.И подключены к общему кодирующему блоку 4, образованному в примере исполнения посредством постоянного блока памяти (КОМ), в котором считанная с помощью многоканального коммутатора 3 пара следующих друг за другом элементов троичного сигнала, т.е. соответствующий такой паре элементов троичцого сигнала квадруполь,. может быть перекодировац следующим 1 из табл . 1 способом с помощью элсмецтов двоичного сигнала, появляющихся ца соответствующих отводах обоих ветвей ,1 и 2.2 линии задержки.В табл . 1 в колонках , ц приводятся возможные пары следуюих один за другим элементов троичцого сигнала, а в колонках ш.1.1, ш.1,И, ш.2.1 и ш.2.И им соответствующие, появляющиеся на выходах мультиплексоров 3.1.1, 3.1.И, 3.2,1 и 3.2.К биты сигнала знака и сигнала модуля. Появляющеся на выходах кодирующего блока ч управляющие биты р, -р , соответствующие отдельным квадруполям битов сигнала знака и сигнала модуля, приведены в табл. 1 в колонках р,-рПри этом управляющие биты ри р , в дополнение к групповому адресу, выданному счетчиком 8, служат выборке накопительных ячеек накопителя 5 сигналовчастичных сумм.В накопителе 5, выполненном при адаптивном фильтровании сигналов, как накопитель считывания и записи (ВАМ), накапливают сигналы частичных сумм, соответствующие А 1/1 возможным комбинациям У друг за другом следующих сигнальных элементов А-значимого ципрового сигнала из И/У друг за другом следующих групп элементов цифрового сигнала из соответствующих, оцененных согласно соответствующей настройке фильтра элементов сигнала отвода. В рассматриваемом здесь примере исполнения с И=2 и А=З в накопителе 4 под каждым групповым адресом, т,е. соответственно для каждой 1-й группы отводов (с З=),М/Ы), в принципе накапливают частичные суммы, указанные соответственно в колонке Р табл . 2, где отдельные слагаемые представляют соответствующие данному индексу коэААициецты Аильтра. Видно, что в принципе накапливают частичные суммы, соответствующие А"=3 =9 возможным комбинациям и 1=2 следующих друг за другом элементов троичного сигнала, из соответствующих, оцененных согласно настройке фильтра, т.е. умноженных на соответствующие козААициенты фильтра И=2 элементов С,С. сигнала от -23- вода, из которых затем согласно парам р.1, р управляющих битов - и тем самым ь соответствии со считанными .элементами сигнала отвода считывают частичную сумму.(СО -- 1) троичных сигк -г 1 ь 1фф 115 палов и для соответствующих табл, 1 уиранля 1 ор 1 их битов р р+ результирующие согласно выражениюЧЧ-Г1(1 с,3)=, а, С +17Ч=О 1 О частных сумм и оцененных с помощью коэАициента С фильтра элементов а; сигнала отвода группы из таких элементов сигнала.Требуемая для накопления частичных сумм емкость накопителя уменьшается, если накапливают только отличные от нуля сигналы частичных сумм и если при знакосимметричном цицероном сигнале только однократно запоминают отличающиеся только своим знаком сигналы частичных сумм, причем тогда в течение каждого шага задержки в соответствии с действительной комбинацией элементов цифрового сигнала прибавля ют или вычитают последовательно считанные сигналы частичных сумм для образования элемента выходного сигнала, а также снова подлежащего запоминанию исправленного сигнала частичных сумм, Таким образом, как это видно из следующих пояснений работает также схема согласно чертежа.Выход накопителя 5 частичных сумм соединен с входным регистром 6.2 блока 6 суммирования сигналов, выходной сигнал которого поступает на вход входного регистра 6,3, что позволяет последовательно суммировать сигналы частичных сумм, считываемые для каж дого шага задержки из накопителя 5.Причем появляющийся на выходе кодирующего блока 4 управляющий бит (р в табл. 1) указывает прибавляется (при р =11) или вычитается (при 45 р =1) находящаяся но входном регистре 6.2 частичная сумма, посредством управляющего бита (р =О в табл.1), появляющегося на выходе кодирующего устройства 4, запирается входной регистр 6,2, если мгновенно достигнутая сумма свертки должна оставаться неизменной, так что не происходит ни сложения, ни вычитания. Если в течение элемента задержки были суммияова 55 ны сигналы частичных сумм, соответствующие поянляюксимся в отводах .1.И,1(Я), 2,2.)-2.:(И) линий задержки элементам цид)роньж сигналов,т. е, были последовательно считаны и друг с другом сложены соответствующие сигналы частичных сумм для соответствующего шага задержки н соответствии с И/М действительными комбинациями троичных сигналов, то н заключении на выходе блока 6 получают соответствующий обработанный, т.е. "отфильтрованный", элемент выходного сигнала 6.Чтобы входной цифровой сигнал был правильно переработан в выходной циА- роной сигнал, т.е. в известной степени (во временном диапазоне) отфильтрован, соответствующие желаемой характеристике фильтра сигналы частичных сумм должны быть накоплены в накопителе 5 частичных сумм. В схеме сигналы частичных сумм с процессе адаптации итеративно образуются тем, что каждый из,последовательно считанных сигналов частичных сумм, будучи скомбинированным с корреляционной велииной, образует исправленный сигнал частичных сумм, как новый сигнал частичных сумм, Для этого выход накопителя 5 соединен с одним входным регистром 7.3 дополнительного блока 7, управляемым также с помощью кодирую- щего блока и который имеет второй входной регистр 7.2 для появляющегося но вречя каждого шага задержки сигналЛД ь, ошибки, оцененного с помощью регулирующей величины Я. Выход дополнительного блока 7, на котором образуется сигнал 8 соединен с входом записи накопителя 5.Сигнал Ь 6ошибки представляет собой отклонение выходного сигнала С от заданной величины и может бьггь образован различными способами, например путем вычитания из вь 1 ходного сигнала б этого же выходного сигнала, оцененного с помощью триггера 111 митта.Сигнал Дб ошибки может также быть соответственно усреднен и/или должен 1 также быть эААективным только по свое;му знаку, что здесь, однако, также более подробно не должно прослеживаться.Сигнал Ь ь ошибки в дополнение клоценке с помощью регулирующей величины я может также быть оценен с помощью величины г 1, т.е. бьгть умноженным, причем в зависимости от выдаваемого кодирующим блоком управляющего бита рвеличина Ч при р=О) имеет значение "1" ипи (при р =1) значение "2". Как видно из табл. 1 величина г 1 равна65539 ТЕф 1) новая (.1)старая "- "1- к 3 20 55 сумме квадратов с:штдццых Ь= элеме- тов сигнала отвода, 11 осредством дополнительной оцецки сигнала опибки с помощью этой суммы квадратов эле 5 ментов сигцалд отвода или с помощьют скалярного произведения давектог к 1 ра (вектор - строка д ) описывающе к,)го с помощью своих чдстичньх компонецВ табл. 2 представлены при цифровом сигнале с тремя значениями (троичном сигнале) и групповом объединении соответственно И= . элементов отвода девять возможных частичных сумм Г(1,1) . Если вместо этого должен быть обработан двузначдций, т.е. имеющий только два значенияи -1 цифровой сигнал (двоичный сигнал), причем в отличие от чертежа, тогда при отсутствии преобразователя 1 кодов требуется предусмотреть только 25 одну ветвь линии 2 задержки, то при групповом объединении соответственно 1=2 элементов сигналов отвода являются возможными только четыре двухзвецные частичнье суммы Г табл . 2.Вообще накопление частичных сумм при А-значимом, знакосимметричном цифровом сигнале требует емкость накопителя 5 равную: 1/2 А И/И частичФнык сумм при четном значении А подле 35 жащего обработке цифрового сигнала, причем коэффициент 1/2 появляется ввиду того, что при знакосимметрии цифрового сигнала должна быть накоплена только полонина возможных вели чин частичных сумм. 11 ри нечетном значении А число подлежа%х накоплению величин частичных сумм уменьшается на единицу, так как ) не требуется запоминать, в таком случае требует ся емкость цакопителя 5, равная 1/2(А - 1)И/И частичных сумм.В табл. 3 приводится число И/И требуемых ца шаг задержки арифметических операций для различных длин50 групп, а также требуемая для накопления частичных сумм емкость накопителя для силлетричого двоичного сигнала и для симметричного троцчного сигнала,Видно, что при 0=2 получаетсяуменье;ие вдвое числа требуемыхарифметических опердни (в сравнениис 1=1 соответствующим известным-д-уность элемецтов цифрового сц дд, появляюшхся в 1 с - м временном э.лсте в отводах по пинии, задержк, д самого себя (вектор - столбец д ., ) в случае цеобходцмости может быть ускорена адаптация частицх сумм,описывающаяся с помощью: трансверсалььпфильтром), причемеобходимдя емкость накопителя прифильтрации двоичного сигнала не попы -шается в то время, как при фильтрацшции троичного сигнала она удваивается. Формула изобретения 1. Способ обработки цифровых сигналов по типу предпочтительного адаптивного трансверсального фильтра, заключающийся в пошаговой задержке времени прохождения элементов сигнала на (И) пагов времени задержки, накоплении сигналов, которые соответствуют группе задержанных элементов сигналов, оцениваемых с учетом массовых коэффициентов, причем во время шагов времени прохождения элементов сигналов с учетом действительных комбинаций задержанных элементов сигналов соответствующие сигналы последовательно считывают, суммируют друг с другом с образованием элементов выходного сигнала, о т л и ч а ю щ и й с я тем, что, с целью повьппения быстродействия, накопление сигналов сумм осуществляют путем суммирования частичных сумм соответствующих И/Я (где Ы(И) следующих друг эа другом групп А , где А - чисФло уравнений элементов сигнала, Ы - число следуюх друг за другом в группе задержанных элементов сигнала, возможных комбинаций следующих друг за другом в группе задержанных элементов сигнала, при этом во время кажцого пага времени прохождения элементов сигнала с учетом И И действительных комбинаций задержанных элементов сигналов, соответствуобщие сигналы частичных сумм последовательно считывают и суммируют друг с другом с образованием элементов выходного сигнала.2. Способ по и. 1, о т л и ч а юп и й с я тем, что каждый из последовательно считаццых сгцдлов частичцьх) 1. Ь Ь сумм скомбинирован с корреляционнойвеличиной и образует исправленный сигнал частичной суммы, который накапливают в качестве нового сигнала час 5тичных сумм.Э. Способ по п. 2, о т л и ч а ющ и й с я тем, что во время каждогошага времени прохождения элементовсигнала отдельные сигналы частичныхсумм корректируют в соответствии споявляющейся во время шага временипрохождения элементов сигнала ошибкойвыходного сигнала, оцененной с помощью установочной величины. 154. Способ поп. 3, о тлич ающ и й с я тем, что отдельные сигналычастичных сумм корректируют в соответствии с ошибкой выходного сигнала,оцененной с помощью установочной велиОчини и суммы квадратов элементов сигнала,5. Способ по пп. 1-4, о т л ич а ю щ и й с я тем, что сигналы час 1тичных сумм, различающиеся своим 25знаком, накапливают однократно, вовремя шага времени прохождения эле-.ментов сигналов последовательно считанные сигналы частичных сумм либоскладывают, либо вычитают в соответ- ЗОствии с действительной комбинациейэлементов сигнала для образованияэлемента выходного сигнала или дляснова подлежащего запоминанию исправного сигнала частичных сумм,6. Устройство для обработки циЬровых сигналов по типу предпочтительно адаптивного трансверсальногофильтра, содержащее линию задержкис (М) ступенями отводов, вход ко Оторой является входом устройства,блок суммирования и многоканальныйкоммутатор, о т л и ч а ю щ е е с я тем, что введены кодирующий блок,накопитель частичных сумм, а многоканальный коммутатор выполнен с Чвыходами, где М - число отводов линии задержки в каждой из М/4 групп,1.-входы которого подключены к отводамд-й группы из М/М групп отводов линиизадержки, выходы многоканального коммутатора подключены к входам кодирующего блока, выходы которого подключены к входам накопителя частичныхсумм, выход которого подключен к одному их входов блока суммирования,выход которого соединен с его другимвходом и является выходом устройства.7. Устройство по и. 6, о т л и -ч а ю щ е е с я тем, что выход накопителя частичных сумм соединен с одним из входов дополнительного блокасуммирования, выход которого подключен к входу записи накопителя частичных сумм, а другой вход дополнитепьного блока суммирования являетсяводом подачи сигнала ошибки, оцененного с помощью установочной величины.8. Устройство по пп. 6 и 8, о тл и ч а ю щ е е с я тем, что многоканальный коммутатор выполнен в видеЧ мультиплексоров с Я/Ы числомвходов.9. Устройство по пп, 6-8, о т л ич а ю щ е е с я тем, что кодирующийблок выполнен в виде постоянного накопителя,10. Устройство по пп. 6-9, о тл и ч а ю щ е е с я тем, что линиязадержки содержит две ветви с (Я)ступенями отводов, входы которых подключены к двум выходам преобразовате.ля троичного сигнала в сигнал модуляи знака соответственно.Таблица 1-С ц Сг) С г 1 н 1Таблица 3 1 Емкость накопителя м гуам/23 е 1 /1 2.И1,). М410.М1345210.И Составитель С.МузычукРедактор М.Бланар Техред А.Кравчук Корректор Н.Ревская Заказ 1960 Тираж 448 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

СмотретьЗаявка

3818872, 30.11.1984

ХАЙНРИХ ШЕНК

МПК / Метки

МПК: H03H 21/00

Метки: адаптивного, предпочтительно, сигналов, типу, трансверсального, фильтра, цифровых

Опубликовано: 07.06.1991

Код ссылки

<a href="https://patents.su/7-1655309-sposob-obrabotki-cifrovykh-signalov-po-tipu-predpochtitelno-adaptivnogo-transversalnogo-filtra-i-ustrojjstvo-dlya-ego-osushhestvleniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ обработки цифровых сигналов по типу предпочтительно адаптивного трансверсального фильтра и устройство для его осуществления</a>

Предыдущий патент: Шаблон для кассет с магнитной лентой

Следующий патент: Радиовещательный передатчик с амплитудной модуляцией

Случайный патент: Способ регенерации и обогащения корунда