Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

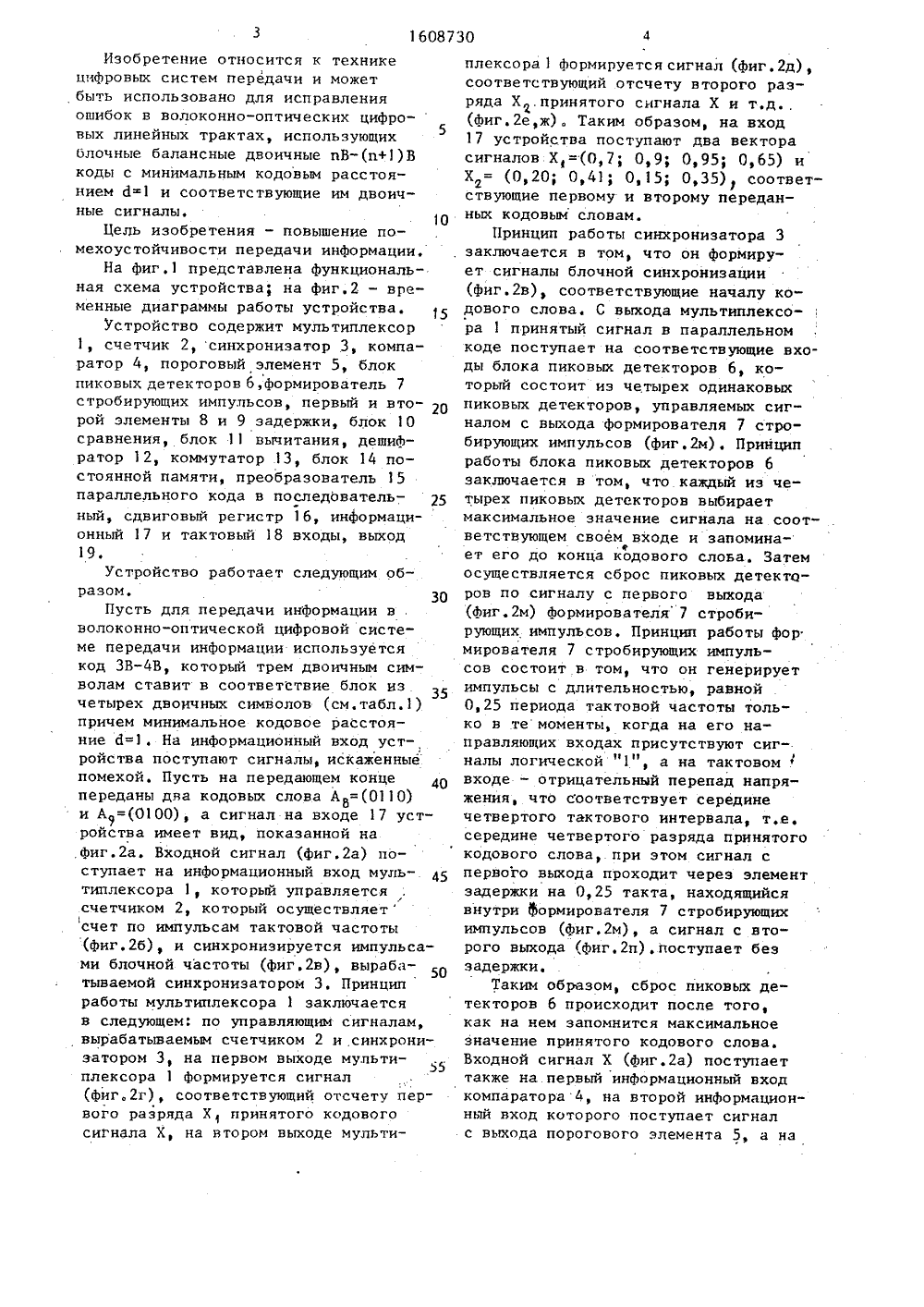

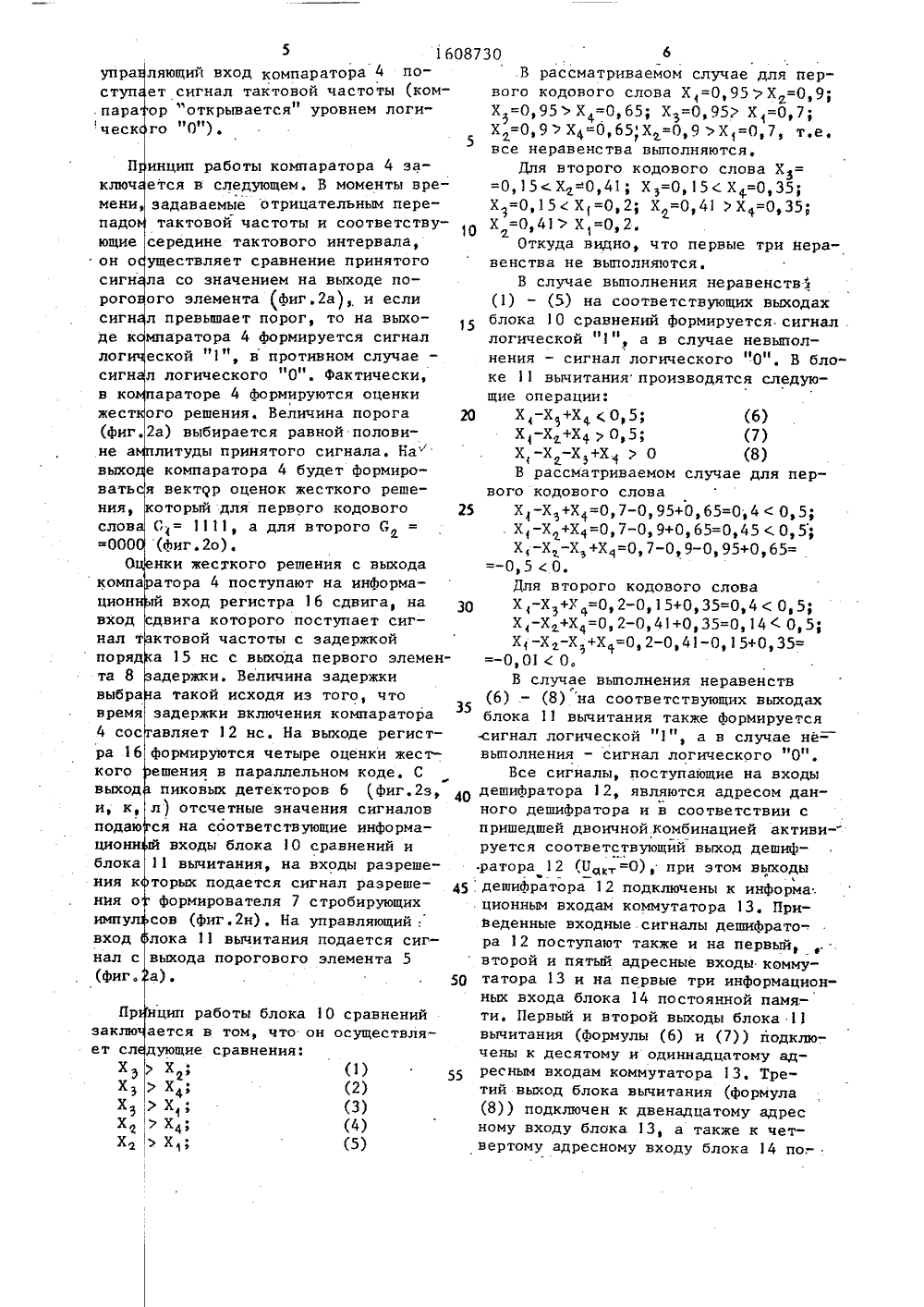

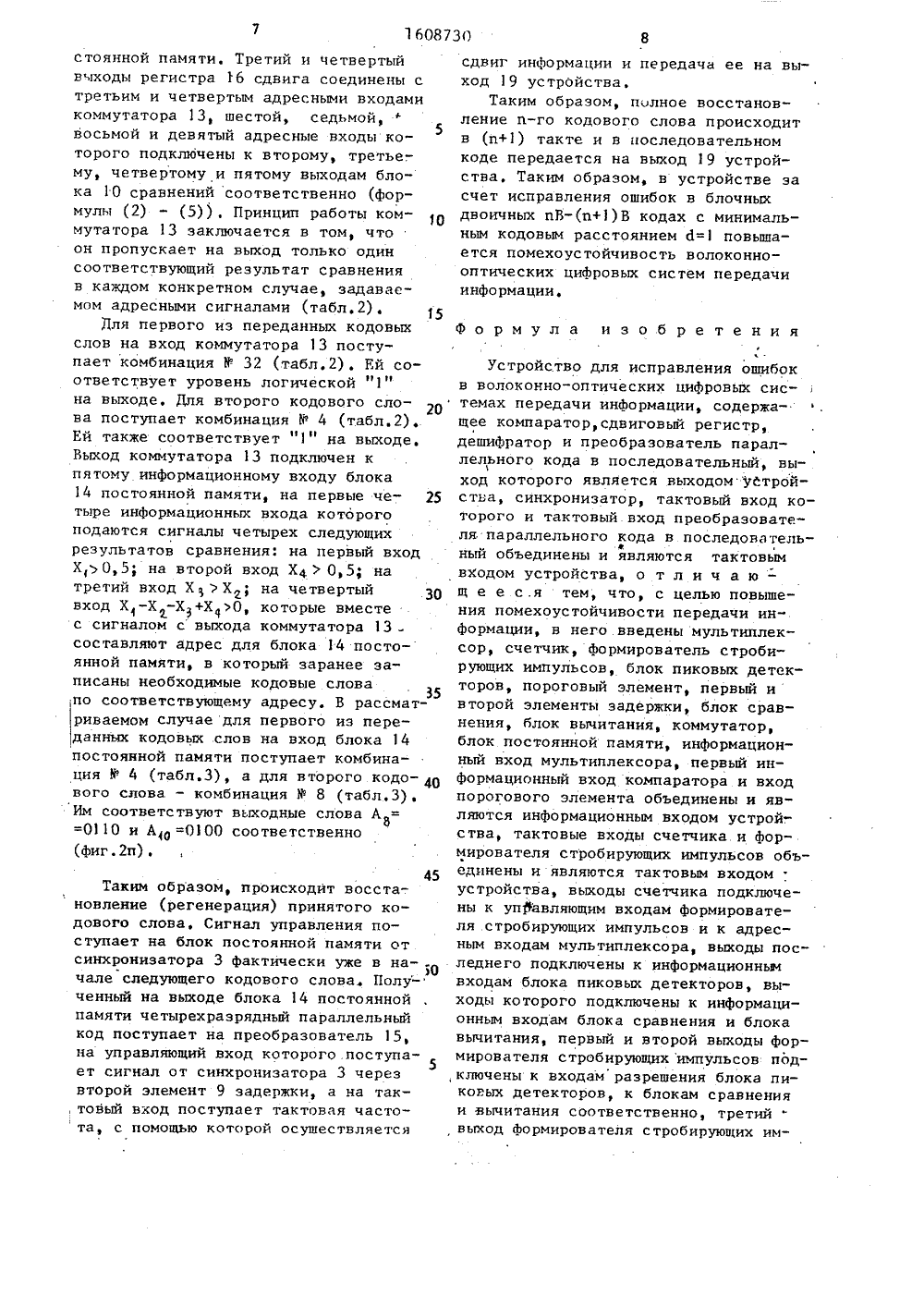

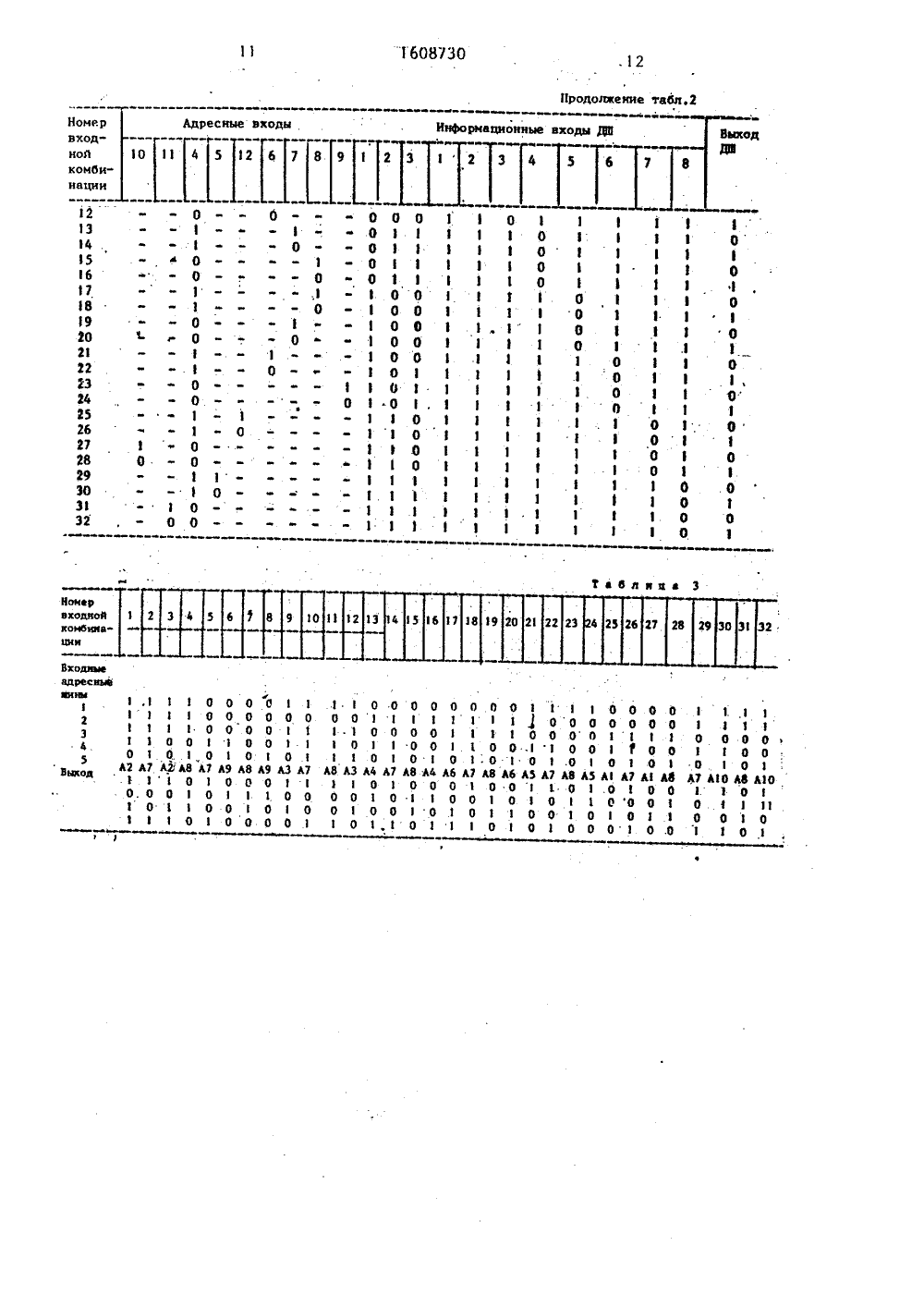

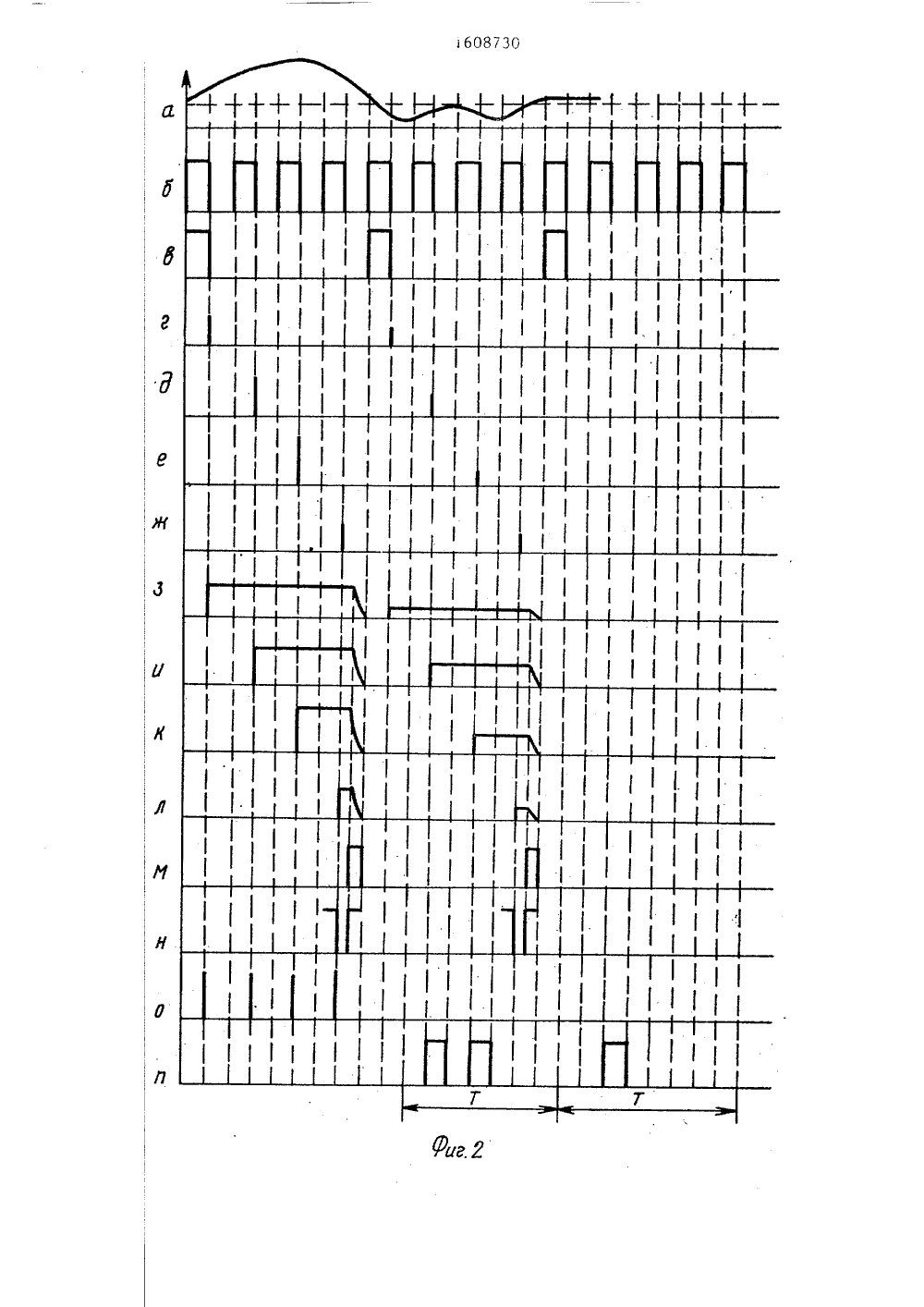

СОЮЗ СОВЕТСНИХСОЦИАЛ ИСТИЧЕСНИХРЕСПУБЛИК 8 С 250 51) 5 ОС ОИ РИ(46) 654370/24-242.02.893.11.90. Бюлнститут радиН АрмССРАРСТВЕННЫЙ НОМИТЕТБРЕТЕНИЯМ И ОТНРЫТИЯМТ СССР 21,398(088,8)вторское свидетельство СССР 028, кль С 08 С 25/00, 1 988СТРОИСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИВОЛОКОННО-ОПТИЧЕСКИХ ЦИФРОВЫХПЕРЕДАЧИ ИНФОРМАЦИИИзобретение относится к технике выл систем передачи и может быть ьзовано в устройствах для ис" ения ошибок в волоконно-оптих цифровых линейных трактах, исующих блочные балансные двоичные(53) 6 (56) А 9137 (54) У БОК СИСТ МАХ (57) цифр испо прав ческ поль 2пК-(и+1)Б коды с минимальным кодовым расстоянием Й=1 и соответствующие им двоичные сигналы. Цель изобретения - повышение помехоустойчивости передачи информации. Поставленная цель достигается введением в устройство содержащее компаратор 4, сдвиговый регистр 16, дешифратор 12, преобразователь 15 параллельного кода,.в последовательный и синхронизатор 3, мультиплексора 1, счетчика 2 формирователя 7 стробирующих импульсов, блока 6 пиковых детекторов, порогового элемента 5, двух элементов 8 и 9 задержки, блока 10 сравнения, блока 11 вычитания, коммутатора 13 и блошка 14 постоянной памяти с соответствующими связями, 2 ил., 3 табл.30 Изобретение относится к техникецифровых систем передачи и можетбыть использовано для исправленияошибок в волоконно-оптических цифровых линейных трактах, использующих5блочные балансные двоичные пВ-(и+1) Вкоды с минимальным кодовым расстоянием с 1 1 и соответствующие им двоичные сигналы,ОЦель изобретения - повышение помехоустойчивости передачи информации,На фиг,1 представлена Функциональная схема устройства; на фиг.2 - временные диаграммы работы устройства,Устройство содержит мультиплексор1, счетчик 2, синхронизатор 3, компаратор 4, пороговый элемент 5, блокпиковых детекторов 6,формирователь 7стробирующих импупьсов, первый и второй элементы 8 и 9 задержки, блок 10сравнения, блок 11 вычитания, дешифратор 1 2, коммутатор 13, блок 14 постоянной памяти, преобразователь 15параллельного кода в последовательгный, сдвиговый регистр 16, информационный 17 и тактовый 18 входы, выход19,Устройство работает следующим образом,Пусть для передачи информации в,волоконно-оптической цифровой системе передачи информации используетсякод ЗВВ, который трем двоичным символам ставит в соответствие блок изчетырех двоичных символов (см.табл,1)причем минимальное кодовое расстояние 6=1. На информационный вход устройства поступают сигналы, искаженныепомехой, Пусть на передающем конце 40переданы два кодовых слова А=(0110)и А=(0100), а сигнал на входе 17 устройства имеет вид, показанной на,Фиг,2 а. Входной сигнал (фиг.2 а) поступает на инФормационный вход мультиплексора 1, который управляетсясчетчиком 2, который осуществляетсчет по импульсам тактовой частоты(фиг.2 б), и синхронизируется импульсами блочной частоты (фиг.2 в), вырабатываемой синхронизатором 3. Принципработы мультиплексора 1 заключаетсяв следующем: по управляющим сигналам,вырабатываемым счетчиком 2 и синхронизатором 3, на первом выходе мупьтиплексора 1 формируется сигнал(фиг.2 г), соответствующий отсчету первого разряда Х 1 принятого кодовогосигнала Х, на втором выходе мультиплексора 1 Формируется сигнал (Фиг.2 д),соответствующий отсчету второго разряда Х.принятого сигнала Х и т,д(Фиг.2 е,ж) . Таким образом, на вход17 устройства поступают два векторасигналов Х=(0,7; 0,9 0,95; 0,65) иХ = (0,20; 0,41; 0,15; 0,35) соответствующие первому и второму переданных кодовым словам.Принцип работы синхронизатора 3заключается в том, что он Формирует сигналы блочной синхронизации(фиг.2 в), соответствующие началу кодового слова. С выхода мультиплексора 1 принятый сигнал в параллельномкоде поступает на соответствующие входы блока пиковых детекторов 6, который состоит из четырех одинаковыхпиковых детекторов, управляемых сигналом с выхода формирователя 7 стробирующих импульсов (фиг,2 м) . Принципработы блока пиковых детекторов 6заключается в том, что каждый из четырех пиковых детекторов выбираетмаксимальное значение сигнала на соответствующем своем входе и запоминает его до конца кодового слова, Затемосуществляется сброс пиковых детекторов по сигналу с первого выхода(Фиг.2 м) Формирователя 7 стробирующих импульсов. Принцип работы формирователя 7 стробирующих импульсов состоит в том, что он генерируетимпульсы с длительностью, равной0,25 периода тактовой частоты только в те моменты, когда на его направляющих входах присутствуют сигналы логической "1", а на тактовомвходе - отрицательный перепад напряжения, что соответствует серединечетвертого тактового интервала, те.середине четвертого разряда принятогокодового слова, при этом сигнал спервого выхода проходит через элементзадержки на 0,25 такта, находящийсявнутри Формирователястробирующихимпульсов (Фиг.2 м), а сигнал с второго выхода (Фиг.2 п),поступает беззадержки,Таким обрезом, сброс пиковых детекторов 6 происходит после того,как на нем запомнится максимальноезначение принятого кодового слова. Входной сигнал Х (Фиг.2 а) поступает также на первый информационный вход компаратора 4, на второй информационнь 1 й вход которого поступает сигнал с выхода порогового элемента 5, а на5 1608730 ляющий вход компаратора 4 поет сигнал тактовой частоты (ком- в ор "открывается" уровнем логи- Х го 1 фОф 1), Х упра ступ .пара ческ П ключ мени, падо ющие он о сиги рого сиги де к лог сиги в ко жест (фиг, не а выхо вать ния,словкомпа ционвходнал т поряд та 8 выбра время 4 сос ра 16 кого выход и, к, подаю ционн блока ния к ния о импулвходнал с(фиг. Пр заклю ет слинцип работы компаратора 4 зается в следующем. В моменты врезадаваемые отрицательным пере- тактовой частоты и соответствусередине тактового интервала, уществляет сравнение принятого ла со значением на выходе поого элемента (фиг,2 а), и если л превышает порог, то на выхомпаратора 4 формируется сигнал еской "1", в противном случае л логического "0". Фактически, параторе 4 формируются оценки ого решения. Величина порога 2 а) выбирается равной половилитуды принятого сигнала. Ба" е компаратора 4 будет формироя вектор оценок жесткого решеоторый для первого кодового С = 1111, а для второго С (фиг.2 о).нки жесткого решения с выхода атора 4 поступают на информай вход регистра 16 сдвига, на сдвига которого поступает сигктовой частоты с задержкой а 15 нс с выхода первого элеменадержки. Величина задержки а такой исходя из того, что задержки включения компаратора авляет 12 нс. На выходе регистформируются четыре оценки жестешения в параллельном коде. Спиковых детекторов 6 (фиг.2 з, лотсчетные значения сигналов ся на соответствующие информай входы блока 1 О сравнений и 11 вычитания, на входы разрешеторых подается сигнал разрешеформирователя 7 стробирующих сов (фиг,2 н), На управляющий: лока 11 вычитания подается сигвыхода порогового элемента 5 а). нцип работы блока 10 сравнений ается в том, что он осуществлядующие сравнения:Х; (1)Х 4 ф (2), Х, (5) 6В рассматриваемом случае для нерого кодового слова Х=0,95Х =0,9;=0,95 Х, =0,65; Х=0,953 Х 1=0,7;2=0,9) Х 4=0,65 ХАМ=019) Х=0979 т евсе неравенства выполняются,Для второго кодового слова Х==0,15(Х=0,41; Х=0,15( Х 4=0,35;10 х =0941) х 1=092Откуда видно, что первые три неравенства не выполняются,В случае выполнения неравенств(1) - (5) на соответствующих выходахблока 10 сравнений формируется сигналлогической "1", а в случае невыполнения - сигнал логического "0". В бло"ке 11 вычитанияпроизводятся следующие операции:20 Х -Х+Х 4 ( О 5 (б)Х -Х+Х0,5; (7)Х,-Х -Х +ХО (8)В рассматриваемом случае для первого кодового слова25 Х-Х +Х=0,7-0,95+0,65=0;4 с 0,5;Х-Х+Х=0,7-0,9+0,65=0,45 ( 0,5Х,-Х -Х +Х=0,7-0,9-0,95+0,65==-0,01 ( О.В случае выполнения неравенств(6) . - (8) на соответствующих выходахблока 11 вычитания также формируетсясигнал логической "1", а в случае не=выполнения - сигнал логического "0".Все сигналы, поступающие на входы40 дешифратора 1 2, являются адресом данного дешифратора и в соответствии спришедшей двоичной комбинацией активируется соответствующий выход дешифратора 12 Яат=О), при этом выходыЬ. о45дешифратора 12 подключены к информа.ционным входам коммутатора 13, Приведенные входные. сигналы дешифратора 12 поступают также и на первый,второй и пятый адресные входы комму 50 татора 13 и на первые три информационных входа блока 14 постоянной памя. -ти. Первый и второй выходы блока 11вычитания (формулы (6) и (7 подклю-.чены к десятому и одиннадцатому адресным входам коммутатора 13. Третий выход блока вычитания (формула(8 подключен к двенадцатому адресному входу блока 13, а также к четвертому адресному входу блока 14 по;стоянкой памяти. Третий и четвертый вчходы регистра 16 сдвига соединены с третьим и четвертым адресными входами коммутатора 13, шестой, седьмой, восьмой и девятый адресные входы ко 5 торого подключены к второму, третье-.му, четвертому и пятому выходам блока 10 сравнений соответственно (Формулы (2) - (5, Принцип работы коммутатора 13 заключается в том, что он пропускает на выход только один соответствующий результат сравнения в каждом конкретном случае задаваемом адресными сигналами (табл,2).Лля первого из переданных кодовых слов на вход коммутатора 13 поступает комбинация У 32 (табл,2), Ей соответствует уровень логической "1" на выходе. Для второго кодового слова поступает комбинация У 4 (табл.2), Ей также соответствует "1" на выходе, Выход коммутатора 13 подключен к пятому информационному входу блока 14 постоянной памяти, на первые че тыре информационных входа которого подаются сигналы четырех следующих результатов сравнения: на первый вход Х,) 0,5; на второй вход Х0,5; на третий вход ХХ, на четвертый вход Х-Х -Х+Х 0, которые вместе с сигналом с выхода коммутатора 13- составляют адрес для блока 14 постоянной памяти, в который заранее записаны необходимые кодовые слова по соответствующему адресу. В рассматриваемом случае для первого из переданных кодовых слов на вход блока 14 постоянной памяти поступает комбинация 9 4 (табл.З), а для второго кодо вого слова - комбинация У 8 (табл.З). Им соответствуют выходные слова А =8 =0110 и Ао =0100 соответственно(фиг. 2 п) .45Таким образом, происходит восстановление (регенерация) принятого кодового слова, Сигнал управления поступает на блок постоянной памяти от синхронизатора 3 фактически уже в на- .10 чале следующего кодового слова Полу- ченный на выходе блока 14 постоянной памяти четырехразрядный параллельный код поступает на преобразователь 15, на управляющий вход которого поступа 5 ет сигнал от синхронизатора 3 через второй элемент 9 задержки, а на так, товый вход поступает тактовая частота, с помощью которой осушествляется сдвиг информации и передача ее на выход 19 устройства.Таким образом, полное восстановление и-го кодового слова происходит в (и+1) такте и в последовательном коде передается на выход 19 устройства. Таким образом, в устройстве эа счет исправления ошибок в блочных двоичных пВ-(и+1)В кодах с минимальным кодовым расстоянием Й= повышаается помехоустойчивость волоконнооптических цифровых систем передачи информации,Формула изобретенияФУстройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации, содержащее компаратор,сдвиговый регистр, дешифратор и преобразователь параллельного кода в последовательный, выход которого является выходом:устройства, синхронизатор, тактовый вход которого и тактовый вход преобразователя параллельного кода в последовательаный объединены и являются тактовым входом устройства, о т л и ч а ю - щ е е с .я тем, что, с целью повышения помехоустойчивости передачи ин" формации, в него введены мультиплексор, счетчик, формирователь стробирующих импульсов, блок пиковых детекторов, пороговый элемент, первый и второй элементы задержки, блок сравнения, блок вычитания, коммутатор, блок постоянной памяти, информационный вход мультиплексора, первый информационный вход компаратора и вход порогового элемента объединены и являются информационным входом устройства, тактовые входы счетчика и Формирователя стробирующих импульсов объединены и являются тактовым входом . устройства, выходы счетчика подключены к управляющим входам формирователя стробирующих импульсов и к адресным входам мультиплексора, выходы последнего подключены к информационным входам блока пиковых детекторов, выходы которого подключены к информационным входам блока сравнения и блока вычитания, первый и второй выходы формирователя стробирующих импульсов под,ключены к входам разрешения блока пиковых детекторов, к блокам сравнения и вычитания соответственно, третий " выход формирователя стробирующих имТ лица Ном ком бин Вход ход код кодет ии)010 000 001 010 011 0 6 1 О О 1 01 11 00 00 11 1 О 01 О 1 10 3 4 5 6 0 101 110 111 0100 101 аблица е вход Адре Выход нформационные входы 1 2 2 3О щ 1 ОО11 О1 1О1О 1; .2 О О О О О О О О О О О О О0.1ОО 1О О О О О О О О О ОО О О О6; ОО 1ОО 1 1. О1 ОО 1 О О 8;9;:О11 йуьсов подключен к управляющему входу, компаратора и через первый элемент н 111 з ержки к входу Сдвиг" сдвигового ре истра, выход порогового элемента по ключен к управляющему входу блока вычитания и к второму информацион ому входу компаратора, выход которо о подключен к информационному вх ду сдвигового регистра, первый и вт рой выходы которого подключены к ервому и второму входам дешифрато а, к первому и второму адресным вх дам коммутатора и блока"постоянно памяти, третий и четвертый выходысдвигового регистра подключены к тр тьему и четвертому адресным входа коммутатора, первый выход блокасравнения подключен к третьему вх ду дешифратора, к пятому адресному вх ду коммутатора и к третьему адресно у входу блока постоянной памяти, вт рой, третий, четвертый и пятый выхо ы блока сравнения подключены к шестому, седьмому, восьмому и девятому адресным входам коммутаторасоответственно, первый и второй выходы блока вычитания подключены кдесятому и одиннадцатому адреснымвходам коммутатора соответственнотретий выход блока вычитания подключен к двенадцатому адресному що входу коммутатора и к четвертому адресному входу блока постоянной памяти, выходы дешифратора подключены кинформационным входам коммутатора,выход которого подключен к пятомуадресному входу блока постоянной па"мяти, выходы которого подключены кинформационным входам преобразователя параллельного кода в последовательный, выход синхронизатора подключен к управляющим входам счетчика,1 блока постоянной памяти и через второй элемент задержки к управляющемувходу преобразователя параллельногокода в последовательный.1 . 11111 1 1111 11111 1 1 1 1111608730 12 Продолжение табл.2 Й Инфо риеционные входы Л 3 Ноиер вход" 1 2 6 У 32 1 Э 14 5 16а вв юаеаа 1 11 111О 31 1 01 10010 11 0 30 1О , " 1 О3 0 0 0 1 11 1 О 1. О 1 ОО01 О ., 0 е ав 18 19 20 2 22 2 Э 24 25 0а . е ааЭ 2 ю заалела Н М Номер входят комбкка" Входвкеадрескывша1З0 0 О 0 0 О0 00Л 7 А 8 А 5 1 0 10 3 .03 1 0 0 03 1 0АЬ Л 7 А 00 . 1 1 00 0 .01 1 00 0 О0 0 00 007 Л 8 А 40 0 03 000 10 0 0ОО0 8 АЗ А 4 0 0 0 01О 00 008 Л 0 0О. 0г Л 7 Лф АВ Аг 300.0 001 00 100 9 А 8 О 00О 3А А 7 ЛВьк О 0 1 00 3 01 1 0 03 0 0 О Адресные входы но 3 10 11 4 5 2 коиби- нации0 0 0О 0 00 0 00 00 0 О О 1 0О00О 1 ОО 3 О0О О 10131 3.0 0 0 0301 0 0.0300А 6 А 7 А 8 Лб Л 500 00 О03 03 0ООР 1 1 1 3 3 31 1.1 О 3ООО1О ,О 1 3 О1 0 3 3ОО 1 1 ОО

СмотретьЗаявка

4654370, 22.02.1989

ИНСТИТУТ РАДИОФИЗИКИ И ЭЛЕКТРОНИКИ АН АРМССР

МАРКАРЯН ГАРЕГИН СТЕПАНОВИЧ, АНДРЕСЯН АНДРЕЙ ГРАЧИЕВИЧ

МПК / Метки

МПК: G08C 25/00

Метки: волоконно-оптических, информации, исправления, ошибок, передачи, системах, цифровых

Опубликовано: 23.11.1990

Код ссылки

<a href="https://patents.su/7-1608730-ustrojjstvo-dlya-ispravleniya-oshibok-v-volokonno-opticheskikh-cifrovykh-sistemakh-peredachi-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации</a>

Предыдущий патент: Устройство для передачи информации по волоконно-оптической линии связи

Следующий патент: Магнитометрический детектор транспорта

Случайный патент: Способ разложения окиси углерода