Цифровой демодулятор сигналов с относительной фазовой модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

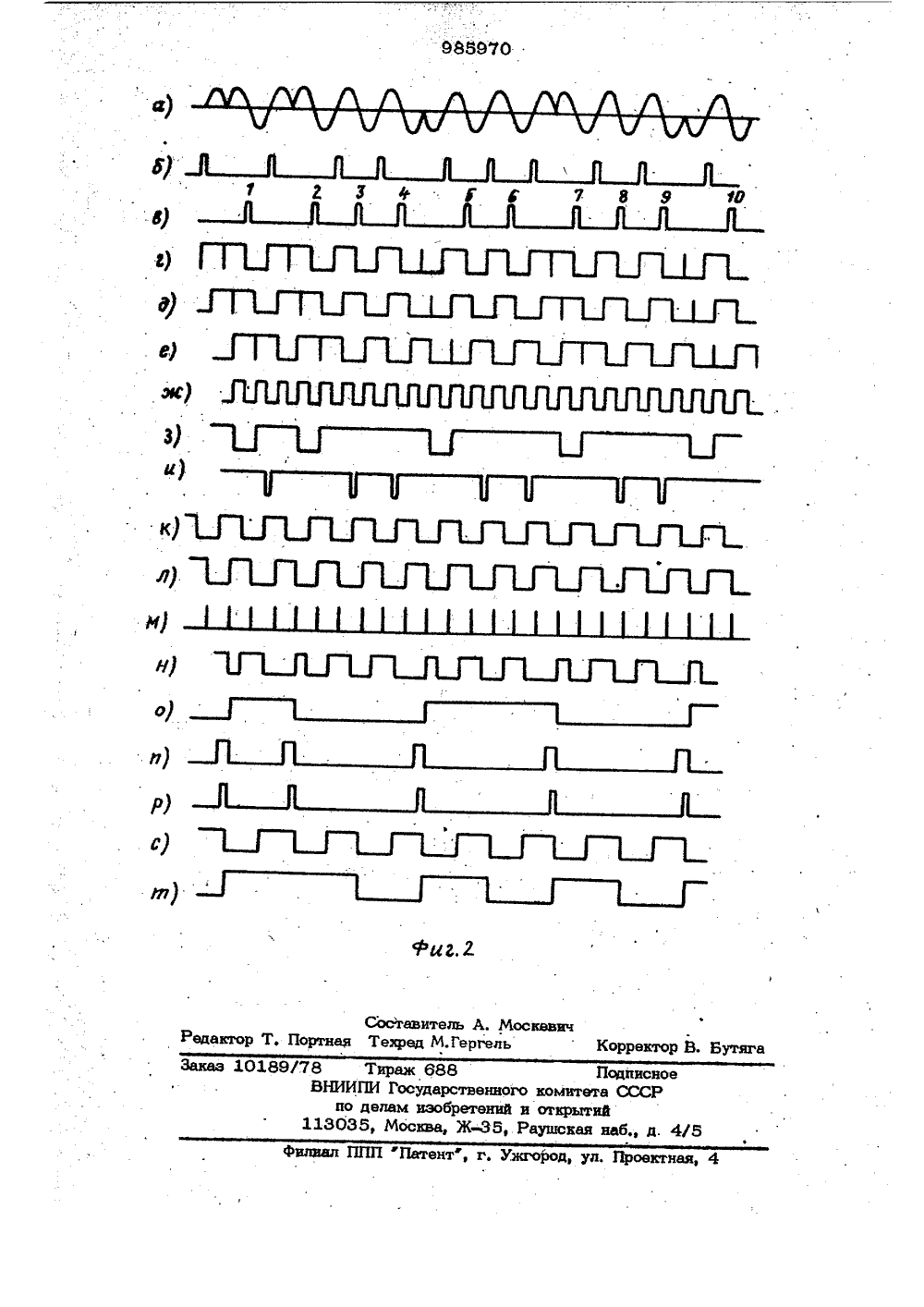

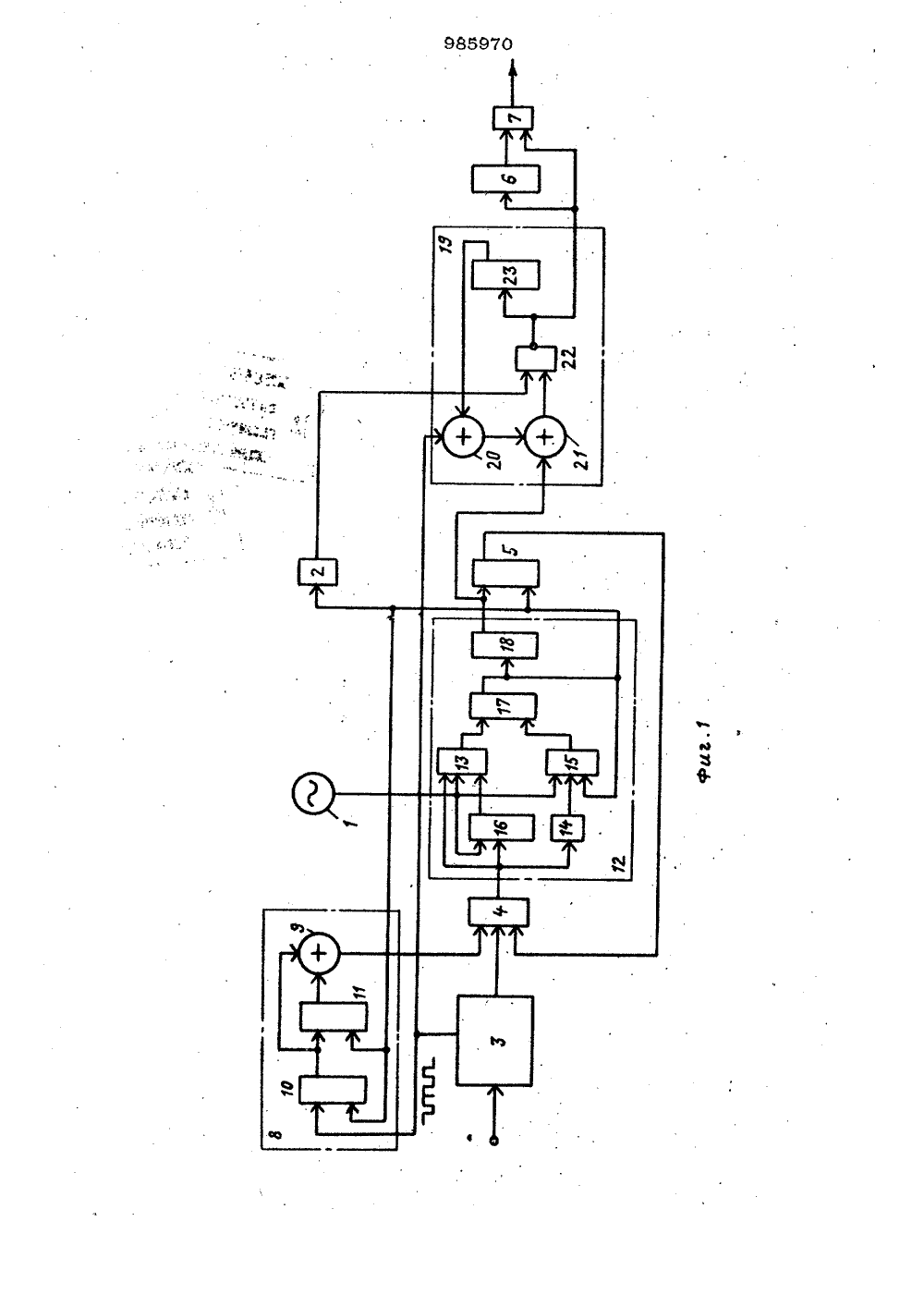

(84) ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОС ОТНОСИТЕЛЬНОЙ ФАЗОВОЙМОДУЛЯЦИЕЙ 1Изобретение относится к техннке асвязи и может использоваться в системах передачи дискретных сообщений.Известен цифровой демодулятор сигналов с относительной фазовой модуляцией, содержащий задающий генератор, выход которого подключен к первому входу блока выделения несущей частоты,и последовательно соединенйые формирователь входного сигнала, фазовый дискраминатор, выделитель тактовой частотыи выходной согласующий блок, второйвход которого соединен с выходом фазо, вого дискриминатора1 1,Однаю известный цифровой демодутор имеет низкие точность и быстрод ейе. ние точБель изобретения носта а быстродейств С этой целью в ц сигналов с относитеаяефровой демодулят льной фазовой демо задающий генераодхлючен к первому входу блока выделения несущей частоты, и последовательно соединенныеформирователь входного сигнала фазовыйдискриминатор, выделитель тактовой частоты а выходной согласующий блок,5, второй вход которого соединен с выхо; дом фазового дискраминатора, введеныблок формирования строба, . Ъ -траггеРвформирователь импулвсов а ключ, выхюдкотарого поаиаочен к второму входу1 ф блока выделеная несущей частоты, первый и второй.выкоды которого соединеныс входамн З-триггера, выход которогоподключен к первому входу ключа, второйвход которого соединен с вторым выходомформирователя входного сигнала, первыйвыход которого подключен к входу блокаформирования строба, выход которогосоединен с третьим входом ключа, приэтом второй вход блока формирования оР строба соединен с вторым вьпюодом блокавыделения несущей частоты и с входомформирователя импульсов, выход юторогоподключен к второму входу фазового дно- мкриминатора, третий вход которого соединен с первым выходом блока выделениянесущей частоты,Блок формирования строба состоит изпоследовательно соединенных первого Зтриггера, второго Э -триггера, и сумматора по модулю два, второй вход которого соединен с выходом первого Этриггера, причем входы 3 -триггеровявляются входами блока формированиястроба, выходом которого является выход сумматора по модулю два.Кроме того, блок выделения несущейчастоты содержит три счетных триггера,два элемента И и инвертор, вход которого соединен с первым входом первогосчетного триггера и с первым входомпервого элемента И, второй вход которого соединен с вторым входом первогосчетного триггера, выход которого подключен к третьему входу первого элемента И, и с первым входом второгоэлемента И, к второму входу которогоподключен выход инвертора, при этомвыходы элементов И подключены к входамвторого счетного триггера, выход которого соединен с третьим входом второгоэлемента И и с входом третьего счетного триггера, выход которого являетсяпервым выходом блока выделения несузошей частоты, вторым выходом которогоявляется выход второго счетного триггера, а входами блока выделения несущейчастоты являются первый вход второгоэлемента И и первый вход первого счет-,ного триггера.35фазовый дискриминатор содержит двасумматора по модулю два и последова.тельно соединенные элемент И-НЕ исчетный триггер, выход которого подклю 4 Очен к первому входу первого сумматорапо модулю два, выход которого соединен с первым входом второго сумматора по модулю два, выход которого подключен к первому входу элемента И-НЕ, выход которого является выходом фазового45дискриминатора, входами которого являются вторые входы сумматоров по модуслю дваи элемента И-НЕ,На фиг, 1 представлена структурнаяэлектрическая схема предложенного циф 50рового демодулятора; на фиг. 2 - эпюры напряжений, поясняющие его работу,Цифровой. демодулятор сигналов с относительной фазовой модуляцией содержит задающий генератор 1, формирователь 2 импульсов, формирователь 3 вход-ного сигнала, ключ 4, З-триггер 5,вьщелитель 6 тактовой частоты, выход 3 М 5970 4ной согласующий блок 7, блок 8 формирования строба, состоящий из сумматора9 по модулю два, первого и второгоО-триггеров 10 и 11, блок 12 выделения несущей частоты, состоящий изэлемента И 13, инвертора 14, элементаИ 15, первого, второго и третьего счетных триггеров 16-18 соответственно,фазовый дискриминатор 19, состоящийиз двух сумматоров 20 и 21 по модулюдва, элемента И-НЕ 22, счетного тритъгера 23.Цифровой демодулятор работает следующим образом.Модулированное по фазе несущее колебание (фиг. 2 а) поступает на входформирователя 3 входного сигнала, свыхода которого импульсы, соответствующие переходам через нуль несущегоколебания (фиг. 26;6) поступают на ключ4. С дополнительного выхода формирователя 3 входного сигнала на Т)-входпервого Э-триггера 10 блока 8 формирования строба и вход фазового дискриминатора 19 поступают усиленные иограниченные импульсы модулированногопо фазе несущего колебания (фиг. 2 г).Первый и второй;1)-триггеры 10 и11 образуют двухразрядный регистрсдвига, сдвигающий входную информацию (фиг. 2 д,Е). Продвижение регистрасдвига осуществляется положительнымифронтами импульсов, частота которых вдва раза выше несущей частоты(фиг. 2 эк), На выходе сумматора 9 помодул о два формируются отрицательныеимпульсы (фиг, 2 ф) - результат суммирования по модулю два (фиг, 2 д, е)запрещающие поступление на вход ключа4 первого импульса фронта несущего колебания, сформированного после моментамодуляции. С выхода ключа 4 (фиг. 2 и.),.мпульсы отрицательной полярности (управляющие) поступают на вход первогосчетного триггера 16 и запрещают поотупление одного счетного импульса задающего генератора 1 на его вход,Коррекция фазы в блоке 12 выделения несущей частоты осуществляется пофронтам несущего колебания, поступаю.щим с выхода ключа 4, причем сдвиг фазы в сторону отставания на один шаг коррекции осуществляется путем запрета одного импульса высокой частоты 11, поступающего от заданного генератора 1,а сдвиг фазы в сторону опережения- путем запрета одного импульса частотыТ 1 на вхоц 4 первого счетного триггера16 блока выделения несущей часготы5 988 12 добавления одного импульса на входе второго счетного триггера 17 этого блока (на входе второго разряда делителя), Для исключения воэможности ложного захвата синхронизации на вход управления 3 блока 12 выделения несущей частоты подаются из формирователя 3 входного сигнала фронты несущей частоты только одного знака. Например, сформированные при переходе через 0 несущей от положи; М тельного .к отрицательному значению. , Эпвмент И 13 формирует из деленной первым счетнцм триггером 16 частоты Т 1 импульсы длительностью в один положительный импульс частоты Т 1. Элемент И И 15 формирует из входного положительного импульса, соответствующего фронту ,несущей частоты, сигнал "Добавление длительностью в один положительный импульс частоты Т 1, когда фронт несущей 20 совпадает с положительным значением импульсов двойной тактовой частоты Т 1-1. Эти импульсы поступают на второй счетный вход второго счетного триггера 17. Импульсы с выхода третьего счет ного триггера 18 (фиг. 2 л) поступают на О-триггер 5, сдвигающий тактовую частоту Т 1-1 на 90 п (фиг. 2 к). Сдвинутая тактовая последовательность поотупает на ключ 4 и обеспечивает пра- Зо вильное фазирование импульсов на выходе ключа 4 (фиг. 2 и), формирователь 2 импульсов формирует импульсы(фиг. 2 м ), обеспечивающие стробирование входной информации в фазовом дискрими наторе в моменты времени, соответству ющие середине каждой полуволны ограниченного сигнала ОФМ (фиг. 2 ).На фиг. 2 показаны импульсы на выходе сумматора 20 по модулю два, на фиг. 20 импульсы на выходе счетного триггера 23, на фиг. 2 п - импульсы на выходе сумматора 21 по модулю два. С выхода фазового дискриминатора45 . импульсы, соответствующие моменту модуляции, поступают на выделитель 6 тактовой частоты, как управляющие импульсы. Импульсы синхронной тактовой частоты с выхода выделителя 6 тактовой частоты (фиг. 2 с ) поступают на первый вход выходного согласующего блока 7, на другой вход которого поступают импульсы, соответствующие момен там модуляции. Выходной согласующий блок 7 осуществляет преобразование относительной модуляции,и на выход устройства поступает синхронная информация в первичном коде (фиг. 21 ),970 6 Таким образом, технико-экономическая эффект йвность предложенного устройства состоит в повышении точности и быстродействия модуляпии дискретных сигналов, т.е. улучшении качества аппаратуры передачи информации. формула изобретения 1. Бифровой демодулятор сигналов. с относительной фазовой модуляцией, содержащий задающий генератор, выход которого подключен к первому вам блока выделения несущей частоты, и последовательно соединенные формирователь входного сигнала, фазовый дискриминатор, вьщелитель тактовой частоты и выходной согласующий блок, второй вход которого соединен с выходом фазового дискриминатора, о т л и ч а ю щ и йс я тем, что, с целью повышения точности и быстродействия, в него введены блок формирования строба, Э -триггер, фоРмирователь импульсов и ключ, выход которого подключен к второму входу блока выделения несущей частоты, первый и второй выходы которого соединены с входами В-триггера, выход которого подключен к первому входу ключа, второй вход которого соединен с вторым выходом формирователя входного сигнала, первый выход которого подключен к входу блока формирования строба, выход которого соединен с третьим входом ключа, при этом второй вход блока формирования строба соединен с вторым выходом блока ващеления несущей частоты и с входом формирователя импульсов, выход которого подключен к второму входу фазового дискриминатора, третий вход которо-, го соединен с первым выходом блока выделения несущей частоты.2, Демодулятор по п,1, о т л и ч а - ю щ и й с я тем, что блок формирования строба состоит из последовательно соединенных первого 9 -триггера, второго З -триггера и сумматора по модулю два, второй вход которого соединен с выходом первого Ъ григгера, причем входы Э-триггеров являются входами блока формирования строба, выходом которого является выХод сумматора по модулю два. 3 Демодулятор по п.1, о т л и ч аю щ и й с я тем, что блок выделения несущей частоты содержит три счетных триггера, два элемента И и инвертор,7 98 вход которого соединен с первым входом йервого счетного триггера и с первым входом первого элемента И, второй вход которого соединен с вторым входом первого счетногв триггера, выход которого подключен к третьему входу первого элемента И, и с первым входом второго элемента И, к второму входу которого подключен выход инвертора, абри этом выходы элементов И подключены к входам второго счетного триггера, выход которого соединен с третьим входом второго элемента И и с входом третьего счетного триггера, выход которого яи ляется первым выходом блока выделения несущей частоты, вторым Выходом которого является выход второго счетного триггера, а входами-блока выделения несущей частоты являются первый вход второго элемента И и первый вход пер, вого счетного триггера. 8970 84, Демодулятор по п.1, о т л и ч аю ш и й с я тем, что фазовый дискриминатор содержит два сумматора по модулю два и последовательно соединенные элез мент И-НЕ и счетный триггер, выход которого подключен к первому входу первого сумматора по модулю два, выход которого соединен с первым входом вто рого сумматора по модулю два, выход ко.1 О торого подключен к первому входу элемента И-НЕ, выход которого являетсявыходом фазового дискриминатора, входами которого являются вторые входы сумматоров по модулю два и элемента И-НЕ.15 Источники информанш принятые во внимание при экспертизеТираж 688 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж, Раушская на

СмотретьЗаявка

3299580, 11.06.1981

ПРЕДПРИЯТИЕ ПЯ М-5619

ГОРДОН ФЕЛИКС ГЕОРГИЕВИЧ, ВЕРТЛИБ МИХАИЛ ЯКОВЛЕВИЧ, УМНОВА ГАЛИНА АЛЕКСЕЕВНА

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, модуляцией, относительной, сигналов, фазовой, цифровой

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/6-985970-cifrovojj-demodulyator-signalov-s-otnositelnojj-fazovojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов с относительной фазовой модуляцией</a>

Предыдущий патент: Демодулятор частотно-манипулированных сигналов

Следующий патент: Способ формирования высокочастотного тв-сигнала

Случайный патент: 158582