Вычислительное устройство для формирования маршрута сообщения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

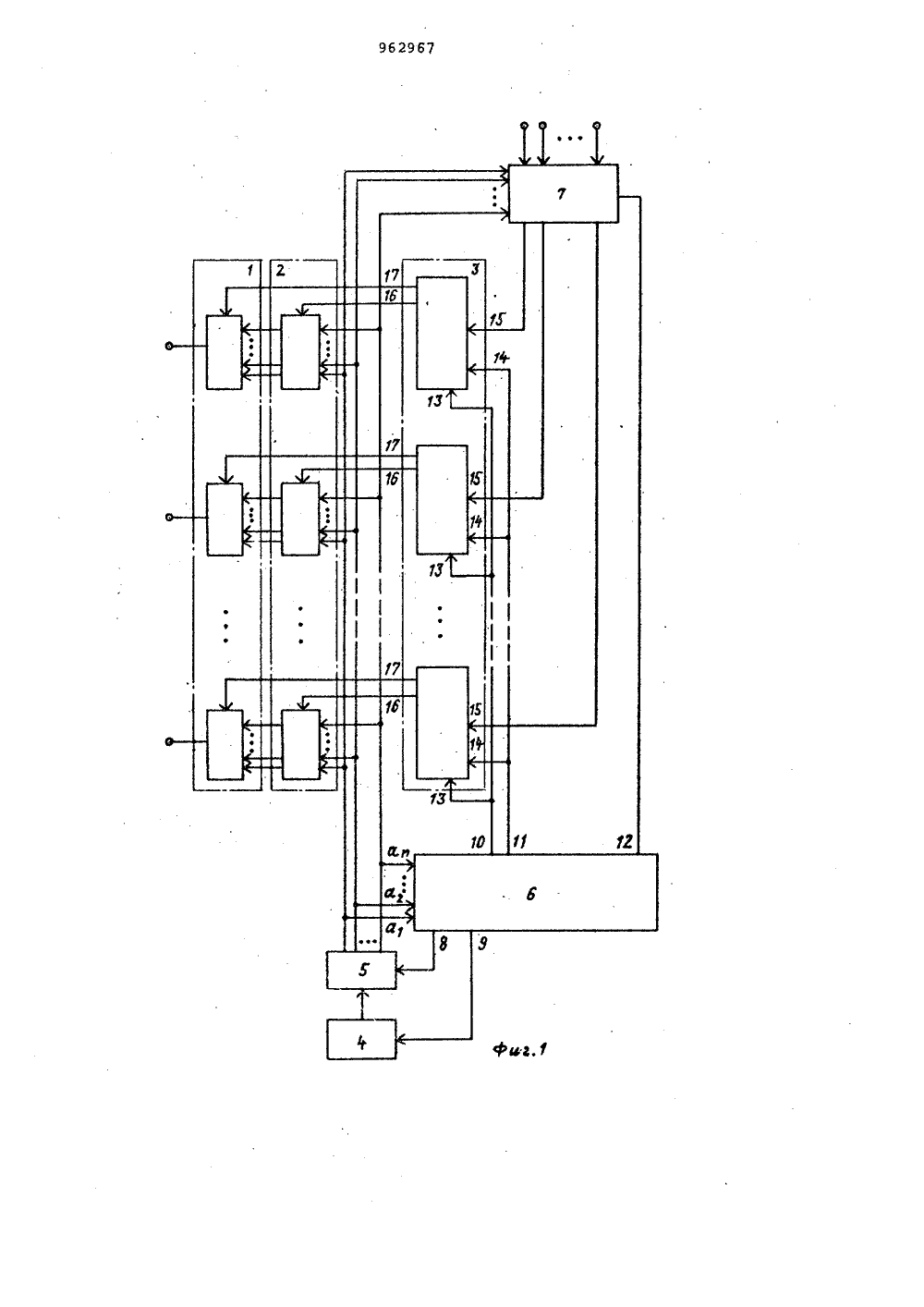

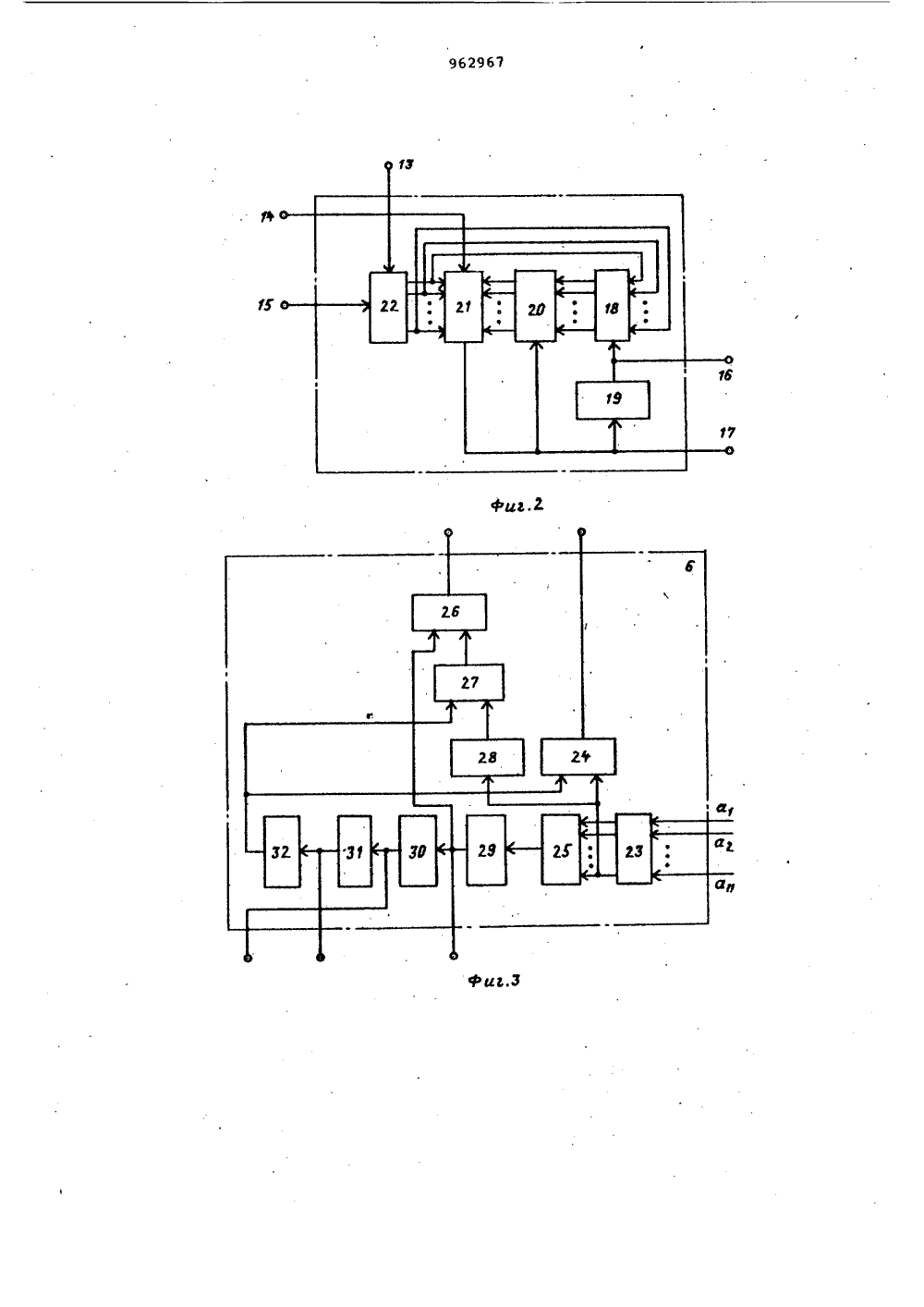

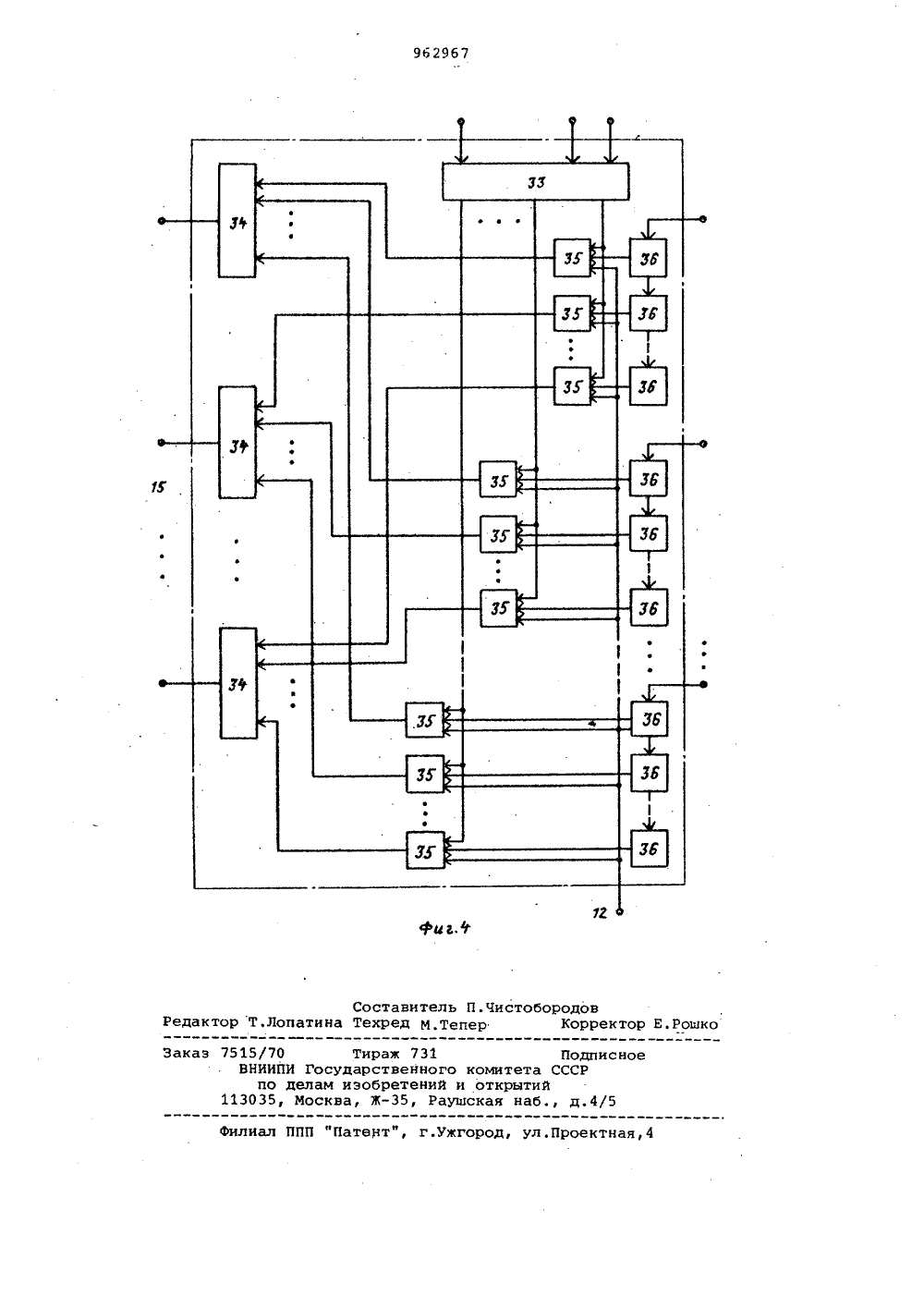

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 22.12.80 (21) 3241464/18-24 11 М. Кл.з 6 06 Р 15/20 с присоединением заявки ссЯ(23) Приоритет -Государственный комитет СССР яо дедам изобретений и открытийОпубликовано 30,0982, Бюллетень М ЗбДата опубликования описания ЗООЯ 82 А.В,Горностай, В.С.Любинский и В.П,Синяви(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ Изобретение относится к сбору и обработке данных, в частности к устройствам коммутации сообщений и пакетов в сетях ЭВМ. 5Известны устройства для Формирования кода маршрута в цифровой сети связи с использованием мини-ЭВМ 111.Недостатками устройств являются высокая стоимость, сложность и сравнительно низкая надежность,Наиболее близким по технической сущности к предлагаемому является устройство, содержащее генератор тактовых импульсов, группу элементов И, группу регистров адресов соседних узлов, счетчик, вход которого соединен с выходом генератора тактовых импульсов, а его выходы - с первыми входами элементов И группы, выходы которых соединены с пряьвми входами регистров группы 2 .Недостатком устройства является низкая эффективность, обусловленная формированием маршрутов с минимальным числом межузловых связей между узлом 25 отправления и узлом назначения, что не исключает больших временных задержек в промежуточных узлах сети .Цель изобретения - .повышение быстродействия работы устройства путем 30 Формирования маршрутов между узламисети по критерию минимума потерь времени на передачу сообщения,Поставленная цель достигается тем,что в вычислительное устройство дляформирования маршрута сообщения, содержащее блок управления, генератортактовых импульсов, счетчик, группуэлементов И, группу регистров адресов соседних узлов, выходы которыхявляются выходом устройства, информационный вход каждого регистра группы подключен к выходу соответствующего элемента И группы, информационные входя всех элементов И группыобъединены и подключены к входу блока управления и вс.1 ходу счетчика,тактовый вход которого соединен свыходом генератора тактовых импуль.сов, первый и второй выходы блокауправления подключены к управляющим входам генератора тактовых им-.пульсов и счетчика соответственновведены группа блоков сравнения икоммутатор, третий вход блока управления подключен к управляющему входу коммутатора, первая группа информационных входов которого являетсягруппой входов устройства, втораягруппа информационных входов комму 962967татора соединена с группой выходовсчетчика, каждый выход группы выходов коммутатора подключен к первому нходу соответствующего блокасравнения группы, второй и третийвходы каждого блока сравнения группы объединены и подключены к четвертому и пятому выходам блокауправления, первый и второй выходыкаждого блока сравнения группы подключены к управляющим входам соответствующих элементов И и регистровадресов соседних узловБлок управления содержит дешиф=ратор, элемент ИЛИ, формировательимпульсов, три элемента задержки, 15два элемента И, элемент НЕ и триггер, выход которого соединенс первым выходом блока, вход сброса триггера соединен с выходом Формирователя импульсов, пятым выходом блока и входом первого элемента задержки, выход которого соединен стретьим выходом блока и входом второго элемента задержки, выход которого соединен с четвертым выходомблока и вхОдом третьего элемента задержки, выход которого подключен кпервым входам первого и второго элементов И, выход второго элемента Иподключен к входу установки триггера, а второй вход - .к выходу элемен- ЗОта НЕ, вход которого соединен с вторым входом первого элемента И и выходом младшего разряда дешифратора,выходы которого подключены к входамэлемента ИЛИ,.выход которого соединен с входом формирователя импульсов,вход дешифратора соединен с входомблока, выход перного элемента И соединен с вторым выходом блока.На .Фиг.1 представлена блок-схема предлагаемого устройства; нафиг.2 - схема блока сравнения; нафиг.3 - схема блока управления; нафиг,4 - структурная схема коммутатора. 45Устройство содержит группу регистров 1 адресов соседних узлов (группа регистров таблицы маршрутов),группу элементов И 2, группу блоков3 сравнения, генератор 4,тактовыхимпульсов, счетчик 5, блок 6 управления, коммутатор 7, входные и выходные шины 8-17.Количество регистров группы регистров 1, элементов И группы 2 иблоков 3 сравнения группы равно количеству узлов назначения в сети дляданного узла. В состан блока сравнения входят группа элементов И 18,элемент 19 задержки, регистры 20 минималных задержек, схемы 21 сравнения и приемный регистр 22. Блок управления содержит дешифратор 23,элемент И 24, элемент ИЛИ 25, триггер26, элемент И 27, элемент НЕ 28, формирователь импульсов 29, элементы 55 30-32 задержки . Коммутатор 7 содержитдешифратор 33, группу элементов ИЛИ34, группу элементов И 35, группубуФерных регистров 36 приема.Устройстно работает следующимобразом.Исходное состояние группы регистров 1 и счетчика 5 - нулевое. Призапуске генератора 4 импульсы поступают на счетчик 5. Если код на счетчике совпадает .с кодом адреса соседнего узла, то генератор отключается и в блоке б управления вырабатывается последовательность управляющих импульсов. Импульсы выполняютследующие функции: первый импульспоявляется на выходе 10 и устанавливдет приемные регистры блоков сравнения в нулевое состояние; второйимпульс (выход 12) поступает в ком.мутатор 7 и разрешает запись информации о задержках для каждого изузлов назначения. Эта информация поступает путем периодического опросаот соседнего узла и хранится н коммутаторе 7, Код адреса очередногососеднего узла находится в счетчике5. По третьему импульсу (выход 11)происходит сравнение принятых задержек с задержками, находящимисяв регистрах минимальных задержекблоков сравнения. В тех блоках сравнения, где задержка меньше, осуществляется ее перезапись в регистр минимальных задержек и вырабатываютсяимпульсы сброса (выход 17), устанавливающие соответствующие регистры1 группы в нулевое состояние, и импульсы записи (выход 16), по которымпроисходит запись кода адреса соседнего узла со,начетчика 5 - в регистры1 блока.После этого вновь запускается генератор, который прекращает генерацию импульсов при совпадении кода насчетчике с кодом адреса очередногососеднего узла. Вырабатываются импульсы управления в блоке б управления, в блоках 3 сравнения группыпроисходит сравнение задержек и всоответствующие регистры 1 группызаписывается код адреса очередногососеднего узла, задержка прохождения информационной посылки:через который для данного узла назначенияменьше. Таким образом, в регистрах 1группы Формируется таблица маршрутов. Цикл продолжается до тех пор,пока не будет опрошен последний соседний узел, после чего счетчик 5 обнуляется.Блок управления работает следующим образом,При наличии на выходе дешифратора кода адреса одного из соседнихузлов на одном из его выходов появляется разрешающий потенциал, которыйчерез элемент ИЛИ 25 поступает наФормирователь импульса 29, на выходе которого появляется импульс, поступающий на вход триггера 26 и переводящий его в нулевое состояние. Этот же импульс, пройдя через элементы 30-32 задержки, поступает на элемент И 27 и,если код на входе дешифратора не является кодом адреса последнего соседнего узла, приводит тоиггер 26 в единичное состояние. В противном случае импульс с элемента 32 задержки через элемент И 24 поступает на выход 8.Блок сравнения работает следующим образом.Исходное состояние регистра 22 единичное. Импульсом сброса (вход 13) регистр 22 устанавливается в нулевое состояние. Запись информации о задержках осуществляется параллельным кодом (входы 15) . По импульсу управления (вход 14) из блока управления происходит сравнение числа А в регистре 22 с числом В в регистре 20. ,Если А с В, то на выходе схемы сравнения 21 появляется импульс, который обнуляет регистр 20 и, пройдя через элемент 19 задержки, разреша- . ет перезапись содержимого регистра .-22 в регистр 20.Коммутатор работает следующим образомПри поступлении на входные шины дешифратора 33 кода адреса соседнего узла на соответствующем выходе дешифратора появляется управляющий сигнал, который поступает на группы элементов И 35 данного соседнего узла.По сигналу управления на шине 12 осуществляется перезапись кодов задержек из группы регистров 36 приема в регистры блоков 3 сравнения через группы элементов И 35 и элементов ИЛИ 34.Устройство позволяет вычислять код маршрута движения сообщения в цифровой сети связи с минимальной задержкой в пути,формула изобретения1. Вычислительное устройство для формирования маршрута сообщения, содержащее блок управления, генератор тактовых импульсов, счетчик, группу элементов И, группу регистров адресов соседних узлов, выходы которых являются выходом устройства, информационный вход каждого регистра группы подключен к выходу соответствующего элемента И. группы, информационные входы всех элементов И группы объединены и подключены к входу блока упранления, выходу счетчика, тактовый вход которого соединен с выходом генератора тактовых импульсон, первый и второй выходы блока управления подключены к управляющим входам генератора тактовых импульсов и счетчика соответственно,о т л и ч а ю щ е е с я тем, что,с целью повышения быстродействия, ннего введены группа блоков сравнения,10 коммутатор, третий нход блока управления подключен к управляющему входукоммутатора, первая группа информационных входов которого являетсягруппой входов устройства, вторая15 группа информационных входов коммутатора соединена с группой выходовсчетчика, каждый выход группы выходовкоммутатора подключен к первому входу соответствующего блока сравнения;щ группы, второй и третий входы каждого блока сравнения группы объединеныи подключены к четвертому и пятомувыходам блока управления, первый ивторой выходы каждого блока сраннения группы подключены к управляющим входам соответствующих элементовИ и регистров адресов соседних узлов.2. Устройство по п.1, о т л ич а ю щ е е с я тем, что, блок упЗ. равления содержит дешифратор, элемент ИЛИ, фбрмирователь импульсов,три элемента задержки, два элемента И, элемент НЕ и триггер, выходкоторогосоединен с первым выходомблока, вход сброса триггера соединенс выходом формирователя импульсов,пятым выходом блока и входом первого элемента задержки, выход которого соединен с третьим выходом блокам входом второго элемента задержки,4 О выход которого соединен с четвертымвыходом блока и входом третьего элемента задержки, выход которого подключен к первым входам первого ивторого элементов И, выход второго45 элемента И подключен к входу установки триггера, а второй вход - квыходу элемента НЕ, вход которогосоединен с вторым входом первогоэлемента И и выходом младшего раз 5 О ряда дешифратора,1 ныходы которогоподключены к входам элемента ИЛИ,выход которого соединен с входомформирователя импульсов, вход дешифратора соединен с входом блока,55 выход первого элемента И соединен свторым выходом блока.Источники информации,принятые во внимание при экспертизе1Клейнрок Л. Вычислительные системы с очередями. М., "Мир", 1979,с.470-473.2, Авторское свидетельство СССРР 547770, кл.б 06 Р 15/20, 1977962967 истобородовКорректор Составитель ПРедактор Т.Лопатина Техред М.Тепе ошко исно ПП "Патеит", г.ужгород, ул.Проектна ил аказ 7515/70 Тивниипи Государпо делам иэо113035, Москва,ж 731 П венного комитета СС етений и открытий 35, Раушская наб.,

СмотретьЗаявка

3241464, 22.12.1980

РИЖСКОЕ ВЫСШЕЕ ВОЕННО-ПОЛИТИЧЕСКОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА БИРЮЗОВА С. С

ГОРНОСТАЙ АЛЕКСАНДР ВЛАДИМИРОВИЧ, ЛЮБИНСКИЙ ВЛАДИМИР СТЕПАНОВИЧ, СИНЯВИН ВЛАДИМИР ПАВЛОВИЧ

МПК / Метки

МПК: G06F 15/173

Метки: вычислительное, маршрута, сообщения, формирования

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/6-962967-vychislitelnoe-ustrojjstvo-dlya-formirovaniya-marshruta-soobshheniya.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительное устройство для формирования маршрута сообщения</a>

Предыдущий патент: Устройство для масштабирования марок времени при обработке сейсмической информации

Следующий патент: Устройство для определения критического пути в графе

Случайный патент: Способ выращивания свиней