Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 955061

Авторы: Тимонькин, Ткаченко, Тытарь, Харченко, Шандуренко

Текст

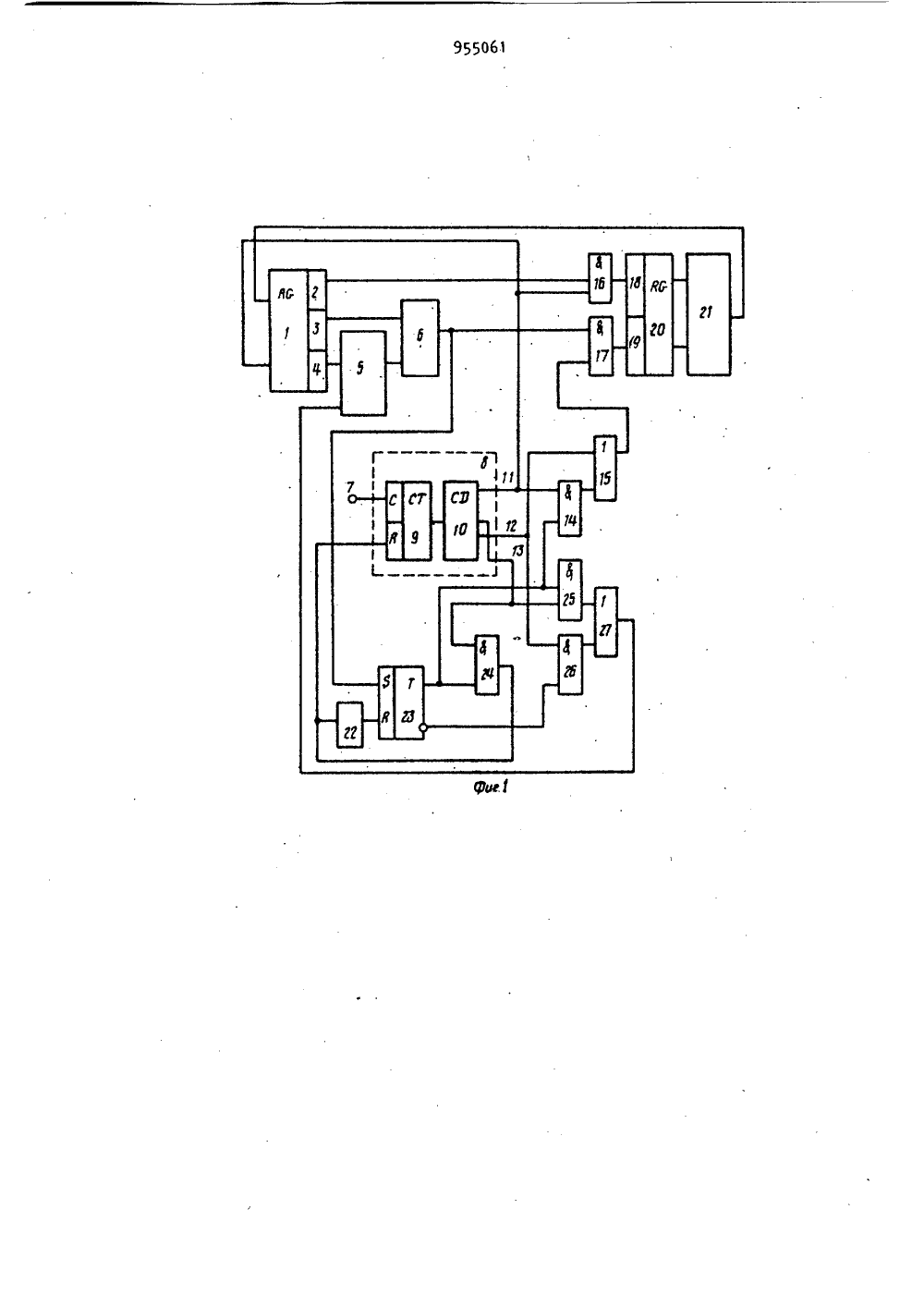

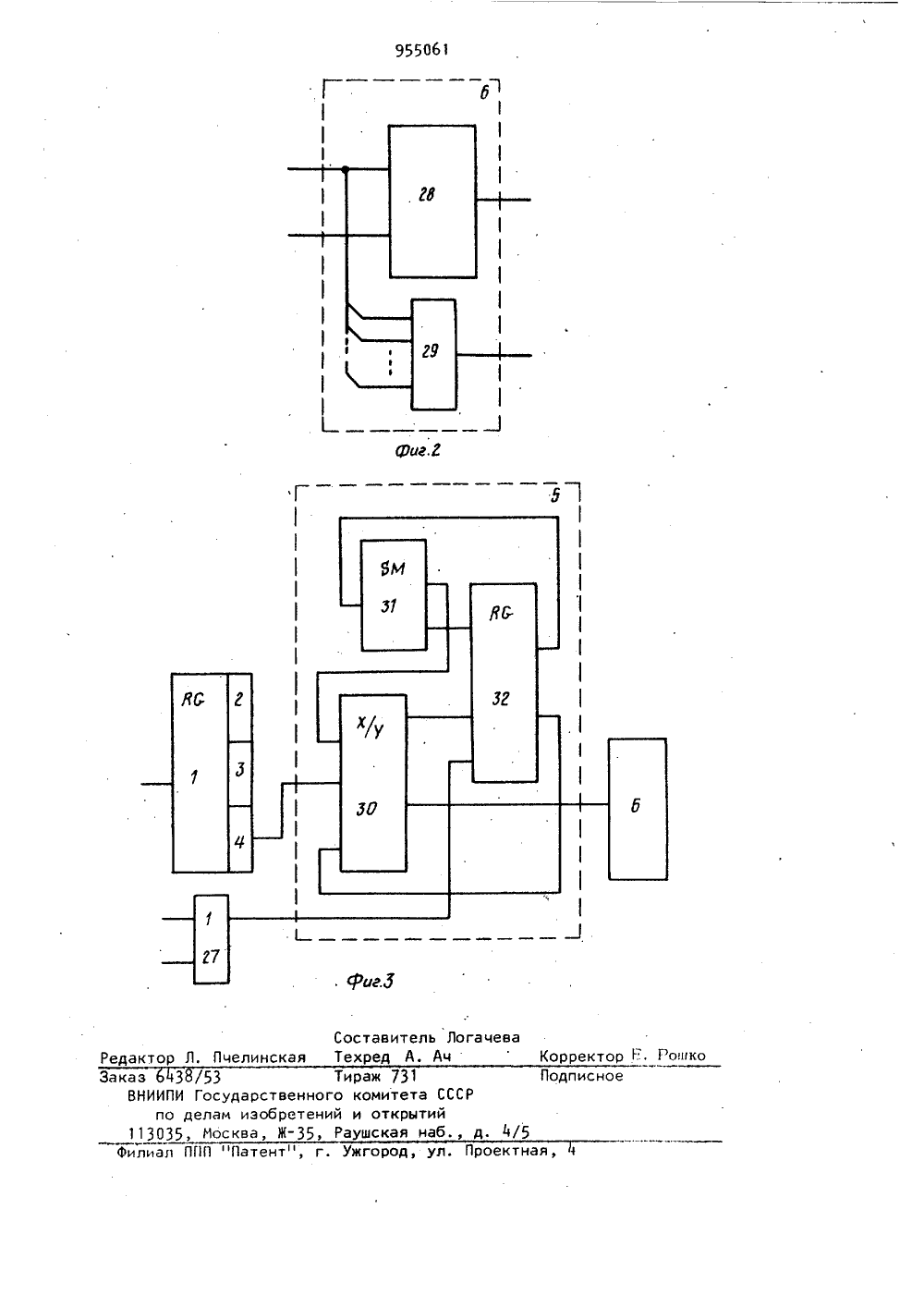

ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 955061 Союз Советски кСоциалистичесиикРеспубликоо делам иэаоретеккк и открытий(71) Заяви 5 Й) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано при построении микропрограм,мных процессоров,Известен микропрограммный процессор, содержащий блок управления, опе.рационный блок, регистры адреса имикрокоманд, дешифратор ветвлений,элемент И и постоянную память 11.Однако данному устройству присущенизкое быстродействие из-за длительной реализации формирования адресовмикрокоманд ветвлений.Наиболее близким к предлагаемомупо технической сущности и достигаемому эффекту является устройство, содержащее регистры адреса и микрокоманд, два элемента И, операционныйблок, блок ветвления, постоянную. память и блок управления, первый выход которого подключен к первомувходу первого элемента И, второйвход которого соединен с первым вы,ходом регистра микрокоманд, а выход - с первым входом регистра адреса, второй вход которого через второй элемент И подключен к первому выходу блока ветвлений, первый и второй выходы регистра адреса соединены соответственно с первым и вторым входами постоянной памяти, выход которой подключен к первому входурегистра микрокоманд, второй выход которого через операционный блок подключен ко второму входу блока ветвлений 21.Недостатком указанного устройства является низкое быстродействие обусловленное тем, что рабочий такт устройства (время между считыванием двух последовательных микрокоманд) одинаково как при реализации линейных последовательностей микрокоманд, так и микрокоманд ветвления, и подразделяется на три синхроимпульса, циклически выдаваемых блоком управления устройства. Однако реализация линейных микрокоманд может осуще 3 9550ствляться в течение более короткоготакта, поскольку в этом случае нетребуется проверка значений сигналов логических условий, поступающихс выхода операционного блока, атакже формйрование на их основе адреса очередной микрокоманды, как вслучае реализации микрокоманд ветвления. Таким образом, отсутствиев данном устройстве элементов и 1 Осредств управления рабочим тактомприводит к существенному снижениюобщего быстродействия устройства.Цель изобретения - повышениебыстродействия микропрограммногоустройства управления,Поставленная цель достигаетсятем, что микропрограммное устройство управления, содержащее регистры адреса и микрокоманд, два элемента И, блок ветвлений, блок па-.мяти, последовательно соединенныесчетчик и шифратор, причем счетныйвход счетчика соединен со входом тактовых импульсов устройства,.первыйвыход шифратора подключен к первомувходу первого элемента И, второй входкоторого соединен с первым выходомрегистра микрокоманд, а выход первого элемента И подклюцен к первомувходу регистра адреса, второй входкоторого через второй элемент И. подключен к первому выходу блока ветвле.ний, первый и второй выходы регистраадреса соединены соответственно с пер.вым и вторым адресными входами блока33памяти, выход которого подключен кинформационному входу регистра микрокоманд, второй вход которого подключен к первому входу блока ветвлений,4 Оуправляющий вход которого подключенк входу устройства, третий выходрегистра микрокоманд является информационным выходом устройства, дополнительно содержит четыре элемента И,два элемента ИЛИ, элемент задержки45и триггер задания режима, единичныйвход которого соединен со вторым выходом блока ветвлений, нулевой вход . -через элемент задержки со входомсброса счетчика и выходом третьегоэлемента Ипервый вход которого подключен к единичному выходу триггеразадания режима и первым входом четвертого и пятого элемента И, выходчетвертого элемента И через первыйэлемент ИЛИ подключен ко второмувходу второго элемента И, второй входпервого элемента ИЛИ соединен со вто 61 4 Рым выходом шифратора и первым входом шестого элемента И, второй вход которого подключен к нулевому выходу . триггера задания режима, выход шестого элемента И соединен с первым входом второго элемента ИЛИ, ко второму входу которого подключен выход пятого элемента И, выход второго элемента ИЛИ подключен к управляющему выходу устройства, третий выход шифратора соединен со вторыми входамитретьего и пятого элементов И, первыйвыход шифратора подключен ко второмувходу четвертого элемента И и управляющему входу регистра микрокоманд.Блок ветвлений содержит элемент Ии шифратор, выход которого подключенк первому выходу блока, информационный вход шифратора является первымвходом блока и подключен ко входамэлемента И, выход которого подключен ко второму выходу блока, управляющий вход шифратора подключен ковторому входу блока.Управление рабочим тактом ведут в.зависимости от типа микрокоманды:микрокоманды линейной последовательности реализуются за два (короткийрабочий такт), а микрокомандыветвления - за три (длинный рабочий такт) тактовых импульса.Введение триггера задания режимапозволяет задавать в каждом рабочемтакте информацию о его длительности:короткий или длинный такт.На фиг. 1 приведена функциональная схема предлагаемого устройствауправления; на фиг. 2 - функциональная схема блока ветвлений; на фиг,3 функциональная схема операционногоблока,Устройство содержит регистр 1 микрокоманд с полем 2 адреса, полем 3ветвления и полем 4 операций, операционный блок 5, блок 6 ветвлений,вход 7 тактовых импульсов, блок 8 управления, содержащий счетчик 9, шифратор:10, первый 11, третий 12 и второй 13 выходы блока 8, элемент И 14,элемент ИЛИ 15, элементы И 16 и 17вход 18 (старшие разряды) и вход 19(младшие разряды) регистра 20 адреса,блок 21 памяти, элемент 22 задержки,триггер 23, элементы И 24-26 и элемент ИЛИ 27.Блок 6 ветвлений (фиг. 2) содержитшифратор 28, предназначенный днявыработки наполнительного адреса очередной микрокоманды (адреса схемы61 Далее работа устройства повторяется аналогично описанному выше.Таким образом, введение указанных новых элементов и связей позволяет существенно повысить общее быстродействие устройства, которое для мик" ропрограммы, состоящей из микрокоманд (0,2 из которых являются микрокомандами ветвления), с учетом того, что микрокоманды ветвления реализуются за время,3 йо, а линейные - за 2 й, определяется выражениемТ = 2. 2 оИПовышение быстродействия, достигаемое в предлагаемом устройстве, составляет Мой2;2,МИспользование предлагаемого устройства в ЭВН позволит повысить их 5 9550 большой интеграции в памяти 21) на основании информации, содержащейся; в младших разрядах адреса очередной микрокоманды (поле 3 регистра 1) и сигналов логических условий (признаков результата), поступающих с выхода операционного блока 5, и элемент И 29 предназначенный для формирования признака выполнения микро- команды. Операционный блок 5 (фиг,3) 1 О содержит преобразователь 30 кодов, сумматор 31 и блок 32 регистров. На фиг. 3 приведена функциональная схема блока 5 и подключение его к связанным с ним регистром 1, с выхода 1 поля М которого на первый вход блокапоступают сигналы микроопераций, элементом ИЛИ 27; выход которого подключен ко второму входу блока 5, и блоком 6 ветвлений, второй вход 2 ф которого соединен с выходом операционного блока.Предлагаемое устройство работает следующим образом.В исходном состоянии в регистре Эз 1 записан адрес очередной микрокоманды, триггер 23 и регистр 20 установлены в нулевое состояние. По импульсу с первого выхода 11 блока управления старшие разряды адреса оче- щ редной микрокоманды через элемент И 16 записываются в поле 18 регистра 20, При этом осуществляется выбор ячейки в схемах большой интеграции блока 21. памяти.Триггер 23 задает режим работы ус. .тройства. В единичном состоянии триг. гера 23 реализуются микрокоманды линейных последовательностей, когда. рабочий такт состоит из двух тактовых импульсов блока 8 управления. Нулевое состояние триггера 23 задает режим реализации микрокоманд ветвлений, выполнение которых сопряжено с проверкой значений сигналов логических условий и модификаций в связи с младшим разрядом адреса очередной микрокоманды. Через .элемент И 17 код младших разрядов адреса микрокоманды с выхода шифратора 28 записывается в поле 19 регистра 20, и осуществляет выбор блока (схемы большой интеграции) в памяти 21, с выхода которой код микрокоманды записывается в регистр 1.По второму импульсу с выхода 13Я блока 8 управления срабатывает элемент И 25, который через элемент ИЛИ 27 производит установку в исход. ное состояние регистров операционно.го блока 5. Кроме того, одновременнооткрывается элемент И 2 М, которыйустанавливает в исходное состояние триггер 23 и блок 8 управления. Устройство переходит к реализации очередного рабочеготакта. Если реализуемая микрокоманда является микро- командой ветвления, то сигнал на вто. ром выходе блока 6 отсутствует и триггер 23 остается в нулевом состоянии. По второму импульсу с выхода 13 блока 8 управления состояние управляющей части схемы не изменяется. Однако за истекающий промежуток времени операционный блок 5 вырабатывает и усТанавливает на втором входе блока 6 условия ветвления, которые модифицируют код младших разрядов адреса очередной микрокоманды. По им пульсу с выхода 12 блока управления через элемент ИЛИ 15 срабатывает элемент И 17, который передает модифицированный код младших разрядов в регистр 20.Кроме того, с выхода поля 1 регистра 1 микрокоманд в операционный блок 5 поступают сигналы микроопера- . ций а с выхода поля 3 регистра 1 код младших разрядов адреса передается в дешифратор .ветвлений. Если реализуемая микрокоманда не предполагает возможности ветвления, то на втором выходе блока 6 появляется сигнал, который устанавливает триггер 23 в единичное состояние.Последний открывает элемент И 14 и и 17.9550 7общую производительность и быстродействие. Формула изобретения 1. Микропрограммное устройствоуправления, содержащее регистры адре са и микрокоманд, два элемента И, блок ветвлений блок памяти, после довательно соединенные счетчик и шифратор, причем счетный вход счетчика соединен со входом тактовых импульсов устройства, первый выход шифратора подключен к первому входу пер вого элемента И, второй вход которого соединен с первым выходом регистра микрокоманд, а выход первого эле- . мента И подключен к первому входу регистра адреса, второй вход которого 20 через второй элемент И подключен к первому выходу блока ветвлений, пер. вый и второй выходы регистра адреса соединены соответственно с первым и вторым адресными входами блока памя- И ти, выход которого подключен к информационному входу регистра микрокоманд, второй выход которого подключен к первому входу блока ветвлений, управляющий вход которого подключен Эр ко входу устройства, третий выход регистра микрокоманд является информационным выходом .устройства, о т л и ч а ю щ е е с я тем, цто, с целью повышения быстродействия, он дополнительно содержит четыре элемента И, два элемента ИЛИ, элемент задержки и триггер задания режима, единичный вход которого соединен с вторым выходом блока ветвлений, нулевой вход -через элемент задержки со входом сброса счетчика и выходом третьего 61 8элемента И, первый вход которого подключен к единичному выходу тригге ра задания режима и первым входам четвертого и пятого элементов И, выход четвертого элемента И через первый элемент ИЛИ подключен ко второму входу второго элемента И, второй вход первого элемента ИЛИ соединен со вторым выходом шифратора и первым входом шестого элемента И, второй вход которого подключен к нулевому выходу триггера задания режима, выход шестого элемента И соединен с первым входом второго элемента ИЛИ, ко второму входу которого подключен выход пятого элемента И, выход второго элемента ИЛИ подключен к управляющему выходу устройства, третий выход шифратора соединен с вторыми входами третьего и пятого элементов И, первый выход шифратора подключен ко второму входу четвертого элемента И и управляющему входу регистра никрокоманд.2. Устройство по и. 1, о т л и -. ч а ю щ е е с я тем, цто блок ветвлений содержит элемент И и :шифратор, выход которого подключен к первому выходу блока, информационный вход шифратора является первым входом блока и подключен ко входам элемента И, выход которого подключен ко второму выходу блока, управляющий вход шифратора подключен ко второму входу блока. Источники информации,принятые во внимание при экспертизе 1. Патент Великобритании У 1398367 кл. 6 4 А, опублик. 1975 2. Авторское свидетельство СССР й 717773, кл. С 06 Г 15/00, 1980.Составитель Логачеведактор Л. Пчелинская Техред А. Ач орректор 1., Рои каз 3 /53 ВНИИПИ Государст по делам иэоб 113035, Москва,Ф ППП Паодписно Тираж 731 Пвенного комитета СССРретений и открытийЖ, Раушская наб., д. ч/5лиал тент, г. Ужгород, ул. Проектная,

СмотретьЗаявка

3239212, 26.01.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТЫТАР ВЛАДИМИР АЛЕКСАНДРОВИЧ, ШАНДУРЕНКО НИКОЛАЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/6-955061-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для формирования адреса команды

Случайный патент: Устройство для подъема грузов со смещенным центром тяжести