Устройство для отображения информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

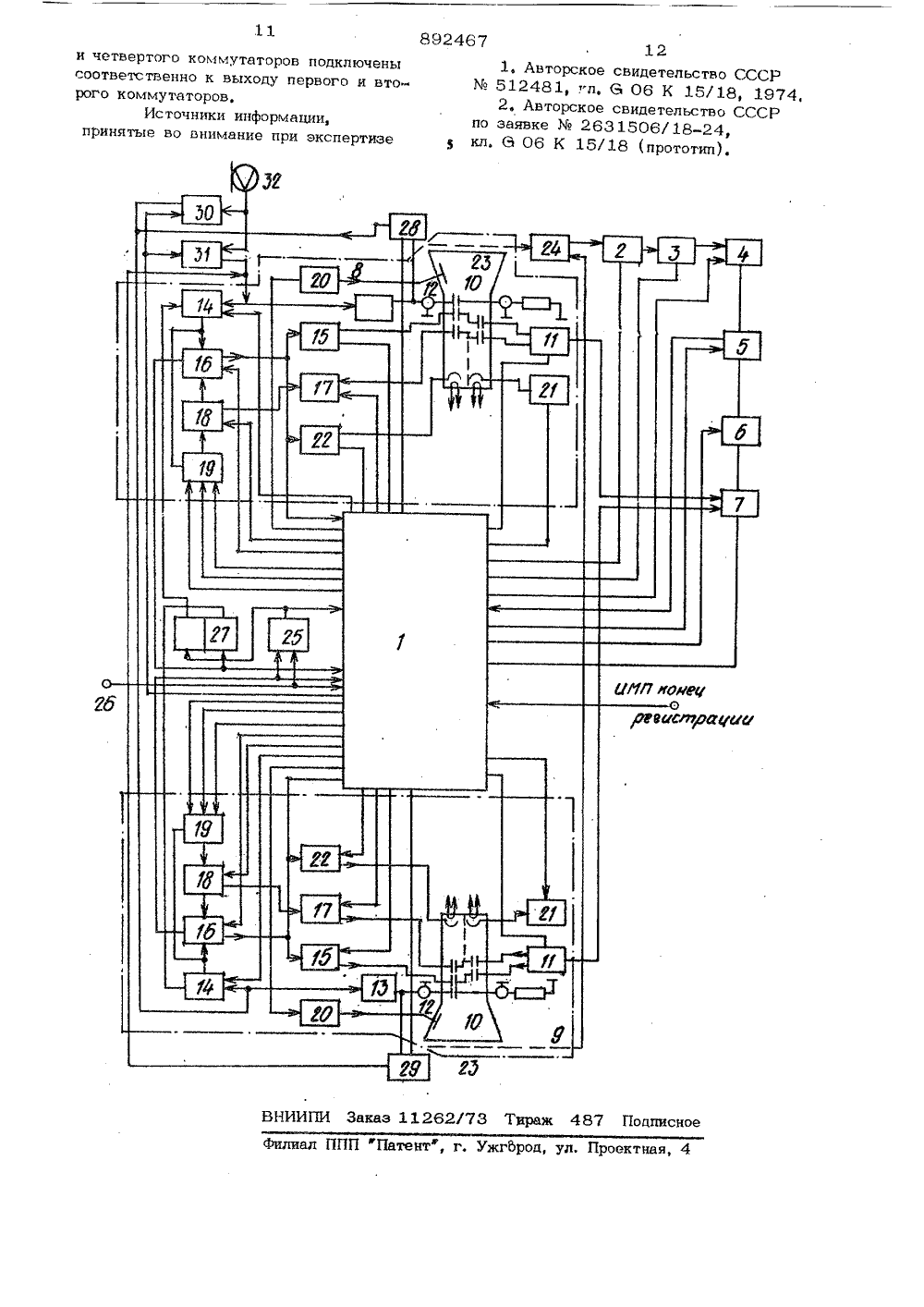

(23) Приоритет твеударстванньй кемнтет СССРОпубликовано 23,12,81, Ьктллетень 47Дата опубликования описания 26,12,81 до делам нзабретений и вткрцтнй(54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ Изобретение относится к устройстьвам анализа и отображения однокрач ных быстропротекающих процессов, при-,меняемых в различных физических экспериментах, связанных с разрушением исследуемой информации и характери 5 зующихся большим объемом регистрируемой информации.Известно устройство для отображения, содержащее электроннолучевую16 трубку, коммутируемый источник, блок задержки, блок развертки записи, блок калибровки, первый блок подсвета, формирователь запускающих импульсов, усилитель, блок развертки: считывания, второй блок подсвета, блок памяти, блок индикации, блок управления, цифровой фазовый дискриманатор, дополнительный блок памяти и блок анализа процесса, причем управляющие входы коммутируе мого источника питания, блока развертки записи, блока калибровки, первого и второго, блоков подсвета соединены с соответствующими выходами блока управления, а выходы - с соответствующимиэлектродами электроннолучевой трубки,управляющий вход формирователя запускающих импултсов соединен с соответствующим выходом блока управления, информационный вход - а шиной входногосигнала и через блок задержки с соот.ветствующим электродом электроннолучевой трубки а выход с запускающимивходами блока развертки записи и первого блока подсвета, входы блока развертки считътвания, усилителя соедйнены с соответствующими электродамиэлектроннолучевой трубки, управляющийи первый информационный входы блокарндикации связаны с выходом блока управления и выходом блока разверткисчитывания соответственно, управляющие входы блока памяти и блока анализа процессов соединены с соответствующими выходами блока управления, информационный вход блока памяти связан свыходом цифроэого фазового дискриминатора, а выход - с информационным892467 входом блока анализа процессов, управляюший и информационный выход которого соединены с соответствующим входом блока управления и первым информационным входом дополнительного блока памяти соответственно, управляющийвход цифрового фазового дискриминаторасвязан с одноименным входом блока развертки считывания и соответствующим выходом блока управления, а информационный вход - с выходом усилителя и вторым информационным входом дополнительного блока памяти, выход которого соединен со вторым информационным входом блока индикации 21 .Однако известное усторйство не позволяет регистрировать большое число однократных сигналов со случайным распределением амплитуд эа один цикл подготовки мишени электроннолучевой трубки,Известно также устройство, содержащее три блока памяти, первый из которых соединен с шинами входного сигнала, блоком управления, индикатором и фазовым дискриминатором, связанным с блоком управления и вторым блоком памяти, который соединен с блоком анализа, подключенным к блоку утравления и третьему блоку памяти, который связан с блоком управления и индикатором, схему сравнения, буферный регистр, сумматор, преобразователь код напряжение и аналого-цифровой преобразователь, соединенные с блоком управления, а аналого-цифровой преобразователь соединен с шинами входного сигнала, первым блоком памяти, сумматором, подключенным к буферному регистру, и схемой сравнения, котораа подключена к буферному регистру, свя звнному через преобразователь код-напряжение с первым блоком памяти 2 Недостатком является то, что устройство не позволяет регистрировать большое количество последовательно следуюших импульсов, так квк регистрация ведется до тех пор, пока амплитуда очередного сигнала не превысит размер свободного участка экрана, после чего устройство переходит на считывание, в следовательно, неизбежна потеря информации,Бель изобретения - повышение достоверности отображения информации.Поставленная цель достигается тем, что в устройство для отображения информации, содержащее последовательно соединенные блок управления, усилитель Ю 15 20 23 30 33 40 43 30 ,33 4считывания, фазовый дискриминатор, первый блок памяти, блок анализа, второй блок памяти и блок индикации, подключенный к блоку управления, связанному с фаэовым дискриминатором, первым блоком памяти, блоком анализа и вторым блоком памяти, и блоки буферной памяти, каждый из которых содержит звпоминвюшую электронолучевую трубку (ЗЭЛТ), узел развертки считывания ЗЭЛТ, подключенный к блоку индикации, отклоняющая система ЗЭЛТ присоединена через элемент задержки к аналогоцифровому преобразователю, узел развертки записи ЗЭЛТ, подключенный к первому выходу элемента сравнения, первый вход которого связан с аналого-цифровым преобразователем, цифроаналоговый преобразователь, связанный с регистром, подключенным ко второму входу элемента сравнения и к сумматору, который подключен к аналого-цифровому преобразователю, подключенному к блоку управления, соединенному с сумматором, регистром, аналого-цифровым преобразователем, третьим входом элемента сравнения, источником питания, узлом развертки записи ЗЭЛТ, цифроаналоговым преобразователем, узлом подсвета записи, узлом развертки считывания и узлом подсвета считывания, введены элементы ИЛИ, триггер и коммутаторы, причем входы первого элемента ИЛИ подключены к коллекторам считывания ЗЭЛТ, а его выход - к усилителю считывания, входы второго элемента ИЛИ соединены со вторым выходом элемента сравнения второго блока буферной памяти и с шинами импульса считывания, а его выход соединен с первым входом триггера и блоком управления, второй вход триггера подключен ко.второму выходу элемента сравнения первого блока буферной памяти, выходы триггера подключены ко входам аналогоцифровых преобразователей, входы первого коммутатора подключены к выходу элемента задержки первого блока буферной памяти и к блоку управления, его выход - ко входу аналого-цифрового преобразователя и к входу элемента задержки второго блока буферной памяти, входы второго коммутатора подключены к выходу элементов задержки второго блока буферной памяти и блоку управления, а его выход - ко входу аналогоцифрового преобразователя и к входу элемента задержки первого блока буферной памяти, первые входы третьегои ч:твертог к,ммутаторо ншключеш 1 ко входу устройства, в "орые входыих- к блоку управления, а выходы третьего и четвертого коммутаторов подключены соответственно к выходу первогои второго коммутаторов,Ведение новых узлов и связей позволяет исключить потери информации засчет переключения сигнального входана свободный блок буферной памяти.На чертеже изображено устрЯстводля отображения информации.Устройство содержит блок 1 управления, усилитель 2 считывания, фазовый дискриминатор 3, первый блок 4памяти, блок 5 анализа, второй блок 6памяти, блок 7 индикации, первый 8и второй 9 блоки буферной памяти, запоминающую электроннолучевую трубку 10, узел 11 развертки считывания,отклоняющую систему 12, элемент 13задержки, аналого-цифровой преобразователь 14, узел 15 развертки записи,элемент 16 сравнения, цифроаналоговыйпреобразователь 17, регистр 18, сумматор 19, источник 20 питания узел21 подсвета считывания, узел 22 подсветя записи, коллектор 23 считывания,первый элемент ИЛИ 24, второй элемент ИЛИ 25, шины 26 импульса считывания триггер 27, первый 28, второй 29, третий 30 и четвертый 31коммутаторы, вход 32. Устройство для отображений информации работает следующим орбазом.Перед регистрацией исследуемых процессов производится подготовка экранов ЗЭЛТ 10 первого 8 и второго 9 блоков буферной памяти. При этом источники питания обоих блоков буферной памяти переводятся в положение, соответствующее режиму подготовки и с помощью узлов развертки 11 и подсвета 21 считывания на экранах ЗЭЛТ высвечиваются прямоугольные растры типа телевизионного. Затем блок 1 управления переводит источники питания в ре-. жим записи, производит запись исходного кода в сумматор 19 и регистр 18 первого 8 и второго 9 блоков буферной памяти. Этот код, преобразованный цифроаналоговым преобразователем 1:/ первого 8 и второго 9 блоков буферной памяти, дает начальный уровень луча записи на мишенях ЗЭЛТ 10.Импульс начала регистрации, поступающий на вход блока 1 управдения и второй элемент ИЛИ 25, устанавливает в единичное состояние триггер 27, устанавливая потенциал разрешения на аналого-цифровом преобразователе 14 первого блока,8 буферной памяти. Первый 28 и четвертый 31 коммутаторы замкнуты, а второй 29 и третий 30 разомкнуты. Первый исследуемый сигнал, приходящий на вход устройства, поступает на входы элемента 13 задержки и аналого-цифрового преобразователи 14 первого блока беферной памяти производящего преобразование амплитуды сигнала в цифровой код, которыйпоступает на элемент 16 сравнения,ф первого блока буферной памяти, где производится его сравнение с кодом, записанным в регистре 18. Если окажется,что код, поступивший с аналого-цифрового преобразователя 14,меньше, либо39 равен коду, поступающему с регистра 18то элемент 16 сравнения формируесигнал запуска, который поступает назапускающие входы узлов развертки 15и подсвета 22 записи первого блока 82 З буферной памяти, а также один из входов блока 1 управления, При этом наэкране ЗЭЛТ 10 записывается исследуемый сигнал, который поступает черезэлемент 13 задержки ко времени сра 36 батывания узлов 15 и 22. Одновременно с процессом сравнения кодов на элементе 16 сравнения в сумматор 19 первого блока 8 буферной памяти подаетсяцифровой код с аналого-цифрового преоб- .зу разователя 14, где производится вычитание поступившего кода иэ кода начального уровня луча записи, Полученный в результате код записывается в регистр 18для сравнения с кодом амплитуды после 40 дующего исследуемого сигнала,Блок 1 управления по сигналу, поступившему с элемента 16 сравнения, формирует сигнал на управление цифроаналоговым преобразователем 17 первого бло4 В ка 8 буферной памяти, на смещение луча записи, с задержкой на время записи в новое положение на мишени ЗЭЛТ,соответсвуюшее коду, записанному врегистре 18 и одновременную подготовку устройства к регистрации следующегопроцесса,Регистрация поступающих исследуемых сигналов производи;гся аналогичным образом с последующим переводом луча в новую зону мишени, Если код, поступающий с аналого-цифрового преобразователя 14, больше кода, записанного в регистре 18, поступивший сиг8924 7нал не запишется в оставшейся рабочей площади мишени ЗЭЛТ. В этом случае элемент 16 сравнения вырабатывает сигнал, который поступает на блок 1управления, на нулевой вход триггера В27, переводя его в нулевое состояниеи разрешая регистрацию, незаписанного и блок 8 буферной памяти сигналав блок 9 буферной памяти. При этом сигнал через первый коммутатор 28 посту16пает на вход аналого-цифрового преобразователя 14 второго блока 9 буферной памяти и производится его регистрация аналогично описанному.Одновременно блок 1 управления 5размыкает коммутаторы 28 и 31 и замыкает 29 и 30, переводит в режимсчитывания блок 8 буферной памяти,подготавливает к записи первый блок 4памяти, запускает узлы развертки и подсвета считывания первого блока 8 буферной памяти, При этом на коллекторе 23 считывания первого блока 8 буферной памяти появляются считанныеи преобразованные сигналы в виде им- дпульсов малой амплитуды, фаза которых,несет в себе информацию об амплитудах дискретиык выборов зарегистрированных иа экранах ЗЭЛТ сигналов в первом блоке 8 буферной памяти, Эти им-пульсы поступают на вход усилтиеля 2через первый элемент ИЛИ 2, с выхода которого сформированные сигналыпоступают на информационный вход цифрового фазового дискриминатора 3, навторой вход которого поступают импуль33сы опорного сигнала с блока 1 управ-ления,1 Опорные импульсы задают началоотсчета фазового сдвига информацион фных импульсов методом последовательного счета и выдают на информационный вход первого блока 4 памяти парадлельный двоичный код, характеризующий каждую дискретную выборку амплитуд, ффзарегистрированных сигналов.После окончания процесса считывания блок 8 буферной памяти переводится в режим подготовки, а затем в. режим записи и находится в ждущем ре- Эжиме, В это время происходит регистрация исследуемых процессов во второйблок 9 буферной памяти до момента,когда код с аналого-шюфрового преобразователя 14 второго блока 9 буферМной памяти окажется больше кода, записанного в регистре 18 второго блока 9 буферной памяти, это означает,67 8что поступивший сигнал не запишетсяв оставшейся рабочей площади мишениЗЭЛТ.В этом случае элемент 16 сравнения второго блока 9 буферной памятивырабатывает сигнал, который поступает в блок 1 управления и через второй элемент ИЛИ 25 на единичныйвход триггера 27, устанавливая егов состояние, при котором разрешаетсяпрохождение регистрируемого сигналас выхода коммутатора 29 на вход ана. лого-цифрового преобразователя 14 первого буферного блока памяти, размыкаются коммутаторы 29 и 30 и замыкаются 28 и 31, При этом блок 9 бу.ферной памяти переводится в режимсчитывания, аналогичный считываниюинформашя иэ первого блока 8 буферной памяти, Информация, считаннаяиз блока 9 буферной памяти, записываетсяв первый блок 4 памяти. В это время происходит регистрация исследуемых процессов в первый блок 8 буферной памяти,Таким образом, регистрация исследуемых процессов происходит то в первый блок 8 буферной памяти, то во второй блок 9 без перерывов на время считывания, что исключает возможные потери при применении одного блока памяти, использующего метод масштабновременного преобразования,циклический процесс записи сигналов на экране ЭЗЛТ первого и второго блоков буферной памяти и считывания с них информации в блок 4 памяти заканчивается по сигналу "Конец регистрацииф, поступающему, на блок 1 управления, формируемому по сигналам внешней синхронизации (можно вручную), по командам оператора. При этом в первом блоке 4 памяти накапливается информация в виде ряда двоичных чисел являющихся цифровыми эквивалентамн дискретных выборок всех зарегистрированных однократных сигналов исследуемого потока. По окончании процесса регистрации система переводится в режим анализа и воспроизведения, Для этого блок управления переводит блок 4 памяти в режим считывания. Считываемая информация вместе с сигналами синхронизации с блока 1 управления поступает на вход блока 5 анализа, который осуществляет последовательный съем информации, ее преобразование, проведение анализа и формирование информации об ординатах амплитудного распределения по802467 тока однократных быстропротекающих процессовв.Процесс индикации зарегистрированной информации предусматривает работуустройства в двух режимах. р.".жим индикации любого из зарегистрированныходнократных процессов и режим индикаш 1 и амплитудного распределения потокаоднократных быстропротекаюших процессов.В режиме отображения (индикации)формы процессов по программе, задаваемой блоком 1 управления, блок 5 анализа осуществляет выбор информации любого из зарегистрированных однократных быстропротекающих процессов, изблока 4 памяти преобразование и записьво второй блок 6 памяти. По окончаниизаписи в блок 6 памяти по команде сблока 1 управления он переводится в режим воспроизведения, В режиме отображения индикации) амплитудного распределения информация, поступающая из блока 5 анализа, аналогичным образом записывается в блок 6 памяти и в режимевоспроизведения индуцируется на экране блока 7 индикации, При воспроизведении на экране блока 7 индикации появляется изображение формы амплитудного распределения исследуемого потокаоднократных быстропротекаюших процессов (или формы любого из зарегистрированных однократных процессов),Таким образом, предлагаемая систе-ма позволяет исключить потери информации за счет дополнительного блока памяти, использующего метод масштабно-временного преобразования, и перекрытьобразующуюся мертвую зону в интервале считывания информации с мишениЗЭЛТ одного из блоков буферной памятина ЗЭЛТ другого,ф ормула изобретения Устройство для отображения информации, содержащее последовательно соединенные блок управления, усилитель считывания, фазовый дискриминатор, первый блок памяти, блок анализа, второй блок памяти и блок индикации, подключенный к блоку управления, связанному с фазовым дискриминатором, первым блоком памяти, блоком анализа и вторым блоком памяти, и блоки буферной памяти, каждый из которых содержит запоминающую электроннолучевую трубку, узел развертки считывания запоми 1 Онающей электроннолучевой трубки, подключенный к блоку индикации, отклоняющая система запоминающей электроннолучевой трубки присоединена через элемент задержки к аналого-цифровому преобразованию, узел развертки записи запоминающей электроннолучевой трубки, подключенный к первому выходу элемента сравнения, первый вход которого связан с аналого-цифровым преобразователем, цифроаналоговый преобразователь, связанный с регистром, подключенным ко второму входу элемента сравнения и к сумматору, который подключен к аналого-цифровому преобразователю,подключенному к блоку управления,соединенному с сумматором, регистром,аналого-цифровым преобразователем,третьим входом элемента сравнения, источником питания, узлом развертки записи запоминающей электроннолучевой трубки, цифроаналоговым преобразователем,узлом подсвета записи, узлом развертки считывания и узлом подсвета считывания, о т л и ч а ю щ е е с я тем,что, с целью повышения достоверностиотображения информации, в него введены элементы ИЛИ, триггер и коммутаторы, причем входы первого элементаИЛИ подключенык коллекторам считывания запоминающей электроннолучевойтрубки, а его выход- к усилителю считывания, входы второго элемента ИЛИсоединены со вторьм выходом элемента сравнения второго блока буфернойпамяти и с шинами импульса считывания, а его выход соединен с первымвходом триггера с блоком управления,второй вход триггера подключен ко второму выходу элемента сравнения перцого блока буферной памяти, выходы триггера подключены ко входам аналого-цифровых преобразователей, входы первогокоммутатора подключены к выходу элемента задержки первого блока буферной памяти и к блоку управления, еговыход. - ко входу аналого-цифровогопреобразователя и к входу элементазадержки второго блока буферной памяти,входы второго коммутатора подключены к выходу элементов задержки второго блока буферной памяти и блоку управления, а его выход - ко входу аналого-цифрового преобразователя и к входу элемента задержки первого блока буферной памяти, первые входы третьего и четвертого коммутатороа подключены Ко входу устройства, вторые входы ихблоку управления, а выходы третьегои четвертого коммутаторов подключены соответственно к выходу первого и второго коммутаторов.Источники информации,принятые во внимание при экспертизе892467 121, Авторское свидетельство СССР512481, ."л. Ь 06 К 15/18, 1974,2. Авторское свидетельство СССРпо заявке2631506/18-24,кл, Я 06 К 15/18 (прототип).

СмотретьЗаявка

2818629, 17.09.1979

ПРЕДПРИЯТИЕ ПЯ Р-6324

БУРДАЕВ БОРИС ЯКОВЛЕВИЧ, ШАНИН АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G09G 1/26

Метки: информации, отображения

Опубликовано: 23.12.1981

Код ссылки

<a href="https://patents.su/6-892467-ustrojjstvo-dlya-otobrazheniya-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для отображения информации</a>

Предыдущий патент: Устройство для отображения информации на экране электронно лучевой трубки

Следующий патент: Способ магнитной записи и воспроизведения цифровой информации

Случайный патент: Сейсмостойкое здание