Программатор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

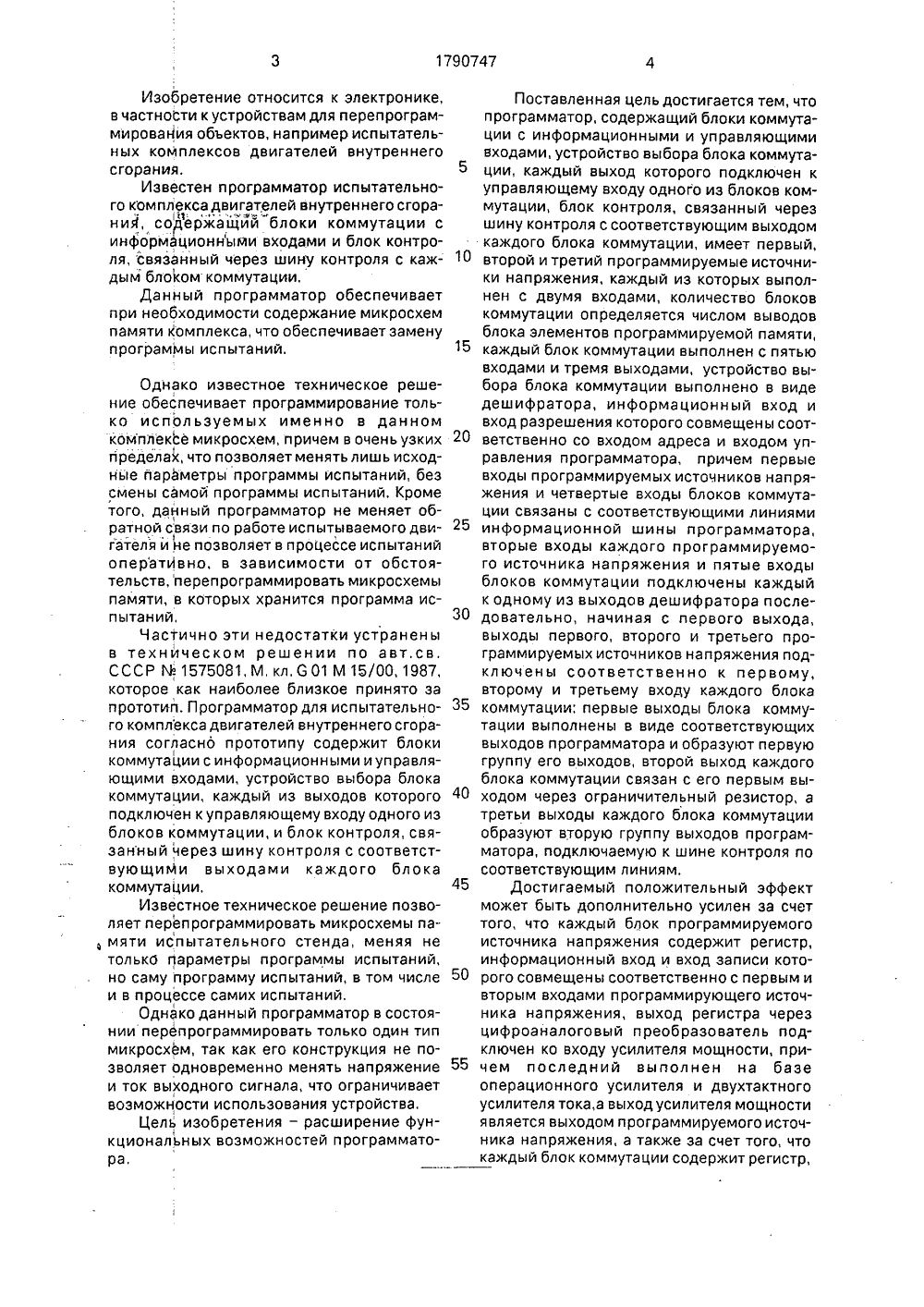

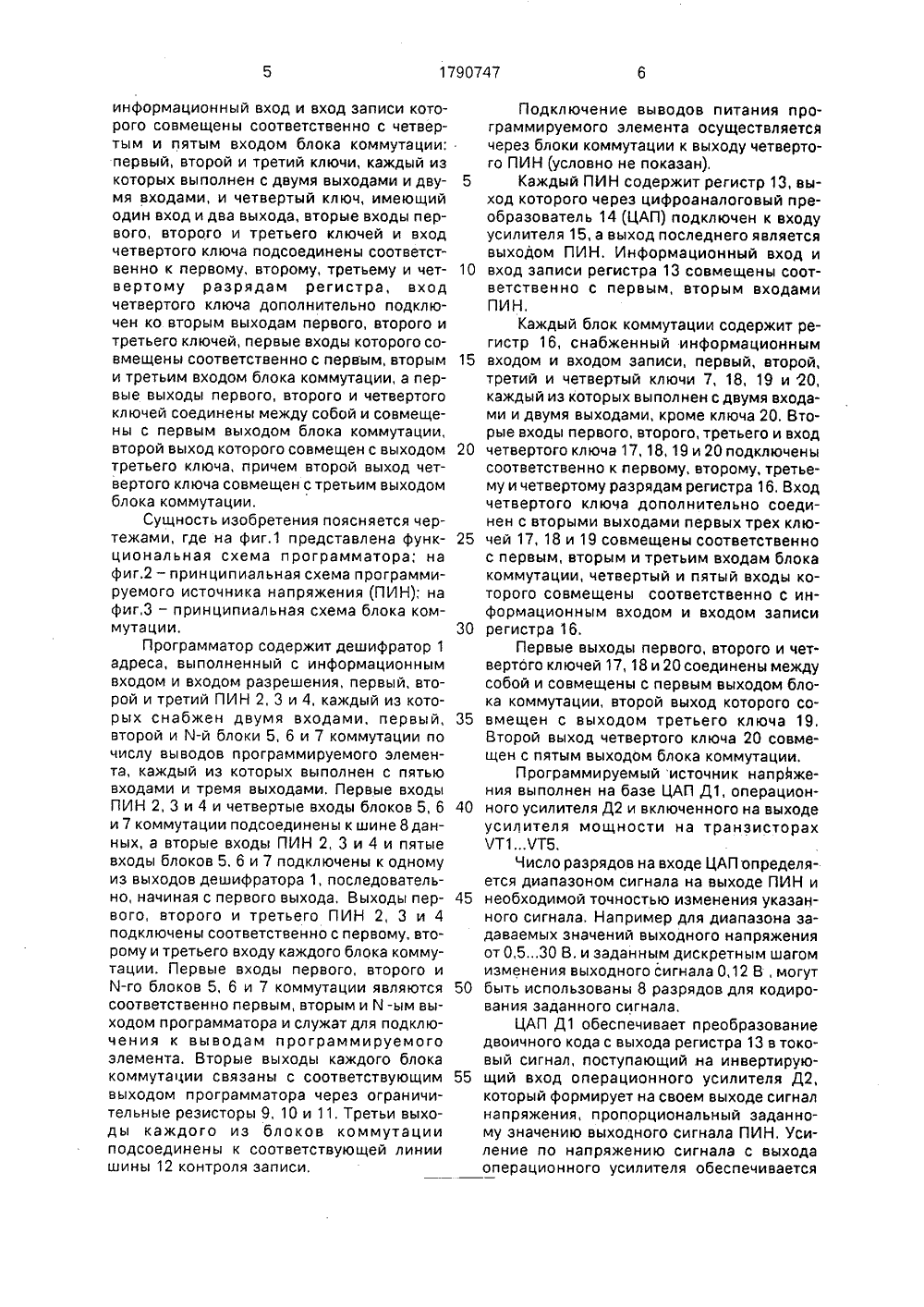

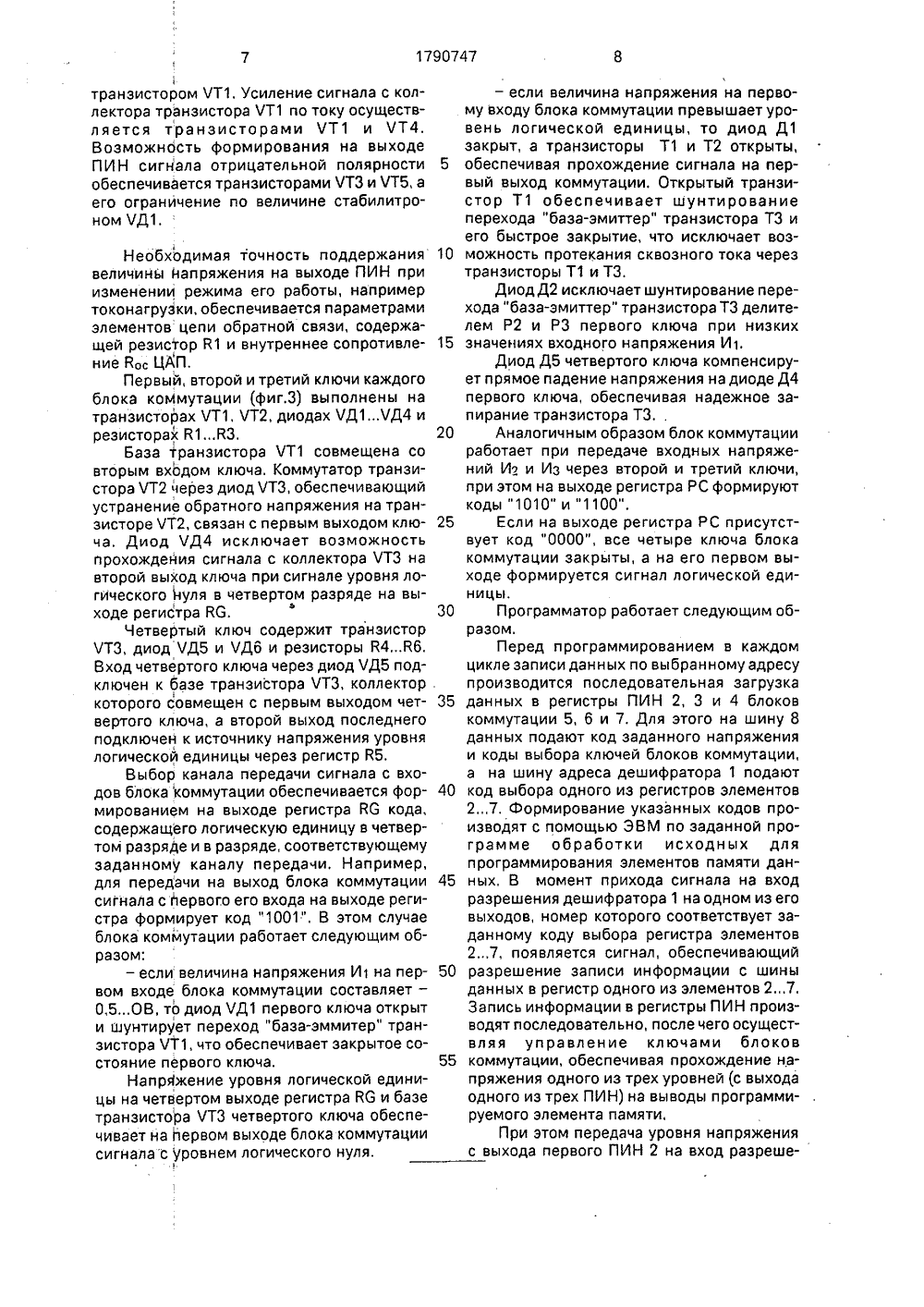

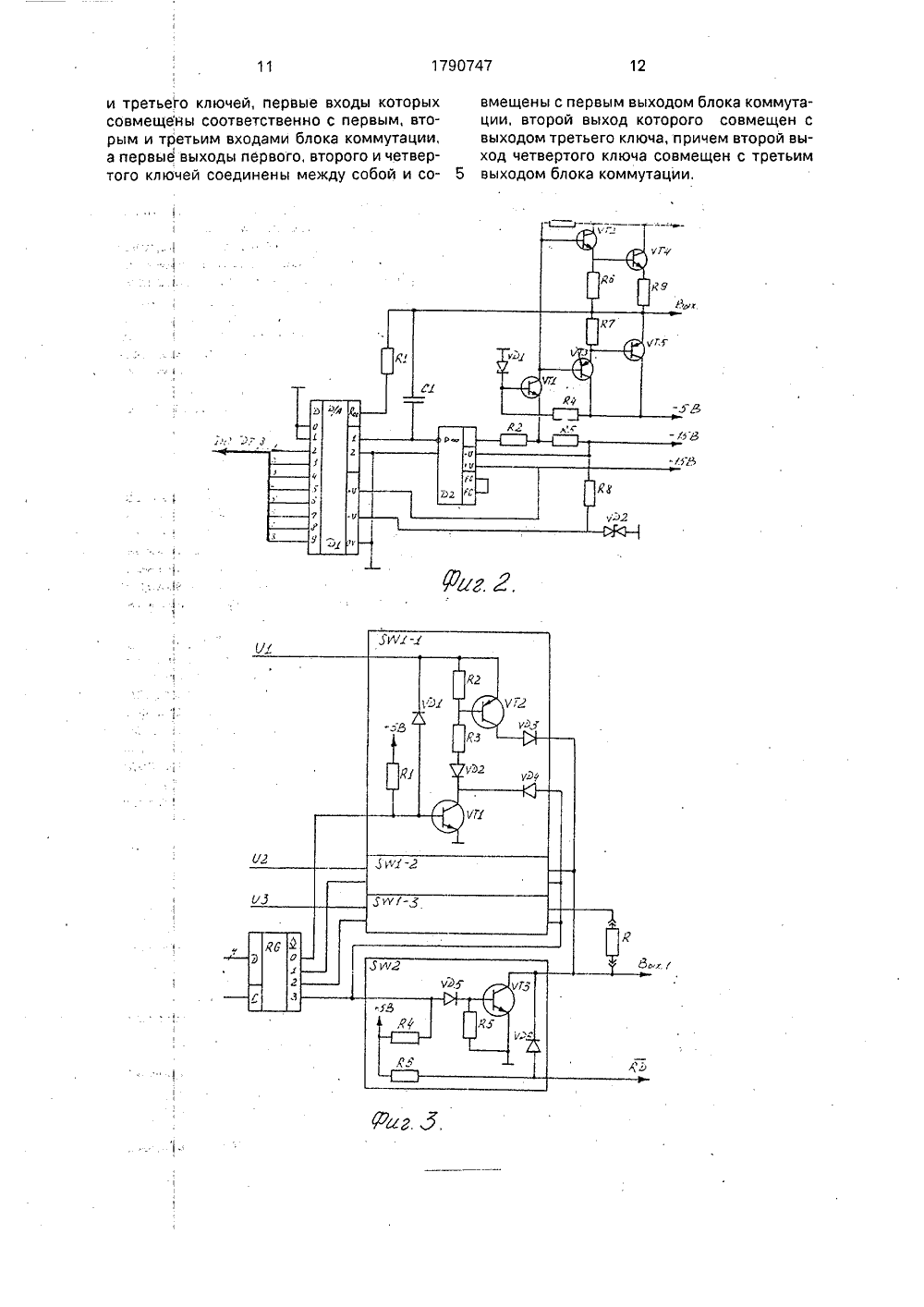

(51)5 С 01 М 15/00 ПАТЕНТУ рамматортри про- напряжеЬ ГОСУДАРСТВЕННОЕ ПАТЕНТНВЕДОМСТВО СССР(56) Авторское свидетельство СССРЛЬ 1575081, кл. 6 01 М 15/00, 1987.(57) Сущность изобретения: прогсодержит дешифратор 1 адреса,граммируемых источника 2, 3 и 4 ния, блоки 5, 6 и 7 коммутации, количество которых соответствует числу выводов программируемого элемента, шину 8 данных, связанных с блоками коммутации, Дешифратор 1 выходами подключен к входам программируемых источников 2, 3 и 4 напряжения и входам блоков 5, 6 и 7 коммутации, Первые выходы блоков 5, 6 и 7 коммутации предназначены для подключения к выводам программируемого элемента. Блоки 5, 6 и 7 коммутации имеют также выходы подключения к шине 12 контроля записи информации. 2 з,п. ф-лы, 3 ил.Изобретение относится к электронике, в частности к устройствам для перепрограммирования объектов, например испытательных комплексов двигателей внутреннего сгорания.Известен программатор испытательного комплексадвигателей внутреннего сгора- ниА, соержащйй блоки коммутации с информационными входами и блок контроля, связанный через шину контроля с каждым блоком коммутации.Данный программатор обеспечивает при необходимости содержание микросхем памяти комплекса, что обеспечивает замену программы испытаний. Однако известное техническое решение обеспечивает программирование только используемых именно в данномкомплексе микросхем, причем в очень узкихпределах, что позволяет менять лишь исходные параметры программы испытаний, безсмены самой программы испытаний, Крометого, данный программатор не меняет обратной связи по работе испытываемого двигателя и не позволяет в процессе испытанийоператйвно, в зависимости от обстоятельств, перепрограммировать микросхемыпамяти, в которых хранится программа испытаний,Частично эти недостатки устраненыв техническом решении по авт.св.С С С Р Р 1575081, М, кл, С 01 М 15/00, 1987,которое как наиболее близкое принято запрототип. Программатор для испытательного комплекса двигателей внутреннего сгорания согласно прототипу содержит блокикоммутации с информационными и управляющими входами, устройство выбора блокакоммутации, каждый из выходов которогоподключен к управляющему входу одного изблоков коммутации, и блок контроля, связанный через шину контроля с соответствующими выходами каждого блокакоммутации,Известное техническое решение позволяет перепрограммировать микросхемы па, мяти испытательного стенда, меняя нетолько параметры программы испытаний,но саму программу испытаний, в том числеи в процессе самих испытаний.Однако данный программатор в состоянии перепрограммировать только один типмикросхем, так как его конструкция не позволяет Одновременно менять напряжениеи ток выходного сигнала, что ограничиваетвозможности использования устройства,Цель изобретения - расширение функциональных возможностей и рограмматора,5 10 15 20 25 30 35 40 45 50 55 Поставленная цель достигается тем, что программатор, содержащий блоки коммутации с информационными и управляющими входами, устройство выбора блока коммутации, каждый выход которого подключен к управляющему входу одного из блоков коммутации, блок контроля, связанный через шину контроля с соответствующим выходом каждого блока коммутации, имеет первый, второй и третий программируемые источники напряжения, каждый из которых выполнен с двумя входами, количество блоков коммутации определяется числом выводов блока элементов программируемой памяти, каждый блок коммутации выполнен с пятью входами и тремя выходами, устройство выбора блока коммутации выполнено в виде дешифратора, информационный вход и вход разрешения которого совмещены соответственно со входом адреса и входом управления программатора, причем первые входы программируемых источников напряжения и четвертые входы блоков коммутации связаны с соответствующими линиями информационной шины программатора, вторые входы каждого программируемого источника напряжения и пятые входы блоков коммутации подключены каждый к одному из выходов дешифратора последовательно, начиная с первого выхода, выходы первого, второго и третьего программируемых источников напряжения подключены соответственно к первому, второму и третьему входу каждого блока коммутации; первые выходы блока коммутации выполнены в виде соответствующих выходов программатора и образуют первую группу его выходов, второй выход каждого блока коммутации связан с его первым выходом через ограничительный резистор, а третьи выходы каждого блока коммутации образуют вторую группу выходов программатора, подключаемую к шине контроля по соответствующим линиям.Достигаемый положительный эффект может быть дополнительно усилен за счет того, что каждый блок программируемого источника напряжения содержит регистр, информационный вход и вход записи которого совмещены соответственно с первым и вторым входами программирующего источника напряжения, выход регистра через цифроаналоговый преобразователь подключен ко входу усилителя мощности, причем последний выполнен на базе операционного усилителя и двухтактного усилителя тока,а выход усилителя мощности является выходом программируемого источника напряжения, а также за счет того, что каждый блок коммутации содержит регистр, 1790747информационный вход и вход записи которого совмещены соответственно с четвертым и пятым входом блока коммутации: первый, второй и третий ключи, каждый из которых выполнен с двумя выходами и двумя входами, и четвертый ключ, имеющий один вход и два выхода, вторые входы первого, второго и третьего ключей и вход четвертого ключа подсоединены соответственно к первому, второму, третьему и четвертому разрядам регистра, вход четвертого ключа дополнительно подключен ко. вторым выходам первого, второго и третьего ключей, первые входы которого совмещены соответственно с первым, вторым и третьим входом блока коммутации, а первые выходы первого, второго и четвертого ключей соединены между собой и совмещены с первым выходом блока коммутации, второй выход которого совмещен с выходом третьего ключа, причем второй выход четвертого ключа совмещен с третьим выходом блока коммутации.Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема программатора; на фиг.2 - принципиальная схема программируемого источника напряжения (ПИН); на фиг,3 - принципиальная схема блока коммутации.Программатор содержит дешифратор 1 адреса, выполненный с информационным входом и входом разрешения, первый, второй и третий ПИН 2, 3 и 4, каждый из которых снабжен двумя входами, первый, второй и К-й блоки 5, 6 и 7 коммутации по числу выводов программируемого элемента, каждый из которых выполнен с пятью входами и тремя выходами, Первые входы ПИН 2, 3 и 4 и четвертые входы блоков 5, 6 и 7 коммутации подсоединены к шине 8 данных, а вторые входы ПИН 2, 3 и 4 и пятые входы блоков 5, 6 и 7 подключены к одному из выходов дешифратора 1, последовательно, начиная с первого выхода, Выходы первого, второго и третьего ПИН 2, 3 и 4 подключены соответственно с первому, второму и третьего входу каждого блока коммутации. Первые входы первого, второго и М-го блоков 5, 6 и 7 коммутации являются соответственно первым, вторым и й -ым выходом программатора и служат для подключения к выводам программируемого элемента. Вторые выходы каждого блока коммутации связаны с соответствующим выходом программатора через ограничительные резисторы 9, 10 и 11. Третьи выходы каждого из блоков коммутации подсоединены к соответствующей линии шины 12 контроля записи. 5 10 15 20 25 30 35 40 45 50 55 Подключение выводов питания программируемого элемента осуществляется через блоки коммутации к выходу четвертого ПИН (условно не показан).Каждый ПИН содержит регистр 13, выход которого через цифроаналоговый преобразователь 14 (ЦАП) подключен к входу усилителя 15, а выход последнего является выходом ПИН, Информационный вход и вход записи регистра 13 совмещены соответственно с первым, вторым входами ПИН,Каждый блок коммутации содержит регистр 16, снабженный информационным входом и входом записи, первый, второй, третий и четвертый ключи 7, 18, 19 и 20, каждый из которых выполнен с двумя входами и двумя выходами, кроме ключа 20, Вторые входы первого, второго, третьего и вход четвертого ключа 17, 18, 19 и 20 подключены соответственно к первому, второму, третьему и четвертому разрядам регистра 16, Вход четвертого ключа дополнительно соединен с вторыми выходами первых трех ключей 17, 18 и 19 совмещены соответственно с первым, вторым и третьим входам блока коммутации, четвертый и пятый входы которого совмещены соответственно с информационным входом и входом записи регистра 16.Первые выходы первого, второго и четвертого ключей 17, 18 и 20 соединены между собой и совмещены с первым выходом блока коммутации, второй выход которого совмещен с выходом третьего ключа 19, Второй выход четвертого ключа 20 совмещен с пятым выходом блока коммутации.Программируемый источник напряжения выполнен на базе ЦАП Д 1, операционного усилителя Д 2 и включенного на выходе усилителя мощности на транзисторах ЧТ 1 ЧТ 5.Число разрядов на входе ЦАП определяется диапазоном сигнала на выходе ПИН и необходимой точностью изменения указанного сигнала. Например для диапазона задаваемых значений выходного напряжения от 0,5,30 В. и заданным дискретным шагом изменения выходного сигнала 0,12 В, могут быть использованы 8 разрядов для кодирования заданного сигнала,ЦАП Д 1 обеспечивает преобразование двоичного кода с выхода регистра 13 в токовый сигнал, поступающий на инвертирующий вход операционного усилителя Д 2, который формирует на своем выходе сигнал напряжения, пропорциональный заданному значению выходного сигнала ПИН, Усиление по напряжению сигнала с выхода операционного усилителя обеспечивается1790747 7транзистором ЧТ 1. Усиление сигнала с коллектора транзистора ЧТ 1 по току осуществляется транзисторами ЧТ 1 и ЧТ 4. Возможность формирования на выходе ПИН сигнала отрицательной полярности обеспечивается транзисторами ЧТЗ и ЧТ 5, а его ограничение по величине стабилитроном ЧД 1. Необходимая точность поддержания величины напряжения на выходе ПИН при изменении режима его работы, например токонагрузки, обеспечивается параметрами элементов цепи обратной связи, содержащей резисгор В 1 и внутреннее сопротивление Вос ЦАП.Первый, второй и третий ключи каждого блока коМмутации (фиг.З) выполнены на транзисторах ЧТ 1, ЧТ 2, диодах ЧД 1 ЧД 4 и резисторах К 1 ВЗ,База транзистора ЧТ 1 совмещена со вторым входом ключа. Коммутатор транзистора ЧТ 2 через диод ЧТЗ, обеспечивающий устранение обратного напряжения на транзисторе ЧТ 2, связан с первым выходом ключа, Диод ЧД 4 исключает возможность прохождения сигнала с коллектора ЧТЗ на второй выход ключа при сигнале уровня логического нуля в четвертом разряде на выходе регистра йб.Четвертый ключ содержит транзистор ЧТЗ, диод ЧД 5 и ЧД 6 и резисторы В 486, Вход четвертого ключа через диод ЧД 5 подключен к 6 азе транзистора ЧТЗ, коллектор которого совмещен с первым выходом четвертого ключа, а второй выход последнего подключен к источнику напряжения уровня логической единицы через регистр В 5,Выбор канала передачи сигнала с входов блока коммутации обеспечивается формированием на выходе регистра ВО кода, содержащего логическую единицу в четвертом разряДе и в разряде, соответствующему заданному каналу передачи. Например, для передачи на выход блока коммутации сигнала с первого его входа на выходе регистра формирует код "1001", В этом случае блока коммутации работает следующим образом:- если величина напряжения И 1 на первом входе блока коммутации составляет - 0,50 В, то диод ЧД 1 первого ключа открыт и шунтирует переход "база-эммитер" транзистора ЧТ 1, что обеспечивает закрытое состояние первого ключа,Напряжение уровня логической единицы на четвертом выходе регистра ВО и базе транзистора ЧТЗ четвертого ключа обеспечивает на йервом выходе блока коммутации сигнала с уровнем логического нуля,5 10 15 20 25 30 35 40 45 50 55- если величина напряжения на первому входу блока коммутации превышает уровень логической единицы, то диод Д 1 закрыт, а транзисторы Т 1 и Т 2 открыты, обеспечивая прохождение сигнала на первый выход коммутации, Открытый транзистор Т 1 обеспечивает шунтирование перехода "база-эмиттер" транзистора ТЗ и его быстрое закрытие, что исключает возможность протекания сквозного тока через транзисторы Т 1 и ТЗ.Диод Д 2 исключает шунтирование перехода "база-эмиттер" транзистора ТЗ делителем Р 2 и РЗ первого ключа при низких значениях входного напряжения И 1.Диод Д 5 четвертого ключа компенсирует прямое падение напряжения на диоде Д 4 первого ключа, обеспечивая надежное запирание транзистора ТЗ, .Аналогичным образом блок коммутации работает при передаче входных напряжений И 2 и Из через второй и третий ключи, при этом на выходе регистра РС формируют коды "1010" и "1100".Если на выходе регистра РС присутствует код "0000", все четыре ключа блока коммутации закрыты, а на его первом выходе формируется сигнал логической единицы,Программатор работает следующим образом,Перед программированием в каждом цикле записи данных по выбранному адресу производится последовательная загрузка данных в регистры ПИН 2, 3 и 4 блоков коммутации 5, 6 и 7. Для этого на шину 8 данных подают код заданного напряжения и коды выбора ключей блоков коммутации, а на шину адреса дешифратора 1 подают код выбора одного из регистров элементов 2,7, Формирование указанных кодов производят с помощью ЭВМ по заданной программе обработки исходных для программирования элементов памяти данных, В момент прихода сигнала на вход разрешения дешифратора 1 на одном из его выходов, номер которого соответствует заданному коду выбора регистра элементов 27, появляется сигнал, обеспечивающий разрешение записи информации с шины данных в регистр одного из элементов 27. Запись информации в регистры ПИН производят последовательно, после чего осуществляя управление ключами блоков коммутации, обеспечивая прохождение напряжения одного из трех уровней (с выхода одного из трех ПИН) на выводы программируемого элемента памяти,При этом передача уровня напряжения с выхода первого ПИН 2 на вход разреше10 1790747 ния записи одной из микросхем программируемого элемента памяти обеспечивает возможность выбора каждой. программируемой микросхемы в заданный момент времени (цикл программирования),Сигнал напряжения И 2 с выхода второго ПИН 3 поступает через ключи блока коммутации к выводам управления программирования, стиранием или адреса в зависимости 10 15 20 Формула изобретения 1, Программатор, содержащий блоки коммутации с информационными и управляющими входами, устройство выбора блока коммутации, каждый выход которого подключен к управляющему входу одного из блоков коммутации и блок контроля, связанный через шину контроля с соответствующим выходом каждого блока коммутации, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей, программатор имеет первый, второй и третий программируемые источники напряжения, каждый из которых выполнен с двумя входами, количество блоков коммутации соответствует числу выводов программируемого элемента памяти, каждый блок коммутации выполнен с пятью входами и тремя выходами, устройство выбора блока коммутации выполнено в виде дешифратора, информационный вход и вход разрешения которого совмещены соответственно с входом адреса и входом управления программатора, причем первые входы программируемых источников напряжения и четвертые входы блоков коммутации связаны с соответствующими линиями информационной шины программатора, вторые входы каждого программируемого источника напряжения и пятые входы блоков коммутации подключены каждый к одному из выходов дешифратора, выходы первого, второго и третьего программируемых источников напряжения подключены соответственно к первому, второму и третьему входу каждого блока коммутации, первые выходы блоков коммутации выполнены в виде соотот типа программируемой микросхемы Уровень напряжения на выходе третьего ПИН 4 подают на выходы данных программируемого элемента памяти, обеспечивая запись необходимой информации в ячейки памяти по адресу, установленному комбинацией напряжений уровня Иг на первых выходах блоков коммутации, подключенных к выводам адреса программируемой микросхемы. 25 30 35 40 45 50 55 Наличие резисторов 9, 10 и 11 обеспечивает ограничение выходных сигналов с ПИН при передаче их через вторые выходы блоков коммутации. Указанное необходимо при программировании различных типов микросхем.Для проверки произведенной записи с выводом данных программируемой микросхемы может осуществляться последовательный съем информации в шину 12 контроля, При этом все ключи блоков коммутации, выходы которых подключены к выводам данных программируемой микросхемы, должны быть закрыты, а выбор адреса проверяемой ячейки памяти осуществляется комбинацией напряжения уровня Иг на первых выводах блоков коммутации, подключенных к выводам адреса программируемой микросхемы. ветствующих выходов программатора и образуют первую группу его выходов, второй выход каждого блока коммутации связан с первым выходом через ограничительный резистор, а третьи выходы каждого блока коммутации образуют вторую группу выходов программатора, подключенную к шине контроля,2. Программатор по п.1, о т л и ч а ющ и й с я тем, что каждый программируемый источник напряжения содержит регистр, информационный вход и вход записи которого совмещены соответственно с первым и вторым входами программируемого источника напряжения, выход регистра через цифроа налоговый п реоб разо ватель подключен к входу усилителя мощности, причем последний выполнен на базе операционного усилителя и двухтактного усилителя тока, а выход усилителя мощности является выходом программируемого источника напряжения.3. Программатор по пп.1 и 2, о т л и ч аю щ и й с я тем, что каждый блок коммутации содержит регистр, информационный вход и вход записи которого совмещены соответственно с четвертым и пятым входами блока коммутации, первый, второй и третий ключи, каждый из которых выполнен с двумя выходами и двумя входами, и четвертый ключ, имеющий один вход и два выхода, вторые входы первого, второго и третьего ключей и вход четвертого ключа подсоединены соответственно к первому, второму, третьему и четвертому разрядам регистра, вход четвертого ключа дополнительно подключен к вторым выходам первого, второгои третьего ключей, первые входы которых совмещены соответственно с первым, вторым и третьим входами блока коммутации, а первые выходы первого, второго и четвертого ключей соединены между собой и совмещены с первым выходом блока коммутации, второй выход которого совмещен с выходом третьего ключа, причем второй выход четвертого ключа совмещен с третьим 5 выходом блока коммутации,

СмотретьЗаявка

4901553, 11.01.1991

В. С. Щичко, М. И. Строков, П. Е. Смирнов и В. В. Нащекин

ЩИЧКО ВЛАДИМИР СЕРГЕЕВИЧ, СТРОКОВ МИХАИЛ ИВАНОВИЧ, СМИРНОВ ПЕТР ЕВГЕНЬЕВИЧ, НАЩЕКИН ВЛАДИМИР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G01M 15/00

Метки: программатор

Опубликовано: 23.01.1993

Код ссылки

<a href="https://patents.su/6-1790747-programmator.html" target="_blank" rel="follow" title="База патентов СССР">Программатор</a>

Предыдущий патент: Стенд для испытаний топливно-регулирующей аппаратуры газотурбинных двигателей

Следующий патент: Устройство управления климатической камерой

Случайный патент: Устройство для измерения термо-эдс минералов