Формирователь тестов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1635187

Автор: Гремальский

Текст

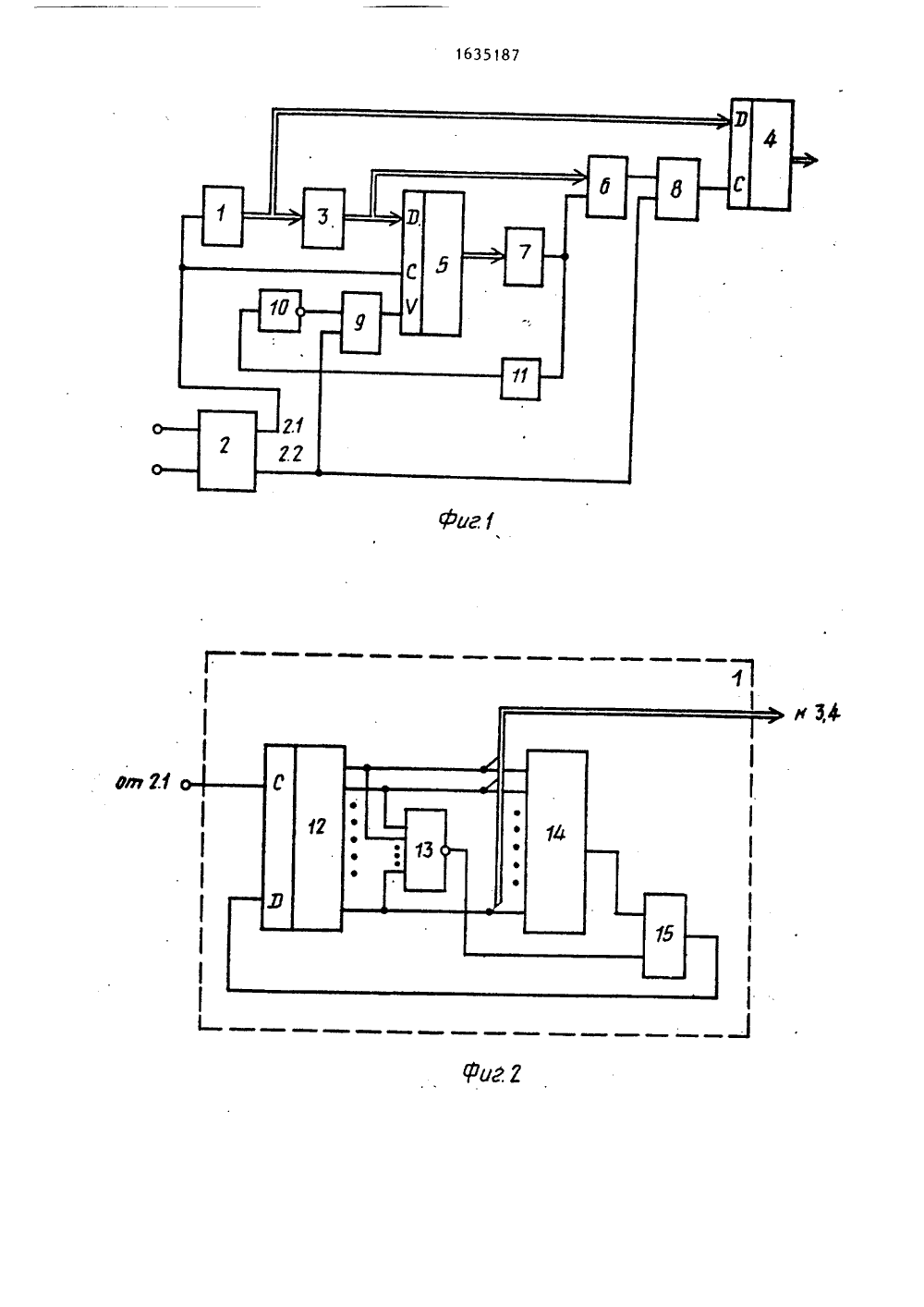

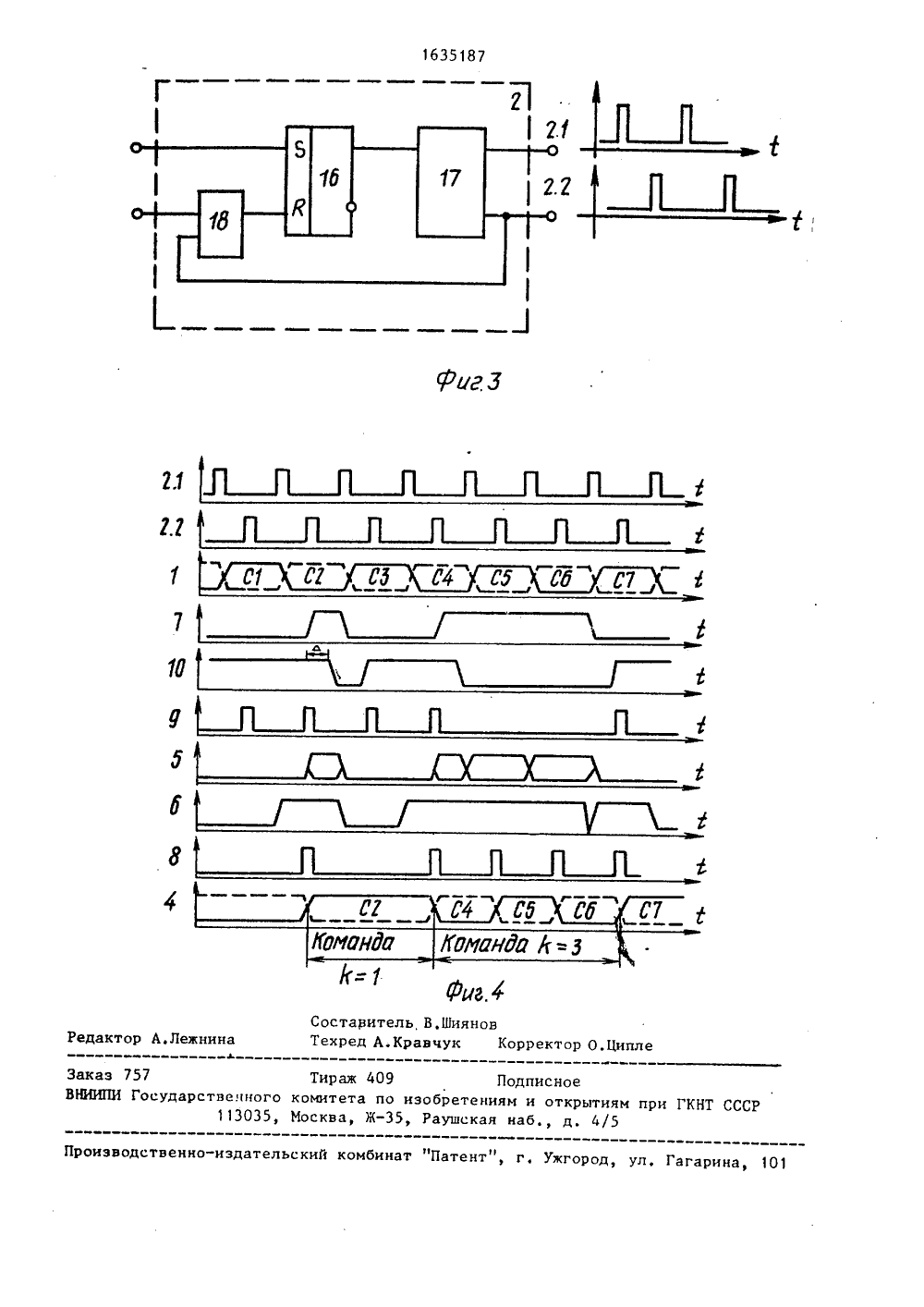

(5 РЕТЕНИ СТ У с следо аучн Ква ьство СССР/00) 1974,тво СССР1/26, 1985 етел Р 11 ельс Р 1 ТЕСТ носи ся к вычистности к то- с:Ю ско тро контроля в. Целью ение быс я по и,2, даций нт цессорных у использова леме ышленности и ен связи оце с водства и ных систе ксплу 1зобревия ф игов ыЦель итродейст На фигая схема я - повышенирователя.тавлена стру вязями, Генег, 2 содержит ент И-НЕ 13, ва и элемент йное число по м ктурователя ратора 3 1 предпредлага фиг, 2чайных к емо ормир гене естов е евдос дов; на фиг.низации; на ффункциониро двига приляющий вхоа 2,1 блокр 14 помо ани ержит ге адов,дами 2.1 разуют це ЭлементОСУДЛРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР ОПИСАНИЕ ИЗ М АВТОРСКОМУ СВИДЕТ(71) КишиНевский нтельский институт(57) Изобретение отлительной технике,средствам автоматичмикропроцессорных уизобретения являетс Изобретение относится к вычислиельной технике, в частности к сред ствам автоматического контроля микро роиств, и может быть адиоэлектронной проомышленности средств разработки, произтации микропроцессорсхема блока синхро временные диаграммь ормирователя, формирователь тестов нератор 1 псевдослучаиныхблок 2 синхронизации с в действия формирователя, Это достигается введением в формирователь, содержащий блок синхронизации, генератор псевдослучайных кодов, дешифратор запрещенных комбинаций и регистртеста, регистра сдвига, двух элементов ИЛИ и элемента задержки. Очередная команда формируется пословно путем выделения из случайных чисел,вырабатываемых генератором псевдослучайных кодов, допустимых команд,В качестве следующих слов командыиспользуются любые случайные числа,Выявление допустимых кодов команд идешифрация длины команды позволяюисключить этап анализа форматов кманд. 4 ил. ешифратор 3 запрещенных комрегистр 4 теста, регистр 5первый элемент ИЛИ 6, второйИЛИ 7, первый элемент И 8,лемент И 9, элемент НЕ 10 и11 задержки,атор 1 псевдослучайных кодов предназначен для формировани чайных чисел, В простейшем с он может быть реализован на регистрах с обратными с ратор, показанный на фи регистр 12 сдвига, элем сумматор 14 по модулю д ИЛИ 15. Очередное случа лучается в регистре 12 с поступлении на его управ "Сдвиг" импульса с выход 2 синхронизации, Суммато лю два и элемент ИЛИ 15 об обратной связи генератораИ-НЕ 13 предназначен для обеспеченияправильной работы генератора в случае,если в регистре 12 сдвига будет записан нулевой код.5Блок 2 синхронизации (фиг. 3)предназначен для формирования двухпоследовательностей сдвинутых одинотносительно другого тактовых импульсов на выходах 2, 1 и 2,2 соответственОно, Блок 2 синхронизации содержиттриггер 16, генератор 17 тактовых импульсов и элемент И 18.Дешифратор 3 (фиг, 1) предназначендля выбора из случайной последователь ности кодов с выхода генератора 1 техчисел, которые являются допустимымикодами команд микропроцессора, а также для определения длины команды, Дешифратор имеет 1 выходов, где 1максимально возможная длина командыконтролируемого микропроцессора. Еслислучайное число на входе дешифратора3 не является допустимым кодом команды, на всех его выходах устанавливаются значения "0", Если же случайноечисло на входе дешифратора 3 являетсякодом некоторой команды, на 1-м выходе, где 1 - длина рассматриваемойкоманды, устанавливается значение " 1",30а на всех остальных выходах - значениее "0",Регистр 4 теста служит для хранения очередного слова формируемой тесткоманды, Регистр имеет информационныйвход, по которому поступают соответст 35вующие слова, и управляющий вход Прием".Регистр 5 сдвига предназначен дляподсчета числа слов формируемой команды, Регистр 5 сдвига имеет информационные входы для параллельногоприема информации, управляющий вход"Прием" и управляющий вход "Сдвиг",Сдвиг в регистре осуществляется всторону младших разрядов,Первый элемент ИЛИ 6 предназначендля выработки сигнала "1" в случае,если на вход дешифратора 3 подаетсядопустимый код ком анды или если содержимое регистра 5 сдвига отлично отнуля.Второй элемент ИЛИ 7 предназначен для выработки сигнала "1" в случае, если содержимое регистра 5 сдвига отлично от нуля.Первый элемент И 8 предназначендля формирования управляющего сигна-ла "Прием" в регистр 4 теста, Сигнал"Прием" вырабатывается импульсом свыхода 2,2, блока 2 синхронизации приусловии, что на выходе первого элемента ИЛИ 6 установлено значение "1".Второй элемент И 9, элемент НЕ 10и элемент 11 задержки предназначеныдля формирования управляющего сигнала "Прием" в регистре 5 сдвига. Сигнал "Прием" формируется импульсом свыхода 2,2 блока 2 синхронизации приусловии, что содержимое регистра 5сдвига равно нулю, Элемент 11 задержки устраняет возможные состязания поконтуру регистр 5 сдвига - элементИЛИ 7 - элемент НЕ 10 - элемент И 9,Величина задержки элемента 11 должнабыть больше, чем время приема информации в регистр 5 сдвига. На практике функции элемента 11 могут выполнять паразитные задержки второго элемента ИЛИ 7 и элемента НЕ 10,На фиг. 4 обозначены: С 1, С,2С - коды на выходе генератора 1псевдослучайных кодов в тактах 1, 2,7 соответственно;- величина задержки элемента 11 задержки;- длина команды,Для пояснения работы формирователя тестов воспользуемся следующейструктурой команд микропроцессора.Команды микропроцессора имеют переменную длину и могут состоять иэ 1,2, 3 и т,д, слов, Например, микропроцессоры типа 1 МТЕ. 8080, К 580 имеют одно-, двух-, грехсловные команды, где длина одного слова состав яет 8 бит (один байт), Независимо оттипа команды код выполняемой операции, длина самой команды и режимыадресации операндов задаются в еепервом слове, Следующие слова команды содержат данные, участвующие воперациях, либо их адреса, Назовемпервое слово команды кодом команды.Формирователь работает следующимобразом.В исходном состоянии все элементыпамяти усгановлены в нулевое состояние (цепи начальной установки не показаны), По сигналу пуска триггер 16блока 2 (фиг, 3) устанавливается вединичное состояние и включает генератор 17, который начинает формирование тактовых импульсов на выходах2.1 и 2,2,По каждому тактовому импульсу свыхода 2,1 блока 2 осуществляетсясдвиг информации в регистре 12 сдви-,163518 35 га генератора 1 и формирование нового кода случайцого числа цл группевыходов генератора 1 (Фиг. 2),Каждый случайный кол с выхода ге 5нератора 1 (Фиг. 1) поступает нл входы дешифратора 3 запрещенных комбинаций, При этом возможны следудощиеслучач.Случлдд 1. Случлйцьпд код с выхода 10генератора 1 це является кодом команды (код С, лддбо Сцл временддой диаграмме Фиг, 4),При этом ца всех Выходлх дешифратора 3 устанавливается значение 15"0", Содержимое регистра 5 сдвига висходном состоянии бддло нулевым, поэтому после импульса сдвига с выхода2.1 содержимос регистрл также Остается нулевым. При этом дда Выходе элемента ИЛИ 7 устанавливается значение"0", ца выходе элемецтл НГ 10 - зцлчецие "1", ца Выходе элемента или 6значение "0", Импульс с Вьдхода 2.2блока 2 через элемент И 9 поступаетна управляющий Вход "Прием регистра5 сдвига, одддакс содержимое регистра5 остается нулевым, так клк все выходы дешифраторл 3 устацовлецы в "0",Поскольку цл выходе элемента ИЛИ 6 30установлено значение "О", цл Вьдходеэлемента И 8 сохраняется цулецосзначение, блокирующее запись случайного кода с выхода генератораврегистр 4 теста (Фиг, 1),Таким образом, если прц Формировании первого слова комлцддп цл Выходегенератора 1 вырабатывается случайный код, который це является кодомкоманды, содержимое регистра 5 сдвддгл дОостается нулевым, а случайцьпд код цезаписывается в регистр 4 теста,Случай 2, Случайньп код с выходлгенератораявляется кодом команды(код С, либо С цл временной диаграмме Фиг. 4), При этом а 1 Г-м Выходе,где 1 с - длина команды, дсшиФратора3 устанавливается зцлчецпе "1", а наостальных выходах - значение "0", Приэтом на Вьдходе элемента ИЛИ 6 устанавливлется зцачецие "1", Посколькув исходном состояцидд содержимое регистра 5 сдвига равно ддулдо, импульсс выхода 2.1 блока 2 це изменяет егосодержимого, При этом выход элементаИЛИ 7 установлен в "0", элемента НЕ10 - в "1". Импульс с выхода 2,2 блока 2 через элемент И 9 поступает цавход "Прием" регистра 5 сдвига и че 76рез элемент И 8 на вход ВПриемн регистра 4 теста. При этом в регистрсдвига записывается информация свыходов дешифратора 3, т,е, "1" запцсывлется в 1 с-й разряд и "Оц - в остальные разряды, а в регистр 4 теста записывается код команды, который с выходарегистра 4 теста поступает на выходФормирОВател 51,Изменение содержимого регистра 5СДВЦГЛ Г 1 РИВОД 1 Т К ТОМУ ЧТО ВЫХОД.лемета ИЛИ 7 устанавливается в "1",олнлко это це сказдпвается на прохож;дешди импульса с выхода 2.2 на вход"Прием" регистра 5, поскольку сигналс Выхода элемента ИЛИ 7 поступает наВход элемеддтл НГ 10 через задержку Ь(фддг4), задаваемую элементом 11задержки,К моменту поступления импульса сВыхода 2.1 блока 2 зддачеддие "1" свьдходл эледдеддта ПЛИ 7 через элемент1 злпсржкц и элемент НГ 10 устанавливает выход элемента И 9 в "О, Импульс с выхода 2.1 блока 2 поступаетл управляющий входСдвиг регистра5 сдвига, Содержимое регистра 5 сдвигается. При этом "1" переходит изразрядл 1 с в разря;1 (1 с) .Очевидно, если длина команды с1, после сдвига содержимое регистрл 5 сдцддга становится равным нулю,Вьдхо 1 элемента ИНИ 7 устанавливаетсяВ "0", л вьдход элемента НЕ 10 - в"1". Нл этом цикл Формирования очередой команды завершен и формирователь возвращается в исходное состояние, Начинается цикл Формированияследующей комлддды,1.сли же длина команды 1 с ) 1, то после сдвига содержимое регистра 5 сдвддга неравно нулю, так как (1 с)-й разряд установлен в "1", При этом "1" с Выхода элемента ИЛИ 7 блокирует поступление импульса с выхода 2,2 блока 2 цл вход "Прием" регистра 5 сд игл и разрешает поступление рассмлтрцваемого импульса через элемент Н 8 ца Вход "Прием" регистра 4 теста. Таким образом, если длина команды) 1, второе после кода команды случайное число с выхода генераторазаписывается в регистр 4 теста (коднл временной диаграмме фиг. 4).5Очередной импульс с выхода 2. блока 2 поступает ца управляющий вход "Сдвиг" регистра 5 сдвига, Приэтом в регистре 5 "1" из разрядаЬ) переходит в разряд (Е).Очевидно, если длина команды 1 с2, то после сдвига содержимое регистра 5 сдвига становится равнымнулю, выход элемента ИЛИ 7 устанавливается в "0", а выход элемента НЕ10 - в "1", На этом цикл формирования команды завершен, формировательвозвращается в исходное состояниеи начинается цикл формирования следующей команды,Если же длина команды 1 с ) 2, топосле сдвига содержимое регистра 5сдвига отлично от нуля и значение"1" с выхода элемента ИЛИ 7 аналогичным образом вновь блокирует прохождение импульса с выхода 2.2 на вход"Прием" регистра 5 сдвига и разрешает его прохождение на вход "Прием"регистра 4 теста. В результате врегистр 4 теста записывается третьеслово формируемой команды (код С)на временной диаграмме фиг. 4). 25С приходом с выхода 2, 1 блока 2очередного импульса в регистре 5 вновьвыполняется сдвиг и т.д. до тех пор,пока содержимое регистра 5 не станетравным нулю. При этом в регистре 4 ,30теста поочередно будут записаны ивыданы на выход формирователя, первое,второе1 с-е слова тест-команды,После выдачи -го слова формировательвновь возвращается в исходное состояние.Далее очередное случайное число(код С 7 на временной диаграмме фиг.4)с выхода генератора 1 вновь анализируется дешифратором 3 и аналогично 40описанному формируется очередная команда. При необходимости прекращения работы формирователь отключается сиг налом останова, подаваемым на вход элемента И 18 (фиг, 3), При этом триггер 16 устанавливается в нулевое ,состояние, генератор 17 выключается и прекращает выдачу тактовых импульсов на выходы 2.1 и 2,2,50Временные диаграммы работы формирователя (фиг, 4) представлены для случая, когда случайный код С 1 на выходе генератора 1 не является допустимым кодом команды, код. С является кодом команды с длиной 1 = 1, код С не является допустимым кодом команды, код С является кодом команды с длиной к = 3 и поэтому следующие коды С и С 6 на выходе генератора 1 используются в качестве второго и третьего слов формируемой тест-команды, код С является кодом команды,.Ф о р м у л а и з обретенияФормирователь тестов, содержащийблок синхронизации, генератор псевдослучайных кодов, дешифратор запрещенных комбинации и регистр теста, причем первый выход блока синхронизациисоединен с входом запуска генераторапсевдослучайных кодов, выходы которого соединены с информационными входами дешифратора запрещенных комбинаций, выход регистра теста являетсявыходом формирователя, о т л и ч аю щ и й с я тем, что, с целью повышения быстродействия, формировательсодержит регистр сдвига, два элементаИЛИ, два элемента И, элемент НЕ иэлемент задержки, причем выходы генератора псевдослучайных кодов соединены с информационными входами регистра теста, группа выходов дешифраторазапрещенных комбинаций соединена сгруппой информационных входов регистра сдвига и группой входов первогоэлемента ИЛИ, выход которого соединенс первым входом первого элемента И,выход которого соединен с входомсинхронизации регистра теста, группаразрядных выходов регистра сдвигасоединена с группой входов второгоэлемента ИЛИ, выход которого соединенс входом первого элемента ИЛИ и входом элемента задержки, выход которого соединен с входом элемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом разрешения регистра сдвига, вход синхронизациикоторого соединен с первым выходомблока синхронизации, второй выход которого соединен с вторыми входамипервого и второго элементов И, 1635187

СмотретьЗаявка

4492772, 10.10.1988

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ "КВАНТ"

ГРЕМАЛЬСКИЙ АНАТОЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 11/26

Метки: тестов, формирователь

Опубликовано: 15.03.1991

Код ссылки

<a href="https://patents.su/6-1635187-formirovatel-testov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь тестов</a>

Предыдущий патент: Устройство для управления переключением резервных блоков

Следующий патент: Устройство для сопряжения эвм с периферийной системой

Случайный патент: Трехфазный магнитный усилитель с положительной обратной связью