Модуль однородной вычислительной структуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

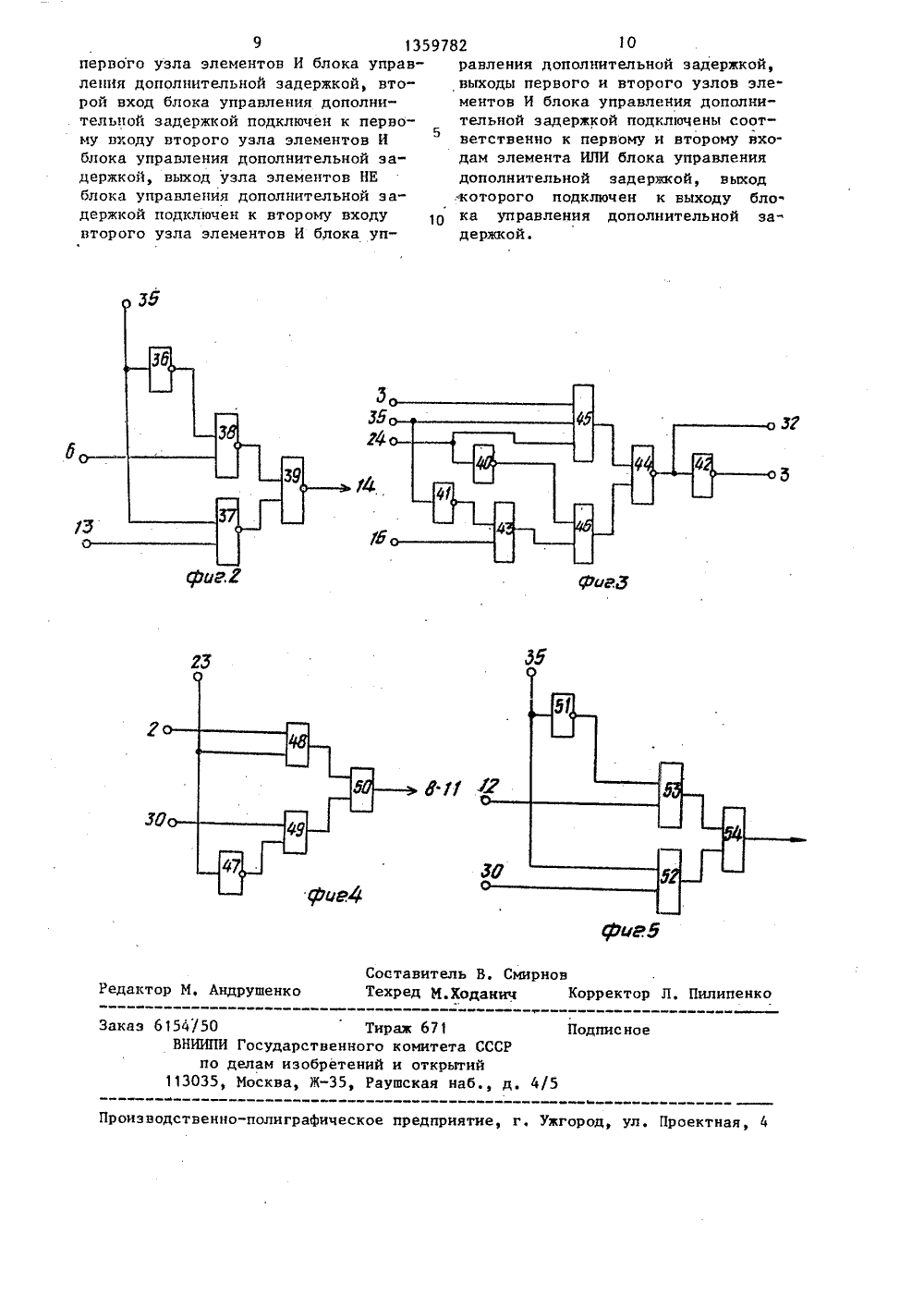

(54) МОДУЛЬСТРУКТУРЫ ИСЛИТ ЕЛЬН О(57) Изобретениетельной техникеиспользования в ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ относится к вычислии предназначено длякачестве модуля однородной вычислительной структуры,ориентированной на цифровую обработку сигналов. Цель изобретения - повышение быстродействия устройства, Указанная цель достигается тем, что вустройство, содержащее арифметика-логический блок 1 последовательного типа, регистр 3 команд, сдвиговый регистр 29 команд, дешифратор 4, триэлемента задержки 2,13 и 14, четыревыходных блока 8-11 коммутации, тривходных блока 5-7 коммутации, введеныблок 12 формирования константы, четвертый элемент задержки 30, блок 31управления дополнительной задержкой,блок 32 управления транзитом и блок33 расширения транзита с соответствующими связями, 5 ил,45 Изобретение относится к вычислительной техцике и предназначено дляиспользования н качестве модуля однородной вычислительной структуры,5ориентированной ца цифровую обработку сигналов.Цель изобретения - повышение быстродегстнпя.На фиг.1 представлена блок-схемамодуля однородной вычислительнойструктуры, на фиг.2 - схема блокарасширенного транзита; ца фиг.Зблок формирования константы; нафиг.4 - схема блока управления дополцительцой задержкой, на фиг.5 - схема блока управления транзитом,Модуль однородной вычислительнойструктуры содержит арифметико-логический блок 1 последовательного типа, 20;первый элемент 2 задержки, регистр 3команд, дешифратор 4, первый, второй,третий входные блоки 5,6 и 7 коммутации, первый - четвертый 8-11 выходные блоки коммутации, блок 12 формиронапия константы, второй элемент 13задержки, третий элемент 14 задеркки,пергый-четвертый 15-18 информационные входы, первый-четвертый выходы19-22 результата, поле 23 кода комацд регистра 3, поле 24 признаказадержки регистра 3, поле 25 адресавходного блока коммутации, поле 26адреса выходного блока коммутации,вход 27 записи команды, вход 28 синхронизации, сднигоный регистр 29 комацд, четвертый элемент 30 задержки,блок 31 управления дополнительной задержкой, блок 32 управления транзитом, блок 33 расширенного транзита, 40выходы 34 и 35 кода команды и кодаконстанты соответственно дешифратора 4, при этом блок 33 расширенноготранзита содеркит узел 36 элементовНЕ, первый и второй узлы 37 и 38элементов ИЛИ, элемент ИЛИ 39 блок12 формирования константы содержитпервый узел 40 элементов НЕ, второйи третий узлы 41 и 42 элементов НЕ,первый и второй узлы 3 и 44 элементов ИЛИ, первый и второй узлы 45и 46 элементов И, блок 31 управления дополнительной задержкой содержит узел 7 элементов НЕ, первый ивторой узлы 48 и 49 элементов И,55элемент ИЛИ 50; блок 32 управлениятранзитом содержит узел 51 элементовНЕ, первый и второй узлы 52 ц 53элементов И, элемент ИЛИ 54. Устройство работает следующим ооразом.Перед началом решения задачи производится запись команды н регистры3 и 29. Код команды состоит из кодаоперации, признака задержки адресоввходов первого и нторого чисел арифметико-логического элемента, адресавхода транзита, адреса выхода арифметико-логического блока и адресовныходов транзита с задержкой ца одинтакт и два такта. Код команды вводится через нхоц 27 модуля,После окончания сигнала, разрешающего ввод программь, код командызапоминается в регистре 3 команд,после чего на вход 28 ячейки подается сигнал управления вводом программы, равныи 0, и модуль переходитв режим выполнения операций, Дешифратор 4 настраивает ячейку ца ныпол-,кение операций согласно записанномун регистр 3 команд коду операций.. На выход 24 регистра команд выводится занесенный в регистр 3 командпризнак задержки н виде "0" или "1",В случае "1" на выходе 24 регистракоманд блока 31 управления дополни- .тельной задержкой результата арифметико-логического блока нключаетсян операционную цепь элемент 30 задержки. При наличии "Оц па выходе24 регистра команд информация с выхода элемента 2 задержки поступаетна вход блока 31 управления дополнительной задержкой результата арифметико-логического блока и далее напервые входы ньтодцьгс блоков 8 - 11коммутации,Выходы 25 и 26 регистра командосуществляют гыбор направления приема и выдачи ицформацяи ячейкой пооперационной цепи и цепи транзита,В зависимости от кода операции, записанного н регистр 3 команд, цепьтранзита может работать автономноот операционной сети, осуществляяпередачу информации с блока 7 черезблок 32 управления транзитом, элемент 13 задержки и третьи входы выходньх блокон 8-11 коммутации, еслив регистр 3 команд записан адрес выхода транзита с задержкой на одинтакт, или после второго элемента 13задержки на второй вход блока 33 расширенного транзита с ее выхода наэлемент 14 задержки и с его выходана вторые входы выходных блоков 8 3 13597 11 коммутации, если в регистр 3 команд записан адрес выхода транзита с задержкой на два тактаПри выполнении ячейкой операции "Расширенный транзит" сигнал с вы 5 ходов 35 дешифратора 4 включает две дополнительные цепи транзита. В первой дополнительной цепи транзита информация принимается с входного блока 5 коммутации на вход первого 10 арифметико-логического блока 1, поступает на его выход и через элемент 2 задержки, элемент 30 задержки и блок 31 управления дополнительной задержкой результата арифметика-логи ческого блока выдается на первые входы выходных блоков 8-11 коммутации. Во второй дополнительной цепи транзита информация принимается с второго входного блока 6 коммутации 20 на вход блока 33 расширенного транзита и с ее выхода поступает на вход элемента 14 задержки, с выхода которого выдается на вторые входы выходных блоков 8-11 коммутации, По при знаку задержки, равному "О" или "1", подаваемому с выхода 24 регистра команд на управляющий вход блока 31 управления дополнительной задержкой результата, в первой дополнительной 30 цепи транзита производится выход транзита с задержкой на один или два такта.При выполнении модулем операции Расширенный транзит цепь транзита модуля работает автономно от двух дополнительных цепей транзита и выдача информации модулем по этой цепи осуществляется только с задержкой на один такт (вход блока 32 управления 40 транзитом, элемент 13 задержки и третьи входы блоков 8-11).При выполнении ячейкой операции нГенератор констант" сигнал с выходов 35 дешифратора 4 включает цепь закольцовки части регистра 29 и отключает операционную цепь модуля от входных блоков 5 и 6 коммутации, сигнал признака задержки с выхода 24 регистра команд, равный "О", отключает из цепи закольцовки блок 12 и включает цепь транзита от входного блока 7 коммутации. Константа с выхода регистра команд через блок 12 по цепи закольцовки циркулирует в разрядах регистра 29 команд и одновременно последовательно через равные интервалы времени, определяемые дли 82 4ной слова константы, поступает с выхода блока 12 на вход блока 32 управления транзитом, передается поцепи транзита и выдается на вторыевходы блоков 8-11.При выполнении модулем операцииГенератор макроконстантн на входблока 12 поступает сигнал признаказадержки с первого выхода 24 регистра команд, равный "1", который под"ключает вход блока 12 к информационому входу 15 модуляразмыкает цепьзакольцовки регистра 29, Информацияс информационного входа 15 модуляпоступает на вход блока 12, а с первого его выхода поступает в разрядырегистра 3 команд, через равные интервалы времени подается с его выхода на вход блока 12 и через второйего выход на вход блока 32 управления транзитом передается по цепитранзита и выдается на вторые входыблоков 8-11.Наличие блока формирования константы и блока управления транзитомобеспечивает возможность реализациигенерации макроконстант длиной более 8 бит,Наличие блока управления дополни,тельной задержкой арифметико-логического блока и четвертого элемента задержки позволяет реализовать программно-управляющую дополнительнуюзадержку результата в операционнойцепи, что дает возможность сэкономить количество модулей при организации вычислительной структуры.Блок расширенного транзита позволяет реализовать в модуле дополнительную независимую от других транспортную цепь, что. увеличивает гибкость реализации алгоритмов на вычислительной структуре. Данный модульоднородной вычислительной структуры позволяет повысить производительность структуры в 1,3 раза прирешении задач обработки изображенийпороговым методом, методом гистограмми методом выделения контуров в системе, а также сократить количествоиспользуемых в структуре модулей доЗОБ по сравнению с использованиемустройства-прототипа,Формула изобретенияМодуль однородной вычислительнойструктуры, содержащий арифметико-ло26команд, вторые управляющие входы с первого по четвертый выходных блоков коммутации подключены соответственно к группам выходов с третьей по шестую поля выходного адреса сдвигового регистра команд, управляющий вход третьего входного блока коммутации под- ключен к пятой группе выходов поля входного адреса сдвигового регистра команды, о .т л и ч а и щ и й с я тем, что, с целью повышения быстродействия, в него введены блок формирования константы, четвертый элемент задержки, блок управления дополнительной задержкой, блок управления транзитом, блок расширенного транзита, первая группа выходов поля задержки регистра команд подключена к первому управляющему входу блока формирования константы, вторая группа выходов поля признака задержки ре- гистра команд подключена к управляющему входу блока управления дополнительной задержкой, первый информационный вход блока формирования константы подключен к первому информационному входу модуля, второй информационный вход блока йормирования константы подключен к выходу переноса последнего разряда сдвчгающего регистра команды, второй управляющий вход блока формирования константы, управляющий вход блока управления транзитом, управляющий вход блока расширения транзита подключены соответственно к группам выходов с второй по четвертую дешифратора, инйормационный выход блока формирования константы подключен к первому информационному входу блока управления транзитом, управляющий выход блока формирования константы подключен к вхо,ду установки в "1" поля признака задержки регистра команд, выход третьего входного блока коммутации подключен к второму информационному входу блока управления транзитом, вы-. ход которого подключен к входу вто; рого элемента задержки, выход второго входного блока коммутации подключен к первому информационному входу блока расширенного транзита, второйинйормационный вход которого подключен к выходу второго элемента задержки, выход блока расширенного.транзита подключен к входу третьего элемента задержки, выход первого элемента задержки подключен к входу 5 135978гический блок последовательного типа,регистр команд, сдвиговый регистр команд, дешифратор, первый, второй итретий элементы задержки, первый,второй, третий, четвертый выходныеблоки коммутации, входы дешийратораподключены к выходам поля кода операции регистра команд, первые инйормационные входы с первого по четвертыйвходных блоков коммутации подключенык первому информационному входу модуля, вторые информационные входы спервого по четвертый входных блоковкоммутации подключены к второму информационному входу модуля, третьиинформационные входы с первого почетвертый входных блоков коммутацииподключены к третьему информационномувходу модуля, четвертые информационные входы с первого по четвертыйвходных блоков коммутации подключенык четвертому инйормационному входумодуля, выходы с первого по четвертыйвыходных блоков коммутации подключены соответственно к выходам с первого по четвертый результата модуля,вход записи команды в модуль подключен к входу записи регистра команди к входу записи сдвигового регистракоманд, вход синхронизации модуляподключен к синхровходу регистра команд и к синхровходу сдвигового регистра команд, вход первого элемента задержки подключен к выходу арийметико-логического блока последовательного типа, первая группа выходовдешифратора подключена к входам кодаоперации арифметико-логического блокапоследовательного типа, первый и вто Орой входы операндОв которого подключены соответственно к выходам первого и второго входных блоков коммутации, управляющие входы которых подключены соответственно к первым ивторым группам выходов поля адресасдвигового регистра команд, выходвторого элемента задержки подключенк третьим информационным входам спервого по четвертый выходных блоков50коммутации, выход третьего элементазадержки подключен к вторым информационным входам с первого по четвертыйвыходных блоков коммутации, первыеуправляющие входы с первого по чет 55вертый выходных блоков коммутацииподключены соответственно к группамвыходов с первой по четвертую полявходного адреса сдвигового регистрачетвертого элемента задержки и к первому инАормациоцному входу блока управления дополнительной задержкой, второй инФормационный вход которого5 подключен к выходу четвертого элемента задержки, выход блока управления дополнительной задержкой подключен к первым информационным входам с первого по четвертый выходных блоков коммутации, при этом блок формирования константы содержит два узла элементов И, два узла элементов ИЛИ, три узла элементов НЕ, первый управляющий вход блока Формирования констант подключен к входу первого узла элемента НЕ блока Аормирования константы и к первому входу первого узла элементов ИЛИ блока формирования константы, второй управляющий вход блока формирования константы подключен к второму входу первого узла элементов ИЛИ блока Аормировация константы и к входу второго узла элементов НЕ блока формирования константы, 25 первый информационный вход блока формирования константы подключен к первому входу первого узла элементов ИЛИ блока Аормирования константы, второй инАормационный вход блока фор- ЗО мирования константы подключен к третьему входу первого узла элементов И блока формирования константы, выход первого узла элементов ИЛИ блока формирования константы подключен к первому входу второго узла элементов И блока Аормирования константы, второй вход которого подключен к выходу первого узла элементов НЕ блока Аормирования константы, выход второго узла элементов НЕ блока Аормирования константы подключен к второму входу первого узла элементов ИЛИ блока формирования константы, выход первого узла элементов И блока Аормирования константы подключен к первому входу второго узла элементов ИЛИ блока формирования константы, второй вход которого подключен к выходу второго узла элементов И, инверсный выход второго узла элементов ИЛИ блока формирования константы подключен к инАормационному выходу блока формирования константы и к входу третьего узла элементов НЕ .блока формирования константы, выход которого подключен к управляющемУ выходу блока формирования константы, при этом блок управления транзитом содержит два узла элементов И, элемент ИЛИ ц узелэлементов НЕ, управляющий вхоп блокауправления транзитом подключен к входу узла элементов НЕ блока управлениятранзитом и к первому входу первогоузла элементов И блока управлениятранзитом, второй вход которого подключен к первому информационному входу блока управления транзитом, вторыеинАормациоцные входы блока управления транзитом подключены к первомувходу второго узла элементов И блокауправления транзитом, второй вход которого подключен к выходу узла элементов НЕ блока управления транзитом,выходы первого и второго блоков элементов И блока управления транзитомподключены соответственно к первомуи второму входам элемента ИЛИ блокауправления транзитом, выход которогоподключен к выходу блока управлениятранзитом, при этом блок расширенного транзита содержит два узла элементов ИЛИ, узел элементов НЕ, элементИЛИ, управляющий вход блока расширенного транзита подключен к входуузла элементов НЕ блока расширенноготранзита и к первому входу первогоузла элементов ИЛИ блока расширенноготранзита, первый вход блока расширенного транзита подключен к первомувходу второго узла элементов ИПИ блока расширенного транзита, второйвход которого подключен к выходу узла элементов НЕ блока расширенноготранзита, второй вход блока расширенного транзита подключен к второмувходу первого узла элементов ИПИ блока расширенного транзита, инверсныевыходы первого и, второго узлов элементов ИЛИ блока расширенного транзита подключены соответственно кпервому и второму входам элементаИЛИ блока расширенного транзита, инверсный выход которого подключен квыходу блока расширенного транзита,при этом блок управления дополнительной задержкой содержит два узлаэлементов И, узел элементов НЕ, элемент ИЛИ, управляющий вход блока управления дополнительной задержкойподключен к первому входу первогоузла элементов И блока управлениядополнительной задержкой и к входуузла элементов НЕ блока управлениядополнительной задержкой, первыйвход блока управления дополнительнойзадержкой подключен к второму входу9 1359782 1 Опервого узла элементов И блока управ- равления дополнительной задержкой, ления дополнительной задержкой, вто" выходы первого и второго узлов элерой вход блока управления дополни- ментов И блока управления дополнительной задержкой подключен к перво- тельной задержкой подключены соотму входу второго узла элементов И5ветственно к первому и второму вхо" блока управления дополнительной за- дам элемента ИЛИ блока управления держкой, выход узла элементов НЕ дополнительной задержкой, выход блока управления дополнительной эа- -.которого подключен к выходу блодержкой подключен к второму входу 10 ка управления дополнительной завторого узла элементов И блока уп- держкой. Ю.О фМРЯ Составитель В. СмирновТехред М.Ходанич Корректор Л, Пилипенч едактор ущенк 154/50ВНИИПИ Государстпо делам изоб113035, Москва, Ж Тираж 671енного комитета СССРетений и открытий35, Раушская наб., д. ака одписно жгород, ул. Проектная, 4 онэ водственно-полиграфическое предприятие

СмотретьЗаявка

3788053, 11.09.1984

ОРГАНИЗАЦИЯ ПЯ М-5222

БОГАЧЕВ МИХАИЛ ПАВЛОВИЧ, ВОЛЬПЕРТ ЛЕОНИД АБРАМОВИЧ, ДЫЧАКОВСКИЙ ВИКТОР БРОНИСЛАВОВИЧ, МИХАЙЛОВ ИГОРЬ АЛЕКСАНДРОВИЧ, МУХИН АЛЕКСЕЙ АЛЕКСЕЕВИЧ, ОСОКИН ЮРИЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: вычислительной, модуль, однородной, структуры

Опубликовано: 15.12.1987

Код ссылки

<a href="https://patents.su/6-1359782-modul-odnorodnojj-vychislitelnojj-struktury.html" target="_blank" rel="follow" title="База патентов СССР">Модуль однородной вычислительной структуры</a>

Предыдущий патент: Многоканальное устройство для обмена информацией

Следующий патент: Система коммутации

Случайный патент: Угловая экструзионная головка дляизготовления цилиндрических изделийиз полимерных материалов