Генератор испытательных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1322275

Авторы: Гроль, Карачун, Лупанова, Ништ, Романкевич

Текст

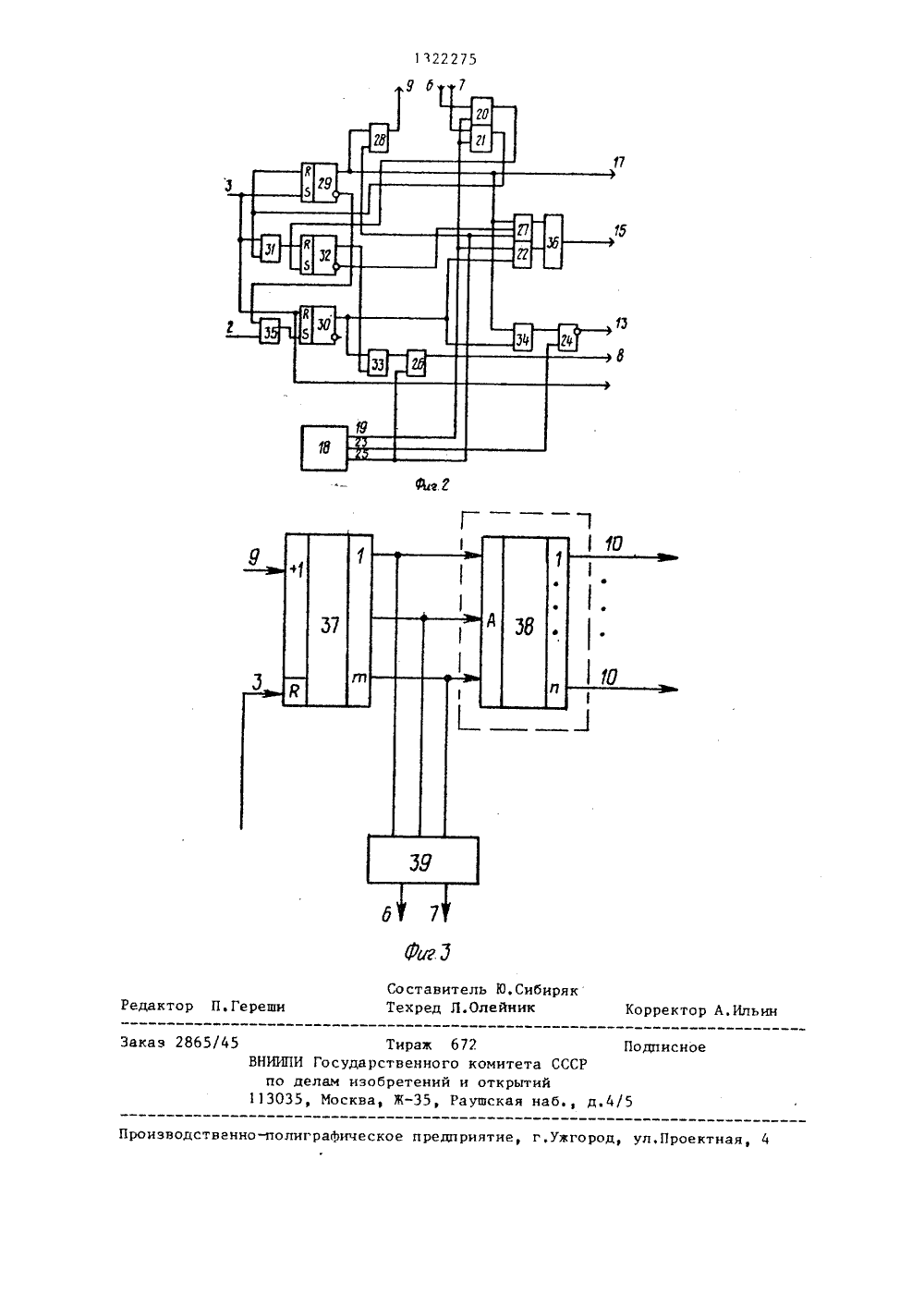

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН 50 4 С 06 8 Н 03 К 3 84 РСТВЕННЫЙ НОМИТЕТ СССР М ИЗОБРЕТЕНИЙ И ОТНРЫТ ГОС ПОД ИСАНИЕ ИЗОбРЕТЕ ОРСНОМУ СВИДЕТЕЛЬСТВ ор(71) Киевский политехнический институт им.50-летия Великой Октябрьскойсоциалистической револоции(56) Авторское свидетельство СССРФ 920718, кл. С 06 Р 7/58, 09.07.80.(54) ГЕНЕРАТОР ИСПЫТАТЕЛЬНЪХ КОДОВ(57) Изобретение может быть использовано в аппаратуре контроля и диагностики цифровых блоков. Цель изобретения - расширение функциональных ора. Генераадреса, коммативной пам6Введение возможностей гене утатибложит счетчик 5 1, блок 12 опер одной регистр 1 ввода, блока 14 лака 1 управлен кага,регия и стров сдви обраэовани ей позволя частотой вых ункциональных ет одновреме появления ед той переключ генератора и довательност ратора, В оп влят гнала, частоов на выходах ичного с ния си риода послегналов генеавлены приия блока 1 еличиновых ед анин п го вью меры конкретуправления иф-лы, 3 ил. а 4 вв 2 э.п.Изобретение относится к импульсной технике и может быть использовано в качестве источника последовательностей различных типон испыта - тельных кодов в аппаратуре контроля и диагностики цифровых блоков.Цель изобретения - расширениефункциональных возможностей генератора испытательных кодов за счет одновременного управления частотой появления единичного сигнала, частотойпереключения сигналов на выходах генератора и величиной периода последовательности выходных сигналов генератора,На фиг.1 представлена функциональная схема генератора испытательныхкодов; на фиг. 2 - функциональнаясхема блока управления; на фиг. 3функциональная схема блока ввода.Устройство содержит блок 1 управления, входами которого являются шина 2 пуска и шина 3 установки в исходное состояние, который подключенк блоку 4 ввода и входу сброса счетчика 5 адреса, Выходы 6 и 7 блока4 ввода подключены к соответствующимвходам блока 1 управления, выход 8которого связан с суммирующим входомсчетчика 5 адреса. Выход 9 блока управления 1 соединен с блоком 4, группа выходов 10 которого связана спервой группой входон коммутатора1, выходы которого соединены с информационными входами. блока 12 оператинной памяти, адресные входы которого подключены к выходам счетчика5 а,преса,1Вьход 13 блока 1 упранления сое Одинен с управляющим входом блока 12оперативной памяти, выходы которогосвязаны с информационными входамиблока 14 регистров сдвига, синхровход которого связан с ныходом 15 4блока 1 управления, подключенным также к синхровходу выходного регистра 16. Выходы блока 14 регистровсдвига соединены с информационнымивходами выходного регистра 16, выходы которого подключены к второй группе входон коммутатора 11, управляющий вход которого связан с выходом17 блока 1 управления и с установочным входом выходного регистра 16, Вы-ходы регистра 16 являются выходамигенератора.Блок 1 управления содержит генератор 18 тактовых импульсов, выход 19 которого соединен с входами элементов И 20-22. Выход 23 генератора 8 тактовых импульсов соединен с входом элемента И 24, выход 13 которого является выходом блока 1 управления 1. Выход 25 генератора 18 тактовых импульсов соединен с входами элементов И 26 - 28, Вход установки в "1" триггера 29 соединен с входом установки в О триггера 30, с входом элемента ИЛИ 31 и с шиной 3 установки н исходное состояние блока 1 управления.Вход установки в "0" триггера 29 подключен к выходу элемента И 21 и соединен с вторым входом элемента ИПИ 31, выход которого связан с входом установки в "0" триггера 32, прямой выход которого соединен с входом элемента ИЛИ 33, выход которого соединен с вторым входом элемента И 26. Прямой выход триггера 29 соединен со нторыми входами элементов И 28 и 27, с входом элемента ИЛИ 34 и с выходом 17 блока 1 управления.Инверсный выход триггера 29 соединен с входом элемента И 35, выход которого подключен к входу установки н "1" триггера 30, прямой выход которого соединен с вторыми входами элементов И 22, ИЛИ 33 и 34, выход последнего заведен на второй вход элемента И 24. Инверсный выход триггера 32 подключен к третьему входу элемента И 27, выход которого. связан с входом элемента ИЛИ 36 выход которого соединен с выходом 15 блока 1 управления.Второй вход элемента ИЛИ 36 связан с выходом элемента И 22, Вход 6 блока 1 управления заведен на второй вход элемента И 20, выход которого соединен с входом установки в "1" триггера 32, Входы 2 и 6 блока 1 управления подключены к вторым входам элементов И 35 и 21 соответственно.Блок 4 ввода содержит счетчик 37, выходы которого соединены с нходами блока 38 постоянной памяти и подключены к входам селектора 39, первый выход последнего соединен с выходом 6 блока 4 ввода, второй выход селектора 39 является выходом 7 блока 4 ввода. Вход 3 блока 4 ввода связан со входом сброса счетчика 37, а вход 9 блока 4 соединен с суммирующим входом счетчика 37, Выходы блока 38 являются группой выходов 10 блока 4.Генератор испытательных кодов работает следующим образом,На этапе загрузки сначала осуществляется заполнение блока 14 регистров, затем - блока 12 оперативной памяти. Для загрузки на блоки управления 1 ввода 4 подается сигнал "Исходная установка . Этим же сигналом счетчик 5 адреса сбрасывается в нулевое состояние. На адресный вход 17 О коммутатора 11 подается управляющий сигнал с блока 1 управления, который разрешает передачу информации с выходов блока 4 ввода на входы блока 12 оперативной памяти, По управляло щему сигналу с выхода 13 блока 1 управления информация записывается в нулевую ячейку блока 12С выхода 15 блока 1 управления на синхровход блока регистров 14 подается управляющий сигнал, сдвигающий на один разряд содержимое регистров блока 14, при этом информация из нулевой ячейки блока 12 записывается в блок 14. Аналогичным образом заполняются все разряды регистров блока 14, после чего с блока 4 ввода на вход 6 блока 1 управления приходит сигнал окончания загрузки блока 14 регистров, формируемый селектором 39, 30 Селектор 39 может быть построен на многовходовых элементах И с входнымиинверторами.функцией селектора 39 является выделение (селекция) двух кодов адре са от счетчика 37, поступающих на блок 38 постоянной памяти. формирование первого из этих кодов свидетельствует об окончании загрузки регистров блока 4 и служит сигналом для 40 блока 1 к заполнению блока 12. Появление второго кода на адресных входах блока 38 является признаком завершения загрузки блока 12 и окончания режима начальной загрузки устрой ства. Затем осуществляется заполнение блока 12 оперативной памяти. При этом в каждом такте с выходов блока 1 упранлеиия на суммирующий вход счетчика 5 адреса поступает управляющий сигнал для перебора адресов ячеек блока 12 оперативной памяти. На синхровход блока 14 регистров в этом слу 55 чае не поступает тактирующий сигнал с выхода 15 блока 1 управления, После заполнения блока 12 с выхода 7 блока 4 ввода (со второго выхода селектора 39) на соответствующий вход блока 1 управления поступает сигнал окончания загрузки блока 12 оперативной памяти, переводящим устройство в режим ожидания сигнала Пуск"По сигналу Пуск, поступающему на шину 2 блока 1 управления, генератор переходит в режим формирования испьггательных кодов. На синхровход регистра 16 поступает тактирующий сигнал с выхода 15 блока 1 управления, При этом информация со "старших" выходон блока 14 регистров записывается в регистр 16, С выходов регистра 16 через коммутатор 11 информация записывается в очередную ячейку блока 12 оперативной памяти.В каждом такте производится сдвиг. содержимого блока 14 регистров с записью информации с выходов блока 12 оперативной памяти н "младшие разряды блока 14, "Старшие" разряды блока 14 регистров заносятся н регистр 16 с последующим занесением содержимого регистра 16 в ячейку блока 12 оперативной памяти 12 по адресу, установленному в предыдущем такте. После этого осуществляется увеличение содержимого счетчика 5 адреса по +1В режиме загрузки блок 1 управления работает следующим образом.При заполнении блока 14 регистров сдвига по сигналу исходной установки триггер 29 устанавливается в единичное состояние, поддерживая единичный сигнал на выходе 17 блока 1 управления, и открывает элемент И 28, разрешая прохождение синхросигнала с выхода 25 генератора 18 тактовых импульсов на выход 9 блокауправления. По сигналу Исходная установка" триггеры 32 и 30 устанавливаются в нулевое состояние, По синхросигналу с выхода 23 генератора 18 тактовых импульсов (при наличии единичного сигнала с выхода триггера 29, который проходит через элемент ИЛИ 34) на выходе 13 элемента И 24 формируется нулевой сигнал записи,На вход 6 блока 1 управления поступает сигнал окончания загрузки блока 14 регистров с выхода 6 блока 4 ввода. По синхросигналу с выхода 19 генератора 18 тактовых импульсов триггер 32 устананливается в единичное состояние и далее осуществляет1322275 51 О15 20 25 управления. ся загрузка блока 12 оперативной памяти. При этом единичным сигналом свыхода триггера 32, проходящим черезэлемент ИЛИ 33, разрешается прохожде.ние синхросигнала с выхода 25 генератора 18 тактовых импульсов на выход 8 блока 1 управления, Сигнал за-,писи на выходе 13 блока 1 управленияформируется так же, как и при загрузке блока 14 регистров, На выход15 сигнал сдвига содержимого блока14 регистров не выдается,На вход 7 блока 1 управления изблока 4 поступает си нал окончаниязагрузки блока 12 оперативной памяти. По этому сигналу триггеры 29 и32 устанавливаются в нулевое состояние (при наличии синхросигнала навыходе 19 генератора 18 тактовых импульсов). Выход 17 блока 1 находится в нулевом состоянии. По сигналу"Пуск", поступающему на шину 2 блока 1 управления триггер 30 устанавливается в единичное состояние иустройство переходит в режим генерации испытательных наборов.По синхросигналу с выхода 19 генератора 18 тактовых импульсов (приналичии единичного сигнала с выходатриггера 30) через элементы И 28 иИЛИ 36 на выходе 15 блока 1 формируется сигнал сдвига. По синхросигналу с выхода 23 генератора 18 тактовых импульсов (при условии единичного состояния триггера 30) на выходе 13 формируется сигнал записи. Темже единичным сигналом с выхода триггера 30 разрешается прохождение синхросигналов с выхода 25 генератора 8тактовых импульсов на выход блока 1 На входе 6 блока 1 Управления сохраняется единичный сигнал, который поступает на первый вход элемента И 21, На второй вход элемента И 21 поступает синхросигнал с выхода 19 генератора 18 тактовых импульсов, в результате чего на выходе элемента И 2 в каждом такте формируется сигнал, поступающий на входы сбросов триггеров 29 и 32, вследствие чего эти триггеры в режиме генерации сохраняют нулевое состояние,Максимальный период выходной последовательности кодов, формируемых на выходах устройства можно рассчитывать по формуле 35 40 45 50 55 6Тмскс (2 + 1) ( + 1 ) + (2 + 1),где 2 - количество ячеек блока 12коперативной памяти 1 1 1число разрядов каждого нз регистров блока 14 регистров сдвига.Таким образом, изменяя число единиц и их расположение в соответствующих ячейках блока 12 оперативной памяти и разрядах регистров сдвигов блока 14, можно управлять изменением частоты появления единичного сигнала, а также задавать временную диаграмму следования сигналов независимо по всем выходам генератора,Величина периода выходной последовательности может меняться в эависимости от исходного состояния ячеек блока 12 оперативной памяти и регистров сдвига блока 14. Так, если для некоторого 1 (2 + 1; ) - четное число (1 = 1,2п), то, повторив некоторую исходную последовательность в блоке 12 и соответствующем регистре точно ц раз, получим, что период выходной последовательности устройстТмаксва Т формула изобретения 1. Генератор испытательных кодов, содержащий счетчик адреса, коммутатор, блок оперативной памяти, выходной регистр о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей, в него введены блок ввода, блок регистров сдвига, блок управления, первый вход которого является шиной пуска, второй вход которого является шиной установки в исходное состояние и соединен с установочным входом счетчика адреса и с первым входом блока ввода, второй вход которого соединен с первым выходом блока управления, который третьим и четвертым входами подключен к первому и второму выходам блока ввода соответственно, группа выходов кото" рого соединена с первой группой входов коммутатора, выходы которого соединены с информационными входами блока оперативной памяти, адресные входы которого соединены с выходами счетчика адреса, вход которого подключен к второму выходу блока управ-, ления, третий выход которого соединен с входом записи блока оператин7 13222 ной памяти, выходы которого подключены к входам блока регистрон сднига, выходы которого связаны с входами выходного регистра, тактирующийнход которого соединен с синхронходом блока регистров сдвига и с четвертым выходом блока управления, пятын выход которого подключен к управляющему входу коммутатора и входу ус 10 танонки выходного регистра, выходы которого соединены со второй группой входов коммутатора.2. Генератор по п.1, о т л и - ч а ю щ и й с я тем, что, блок управления содержит три триггера, четыре элемента ИЛИ, восемь элементов 15 И, генератор тактовых импульсов, причем первый вход первого элемента Исоединен с перным входом блока управ 20 ления, второй вход которого соединен с входом устанонки н единицу первого триггера, с первым входом первогоэлемента ИЛИ и с входом установки внуль второго триггера, вход установки в единицу которого соединен с выходом первого элемента И, второйвход которого соединен с инверснымвыходом первого триггера, вход уста 25 нонки в нуль которого соединен с вторым входом первого элемента ИЛИ и З 0 с выходом второго элемента И, первыйвход которого соединен с первыми входами третьего и четвертого элементов И и с первым выходом генератора тактовых импульсов, второй выход которо го соединен с первым входом пятогоэлемента И, второй вход которого свяэан с выходом второго элемента ИЛИ,первый вход которого связан с первыгера, который соединен с пятью выходом блока управления, второй вход шестого элемента И связан с иннерсным выходом третьего триггера, вход установки в единицу которого соединен ми входами шестого и седьмого элемента И и с прямым выходом первого тригс выходом третьего элемента И, нторой вход которого соединен с третьим входом блока управления, четвертый вход которого соединен с вторым входом второго элемента И, третий вход шестого элемента И соединен с вторым входом седьмого элемента И, третьим выходом тактового генератора и первым входом восьмого элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с прямым выходом второго триггера, вторым нходом второго элемента ИЛИ и вторым входом четвертого элемента И, выход которого и выход шестого элемента И соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с четвертым выходом блока управления, выход первого элемента ИЛИ сое- динен с входом установки в нуль третьего триггера, прямой выход которого соединен с вторым входом третьего элемента ИЛИ, первый выход блока управления соединен с выходом седьмого элемента И, второй выход блока управления соединен с выходом восьмого элемента И третий выход блока управления соединен с выходом пятого элемента И.3. Генератор по п.1, о т л и - ч а ю щ и й с я тем, что, блок ввода содержит счетчик, блок постоянной памяти, селектор, причем ныходы разрядов счетчика соединены соответствующим образом с адресныки входами блока постоянной памяти и входами селектора, первый и второй выходы которого являются первым и вторым выходами блока внода, выходы блока постоянной памяти являются группой выходов блока ввода, первый вход которого соединен со входом установки н нуль счетчика, тактовый вход которого является вторым входом блока вво- дае3322275 Составитель Ю,СибиряТехред Л.Олейник ектор А,Ильин Редактор П.Гереши Заказ 2865/ сное Производственно-полиграфическое предприятие, г,ужгород, ул,Прое НИИПИ Го по делам 13035, М Тираж 672 Пдарственного комитета СССРизобретений и открытийква, Ж, Раушская наб., д.4/5

СмотретьЗаявка

3977747, 19.11.1985

КИЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

РОМАНКЕВИЧ АЛЕКСЕЙ МИХАЙЛОВИЧ, ГРОЛЬ ВЛАДИМИР ВАСИЛЬЕВИЧ, КАРАЧУН ЛЕОНИД ФЕДОРОВИЧ, ЛУПАНОВА РИММА ИВАНОВНА, НИШТ ЛАРИСА ИВАНОВНА

МПК / Метки

Метки: генератор, испытательных, кодов

Опубликовано: 07.07.1987

Код ссылки

<a href="https://patents.su/6-1322275-generator-ispytatelnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор испытательных кодов</a>

Предыдущий патент: Генератор равномерно распределенных случайных величин

Следующий патент: Датчик случайных чисел

Случайный патент: Устройство для управления шаговым электродвигателем