Система передачи дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1262741

Авторы: Вайс, Кордонский, Котиков, Мягков, Черный

Текст

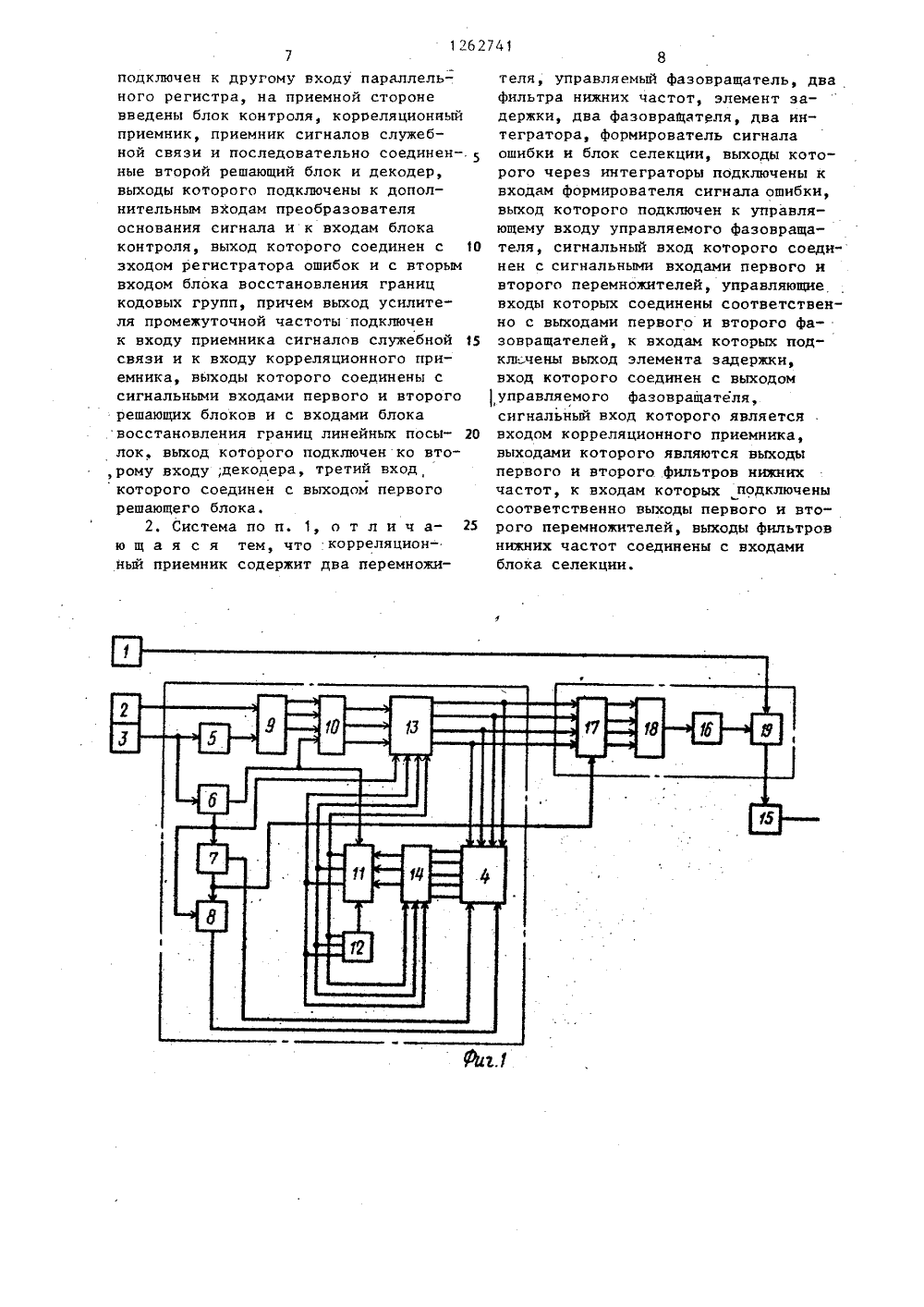

(51) 4 Н 04 РЕТЕНИЯ ЛЬСТВ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОПИСАНИЕН АВТОРСКОМУ СВИ(56) Авторское свидетельство СССРУ 818026, кл. Н 04 Ь 5/00, 1976.(57) Изобретение относится к радиотехнике. Увеличивается объем передаваемой информации. Система на передающей стороне содержит источник дискретной информации, блок синхронизации, формирователь (Ф) синхросигнала кодовых групп,Ф синхросигналалинейных посылок, 1-й сумматор, преобразователь основания кода. Вновьвведены блок стробирования, источник сигналов служебной связи, 2-йсумматор, фильтр верхних частот,блок сдвига, частотный модулятор,последовательный регистр, инвертор,два счетчика, блок памяти, параллельный регистр и блок запрета. На приемной стороне система содержит приемник (П) дискретной информации, Ф двоичного сигнала, блок восстановле-, ния границ информационных посылок, УПЧ, преобразователь основания сигнала, 1-й решающий блок, блок восстановления границ линейных посылок, блок восстановления границ кодовых групп, регистратор ошибок, состоящий из счетчика и блока индикации. Вновь введены блок контроля, корреляционный П, состоящий из двух перемножителей, управляемого фазовращателя, Ф сигнала ошибки, элемента задержки, а двух интеграторов, двух фильтров нижних частот, двух фазовращателей и блока селекции,П сигналов служебной связи, и последовательно соединенные 2-й решающий блок и декодер., Преобразование двоичного основания в четвертичное осуществляется в соответствии с таблицей, приведенной в описании изобретения. 1 э.п. ф-лы. 2 ил., 1 табл.Изобретение относится к радиотехнике и может использоваться для передачи дискретной информации,Цель изобретения - увеличение обьема передаваемой информации.На фиг. 1 представлена структурная электрическая схема передающей стороны системы передачи дискретной инФормации; на фиг, 2 - структурная электрическая схема приемной стороны системы передачи дискретной информации.Система передачи дискретной информации содержит на передающей стороне (Фиг. 1) источник 1 сигналовслужебной связи, источник 2 дискретной информации, блок 3 синхронизации,первый счетчик 4, инвертор 5, формирователь б синхросигнала кодовыхгрупп, формирователь 7 синхросигналалинейных посылок, блок 8 сдвига, последовательный регистр 9, параллельный регистр 10, блок 11 памяти, блок12 запрета, преобразователь 13 основания кода, второй счетчик 14,частотный модулятор 15, фильтр 16верхних частот, блок 17 стробирования, первый и второй сумматоры 18и 19, а на приемной стороне содержит (фиг. 2) приемник 20 сигналовслужебной связи, приемник 21 дискретной информации, формирователь 22двоичного сигнала, блок 23 восстановления границ информационных посылок,усилитель 24 промежуточной частоты,корреляционный приемник 25, состоящий из двух перемножителей 26 и 27,управляемого фазовращателя 28, формирователя 29 сигнала ошибки, элементазадержки 30, двух интеграторов 31 и32, двух фильтров 33 и 34 нижнихчастот, двух фазовращателей 35 и 36и блока 3 селекции, преобразователь38 основания сигнала, первый и второй решающие блоки 39 и 40, блок 41восстановления границ линейных посылок, декодер 42, блок 43 восстановления границ кодовых групп, блок 44контроля, регистратор 45 ошибок,состоящий из счетчика. 46 и блока 47индикации,Система передачи дискретной информации работает следующим образом.Преобразование двоичного основания в четвертичное осуществляется в соответствии со следующей таблицей.13 (+2)21(0) 13 (+2)21(0) 03 (0) 21(0) 31 (+2) 31 (+2) 10(-4) 01(-4) 101 100 22(+2) 22(+2) В таблице рядом с каждой четвертичной кодовой группой указано значение цифровой суммы в данной группе,вычисленное как алгебраическая суммаамплитуд импульсов в кодовой группепри условии, что символам 0,1,2,3кода поставлено в соответствие нормированное напряжение -3, -1, +1, +3,Над каждой из трех колонок кодовых групп указано значение цифровойсуммы на границе кодовых групп, хранящейся в блоке 11 памяти на передающей стороне (фиг. 1) к моменту поступления следующей двоичной группы,состоящей из трех символов, с выходаисточника 2 дискретной информации,синхронизируемого блоком 3 синхронизации, и записываемой в последовательный регистр 9 инверсной двоичнойтактовой частотой с выхода инвертора 5. Три символа, записанные в пос ледовательном регистре 9, переписываются инверсным кодовым синхросигналом с второго выхода Формирователя6 синхросигнала кодовых групп в па"раллельный регистр 10 и хранятся тамв течение времени, равного трем дво-.ичным тактовым интервалам. На вторуюгруппу входоь преобразователя 13 основания кода с выхода блока 11 памяти поступает значение предшествующейцифровой суммы на границе кодовыхгрупп, представленное в двоичномвиде, а на первый вход - кодовыйсинхросигнал с первого выхода Форми12 Ь 27 1 рователя 6, который также подается через Формирователь 7 и блок 8 на первый счетчик 4. Причем нуль в кодовом синхросигнале соответствует первому четвертичному символу на выходе преобразователя 13, а единица - второму, и четыре его выхода соответствуют шинам четырех символов О, 1, 2 и 3. Так,если ЦС = -2 (соответствует сигналу 100 на выходе блока 11 10 памяти), то в соответствии с таблицей приходящая двоичная группа, например 011, кодируется группой из левой колонки таблицы в данном случае 32, которая на выходе первого 15 сумматора 18 представляется двумя импульсами с амплитудами +3 +1. Подсчитанная в первом счетчике 4 цифровая сумма (для группы 32 цифровая сумма равна +4) складывается во вто ром счетчике 14 с предыдущим значением (в нашем примере - 2 +4) и результата +2 (двоичное представление 001) записывается в блок 11 па-, мяти (в случае разрешения с блока 12 25 запрета инверсным кодовым синхросигналом с второго выхода формирователя 6 синхросигнала кодовых групп). Следукицая двоичная группа, например 001, должна кодироваться группой из правой колонки таблицы (в данном случае 02 с цифровой суммой в кодовой группе - 2) и т.д. Таким образам при поступлении сигнала с преобразователя 13 на выходе первого сумматора 18 полу 35 чают четырехуровневый балансный сигнал, прошедший через блок 17 стробирования, в энергетическом спектре которого отсутствуют постоянная составляющая, а мошность низкочастотных составляющих незначительна, Поэтому четырехуровневый сигнал на выходе фильтра 16 верхних частот практически не искажается, а мощность помех в канале служебной связи на выходе.45 второго сумматора 19 пренебрежимо мала. Суммарный сигнал с выхода второго сумматора 19 по команде с источчика 1 поступает на вход частотного модулятора 15 и далее в радиотракт.50На приемной стороне (фиг. 2 э) сигнал с выхода усилителя 24 промежуточ.ной частоты поступает на управляемый фазовращатель 28 корреляционного приемника 25, создающий начальный сдвчг 55 фаз между сигналами, приходящими на первый и второй перемножители 26 и 27. После перемножения и интегриро 4в ания в обоих Фильтрах 33 и 34 нижнихчастот на их выходах Формируютсядвоичные сигналы,Выходы фильтров 33 и 34 нижнихчастот подключены к входам блока 37селекции, который вьделяет напряжения квадратурных составляющих, .находящихся в первом или третьем квадрантах сигнала Фазоразностной модуляции (ФРМ),Выбор первого или третьего квадранта определяется тем, что в этих квадрантах знаки квадратурных составляющих одинаковы, что позволит однозначно определить величину и знак сигнала ошибки. Выходы блока 37 селекции соединены с входами интегратора 31 и 32, которые Формируют напряжения, подаваемые на формирователь 29, пропорциональные средним значениям напряжений квадратурных состав-" ляющих при передаче сигнала ФРМ в первом или третьем квадрантах.Сигнал ошибки с выхода формирователя 29 подается на вход управляемого Фазовращателя 28, который компенсирует сдвиг фаз, возникающий между поступающими на первый и второй пере- множители б и 27 напряжениями и, тем самым, исключает уменьшение помехоустойчивости приема вследствие действия нестабильности частоты несущей, Сигналы управления на пере- множители 26 и 27 поступают через эле-. мент 30 задержки и Фазовращатели 35 и 36. С выходов фильтров 33 и 34 нижних частот сигналы поступают соответственно на первые входы решающих блоков, на вторые входы которых поступает тактовый синхросигнал, вьделенный из сигналов с выходов фильтров 33 и 34 нижних частот в блоке 41 восстановления границ линейных посылок. Двоичные последовательности с выходов первого и второго решающих блоков 39 и 40 преобразуются в декодере 42 в четыре двоичных последовательности, соответствующие символам О, 1, 2 и 3 четвертичного основания, которые поступают на соответствующие входы преобразователя 38 основания кода и блока 44 контроля. С выхода блока 44 сигналы, пройдя блоки 43 и 23, пос- тупают на другие входы преобразователя 38. На выходе преобразователя 38 формируются два цифровых потока, полученных в результате обратного преобразования четвертичных символов вдвоичные в соответствии с таблицей.Эти два цифровых потока, пройдя формирователь 22, поступают в приемник21. Нормальная работа преобразователя 38 основания сигнала обеспечивается двумя импульсными последовательностями, следующими на границах кодовых групп и на границах информационных посылок, Первая из последовательностей создается в блоке 43 10Восстановления границ кодовых групп,а вторая - в блоке 23 восстановленияграниц информационных посылок. Причем сигналы служебной связи с выхода усилителя 24 поступают в приемник 1520 сигналов служебной связи,Под нарушениями правил четвертичного кодирования в коде ЗВ 20 (см, таблицу) понимаются превышения граничных значений цифровой суммы (ЦС = +2 и ЦС = -2), которые возникают при наличии ошибочных символов в принимаемом сигнале. При этом все единичные ошибки в принимаемом сигнале приводят к превышению гранич 1 ных значений цифровой суммы. Для контроля и регИстрации нарушений граничных значений служит регистратор 45. При этом подсчет превышенийЗО .граничных значений цифровой суммы в счетчике 46 и индикация в блоке 47 позволяет контролировать все ошибки, возникающие в принимаемом сигнале,еФормула из обре тения1. Система передачи дИскретной информации, содержащая на передающей стороне первый сумматор, источ-,40 ник дискретной информации и блок синхронизации, выход которого подключен к входу формирователя синхросигнала кодовых групп, первый выход которого подключен к входу формирователя син-хросигнала линейных посылок и к одному входу преобразователя основания кода, а на приемной стороне - усилитель промежуточной частоты, регистратор ошибок и блок восстановления границ линейных посылок, выход которого подключен к управляющему входу первого решающего блока и первому входу блока восстановления границ кодовых групп, выход которого соединен с входом блока восстановления границ информационных посылок и с одним входом преобразователя основания сигнала, другой вход и выходы которого саепинены соответственно с выходом блока Восстановления границ информационных посылок и входами формирователя двоичного сигнала, выход которого подключен к входу приемника дискретной инФормации, а т л и ч аю щ а я с я тем, что, с целью увеличения объема передаваемой информации,в ней на передающей стороне введены блок стробиравания, источник сигналов служебной связи, второй сумматор, фильтр верхних частот, блок сдвига, частотный модулятор, последовательный регистр, инвертор, два счетчика, блок памяти, параллельный регистр и блок запрета, выход которого падкхпочен к одному Входу блока памяти, другой вход и выходы которого саедииены соответственно с вторым выхоцом Формирователя синхросигнала кодовых групп и с другими входами преобразователя основания кода, выходы которого подключены к одним входам первого счетчика, выходы которого соединены с одними входами второго. счетчика, и к одним входам блока стробирования, выходы которого соединены с входами первого сумматора, выход которого через фильтр верхних частот подключен к первому входу второго сумматора, второй вход и выход которога соединены соответственно с выходом источника сигналов служебной связи и входом частотного модулятора,при этом, выход источника дискретной информации подключен к одному входу последовательного регистра, другой вход и выходы которого соединены сответственно с выходом инвертора, к .Входу которого подключен выход блока синхронизации, и с одними входами параллельного регистра, выходы кото" рого подключены к соответствуюшим входам преобразователя основания кода, выходы блока памяти подключены к входам блока запрета и к другимвходам второго счетчика, выходы каторогс соединены с соответствующими входами блока памяти, а соответствующие входы первого счетчика соединены с выходом блока сдвига и с вторым выходом формирователя синхросигнала линейных посылок, первый выход которого подключен к другому входу блока стробирования и к первому входу блока сдвига, Второй вход которого соединен с перВым выходом формирователя синхросигнала кодовых групп, второй выход которого1262741 7подключен к другому входу параллельного регистра, на приемной стороне введены блок контроля, корреляционный приемник, приемник сигналов служебной связи и последовательно соединен-. ные второй решающий блок и декодер, выходы которого подключены к дополнительным входам преобразователя основания сигнала и к входам блока контроля, выход которого соединен с зходом регистратора ошибок и с вторым входом блока восстановления границ кодовых групп, причем выход усилителя промежуточной частоты подключен к входу приемника сигналов служебной связи и к входу корреляционного приемника, выходы которого соединены с сигнальными входами первого и второго решающих блоков и с входами блока восстановления границ линейных посылок, выход которого подключен ко вто,рому входу;декодера, третий вход, которого соединен с выходом первого решающего блока.2. Система по и, 1, о т л и ч аю щ а я с я тем, что корреляционный приемник содержит два перемножителя, управляемый фазовращатель, двафильтра нижних частот, элемент задержки, два фазовращателя, два интегратора, формирователь сигналаошибки и блок селекции, выходы которого через интеграторы подключены квходам формирователя сигнала ошибки,выход которого подключен к управляющему входу управляемого фазовраща 10 теля, сигнальный вход которого соеди"нен с сигнальными входами первого ивторого перемножителей, управляющиевходы которых соединены соответственно с выходами первого и второго фа 15 зовращателей, к входам которых подключены выход элемента задержки,вход которого соединен с выходомуправляемого фазовращателя,сигнальный вход которого является20 входом корреляционного приемника,выходами которого являются выходыпервого и второго фильтров нижнихчастот, к входам которых подключенысоответственно выходы первого и вто 25 рого перемножителей, выходы фильтровнижних частот соединены с входамиблока селекции.1262741 Составитель А. МоскевичТехред В.Кадар дактор А. Сабо орректор Т. Ко каз 5447 624 Т дписн ВНИИПИ Государственного комитета СССР по делам изобретений и открьггий 3035, Москва Ж, Раушская наб , д. 4/5

СмотретьЗаявка

3877936, 01.04.1985

ПРЕДПРИЯТИЕ ПЯ Р-6609

КОТИКОВ ИГОРЬ МИХАЙЛОВИЧ, КОРДОНСКИЙ БОРИС ШЛЕМОВИЧ, ВАЙС ЭММАНУИЛ АРОНОВИЧ, ЧЕРНЫЙ ВЛАДИМИР ЭМИЛЬЕВИЧ, МЯГКОВ ИГОРЬ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H04L 5/00

Метки: дискретной, информации, передачи

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/6-1262741-sistema-peredachi-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи дискретной информации</a>

Предыдущий патент: Многоканальная система передачи и приема информации

Следующий патент: Цифровой формирователь синусоидальных колебаний переменной частоты

Случайный патент: Способ флотации угля и графита