Система сбора и обработки информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

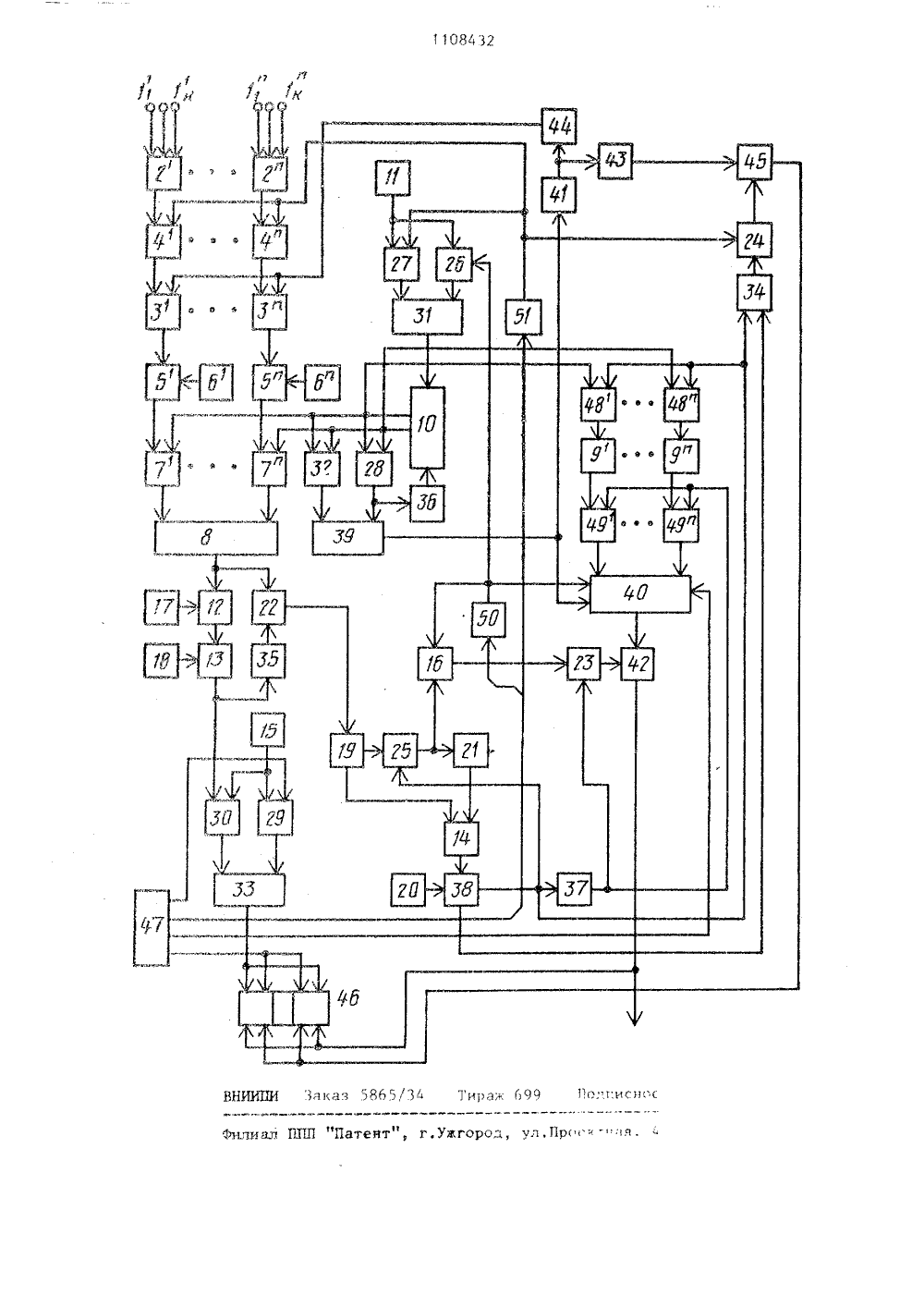

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН И 9) (И в С 06 Р 3 04 САНИЕ ИЗОБРЕТЕНИЯ ИДЕТЕЛЬСТВУ АВТОРСКОМ ммутат ответст ев,тво ССС981.о СССР5.04.83 АБОТ перво четт того элеог че входаментов И ра соа И,сдв триг леме выход первоодом первог динен с в третьим в егистра оследов ом первог оединеннь ель а и чере о первый коммутат ст ти, выходн с входам ом пе т ера соеди торого т, второгооммутатора,элементов запрет элемента И и тре о к удАРстВенный кОмитет сссДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(прототип),(54)(57) СИСТЕМА СБОРА И ОБР КИИНФОР 1"1 А 11 ИИ, содержащля генератор,выход которого через первый и второйэлементы И соединены с входамиго элемента ИЛИ, регистр с вигл,выходы которого соединены с входамивторого элемецтл ИЛИ и третьего элемента И, выход которого соединен свходом первого элемента задержки,входы устройства соединены с входамикоммутаторов первой группы, первыйрегистр адреса, вьход которого соедицен с входом первой памяти, четвертыйэлемент И, выход которого соединенс входом третьего элемента ИЛИ, счик, о т л и ч л ю щ л я с я тем,ч о, с целью повыщеция коэффициентаиспользования оборудования, достоверности и оперлтицости коцтроля, в неевведены дв плмятц, блок сравнения,регистр ддресл, блок регистрации,двл триг ерл, схема сравнения, тривычитлтеля, шесть регистров, четырекоммутатора, элем цт задержки, группа элем втоц злпрс тл, группа элементов 11 ЛИ, группл оц тчикв, группакоммутдторов, группа элемьцтов И,группа б оков зл мц ц гон И, блок элемецтов 11 Л 11, гр;ццл р гигтров, группа умножителей, таймер, элемент ИЛИ, элемент И, элемент НЕ, причем выходы ко оров первой группы через совующие элементы запрета группы соединены с входами соответствующих элементов ИЛИ группы, выходь 1 кото рых через соответствующие умножители группы соединены с входами соответ ствующих блоков элементов И группы, выходы которых через блок элементов ИЛИ соединены с входами первых коммутатора и вычитателя, выход которого через второй вычитатель соединен с входами элемента НЕ и пятого элемента И, выход которого через третий элемент ИЛИ соединен с входом блока регистрации, другие входы которого соединены соответственно с первым управляющим входом системы,и выходами первой памяти и блока сравнения, второй управляющий вход системы соединен с входом четвертого элемента И, третий управляющий вход системы соединен с первым входом первого регистра адреса, второй вход которого и вход второго регистра адреса через счетчик соединены с выходами второго элемента ИЛИ и третьего элемента И, четвертый управляющий вход системы соединен с входами первого и второго триггеров, выход таймера соединен110 йч 32 Выход второго регистра адреса черезвтору(В и гр(.тью памяти соединен соответстгзенно входами блока сравненияи ззментов ИЛИ группы, Выходь регистров группы соединены с Входами соответствунших умножителей группы,выходы регистра сдвига соединены свходами соответствующих локон элементов И группы и элементов И группы, вьгходы которых через соответствующие счетчики группы соединены свходами соотгзетствующих коммутатороввторой группы, выходы которых соедине(зы с группой гзходов первого резистра адреса, выходы второго и третьегорегистров соединены соответственно с входами первого и второго Вычитателей, выход элемента Е через соеДИНЕНГПс(Е ИОСЛЕДОВатЕЛЬНО ПЕРВЫЙ КОМ- мутатор и четвертый регистр - с вхоИзобретение относится к области Вычислительной техники и может быть использовано для связи блока обработ. ки информации ЭВс) с периферийным оборудснанием наблюдением состояния ныбрянпь(х гругзп Датчиков, в частности с оборудованием контроля состояния тепловых сетей.Известно устрОйство для Ввода ин- формации, содержащее регистр сдвига, группу регистров, дна элемента ИЛИ, двя регистра, дпа элемента И, два элемента задержки 1"НЕДОСТАТКОМ Дс(ННОГО Ус "Г 0(гствсэ является отсутствие возможности работы с группой различных датчиков, используемых при контро.пе состояния тепловых сетей, формирования и предварительной обработки указанной информации.Система сбора и обработки информации, содержащая генератор, выход которого через первый и второй э.цементы И соединены с входами первого элемента ИЛИ, регистр сдвига, выходы которого ссоединены с входами второго элемента ИЛИ и третьего элемента И, выход которого соединен с входом первого эг(ементя задержки, входы устройства соединены ( входами коммутаторов пер(зой гр лпы, првьгй регистр ядредами третьего вычитателя и четвертого коммутатора, выходы пятого регистра и третьего вычитателя соединены с Входами схемы сравнения, первый Выход которой соединен с входами второго элемента задержки, четвертогоэлемента ИЛИ, элементов И группы, ичерез четвертый коммутатор с входамипервого и шестого регистров, второйвыход схемы сравнения через соединенные последовательно четвертый элемент ИЛИ и третий коммутатор соединен с входом блока сравнения, выходвторого элемента задержки соединен с входами второго коммутатора и комму. тяторов группы, выход шестого регистра соединен с вхопом третьего нычитателя, выходы первого элемента ИЛИ и первого элемента задержки соединены с входами регистра сдвига,ся, вь(ход которого соединен с входомпервой памяти, четвертый элемент И,выход которого соединен с входомтэеть(ГО элемента И.И,счетк позво 5 ля(.т проводить избирательный опросдятчг(ко( .2 ,Однако система не учитывает специфику зп(формации от отдельных дат -чиков отдел Вых групп датчиков),не производит ра;зделение существенной информации, что значительноВлияет на Обсьсм требуемой памятиили достоверность собранной информации, не позволяет обеспечить постоян 15 ное няблюден (е за состоянием выбранных групп датчиков. Кроме того, известная систем;не может обеспечить КОНТРОЛЬ ОПЕРсстОРа За СОСТОЯНИЕМ Всей совокупности датчиков и опера тинный Вывод данных на индикацию ипечать, зафиксировать аварийну(о ситуацию и обеспечить надежность за счет самоконтроля системы. Цель изобретения - повышение коэффициента использования оборудования, достоверности и оперативности контроля.1 оставленная цель достигается тем, что В систему сбора и;бработки инфорл(г(ци, содржа(цу(с георатор,выход которого через первый и второй элементы И соединены с входами перво. го элемента ИЛИ, регистр сдвига, выходы которого соединены с входами второго элемента ИЛИ и третьего элемента И, выход которого соединен с входом первого элемента задержки, входы устройства соединены с входами коммутаторов первой группы, первый регистр адреса, выход которого соединен с входом первой памяти, четвертый элемент И, выход которого соединен с входом третьего элемента ИЛИ, счетчик, введены две памяти, блок сравнения, регистр адреса, блок регистрации, два триггера, схема сравнения, три вычитателя, шесть регистров, четыре коммутатора, элемент задержки, группа элементов запрета, группа элементов ИЛИ, группа счетчиков, группа коммутаторов, группа элементов И, группа блоков элементов И, блок элементов ИЛИ, группа регистров, группа умножителей, таймер, элемент ИЛИ, элемент И, элемент НЕ, причем выходы коммутаторов первой группы через соответствующие элементы запрета группы соединены с входами соответствующих элементов ИЛИ группы, выходы которых через соответствующие умно- жители группы соединецы с входами соответствующих блоков элементов И группы, выходы которых через блок элементов ИЛИ соединены с входами первых коммутаторов и вычитателя, выход которого через второй вычитатель соединен с входами элемента НЕ и пятого элемента И, выход которого через третий элемент ИЛИ соединен с входом блока регистрации, другие входы которого соединены соответственно с первым управляющим входом системы, и выходами первой памяти и блока сравнения, второй управляющий вход системы соединен с входом четвертого элемента И, третий управляющий вход системы соединен с первым входом первого регистра адреса, второй вход которого и вход второго регистра адр.са через счетчик соединены с выходами второго элемента ИЛИ и третьего элемента И, четвертый управляющий вход системы соединен с входами первого и второго триггеров, выход таймера соединен с входами четвертого и пятого элементов И, выход первого триггера соединен с входом первого элемента И, третьим входом первого регистра сдвига и через сое диненные последовательно первый регистр и второй коммутатор с входомпервой памяти, выход второго триггера соединен с входами элементов эапрета группы, второго элемента Ии третьего коммутатора, выход второмы сравнения через соединенные последовательно четвертый элемент ИЛИи третий коммутатор соединен с входом блока сравнеция, выход второгоэлемента задержки соединен с входамивторого коммутатора и коммутаторовгруппы, выход шестого регистра соедицен с входом третьего вычитателя,выходы первого элемента ИЛИ и первого элемента задержки соединены с входами регистра сдвига,40 45 На чертеже приведена структурная схема предложенной системы.На чертеже указаны выходы датчик ков 11 к1(1, , 11 1 л, коммутаторы 22", элементы ИЛИ 33" группы, элементы запрета 44 группы, умножители 55 группы, регистры коэффициентов 6 6" группы, блоки элементов И 7 7 группы, блок элементов ИЛИ 8, счетчики 9 9 группы, регистр сдвига 10, гецераго регистра адреса через вторую итретью памяти соединен соответственно с входами блока сравнения и эле Оментов ИЛИ группы, выходы регистровгруппы соединены с входами соответствующих умножителей группы, выходы регистра сдвига соединены с входамисоответствующих блоков элементов И 15группы и элементов И группы, выходыкоторых через соответствующие счетчики группы соединены с входами соответствующих коммутаторов второй группы, выходы которых соединены с группой входов первого регистра адреса,выходы второго и третьего регистровсоединены соответственно с входамипервого и второго вычитателей, выходэлемента НЕ через соединенные последовательцо первый коммутатор и четвертый регистр - с входами третьеговычитателя и четвертого коммутатора,выходы пятого регистра и третьеговычитателя соединены с входами схемы ЗО сравнения, первый выход которогосое динен с входами второго элементазадержки, четвертого элемента ИЛИ,элементов И группы, и через четвертый коммутатор с входами первого и 35 шестого регистров, второй выход схе 08432тОр таКГОВЫХ ГХ 1 Гдттс11 11, ГЫЧИтател 12-.14 таймер 15, регистр 16 данных, регистр 17 Гп)рог, регистр 18 порога, регистр 19 ткуцего значения, регистр 20 допустимых отклоне ций буферный регцс"г 1) 2 1, коммутаторы 22-25, ээемецты И 26-30, элеметы ИЛИ 31-31, злемец- ПЕ 35, элемты 36-37 задержки, схема 38 сравнеция, счетчик 39 номера зоны, регистры 40,41 адреса, память 42 даццых, память 43 отклонений, память 44 эталоццых сигцалов, блок 45 сравнецтя, блок 46 регистрации, пульт 47 управления, элементы И 488 15и группы, коммутаторы 4949 группы, триггер 50 упрлвлеция, триггер 51 контролЯ (блок стцхроцРзацРГи тлкти - руюптгл работ) Отдслтных узэтов, уст;Потки тл)иггеров ре т 1 стров счет - л 0 ЧИГ(013 И Т, Д, ив ПОЕЛ З ЛГПЯ) Систем работает с,пт,пуощим образом.(10 сигцл 11 ь ОтеРГтОРЯ с пУлтгглт 47выбрлется режим рлботы системт. Пред;.,пОлгастс:5 Пца рс.ж 1 мл рябогырабочий регистре с "э тгс етт 11 Гцст управс)ци 51сдвигается импульсами от гс цс.ратора 11, Гтоцлваемым 1 трез элеГлЕНТ И 1 И 31. 1 ЛКИ: Обрл;том,;тро 1 ЭОДИТСЯ ПОДК 11 ОЧЕНИЕ ГллГтя.:тоц;ЯТттИКОВвыбранной грутпы к блоку эле. и.цтов ИЛПИ 8. С выходя блока 8 сцгцл:ГПОСтуПЛЕт В КОММутатср 22 ц ц,тИТЛте.тп: 12, гд сравнивтся со зцлчетп;ем р Гис трл пот)ОГя 1 7, Поэъ ц ил яряПИця Гтт)стПЛЕ 1 В ВЬ 111 ЧГТСПГ. 1 ) 50 И СЛМОКОтТ 1 то,т 15 Г лВ рабочем рлж 1 ме т;ттггер управ;тс.- ция 50 устлцлвэивлется в е,"ГРцттОе сост 051 цие л трГггер онтрол 5 т 51 Ос 10 тлется ц исходном, СГалы от длтчилКОв 1остьплот чсрз коммьт 3 тторы2 т, ээсменть злпрс.тл(ОтКРГГЫЕ, ГС)СКОЛЬКУ СИГЦатт с триггера 51 отсутстцус т) и элементы ИЛП 33 1.л гходы млсштлбиру мых умцожггелс й 55 . Вест. ллссв датчиков разбит и т) выделецньп( групп. 1 т кл)эло 1 группе обГьед цены датчИКИ ОППОГО СГЪуцК 11(гцгт)П цОГ О 1 ЛЗПЛ 10 ЧЕНИЯ (ТСМПЕРЛТУГ)Ы) ПтЧ ГС.515 И 7,Д, ) ДЛ 51 КЛЖД 011 Г), ППЬ УСТЛГГ 11)т:ЛЕТСЯ свой масштабный коэффицисцт, записанцый в регистрах 66 , Посте мас -гг 1 шт;бироэл 1 я ц уможите,я 55.сигналы пос:упяют нл входы блоков элементов И 77 , которы управляются ситилами от рс гцс:гря 10, Р) где сравнивается со значением регистра порога 18, В случае превышения поступившим сигналом значения комбинированного порога выдается сигнал аварийной сигнализации, и время поступления аварийной ситуации Фиксируется таймером 15 через элемент И 30 и элемент ИЛИ 33 в блоке 46, В этом случае анализ поступившей информации по рабочему алгоритму це производится, так как коммутатор 22 закрыт сигналом от едицичцого плеса знакового разряда вычитателя 13 через элемент НЕ 35, Злемецт НЕ 35 вклоченв схему для отражения логического взаимодействия узлов при обработке информации, В принципе может бьть использован сигнал с нулевого плеча закового разряда вычцтателя 13.По сигналу аварийной ситуации оператор выдает сигнал сброса триг - гера 50 и производится ряд мероприятий по локализации и устранс нию аваР 1 й,Если значение поступищего сигнала ц превьппяет значения установленного порога, то производится дл.пьцейший анализ гоступившей ицформлции.При этом информация через коммутатор 22 по разрешающему сигналу от .элемента НЕ 35 подается в регистр 19 и далее в вычитатель 14, где проРзводится ее сравнение с содержимым регистра 2 1. Результат, полученный от вычитлтеля 14, поступает в с;(ему срлвцция 38, которая определяет суЩЕСтЭЕГПОСтЬ ПОСТУГГПЯШЕлй ИНФОРМЯЦИИ. ЭТО Осу пествп 51(этся следующим обрязОМЕсли разность, полу ецнля тэ втитятеле 14, превьппяет значение допустимого отклоения, записанного в регистре 20, то данная информация считается существеиой и из регистр 19 через коммутатор 25 перегтисывлется и регистр 21. Рновь поступлюпяя информация сравнивается уже с этим новым значением. Таким образом, проводится выборка и фиксация только существенцой ицформяции, которая записывлс.тся в регистр данных - 16 памяти 4. тДРЕС ЯЧЕИКИ ПЛМЯтИ, ЬУЦЯ Г 7 ЕГУЕ ЗЛПГГСтВЛТЬ ИНФОРЬГЛГПКГ, ФОРМИРУЕТСЯ следующим образ)ы.Сигналы от репи тра сдвГгт 10 через элемент ИЛИ 32 пос 7 )5 як т тт счет - чик 39, где Формцруется цо ир стц;, ОТВОД 1 ПОЙ 5 ЛЯ Каждо 7 КЛИЛ ( и- деленной группы ллтчкстц). Номеп ячей -ки в зоцс Формируется с. помощью счетчиков 99 , куда поступает единичная информация каждый раз при поступлении существенной выборки по данному каналу. Это осуществляется при поступлении сигналов ца один элемент И 48 48от соответствусщего выхода регистра сдвига 10 и схемы сравнения 38.Код от выбранного счсзтчика 9 9 поступает в регистр адреса 40 че ирез коммутаторы 4949 одновременно с поступлением содержимого регистра 16 на цнформаццоццый вход памяти 42 через коммутатор 23, но после некоторой задержки, осуществляемой элементом задержки 37. Это необходимо для того, чтобы устранить влияние переходных процессов и исклочить запись неверной или старой информации.После прохождения сигнала по всему регистру сдвига 10, т,е, после Формирования номеров всех зон счетчиком 39, срабатывает элемент И 28 и устанавливает счетчик 39 в нулевое состояние. После некоторой пау:ы, формируемоц элементом задержки 36, достаточной для срабатывация всехпредусмотреццых В данном шаге операции средств, в единичном разряде регистра 10 вновь устацавлцвается единица ц цикл работы повторяется, Для считывания ццформации из любой выбранной ячейки памяти 42 оператор может набрать код адреса этой ячейки и выдать ее содержимое ца выходсистемы, цл блок 4 Г,Периодически цлц по специальномусигналу оператора на блоке через элементы И 29 ц ИИ 3 может Фиксироваться выбранная инФормация и время,Прц работе ВО Втором режиме включается триггер 51, а триггер 50 сбрасывается. Единичное состояие триггера 51 разрешает работу регистра адреса 41, элемента И 27 ц запрещаетИработу элементов запрета 4Импупьсы с генератора 11 черезэлемент И 27 ц э.пемс цт ИЛИ 31 поступают в регистр сдвига 10 ц управляют сдвигом едиццс, в цем. Одновременно сигналы с Выходом регистра 10через лемс цт 1: 32 поступлнт цавход счетчика 39, который через регистр 41 уцрлп пег выдачей эталонныхсигца.пов цп,мяти .тазцццых сцгца .Гоез 4 4 цсз цхсц 3цементов П 310 15 20 25 30 35 40 45 50 55 3 . Эти сигналы через элементы ИЛИ 33, умножители 55 , блоки элементов И 77 и блок элемецитов ИЛИ 8 поступают на коммутатор 22, в сумматор и далее . вычитатель 13. С выхода сумматора через элемент НЕ 35 разрешается работа коммутатора 22 (эталонный сигнал выбирается меньше аварийного) и информация обрабатывается в вычитателе 14 и в схеме сравнения 38 с помощью регистров 19, 21, 20, коммутатора 25 по описанному алгоритму, В память 42 результаты обработки не заносятся, поскольку работа регистров 16, 40 запрещена триггером 50.С выхода вычитателя 14 значение отклонения поступает в коммутатор 24, на который поступают разрешающие сигналы от триггера 51 и через элемент ИЛИ 34 с выходов схемы сравне-. ния 38. Элемент ИЛИ 34 введен для соблюдения общей логики работы системы, Таким образом, коммутатор 24 передает значение полученного отклонения на блок сравнения 45, куда также поступают значения заранее известных расчетных отклоцений из памяти отклонения 43. Результаты сравнения поступают в блок 46 и контролируются оператором. При появлении существенного расхождения рассчитаццого и полученного отклонений о;. может остановить (и повторить) работу системы, осуществить оперативный контроль работоспособности системы. Прц возникновении сбойных ситуаций оператор может повторить работу в режцме само. контроля запланированное колцчесгво раз и в случае повторения ошибки несколько раз (устанавливается по согласованию) зафиксировать ошибку.Таким образом, изобретение позволяет обеспечить контроль оператора за состоянием всей совокупцостц датчиков (контроль параметров теплоносителей и состояния технологического оборудования тепловых сетей), оперативный вывод данных нл индикацию и печать, а также зафиксировать аварийную ситуацию и обеспечить надежность работы системы зл счет организации самоконтроля системы. Кроме ТОГО, СИСтЕМа ПРОИЗВОДИТ ВЫДЛЕНЦЕ существенной информации, что сццжает объем требуемой памяти без г.цжеция информативности и достоверцстц,

СмотретьЗаявка

3649551, 17.10.1983

ПРЕДПРИЯТИЕ ПЯ В-2655

КЕВОРКОВ МАРК РУБЕНОВИЧ, ЛАЗАРЕВ НИКОЛАЙ НИКОЛАЕВИЧ, ЛЕБЕДЕВА ГАЛИНА АБРАМОВНА, ЩЕРБАКОВ СЕРГЕЙ БОРИСОВИЧ

МПК / Метки

МПК: G06F 3/04

Метки: информации, сбора

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/6-1108432-sistema-sbora-i-obrabotki-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система сбора и обработки информации</a>

Предыдущий патент: Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе

Следующий патент: Устройство для ввода информации

Случайный патент: 416243