Калибратор фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1048424

Автор: Глинченко

Текст

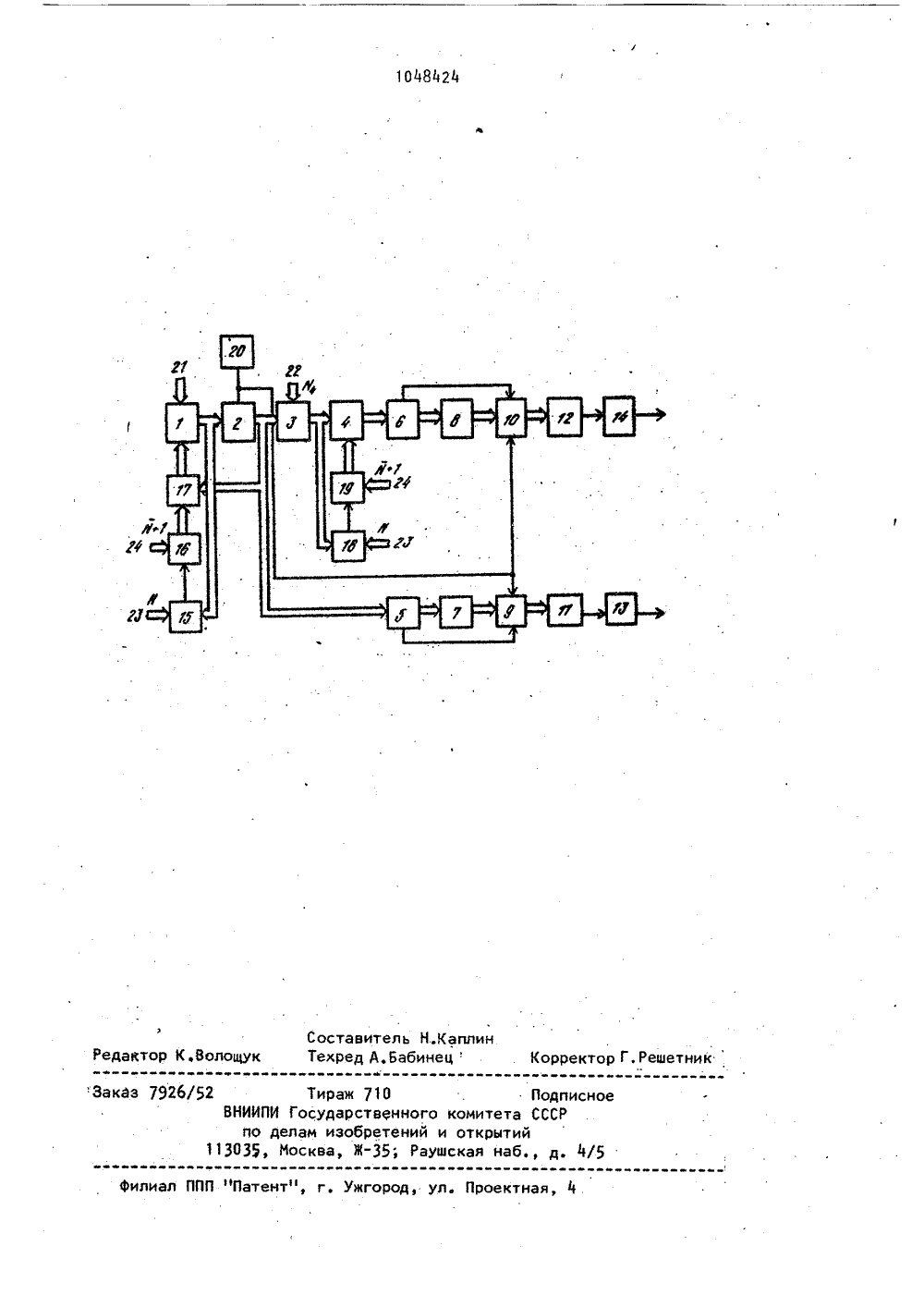

( ) (46) (72) (71) инст (53) (56) итехнический ОСУДАРСТВЕННЫЙ . КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ 621.317.7(088,8)1. "Техника средств связи",Сер. "Радиоизмерительная техника",1978, вып. 6(18), с. 41.2. Авторское свидетельство СССРИ 853563, кл. 6 О 1 Р 25/04, 1981(54)(57) КАЛИБРАТОР ФАЗЫ, содержащий задающий генератор, два.постоянных запоминающих элемента, двафильтра нижних частот, первый и вто"рой цифро-аналоговые преобразователи, выходы которых соединены соответственно с входами первого и второго фильтров нижних частот, выходыкоторых подключены соответственнок первому и второму выходам калибратора фазы, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены четыре,сумматора, регистр, два многоразрядных элемента И, два элемента сравнения кодов, два преобразователя кодаадреса и два преобразователя кодаданных, причем первые входы первогосумматора подключены к шине кода Икалибратора Фазы, вторые входы первого сумматора соединены с выходамивторого сумматора, а выходы первогосумматора подключены к входам регистра и первым входам первого элементасравнения кодов, вторые входы которого соединены с шиной кода Й калибратора Фазы, а выход первого элемента сравнения кодов подключен к управля- ющему входу первого многоразрядного. элемента И, информационные входы которого подключены к шине дополнительного кода И и к информационным входам второго многоразрядного элемента И, а выходы первого многоразрядного элемента, И соединены с первыми входами второго сумматора, вторые входы которого подключены ко входам первого преобразователя кода ад-. реса, к первым входам третьего сумматора и к выходам регистра, вход записи которого подключен к выходу задающего генератора и к первым упР равляющим входам первого и второго э преобразователей кода данных, вторыевходы третьего сумматора соединены : Цф с шиной кода Й( калибратора Фазы, а выходы третьего сумматора подключены к первым входам четвертого сумматора и второго элемента сравнения кодов, вторые входы которого соединены с шиной кода й калибратора азы, а выход второго элемента сравнения кодов подключен к управляющему входу второго многоразрядного элемента И, выходы которого подклюцены к вторым входам четвертого сумматора, выходы которого соединены с ,входами второго преобразователя ко- кафф да адреса, управляющие выходы первого и второго преобразователей кода адреса соединены с вторыми управляющими входами соответственно первого 1 и второго преобразователей кода данных, а выходы разрядов первого и второго преобразователей кода адреса подключены к адресным входам соответственно первого и второго постоянных запоминающих элементов, выходы разря-,дов котбрых соединены с входами соответственно первого и второго преобразователей кода данных, выходы 1048424разрядов которых соединены с входамисоответственно первого и второго цифро-аналоговых преобразователей.Изобретение относится к импульсной и радиоизмерительной технике и может быть использовано для построения калибраторов фазы низкочастотного и инфранизкочастотного диапазона.Известен измерительный двухфазный генератор (калибратор фазы), содержаий два канала - опорный и фазопеременны, включающие последовательно соединеннце первый и второй счетчики-делители частоты, реверсивный распределитель импульсов, ПЗУ, вычислительное устройство, ЦАП, ФНЧ, усилитель и аттеннюатор, а также блок управления, соединенныйс вторым счет. чиком-делителем частоты, ПЗУ, вычислительным устройством и ЦАП, об" щие для обоих каналов блок сравне" ния кодов с подключенным к нему бло" ком задания кода фазового сдвига, последовательно соединенные блок управления частотой,. генератор сетки частот и распределитель импульсов, который первым выходом подключен ко входу первого счетчика-делителя частоты и блока управления опорного канала, а другими выходами через переключатель соединен с соответствующими элементами фазопеременного канала и входом блока сравнения кодов, который также соединен с выходами счетчиков-делителей частоты опорно" го канала и входами установки нуля счетчиков-делителей частоты фаэопе" ременного канала Я .Данное устройство требует, боль" шого объема ПЗУ для хранения всех отсчетов гармонического сигнала, соответствующих его периоду, имеет большое время установления фазы выходного сигнала (не менее одного периода), что в диапазоне инфраниэких частот может составлять единицы- сотни секунд, Кроме того, количество считываемых точек гармонического сигнала здесь постоянно в диапазоне рабочих частот и выбирается исходя 2иэ необходимого дискрета измененияфазы на верхней частоте диапазона.Этим ограничивается возможность улучшения формы сигнала на низких ча стотах путем увеличения числа считываемых точек по мере понижения частоты сигнала, а также возможностьрасширения частотного диапазона вобласть верхних. частот путем умень шения числа считываемых точек сигнала по мере повышения частоты сигнала.Наиболее близким по техническойсущности к изобретению является циф ровсе устройство для воспроизведенияфазовых сдвигов (калибратор Фазы),содержащее два канала, включающихпоследовательно соединенные делительчастоты, реверсивнцй счетчик, посто янный запоминающий элемент, преобра-зователь код - напряжение, ВС-цепь,общий для обоих каналов задающий генератор, соединенный выходом с делителями частоты и реверсивными счетчи ками обоих каналов, выход "Установкануля Первого делителя частоты соединен со входом "Запись" второго делителя частоты, управляющие входы которого соединены с шиной кода фазы, вы ходы "Знак 0", и "Знак О" первогои второго дилетелей частоты подключены к управляющим входам соответствующих преобразователей код - напряжение. (Преобразователь код - напряжение и ЙС цепь В дальнейшем целесообразнее называть как цифроаналоговый преобразователь и фильтр нижнихчастот) 2.8 известном устройстве в ПЗУ хра- "0 нятся значения синусоидальной функциидля одного квадранта, а код фазы задается путем предустановки второго делителя частоты в момент времени, когда текущий код первого делителя частоты равен акулю. При этом время установления фазы велико, а постоянство числа считываемых точек ограни" чивает воэможности расширения частот3 1048424 4ного диапазона. Указанные недостатки четвертого сумматора, выходы котороснижают быстродействие устройства. го соединены с входами второго преЦель изобретения - повышение быст" образователя кода адреса, управляю-родействия, щие выходы первого и второго преобПоставленная цель достигается тем, 5, разователей кода адреса соединены счто в калибратор фазы, содержа- вторыми управляющими входами соотщий задающий генератор, два посто- . ветственно первого и второго преобянных запоминающих элемента, два разователей кода данных, а выходы разфильтра нижних частот, первый и вто- . рядов первого и второго преобразоварой цифра-аналоговые преобразователи, 10 телей кода адреса подключены к адресвыходы которых соединены соответст- ным входам соответственно первого ивенно с входами первого и второго . второго постоянных запоминающих элефильтров нижних частот, выходы кото- .; ментов, выходы разрядов которых соерых подключены соответственно к пер" динены с входами соответственно первому и второму выходам калибраторавого и второго преобразователей кофазы, введены четыре сумматора, Ре- да данных, выходы разрядов которыхгистр, два многоразрядных элемента соединены с входами соответственноИ, два элемента сравнения кодовпервого и второго цифро-аналоговыхдва преобразователя кода адреса ипреобразователей.два преобразователя кода данных, при" 2 Очем первые входы первого сумматора На чертеже приведена блок-схемаподключены к шине кода И калибратора ,:калибратора,. фазы, вторые входы первого сумматора , Калибратор фазы содержит последовасоединены с выходами второго сумма- тельно соединенные первый сумматор .тора, а выходы первого сумматора 25 1, регистр 2, третий сумматор 3,подключены к входам регистра и пер- четвертый сумматор 4, последовательвым входам первого элемента срав- но соединенные в обоих каналах пернения кодов, вторые, входы которого вый и второй преобразователи 5 и 6соединены с шиной кода й калибра- кода адреса, первые и вторые постоянтора фазы, а выход первого элемента ные запоминающие элементы 7 .и 8,сравнения кодов подключен к управ- первый и второй преобразователи 9ляющему входу, первого многоразряд- .и 10 кода данных, первый и второйного элемента И,информационные цифро-аналоговые преобразователи 11входы которого подключены к шине до- и 12 и первый и второй фильтры, нижполнительного кода й и к информа- них частот 13 и 14, последовательноционным входам второго многоразряд- соединенные первый элемент 15 срав 31ного элемента И, а выходы первого кения кодов, первый многоразрядный.многоразрядного элемента И соеди- элемент 16 И и второй сумматор 17,нены с первыми входами второго сум- последовательно соединенные второйматора, вторые входы которого под- :элемент 18 сравнения кодов и второйключены ко входам первого преобра- , многоразрядный. элемент 19 И, а также40зователя кода адреса, к первым входам задающий генератор 20, соединенный стретьего сумматора и к выходам ре- регистром 2, который связан выходагистра, вход записи которого под- . ии с вторыми входами второго сумматоключвн к выходузадающего генерато- ра 17 и первого преобразователя 5 кора и к первым управляющим входам пер-.: да адреса, входы второго преобразо 4 Я,вого и второго преобразователейвателя 6 кода адреса соединены с выхо"кода данных, вторые входы третьего дами четвертого сумматора 4, вторые.сумматора соединены с шиной кода ,входы которого подключены к выходамйкалибратора фазы, а выходы третье- второго.ийогоразрядного элементаго сумматора подключены к первым 50 . 19 И, выходы разрядов первого и тревходам четвертого сумматора и второ-тьего сумматоров 1 и 3 соединены сго элемента сравнения кодов, вторые : входами соответственно первого 15 ивходы которого соединены с виной второго 18 элементов сравнения кодов,кода й калибратора фазы, а выход первый и второй входы соответственновторого элемента сравнения кодов под-.первого и третьего сумматоров 1 и 3ключен к управляющему входу второгосоединены соответственно с шиной 21многоразрядного элемента И, выходы кода И и шиной 22 кода й, вторыекоторого подключены к вторым входам входы первого и второго элементов5 10484 15 и 18 сравнения кодов соединены с шиной 23 кода М, а информационные входы первого и второго многоразрядных элеиентов 16 и 19 И соединены с шиной 24 дополнительного кода иисла М. 5Устройство работает следующим образом.Допустим, на первые входы первого сумматора 1 с шины 21 подан код М 1, а регистр 2 находится в нулевом начальном состоянии. Так как входной код первого сумматора 1 при этом меньше М, где М - максимальное число считываемых точек заданной (синусои" дальной) функции сигнала за период, 15 то на выходе первого элеиента 15 сравнейия кодов будет логический нуль, которому соответствуют нулевые , уровни на выходах разрядов первого многоразрядного элемента 16 И и вто рого сумматора 17, а на выходах разрядов первого сумматора 1 будет двоичный код единицы. Выходы разрядов регистра 2 соединены с входами перво-го преобразователя 5 кода адреса непосредственно и с входами второго пре. образователя 6 кода адреса через третий и четвертый сумматоры 3 и 4. С помощью этих сумматоров и связанных с. ними второго элемента 18 сравне ния кодов и второго многоразрядного элемента 19 И задается фазовый сдвиг, между выходными сигналами первого и второго каналов, определяемый двоичным кодом Му, подаваемым с шины 22 на вторые входы третьего сумматора 3. Этот код сумиируется с выходным кодом регистра 2 и поступает на первые входы четвертого сумматора 4 и второго элемента 18 сравнения кодов, 40 Если суммарный код меньше М, то на вторые входы четвертого сумматора 4 с.выходов разрядов второго многоразФрядного элемента 19 И подается нулевой код и таким образом выходной код 45 третьего сумматора 3 без изменения поступает на входы второго преобразователя 5 кода адреса.С помощью первого и второго преобразователей 5 и 6 кода адреса определяется номер квадранта синусоидальной функции и преобразование кодовадресов считываемых ячеек первого ивторого постоянных запоминающих элементов 7 и 8, где записаны М/4 значений синусоидальной функции в первом квадраяте (0-90 ), При этом впервом и третьем квадрантах выходные 24 . Ькоды первого и второго преобразователей 5 и 6 линейно возрастают отнуля до (М 74-1) в соответствии с выходными кодами регистра 2 и четвертого суиматора 4, а во втором и четвертом квадрантах - линейно убывают от(М/4-1) до нуля. Первый и второйпреобразователи 5 и 6 кода адреса управляют также соответствующими первыми и вторыми преобразователями кодаданных, с помощью которых преобразуются выходные коды первого и второгопостоянных запоминающих элементов7 и 8, При этом в первом и второмквадрантах к выходным кодам первого .и второго постоянных запоминающихэлементов 8 и 7 прибавляется единица, а в третьем и четвертом квадрантах эти коды преобразуются в обратныйкод, В результате на входы первого ивторого цифро-аналоговых преобразователей 11 и 12 поступают коды значе"ний синусоидальной функции.О (пТ) =з 1 п (2 ЯГТ+)+1,0 (пТ)=в 1 п(2 ЯГТ)+1,где Т - период дискретизации, определяемый частотой задающегогенератора;п=0,1;Е " частота сигнала.Амплитуда сигналов на выходах пер"вого и второго цифро-аналоговых преобразователей 11 и 12 определяютсяуровнем эталонного напряжения От, аисключение постоянной составляющейиз выходного сигнала осуществляетсяс помощью операционного усилителя,подключаемого к выходам первого и.второго цифро-аналоговых преобразователей (на цертеже не показаны,так как они входят в состав цифро"аналоговых преобразователей). Отсутствие коммутации полярности эталонного напряжения первого и второгоцифро-аналоговых преобразователей11 и 12 по сравнению с прототипомповысит точность преобразования ибыстродействие устройства.Выходные сигналы цифро-аналоговых преобразователей ступенчатойформы отфильтровываются от высшихгармоник с помощью первого и второго фильтров 13 и 14 нижних частот ипоступают на выходы устройства практически к выходам ФНЧ подключаютсятакже усилитель и управляемый атте"нюатор, которые обеспечивают усиление мощности сигналов и заданноеослабление их уровней),Считывание очередного отсчета выходного сигнала с выходов первогои второго постоянных запоминающихэлементов7 и 8 и занесение его в .регистры памяти первого и второгопреобразователей 9 и 10 производится с частотой задающего генератора20. Под действием импульсов этого Ю.генератора осуществляется запись выходного кода первого сумматора 1 врегистр 2, в результате чего выходные коды второго 17 и первого 1 сумматоров увеличиваются на единицу 15(при М 1). Также на единицу увеличиваются и выходные коды третьего3 и четвертого 4 сумматоров, в результате чего адрес считываемой ячейки первого и второго постоянных 20запоминающих элементов 7 и 8 изменяется на единицу (увеличивается илиуменьшается в зависимости от номераквадранта) а ее .содержимое поступает в первый и второй преобразова-. 25тели 9 и 10 кода данных для форми"рования отсчета выходного сигнала.В следующем такте процессы повторяются. При достижении выходным кодом первого или третьего суммато" 30ров 1 и 3 значения М срабатываютпервый и второй элементы 15 и 18 сравнения кодов и открывают первый и второй многоразрядные элементы 16 и19 И, на выходах разрядов которыхпоявляется дополнительный код числа,равный М+1, задаваемый с шины 24,где М - обратный код числа М. Этоткод складывается в четвертом сумматоре 17 с выходным кодом регистра 2 4 Оили третьего сумматора 3, в реэуль"тате чего на выходах второго и четвертого сумматоров 17 и 4 код уменьшится на величину М, Таким образом, навыходах регистра 2 и четвертого сумматора 4 формируется текущий код,изменяющийся в пределах (О-М),используемый для формирования кодаадреса, принимающего значения (О""1)М . юна выходах разрядов первого и второ-50го преобразователей 5 и 6 кода адре"са. При этом за период сигнала считываются все М значений синусоидаль"ной функции, М/4 значений которойдля первого квадранта записаны в первом и втором постоянных запоминающих55элементах 7 и 8. Частота выходного 1048424 8сигнала в этом случае определяется как Г Г /М, Ее верхнее значение ог,раничивается быстродействием постоянных запоминающих устройств и цифро 5 .аналоговых преобразователей, имею- .щих по сравнению с другими элементами устройства наименьшее. быстродействие.1048424 ставитель Н.Каплихред А,БабинецКорректор Г. Решетник едактор К .Волошук йз 792 б/ Тираж 710 . Подп ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 303, Иосква, Ж; Раушская наб., д.

СмотретьЗаявка

3444887, 28.05.1982

КРАСНОЯРСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ГЛИНЧЕНКО АЛЕКСАНДР СЕМЕНОВИЧ

МПК / Метки

МПК: G01R 25/04

Метки: калибратор, фазы

Опубликовано: 15.10.1983

Код ссылки

<a href="https://patents.su/6-1048424-kalibrator-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Калибратор фазы</a>

Предыдущий патент: Устройство для измерения погрешности фазовращателя

Следующий патент: Измеритель полной проводимости нагрузки радиопередающего устройства

Случайный патент: Способ изготовления объемных резисторов