Периферийный процессор обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

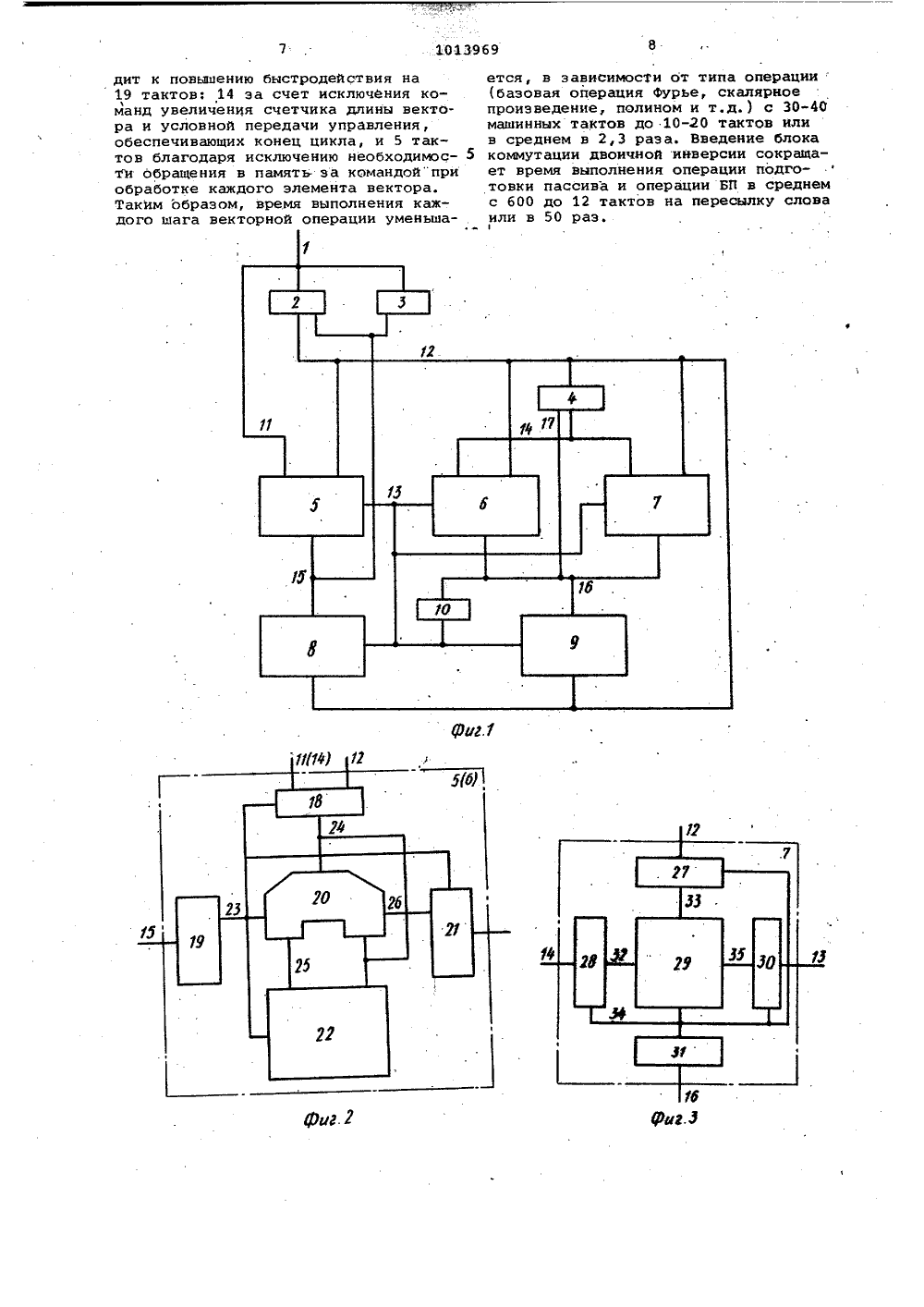

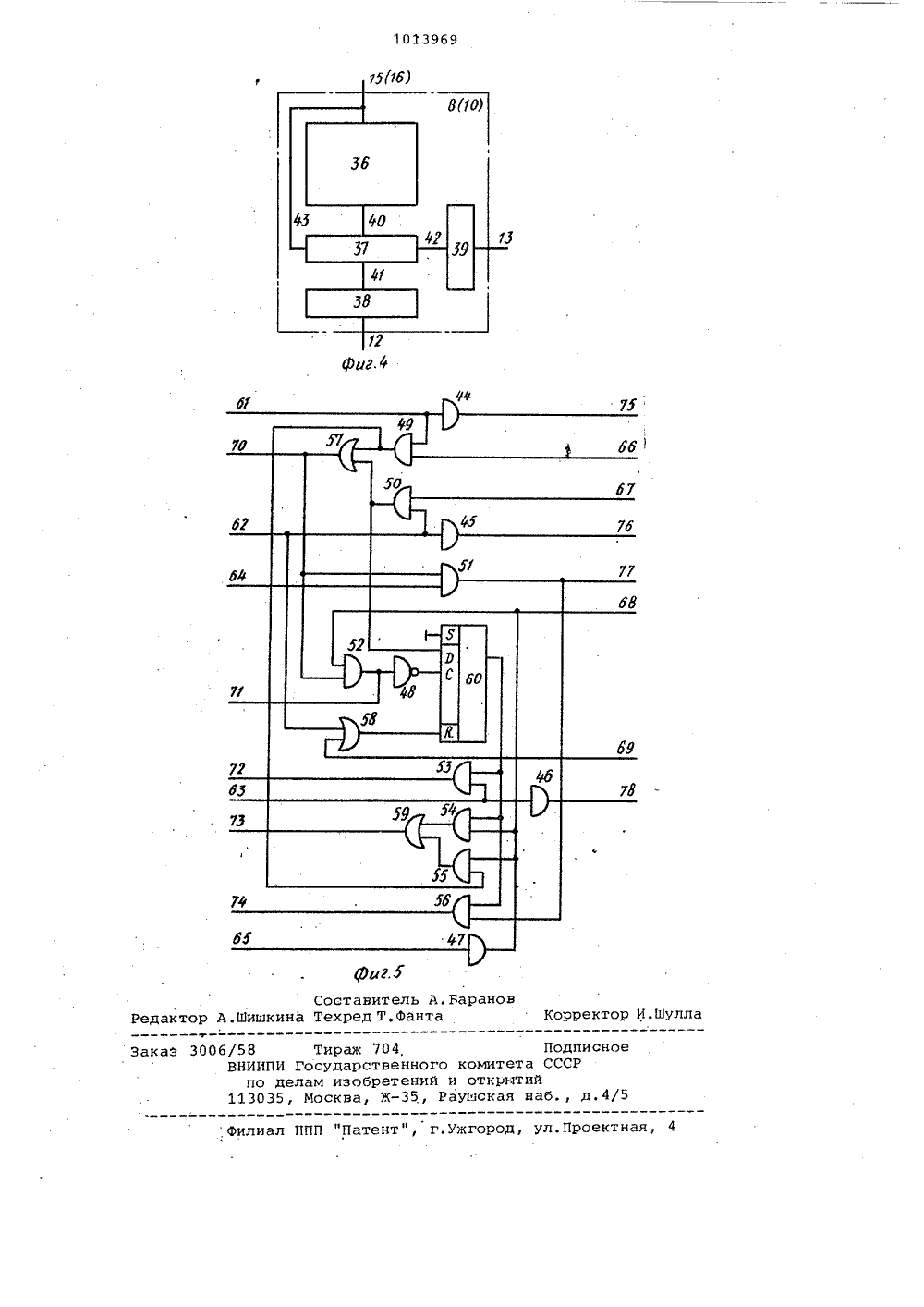

969 СОКИ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 3(51) С 06 ГЬ 4 ЦМр 5.- .Г.щ кь % М ОсудАРстВенный КОмите ДЕЛАМ ИЭОБРЕТЕНИЙ И О ОПИСАНИЕ ИЗОБРЕТЕН ОМУ СВИДЕТ К АВТО(54)(57) 1. ПЕРИФЕРИИНЫЯ ПРОЦЕССОР ОБРАБОТКИ СИГНАЛОВ, содержащий первый и второй блоки управления.,первый и второй блоки сложения блок умножения, блок коммутации. и блок сопряжения, вход-выход которого объединен с входом блока коммутации и является входом-выходом процессора, выход первого блока управления соединен с управляющим входом первого блока сложения и управляющими входами блока сопряжения и блока коммутации, выход которого .соединен с первыми входами- выходами первого и второго блоков сложения, первым входом-выходом блока умножения и первыми входами первого и второго блоков управления, выходы признака результата суммирования первого и второго блоков суммирования и выход признака результата умножения блока умножения соединены с вторыми входами первого и второго блоков управления, .выход второго блока управления соединен с управляющими входами второго блока сложения и блока умножения, второй выход-вход второго блока сложения подключен к второму входу-выходу блока умножения, о тл и ч а ю щ и й с я тем, что, с це- лью повышения быстродействия в него введены блдк коммутации состояния и блок коммутации двоичной инверсии, выход которого соединен с первыми входами первого и второго блоков управления, выход второго блока управления подключен к входу блока коммутации состояния, выход которого соединен.свторыми входами первого и второго блоков управления, вход блока коммутации двоичной инверсии соединен с вторыми выходами-входами второго Щ блока сложения и блока умножения, а второйвход-выход первого блока сложения подключен к выходу-входу блока сопряжения.2, Процессор по п.1, о т л и ч аю щ и й с. я тем, что блок управле- Я ния содержит узел памяти дешифратор, регистр команД и регистр состояния; выход которбго подключен к первому входу дешифратора, выход которого со единен с щкщом узла памяти, выход которого является .выходом блока управления и подключен к второму входу дешифратора, третий вход которого соединен с выходом. регистра. команд, вход которого является первым входом блока управления, а вход регистра состояния является вторым входом блока.управления.рую внутреннюю магистраль процессора,используемую для проведения обменов информацией между блоками сложения и умножения и для выдачи адресов и дан. ных из блоков сложения и умножения на вход блока коммутации и далее н магистраль ЭВМ.Соединение выхода первого устройства управления с входами управления первого блока сложения, регистрации блоков коммутации и блоком сопряжения образует первую магистраль управления, используемую для передачи кодов управления.Соединение выхода второго устройства управления с входами управления второго блока сложения и блока умножения образует вторую магистраль управления, используемую для передачи кодов управления. Соединение выходов состояния обоих блоков сложения и блока умножения с входом состояния первого устройства упранления образу -ет магистраль состояния, н которуювыдаются кодьФ признаков результатоввыполненных операций.,Распределение функций обработкиданных между первым блоком сложения,с одной стороны, и блоками сложенияи умножения, с другой, дает возможность уменьшить объем пажити устройства управления и увеличить быстродействие процессора за счет совмещения выполнения арифметических действий в блоках сложения и умножения с вычислением адресов в блоке сложения. Дополнительным ресурсом повышения производительности является воэможность подключения нескольких процессоров, работающих с общей памятью к одной магистрали ЭВМ 2.Недостатком известного процессора является низкое быстродействие.Целью изобретения является повыше ние быстродействия процессора на задачах цифровой обработки сигналов,Указанная цель достигается тем, что в периферийный процессор обработки сигналов, содержащий первый и второй блоки управления, первый и второй блоки сложения, блок умножения, блоккоммутации и блок сопряжения, входвыход которого объединен с входомблока коммутации и является входомвыходом процессора, выход первого блока управления соединен с управляющим входом первого блока сложения иуправляющими входами блока сопряжения и блока коммутации, выход которого соединен с первыми нхсдами-выходами первого и второго блоков сложения,первым входом-выходом блока умножения и первыми входами первого и второгоблоков управления, выходы признакарезультата суммирования первого ивторого блоков суммирования и выходпризнака результата умножения блока умножения соединены с вторыми входами Изобретение относится к микроэлектронике и вычислительной техникеи может быть использовано для построения вычислительных систем цифровой . обработки сигналов н реальном времени. 5Известен специализированный периферийный процессор для обработки массивов информации, содержащий арифметическое устройство, выполняющее арифметические действия над числами, 10 представленными в форме с Фиксированной или плавающей запятой, внутреннюю память, состоящую из двух незанисимых блоков, одновременно осуществляющих обмены с памятью. центрального процес сора и арифметическим устройством, три устройства управления на основе ПЗУ, управляющие работой памяти, арифметического устройства и обмена информацией между памятью периферийного процессора и памятью центрального процессора.Трубопроводный принцип организации структуры процессора позволяет достичь высоких показателей быстродействия эа счет перекрытия и распараллеливания обработки информации. Распределение функций обработки данных между центральным и периферийным процессорами позволяет строить оптимальным образом специальные алгоритмы спектрального анализа. Существует возможность улучшения характеристик систем путем подключения к одному центральному процессору нескольких периферийных Г 1.35Однако специализированный периферийный процессор приводит к большим аппаратурным затратам, что исключает возможность его использования в вычислительных системах с жестким 40 ограничением на объем оборудования.Наиболее близким к изобретению по технической сущности является процессор, лрименяемый в ЭВМ, с асинхронным, унифицированным интерфейсом, 45 подключаемый к магистрали ЭВМ и состоящий иэ регистров блока коммутации и блока сопряжения, двух блоков сложения, блока умножения, двух Уст ройств управления, связанных между собой внутренними информационными магистралями процессора и магистралями управления,.причем соединение первых входов-выходов блоков сложения, блока умножения, командных входов первого и второго устройств управления, входа состояния .второго устройства управления и выхода блока коммутации образует первую внутреннюю магистраль процессора; используемую для приема данных и команд из памяти и 60 проведения обменов информацией между блоками сложения и умножения.Соединение вторых входон-выходов блоков сложения, блока умножения и входа блока коммутации образует нто65 первого и второго блоков управления, выход второго блока управления соединен с управляющими входами второго блока сложения и блока умножения,второй выход-вход второго блока сложения подключен к второму входу-выходу блока умножения, введены блок коммутации состояния и блок коммутации двоичной инверсии, выход которого соединен с первыми входами первого и второго блоков управления, выход второго блока управления подключен к входу блока коммутации состояния,. выход которого соединен с вторыми входами .первого и второго блоков управления, вход. блока коммутации двоичной инвер. сии соединен с вторыми выходами-входами второго блока сложения и блока умножения, а второй вход-выход первого блока сложения подключен к выходу- входу блока сопряжения.Причем блок управления содержит узел памяти, дешифратор, регистр команд и регистр состояний, выход которого подключен к первому входу дешифратора, выход которого соединен с входом узла памяти, выход которого является выходом блока управления и подключен к второму входу дешифратора, третий вход которого соединен с выходом регистра команд, вход которого является первым входом блока уп равления, а вход регистра состояния является вторым входом блока управления.На Фиг.1 представлена функциональная схема периферийного процессора; на фиг.2 - функциональная схема блока сложения, на фиг.З - функциональная схема блока умножения; на фиг.4 Функциональная схема устройства управления, на фиг.5 - функциональная схема блока сопряжения.Периферийный процессор обработки сигналов (Фиг.) подключен к магистрали 1 ЭВМ с асинхронным унифицированным интерфейсом. Процессор содер- жит блок 2 коммутации, блок 3 сопряжения, блок 4 коммутации двоичной инверсии, первый блок 5 сложения, второй блок 6 сложения, блок 7 умножения, первый блок.8 управления, второй блок 9 управления и блок 10 коммутации состояния.Вход-выход 11 первого блока 5 сложения соединен с магистралью 1 ЭВМ. Первая внутренняя магистраль 12 процессора соединяет первые входы-выхо,ды первого блока 5 сложения, второго бло ка 6 сложения и блока 7 умножения, коман дные входы блоков 8 и 9 управления, выходы блока 2 коммутации и блока 4 коммутации двоичной инверсии. Магистраль 13 состояния соединяет выходы с:стояния блоков 5-7, блока 10 комму-. тации состояния и входы состояния блоков 8 и 9 управления. Вторая внутренняя магистраль 14 процессора соединяет вторые входы-выходы второгоблока 6 сложения и блока 7 умноженияс входом блока 4 коммутации двоичнойинверсии. Первая магистраль 15 управления соединяет выход первого блока5 8 управления с управляющими входамипервого блока 5 сложения, блока 2коммутации и блока 3 сопряжения. Вторая магистраль 16 управления соединя-.ет выход второго блока 9 управления10 с управляющими входами второго блока6 сложения, блока 7 умножения, блока10 коммутации состояния и с управляющим входом 17 блока 4 коммутации двоичной инверсии.Регистр блока 2. коммутации предназначен для буФеризации принимаемыхиз магистрали 1 команд и данных итрансляции их в первую внутреннюю магистраль 12 процессора.20Каждый блок 5 и 6 сложения процессора (фиг.2) включает узел коммутатора 18, дешифратор 19, сумматор,регистр 21 состояния и регистры 22общего назначения, соединенные междусобой цепями 23-26.Коммутатор 18 соединяет выходнуюцепь 24 блока сложения с первым 11.(14) и вторым 12 входами-выходамиданных блоков 5 и 6 сложения. Дешифратор 19 преобразует поступающие поЗ 0 входу 15 управления коды в сигналыуправления и выдает их по цепи 23 навсе схемы блока сложения. Сумматор20 выполняет набор арифметических илогическчх операций над данными, по-.35 ступающими на него по входам 24 и 25.На регистре 21 состояния хранятсяпризнаки результата сумматора, записываемые в йего по цепи 26 и выдаваемые из блока сложения по цепи 13. Ре 40 гистры 22 общего назначения предназ- .начены для временного хранения информации внутри блока сложения.Блок 7 умножения (фиг.З) состоитиз двух регистров 27 и 28, умножителя 29, регистра 30 состояния и де-шифратора 31 кодов управления,В регистрах 27 и 28 запоминаютсяоперации, поступающие по первому ивторому входам-выходам 12, 14 данныхна .блок умножения. После выполненияоперации умножения умножителем 29над содержимым регистров 27 и 28, поступающим на умножитель по цепям32 и 33, результат умножения записывается в регистры 27 и 28.55 Дешифратор 31 кодой управленияблока умножения преобразует поступающие на вход 16 управления коды в управляющие сигналы для всех схем блока умножения, выдаваемых им по це 60 пи 34. Признаки состояния результата выполнения операции умножения записыва. - ются в регистр 30 состояния блока ум. ножения по цепи 35.(фиг.4) процессора состоит из узла36 памяти, дешифратора 37, регистра38 команд и регистра 39 состояния,соединенных цепями 40-43,Коммутатор двоичной инверсии представляет собой управляемый коммутаторвыполняющий функции: при наличии логической единицы на входе 17, информация из 1-й линии магистрали 14 передается в (15-) линию магистрали 12,10при наличии логического нуля на входе17 передача информации из магистрали14 в магистраль 17 через блок 4 прекращается. 15Блок 3 сопряжения (фиг.5) содержит четыре усилителя 44-47, инвертор48, восемь элементов И 49-56, триэлемента ИЛИ 57-59 и 0-триггер 60.Со стороны процессора в блок сопряжения входят линии запроса прерывания61, запроса обмена 62 и чтения 63,входящие в состав первой магистрали15 управления, линии сопровождениявыдачи данных 64 по магистрали 11 исопровождения приема данных 65 помагистрали 12. Со стороны ЭВМ в блоксопряжения входят линии разрешенияпрерывания 66, разрешения обмена 67,подтверждения приема 68 и установки69, входящие в состав магистрали 1.Иэ блока 3 сопряжения процессора выходят линии разрешения выдачи 70 (иэгруппы линий 15), подтверждениях приема 71 по магистрали 11, управленияблоком комиутации 72 и завершения .об мена из группы линий 15 и сопровожде ния выдачи данных 73 и 74 по магистрали 14. Из блока сопряжения на ма .гистраль ЭВМ выходят линии запроса прерывания 75,.запроса обмена 76, 40 сопровождения выдачи данных 77 и чтения 78.Блок сопряжения выполняет временные диаграммы выполнения операции чтения, записи и прерывания по магист 45 рали 1 в соответствии со стандартом.Блок 10 коммутации состояний позволяет передавать с выхода устройства 9 управления в региСтр 39 состояния устройства 8 управления коды состояний, хранящиеся в устрбйстве 9 управления и, тем самым, влиять на выходные управляющие сигналы устройства 8 управления, т.е. изменять порядок обработки данных в процессоре в зави-. симости от результатов не только непосредственно предшествующих выборке управляющих сигналов, но и Любой ранее выполняемой операции. Схема коммутации состоянийпредставляет собой находящиеся подобщим управлением 60 ключевые элементы, которые в открытом состоянии пропускают информационные сигналы из магистрали 16 управле. ния в магистраль 13 состояний, а в э акрытом состоянии - н пропускают. Процессор работает следующим образом,Включение питания приводит всеблоки 3, 5, 6-9 процессора в исходноесостояние и переводит его в состояние"Стоп". Нэ состояния "Стоп" процессор может быть выведен загрузкой команды "Луск", например,с пульта или из центрального процессора ЭВМ, поступающей из магистрали1 ЭВМ через блок 2 коммутации и внутреннюю магистраль 12 на командныевходы блоков 8 и 9 управления. Послеэтого процессор начинает последовательное выполнение команд, хранящихся в памяти ЭВМ.Цикл выполнения команды можно разделить на следующие этапы выборкаоперации, выполнение операции; записьрезультата операции; проверка условиязавершения выполнения команды, выборка кода следующей команды,На первом этапе в зависимости откода команды происходит выборка одного или нескольких операндов из памятипо адресам, вйчйсляемым блоком 5 сложения и выдаваемым через магистраль11 в магистраль 1 ЭВМ и приема их измагистрали 1 ЭВМ через блок 2 коммутации и магистраль 12 в один из блоков 5, 6 сложения и блока умножения7. На втором этапе выполняется операция блоками сложения 5,6 и умножения7 и вырабатываются признаки результата операцииНа третьем этапе результат операции записывается на регистры одногоиэ блоков сложения 5, 6 или умножения7 или записывается в память. В последнем случае блок сложения вычисляетадрес записи результата и выдает егочерез магистраль 11 в магистраль 1ЭВМ. Далее результат операции транслируется из внутренней магистрали 12через блок 5 сложения в магистраль 11и в магистраль 1 ЭВМ, На четвертомэтапе вырабатывается условие завершения выполнения команды, например признак обнуления счетчика циклов, ипринимается через магистраль 13 сос. -тояния на вход состояния блоков 8 и 9управления, По результатам анализапризнака завершения выполнения команды происходит переход к первому илипятому этапу выполнения команды. Напятом этапе блоком 5 сложения вычисляется адрес следующей команды и выдается через магистраль 11 в магистраль 1 ЭВМ. Считанный код команды измагистрали 1 ЭВМ через блок 2 коммутации и магистраль 12 поступает накомандные входы блоков 8 и 9 управления.Наличие связи магистрали состоянияпроцессора с входом состояния второгоустройства управления обеспечиваетвоэможность выполнения циклическихкоманд обработки массивов, что приводит к повышению быстродействия на 19 тактов: 14 эа счет исключения команд увеличення счетчика длины вектора и условной передачи управления, обеспечивающих конец цикла, и 5 тактов благодаря исключению необходимос ти обращения в память. за командой"при обработке каждого элемента вектора. Таким образом, время выполнения каждого шага векторной операции уменьша- .Ж ется, в зависимости от типа операции(базовая операция фурье, скалярноепроизведение, полином и т,д.) с 30-40машинных тактов до 10-20 тактов илив среднем в 2,3 раза. Введение блокакоммутации двоичной инверсии сокращает время выполнения операции подготовки пассива и операции БП в среднемс 600 до 12 тактов на пересылку словаили в 50 раз.11023969 г. оставитель А ехред Т,Фанта ран ректор И.Шулл исн Филиал ППП "Патент", г.ужгород, ул.Проект Редактор А.ШишкЗакай 3006 58/ Тираж 704, ВНИИПИ Государственнопо делам изобретени 113035, Москва, Ж,Подкомитета СССи откритийадская наб.,

СмотретьЗаявка

3362039, 09.12.1981

ПРЕДПРИЯТИЕ ПЯ Р-6429

ЕЛАГИН ВАЛЕРИЙ МИХАЙЛОВИЧ, КАЛЬНЕЙ СЕРГЕЙ ГРИГОРЬЕВИЧ, ГУБАРЕВ НИКОЛАЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G01R 23/16, G06F 15/00, G06F 17/00, G10L 19/02

Метки: периферийный, процессор, сигналов

Опубликовано: 23.04.1983

Код ссылки

<a href="https://patents.su/6-1013969-periferijjnyjj-processor-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Периферийный процессор обработки сигналов</a>

Предыдущий патент: Устройство для опроса абонентов

Следующий патент: Анализатор спектра

Случайный патент: Смеситель