Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 955055

Автор: Берсон

Текст

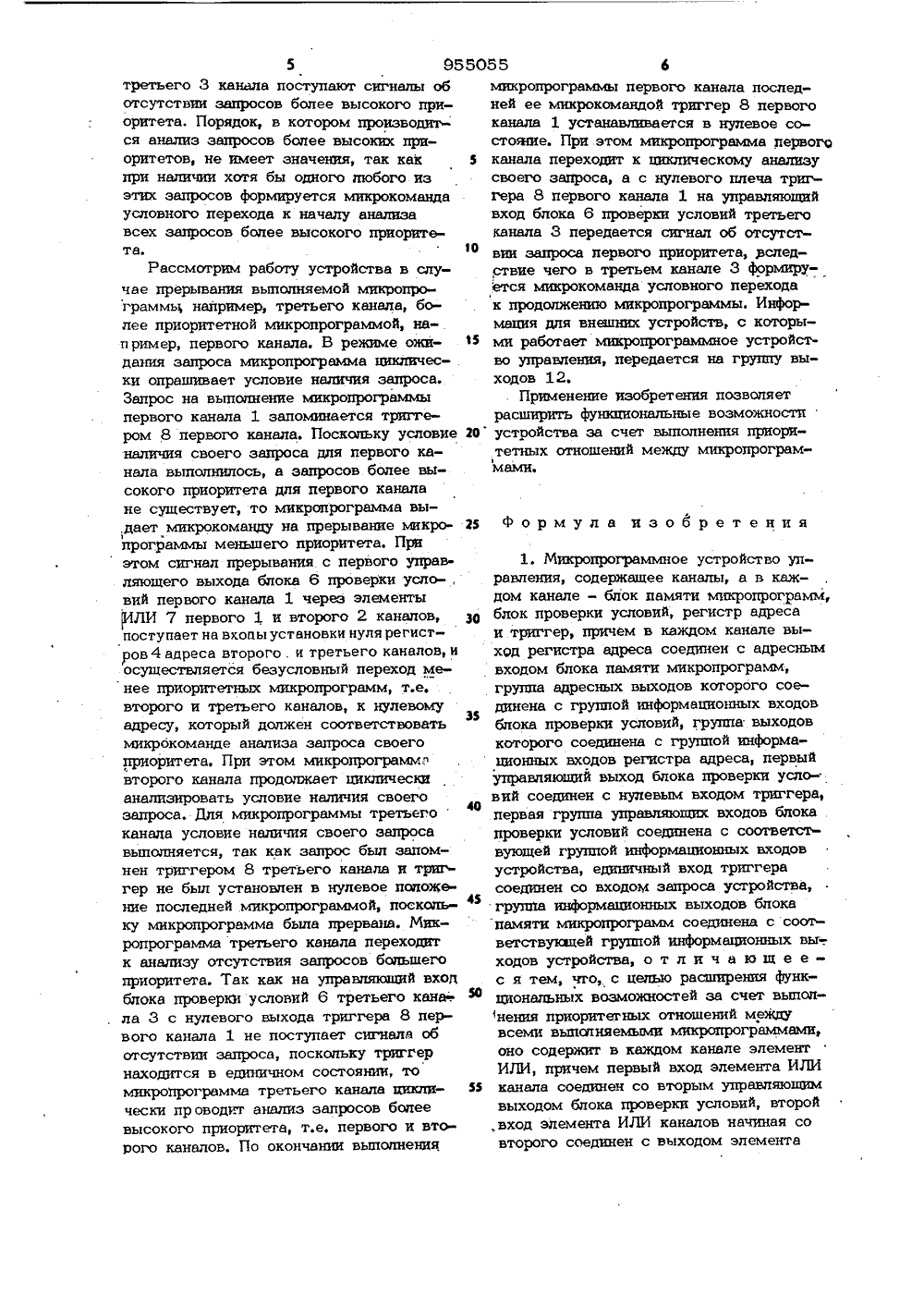

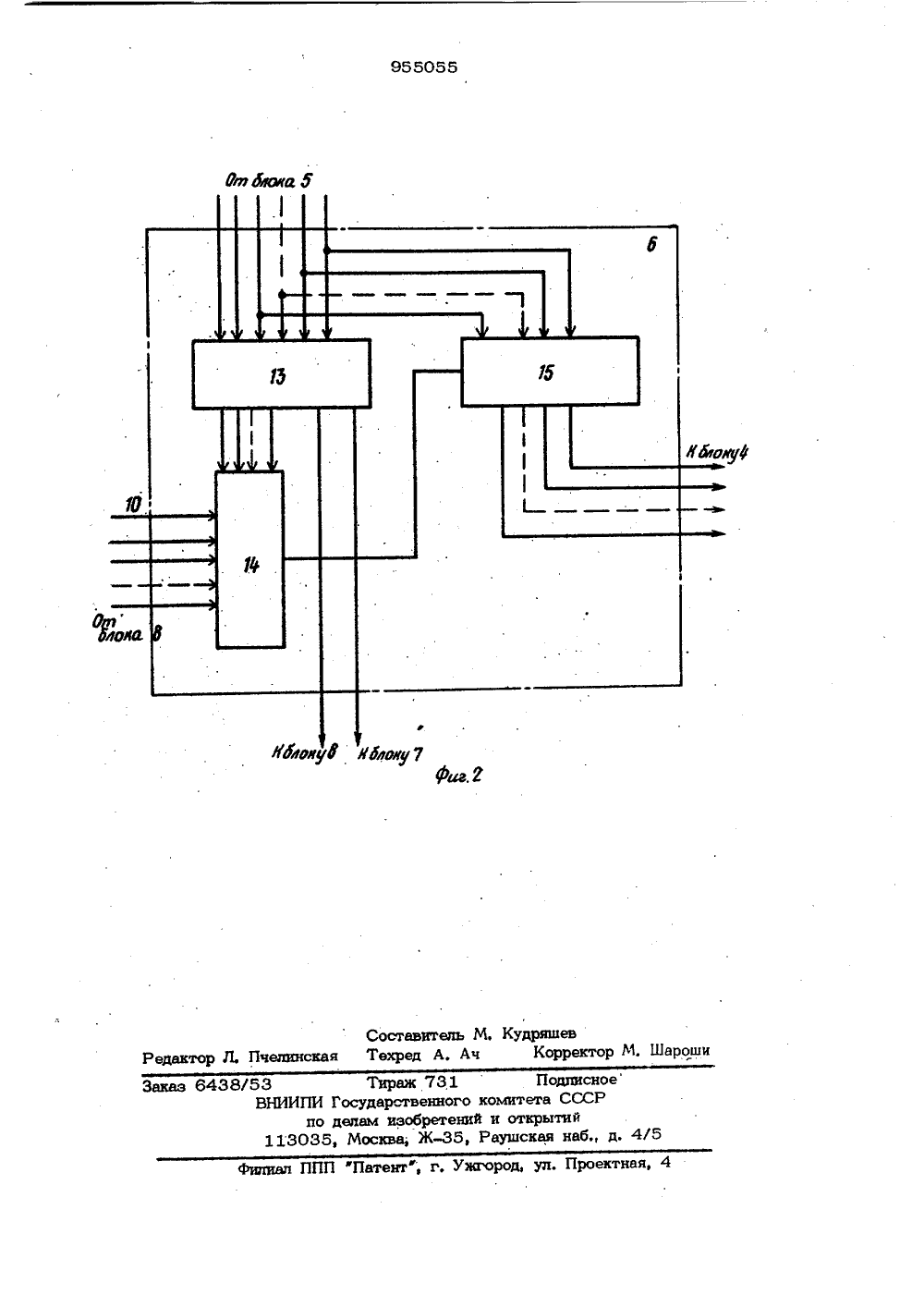

Союз СоветсиикСоциалистическиеРеспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(5) М. Кл. 5 06 Г 9/22 Гееудедстееннцй кемнтет СССР ао, делам нзебретеннй н открытий1 еИзобретение относится к вычислителтной технике, а именно к устройствам дпя программного управления, и может быть использовано в качестве устройст ва управления в специализированных вы 5 числительных машинах и периферийных устройствах автоматизированных систем управления, например в устройствах ввода-вывода информации.и / й й ,ййййй/// го управления, содержащее два блока памяти микропрограмм, два. блока проверки условий, два элемента И, два триггера и два регистра адреса 1Данное устройство не допускает возможности параллельного выполнения микроцрограмм в режиме ожидания основной или более приоритетной микрсетрограммы, а также управления несколькими операпионными устройствами, работа которых 20 имеет различный приоритет.Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство, состоящее 2из блока памяти микропрограмм, блокапроверки условий, элемента И, регистровадреса и триггеров 2)Недостатком известного устройстваявляется то, что отношение абсошотного приоритета установлено между основнойи всеми дсаопннтельными микропрограммами, а сами дополнительныемикроирограммы не связаны приоритетными отношениями.Цель изобретения - расширение функциональных. воэможностей устройства за счет выполнения приоритетных откровений между всеми выполняемыми микропрограммамивПоставленная цель достигается, тем, что в микропрограммное устройство управления, содержащее каншты, а в каждом канале - блок памяти микропрограмм,блок проверки условий, регистр адресаи триггер, причем в каждом канале выход регистра адреса соединен с адреснымвходом блока памяти микропрограмм, группа адресных выходов которого сое3 9880динена с группой информационных входов блока проверки условий, группа выходов которого 1 соединена с группой информационных входов регистра адреса, первый управляющий выход блока проверки условий соединен с нулевым входом триггера, группа управляющих входов блока провер ки условий соединен с соответствующей группой информационных входов устройства, единичный вход триггера соединен р со входом запроса устройства, группа информационных выходов блока памяти микропрограмм соединена с соответствующей группой информационных выходов устройства, введены в каждом канале элемент ИЛИ, причем первый вход элемента ИЛИ канала соединен со вторым управляющим выходом блока ггроверки условий, второй вход элемента ИЛИ кана-, лов начиная со второго соединен с выходом элемента ИЛИ предыдущего канала, второй вход элемента ИЛИ первого канала соединен со входом логического нуля устройства, выход элемента ИЛИ каждого 1 -го канала соединен с управляющимвходом регистра адреса ( 4 + 1)-го канала, единичный выход триггера каждого канала соединен с первым управляющим входом второй группы входов блока проверки условий своего канала, нулевой30выход триггера каждого канала соединен с управляющими входами второй группы входов блоков проверки условий всех последующих каналов.Кроме того, блок проверки условийсодержит дешифратор, счетчик и коммутатор, причем группа входов счетчика .соединена с группой входов коммутатора и группой информационных входов блока, группа выходов счетчика соединена с первой группой входов дешифратора, вто-, фО рая группа входов. которого соединена с первой и второй группами управляющих входов блока, выход дешифратора соединен со входом коммутатора, группа выходов которого соединена с группой вы ходов блока, первый и второй выходы счетчика соединены соответственно с первым и вторым управляющими выходами блока.На фиг, 1 приведена структурная схе ма устройства; на фиг. 2 - структурная схема блока проверки условий.Устройство содержит каналы 1 - 3, регистр 4 адреса, блок 5 памяти микропрограмм, блок 6 проверки условий, элемент ИЛИ 7, триггер 8, вход 9 запроса устройства, группу информационных входов 10, устройства, вход 11 логического 85 4нуля устройства и группу информационных выходов 12 устройства.Блок 6 проверки условий содержит счетчик 13, дешифратор 14, коммутатор 15,Блоки 5 памяти предназначены для хранения микропрограмм работы операционных устройств, причем в каждом блоке.может храниться микропрограмма работы своего устройства или в нескольких блоках могут храниться различные микропрограммы работы одного устрояства.Блок 6 проверки условий, включающий дешифратор микрокоманд и счетчик адреса, предназначен для формирования адресаследуншей микрокоманцы в зависимос;ти от осведомительных сигналов логических условий, поступающих на его управляющие входы 10. Триггеры 8 предназначены для запоминания запросов на выполнение микропрограмм. Регистры 4 . предназначены для хранения адреса очередной микрокоманды.При поступлении запроса на вьгполнение микропрограммы какого-либо канапа этот запрос запоминается соответствую-. щим триггером 8. Единичное состояние триггера свидетельствует о том, что получен запрос на выполнение данной микропрограммы, но выполнение этой микропрограммы не закончено. Адрес очередной микрокоманды формируется блоком 6 проверки условий в зависимости от осведомительных сигналов логических условий, поступающих на его входы. Запись адреса очередной микрокоманды в регистр 4 адреса производится по его информационным входам с адресных выходов блока 6 проверки условий. С выхода регистра 4 адрес очередной микро- команды передается на вход блока 5 памяти микропрограмм, В случае отсутствия запросов на выполнение микропрограмм управления операционными устройствами микропрограммами всех каналов проводится циклическая проверка своих запросов. При поступлении запроса на выполнение микропрограммы какого либо канала, например третьего, сигнал с единичного выхода триггера 8 этого канала поступает на управляющий вход соответствующего блока 6 проверки условий, при этом формируется микрокоманда ус,ловного перехода к анализу отсутствия запросов более высокого приоритета. Поскольку запросов на выполнение более приоритетных микропрограмм не поступает, то с единичных выходов триггеров 8 первого 1 и второго 2 каналов на управляющие входы блока проверки условий 63 10 15 20 1. Микропрограммное устройство управления, содержащее каналы, в в каждом канале - блок памяти микропрограмм, З 0 блок проверки условий, регистр адресаи триггер, причем в каждом канале выход регистра адреса соединен с адреснымвходом блока памяти микропрограмм,группа адресных выходов которого соединена с группой информационных входов 3блока проверки условий, группа выходовкоторого соединена с группой информационных входов регистра адреса, первыйуправляющий выход блока проверки условий соединен с нулевым входом триггера, 40первая группа управляющих входов блокапроверки условий соединена с соответствующей группой информационных входовустройства, единичный вход триггерасоединен со входом запроса устройства,группа информационных выходов блокапамяти микропрограмм соединена с соответствуквцей группой информационных вы-,ходов устройства, о т л и ч а ю щ е ес я тем, что, с целью расширения функф 0 циональных возможностей за счет выполнения приоритетных отношений междувсеми выполняемыми микропрограммами,оно содержит в каждом канале элементИЛИ, причем первый вход элемента ИЛИ И канала соединен со вторым управляюпшмвыходом блока проверки условий, второй,вход элемента ИЛИ каналов начиная совторого соединен с выходом элемента 5 95 третьего 3 канала поступают сигналы об отсутствии запросов более высокого приоритета, Порядок, в котором производится анализ запросов более высоких приоритетов, не имеет значения, так как при наличии хотя бы одного любого из этих запросов формируется микрокомвнда условного перехода к началу анализа всех запросов более высокого приоритета.Рассмотрим работу устройства в случае прерывания выполняемой микропрограммь например, третьего квнапа, более приоритетной микропрограммой, например, первого канала, В режиме ожидания запроса микропрограмма циижчес- . ки опрашивает условие наличия запроса, Запрос на выполнение микропрограммы первого канала 1 запоминается триггером 8 первого канала. Поскопьку условие наличия своего запроса для первого канала выполнилось а запросов более высокого приоритета дпя первого канала не существует, то микропрограмма вы,дает микрокоманду на прерывание ьекропрограммы меньшего приоритета. При этом сигнал прерывания с первого управляющего выхода блока 6 проверки усло-, вий первого канала 1 через элементы ИЛИ 7 первого 1 и второго 2 каналов, поступает на входы установки нуля регистров 4 адреса второго . и третьего каналов, и осуществляется безусловный переход менее приоритетных микропрограмм т.е. второго и третьего каналов, к нулевому адресу, который должен соответствовать микрокоманде анализа запроса своего приоритета. При этом микропрограмма второго канала продолжает циклически анализировать условие наличия своего запроса. Для микропрограммы третьегоканала условие наличия своего запроса выполняется, так как запрос был запомнен триггером 8 третьего канала и триггер не был установлен в нулевое положение последней микропрограммой, поекопьку микропрограмма была прервана. Микропрограмча третьего канала переходит к анализу отсутствия запросов большего приоритета. Так как на управпякиций вход блока проверки условий 6 третьего кана. ла 3 с нулевого выхода триггера 8 первого канала 1 не поступает сигнала об отсутствии запроса, поскольку триггер находится в единичном состоянии, то микропрограмма третьего канала циклически проводит анализ запросов более высокого приоритета, т.е, первого и второго каналов. По окончании выполнения микропрограммы первого канала последней ее микрокомандой триггер 8 первого канала 1 устанавливается в нулевое состожие. При этом микропрограмма первого канала переходит к циклическому анализу своего запроса, а с нулевого ппеча триггера 8 первого канала 1 на управляющий вход блока 6 проверки условий третьего канала 3 передается сигнал об отсутствии запроса первого приоритета, вследствие чего в третьем канале 3 формируется микрокоманда условного перехода к продолжению микропрограммы. Информация для внешних устройств, с которыми работает микропрограммное устройство управления, передается на группу выходов 12,Применение изобретения позволяет расширить функциональные возможности устройства за счет выполнения приоритетных отношений между микропрограммами. 2 формула изобретения7 988 О 88 8ИЛИ предыдущего канала, второя вход татора и группой информационных входов, элемента ИЛИ первого канала соединен блока, группа выходов счетеюса соединесо входом логического нуля устройства, на с первой группой входов деинфратора, выход элемента ИЛИ каждого-го ка- вторая группа входов которого соедннаи нала соединен с управляющим входом ре- ф с первой н второй группами управляющнх гнстра адреса ( 1 + 1)-го канала, еду- входов блока, выход дешнфратора соеднннчнйй выход, триггера каждого канала нен со входом коммутатора, группа высоедвнен с первьм управляющим входом ходов которого соединена с группой вывторой группы входов блока нроверкн ус- ходов блока, первый н второй выходы повий своего канала, нулевой" выход триг счетчика соединены соответственно с гера каждого канала соединен с удрав- первым н вторым управлякацими выкодалякацнми входами второй группы входов ми блока.. блоков проверки условий всех последую- Источники информации,3 пях каналове принятые во внимание при экспертизе2. Устройство по и. 1, о т л н ч а. - 1 э 1. Авторское сищетельство СССР ю щ е е с я тем, что, блок проверки ус- % 437072, кл, С 06 Р 9/22, 1972. повий содержит децпфратор, счетчнк н 2. Авторское свидетельство СССР коммутатор, причем группа входов счет- М 643874, кл. С 06 Р 9/22, 1976 чика соединена с группой входов комму- (прототвп.,1ого комитений и5, Ра Подлисное ета СССР крытий ская наб., д. 4/

СмотретьЗаявка

2921715, 07.05.1980

ПРЕДПРИЯТИЕ ПЯ Г-4152

БЕРСОН ГЕРМАН ЗАЛКОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/5-955055-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Стохастический дифференциатор

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для измерения характеристик морских ветровых волн