Устройство для вычисления параметров экспоненциальных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 911524

Авторы: Головченко, Гусев, Редько, Рудковский

Текст

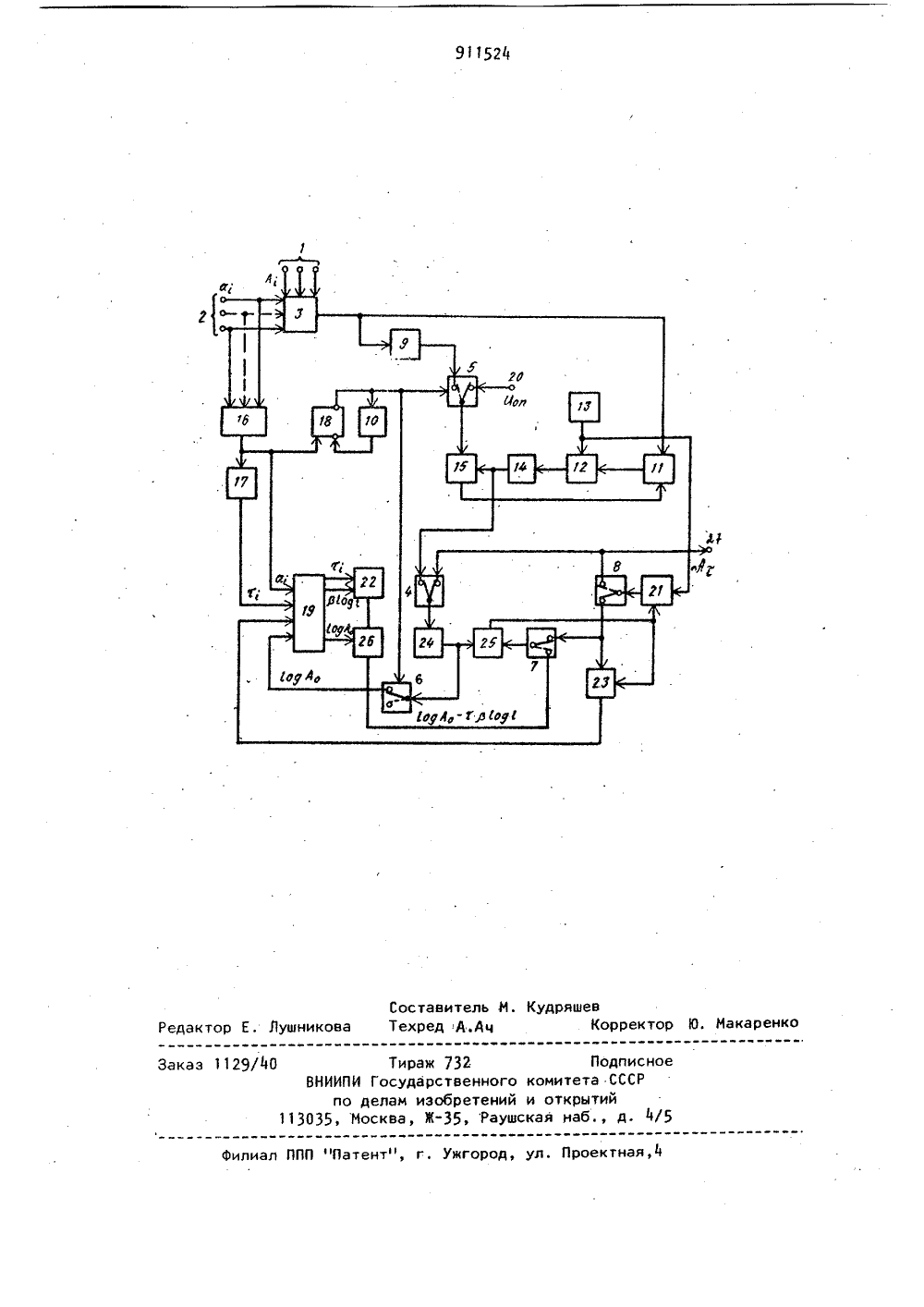

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическиеРеспублик и 911524(51)М. Кл. 6 06 Р 7/556ркудвретеенныйквинтет СССР ве делан изобретений и етерыткй(23) Приоритет Опублнковано 07.03.82, Бюллетень,В 9 Дата опублнковання описания 07.03 82(71) Заяентел 4) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПАРАМЕТРО ЭКСПОНЕНЦИАЛЬНЫХ ФУНКЦИЙПредлагаемое изобретение относится к вычислительной и преобразовательной технике и может быть использовано для исследования парамет. ров экспоненциальных функций.Известно устройство для измерения логарифмического декремента колебаний 1 1.Однако устройство не позволяет определить величину , характеризующую параметры цепи, влияющие на затухание сигнала, а лишь кон" статирует сам факт затухания и оп" ределяет его декремент. Кроме того устройство не позволяет прогнозировать значение экспоненциальной функции во времени.Наиболее близким по технической сущности к предлагаемому является устройство, содержащее логические элементы, переключатели блок умножения, цифроаналоговый преобразователь, счетчики и блок сравнения 2 1,Однако при помощи этого устрой. ство можно лишь вычислять логариф"мические и показательные функциипо заданному значению основания(степени) Функции.Цель изобретения - расширение об" ласти применения устройства.Поставленная цель достигается тем, что в устройство для вычисления параметров экспоненциальных функций, содержащее два переключателя, умножитель, первый элемент И, логарифматор, два счетчика, первую схему сравнения и цифроаналоговый пре" образователь, причем выход логариф матора соединен с первым вхэдом первой схемы сравнения, вход логарифматора соединен с выходом первого переключателя, выход первой схемы сравнения соединен с первым входом первого счетчика, информационный выход устройства соединен с первыми входами первого и второго переключателей, введены коммутатор,9115 244схемы сравнения, выход вычитателясоединен со вторым входом пятого переключателя, выход которого соединен со вторым входом первой схемысравнения.На чертеже приведена структурнаясхема устройства.устройство содержит группу информационных входов 1 устройства, группу управляющих входов 2 устройства,коммутатор 3, переключатели 4-8,элемента 9 и 1 О задержки, схема 11сравнения, элемент И 12, генератор13 импульсов, счетчик 4, цифроаналоговый преобразователь 15, элемент ИЛИ 16, таймер 17, триггер 18,блок 19 памяти, вход 20 отпорногонапряжения устройства, счетчик 21,умножитель 22, делитель 23, логарифматор 24, схема 25 сревнения, вычитатель 26, информационный выход 27устройства.Коммутатор 3 предназначен для подачи входных сигналов с группы входов 1 под управлением сигналов группы входов 2. Элемент задержки 9предназначен для задержки входныхсигналов по отношению к сигналам свыхода счетчика 14, схема 11 сравнения предназначена для сравнениявходного сигнала с сигналов с выхода преобразователя 15. Генератор13 импульсов и элемент И 12 предназначены для подачи тактовых сигналов на вход преобразователя 15. Элемент ИЛИ 16 предназначен для запуска таймера 17, который в свою очередь обеспечивает временную диаграмму работы блока 19 памяти. Триггер18 предназначен для переключения.переключателей 5 и б, Элемент 1 О задержки предназначен для сброса триггера 18, вхоц 20 - для подачи опорного напряжения на вход устройства.А = А о В- функция исследуемого сигнала А .;А , А , А - значения исследуемого сигнала,начальное в момент й , измеренное в моментй и вычисленноеустройствомв момент- параметр цепи,учитывающийформу экспоненты,- время; 10 элемент ИЛИ, таймер, блок памяти, третий, четвертый и пятый переключа,тели, триггер, два элемента задержки, генератор импульсов, вычитатель, вторая схема сравнения и делитель, причем первая и вторая группы входов коммутатора являются соответственно группой информационных и группой управляющих входов устройствагруппа управляющих входов устройства соединена с группой входов элемента ИЛИ, выход которого соединен с единичным входом триггера, с первым входом блока памяти и с входом таймера, выход которого соединен со вторым входом блока памяти, выход33 коммутатора соединен с первым входом второй схемы сравнения и через перивыи элемент задержки с первым входом третьего переключателя, нулевой выход триггера соединен с входом второго элемента задержки, с управляющим входом третьего переключателя и с управляющим входом четвертого переключателя, выход второго элемента задержки соединен с нулевым входом триггера, первый и второй выходы блока памяти соединены с первым и вторым вхо" дами умножителя, выход которого соединен с первым входом вычитателя, второй вход которого соединен с третьим выходом блока памяти, третий и четвертый входы блока памяти соединены соответственно с выходами делителя и с первым выходом четвер- ЗЗ того переключателя, второй вход третьего переключателя соединен с выходом опорного напряжения устройства, выход третьего переключателя соединен с первым входом цифроана логового преобразователя, второй вход которого соединен с выходом второго счетчика и со вторымвходом первого переключателя, выход генератора импульсов соединен с первым 43 входом элемента И и со вторым входом первого счетчика, выход элемента И соединен с входом второго счетчика, второй вход элемента И соединен с выходом второй схемы сравнения, Ичвторои вход которой соединен с выхо" дом цифроаналогового преобразователя, выход первого счетчика соединея со вторым входом второго переключателя, выход которого соединен с первымвходом делителя и с первым входомпятого переключателя, второй входделителя соединен с выходом первой40 формула изобретения Устройство для вычисления пара 55метров экспоненциальных функций,содержащее два переключателя, умно"житель, элемент И, логарифматор,двасчетчика, первую схему сравнения и время задержки,формируемые соответственноэлемгчтами 9 и10 задержки; 511 о = соп 51 - опорный сигнал;11 Ару 11 - максимальнаяАО/А 1емкость счетчика 14 и кодыцифровых эквива- олентов аналоговых величинАои А /АУстройство работает следующим образом,15В работе устройства можно выделить три этапа: первый - вычислениелогарифма 1 од Ао начального значения Ао исследуемого сигнала А; второй - вычисление логарифма отношения 201 од - и параметра Р 1 од 6 экспоненААоциальной Функции; третий - вычислениеА исследуемого сигнала А.Первый этап. Переключатели 4-8 Иустанавливают в положения, указанныена чертеже.При подключении входа схемы 11сравнения через коммутатор 3 к соот Оветствующему входу 1 с исследуемымсигналом А , определяемом стробирующим импульсов с входа 2, происходит преобразование аналоговой величины Ар в цйфровой экивалн35 с последующим вычислением его логарифма 1 од А в логарифматоре 24 и записью значения 1 од Ар в блок 19 памяти через переключатель 6 здесь и далее для простоты объяснений аналоговые значения А и их цифровые эквиваленты И будут обозначены одним и тем же символом А). Через время задержки 1 оу на выходе триг 2 Огера 18 появляется сигнал, который переводит переключатели 5 и 6 в по 50 ложения, указанные пунктиром на чертеже,обозначающие подготовку ко второму этапу работы.Второй этап. Переключатели 5 и 6 в положениях, указанных пунктиром, переключатели 4,7,8 в положениях, указанных на чертеже. На вход преобразователя 15 и вход 20 поступают соответственно сигналы А и А-т 5 о ф 1 А М,,ИАрпропорциональное отношению в , коАь Ао торое. далее логарифмируется в логарифматоре 24, В результате этого на первый вход схемы 2. сравнения поступает значение 1 ор - и счетчикААо21 заполняется импульсами с генера" тора 13 до момента равенства значений кодов на первом и втором входах схемы 2 сравнения в соответствии с выражением 1 од - = - йр 1 од 8ААов момент равенства которого вход второго счетчика 24 заблокируется и результат деления ГоГ с выхода делителя .23 переписывается в блок 19 памяти.Третий этап. Переключатели 4,6, 7,8 переведены в положения, указанные на чертеже пунктиром. С выходов блока 19 памяти и на входы умножителя 22 и вычитателя 26 поступают соответственно значенияй Сои й и-ф 1 од А, в результате чего на втором входе блока 25 сравнения значение кода равно Ар-Г-Ъ 1 одР Уравно" вешивание кодов на первом ивтором входах схемы 25 сравнения осуществляют аналогичным второму этапу задолнения импульсами второго счетчика 21. В результате этого появление сигнала равенства на выходе схемы 25 сравнения фиксирует в счетчике, 21 значение А , которое и определяет на выходе 27 устройства конечный результат вычислений-ГА =А Р Применене изобретения позволяет расширить ебласть применения устройства91цифроаналоговый преобразователь, причем выХод логарифматора соединен с первым входом первой схемы сравнения, вход логарифматора соединен с выходом первого переключателя,выход первой схемы сравнения соединен с первым входом первого счетчика,информационный выход устройства соединен с первыми входами первого и второго переключателей, о т л ич а е щ е е с я тем, что, с целью расширения области применения устройства,оно содержит коммутатор, элемент ИЛИ, таймер, блок памяти, третий, четвертый и пятый переключатели, триггер, два элемента задержки,генератор импульсов, вычитатель, вторую схему сравнения и делитель, причем первая и вторая группы входов коммутатора являются соответственно группой информационных и группой управляющих входовЭустройства, группа управляющих входов устройства соединена с группой./входов элемента ИЛИ, выход которого соединен с единичным входом триггера, с первым входом блока памяти и с входом таймера, выход которого соединен со вторым входом блока памяти, выход коммутатора соединен с первым входом второй схемы сравнения и через первый элемент задержки с первым входом третьего переключателя, нулевой выход триггера соединен с входом второго элемента задержки, с управляющим входом третьего переключателя и с управляющим входом четвертого переключателя, выход второго элемента задержки соединен с нулевым входом триггера, первый и второй выходы блока памяти соединены с первым и вторым входами умножителя, выход которого соединен с первым входом вычитателя, второй входкоторого соединен с третьим выходомблока памяти, третий и четвертый входы блока памяти соединены соответственно с выходом делителя и с первым выходом четвертого переключателя,второй вход третьего переключателясоединен с выходом опорного напряже О ния устройства, выход третьего переключателя соединен с первым входомцифроаналогового преобразователя,второй вход которого соединен с выходом второго счетчика и со вторымвходом первого переключателя, выходгенератора импульсов соединен с первым входом элемента И и со вторымвходом первого счетчика, выход элемента И . соединен с входом второгосчетчика, второй вход элемента И соединен с выходом второй схемы сравнения, второй вход которой соединен свыходом цифроаналогового преобразователя, выход первого счетчика соединен со вторым входом второго переключателя, выход которого соединенс первым входом делителя и с первымвходом пятого переключателя, второйвход делителя соединен с выходомпервой схемы сравнения, выход вычитателя соединен со вторым входомпятого переключателя, выход которогосоединен со вторым входом первойсхемы сравнения.35 Источники информации, принятые во внимание при.экспертизе1. Авторское свидетельство СССРМ 481918, кл. С 06 Р 3/00, 1974.2. Авторское свидетельство СССРйф 634308, кл, б 06 Р 3/00, 19769 1524 Составитель М. КудряшевТехред Д.Дч Корректор Ю. Макаренг дактор Е. Лушнико Тираж 732 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2890619, 04.01.1980

КИЕВСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "АНАЛИТПРИБОР"

РУДКОВСКИЙ СТАНИСЛАВ ИВАНОВИЧ, ГОЛОВЧЕНКО ПЕТР ФЕДОРОВИЧ, РЕДЬКО СЕРГЕЙ КУЗЬМИЧ, ГУСЕВ ВСЕВОЛОД МАКСИМОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, параметров, функций, экспоненциальных

Опубликовано: 07.03.1982

Код ссылки

<a href="https://patents.su/5-911524-ustrojjstvo-dlya-vychisleniya-parametrov-ehksponencialnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления параметров экспоненциальных функций</a>

Предыдущий патент: Устройство для вычисления логарифмов чисел, представленных число-импульсным кодом

Следующий патент: Частотное делительное устройство

Случайный патент: Способ выделения продуктивных нефтяных пластов в процессе бурения