Формирователь управляющих сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 896774

Автор: Мареев

Текст

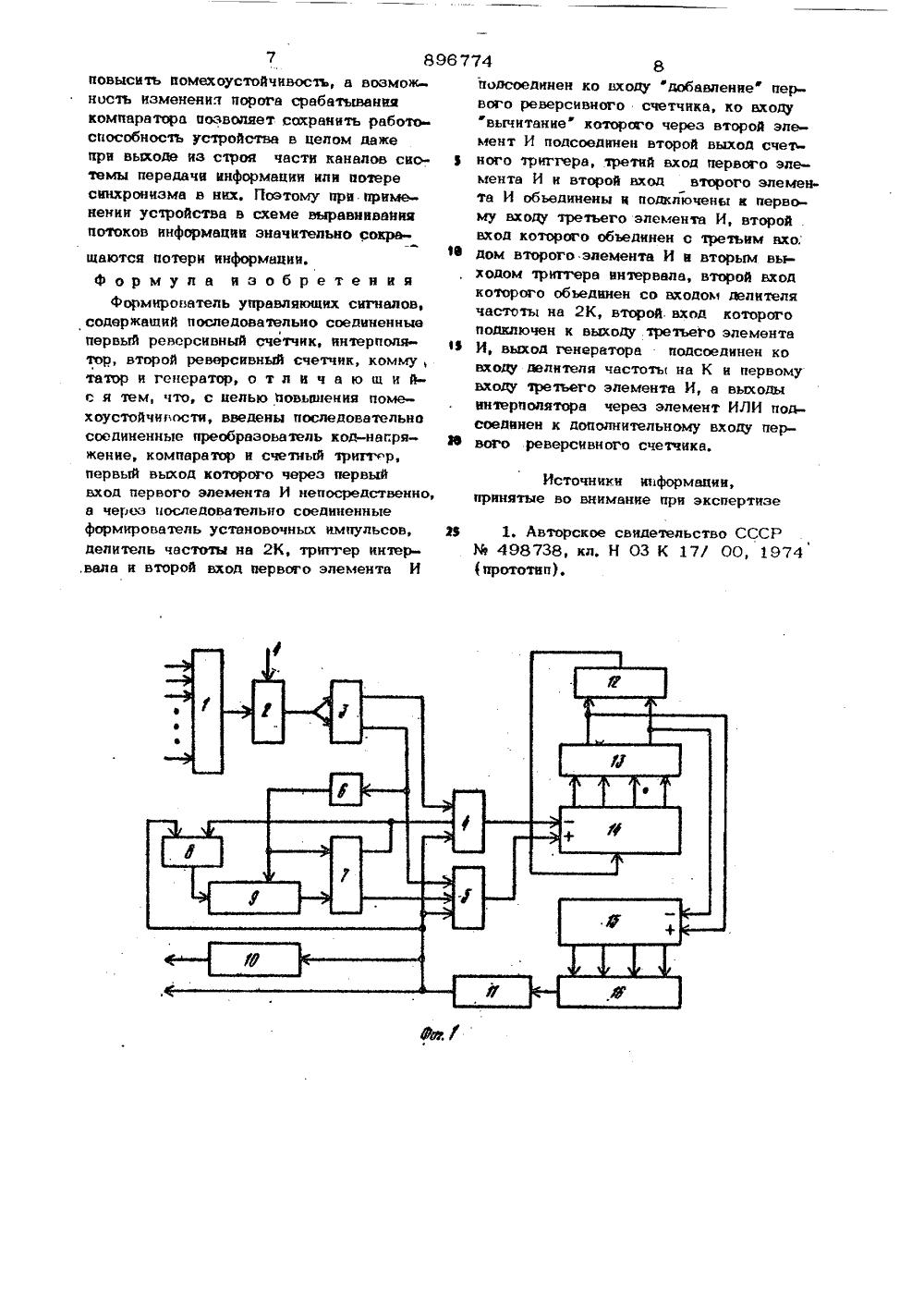

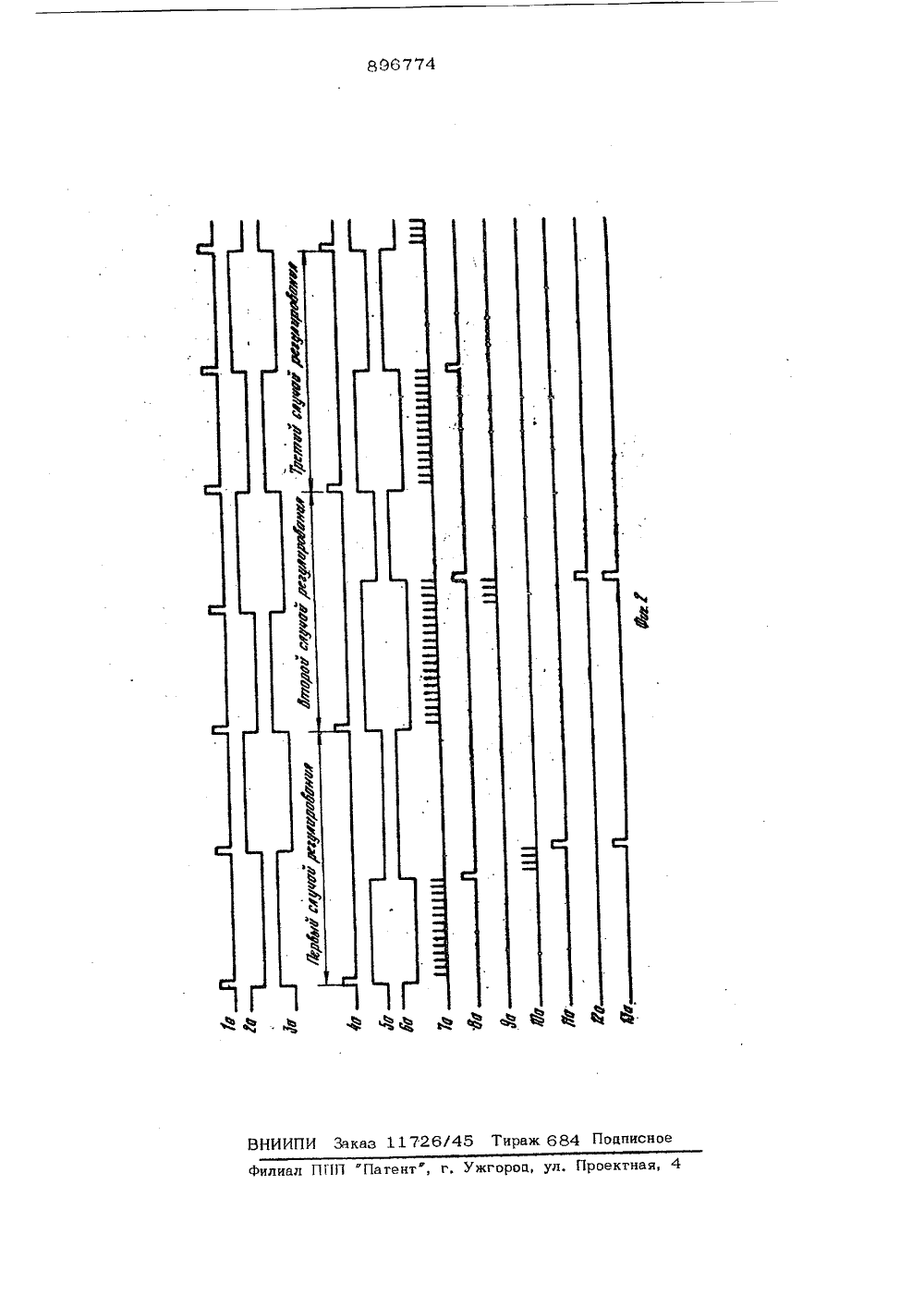

ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Совет скикСоциалистическиеРеспублик 896774 6 ) Дополнительное к авт, свид-ву. Кл.04 ХЗ/ОЗК 17 с присоединением заявки РЙ(23) П риоритет Государственный комнте СССР,82. Бюллетен Опубликованб 07 лам изобретеннни открытий ЮК 625,394,14(088 8) ата опубликования описания 07.01 72) Автор изобретен Мареев(54) ФОРМИРОВАТЕЛЬ УПРАВЛЯЮ ойства является нес многоканальным оме того, устройвеняо,Устройство относится к передаче и обработке информации в многоканальных цифровых системах с цикловой синхронизацией, в которых синхросигнал паредаевся в виде последовательности чередующихся маркерных синхрогрупп двух видов, когда длина цикла во всех каналах одинакова, однако маркеры различных каналов смещены во времени относительно друг друга, т. е, .преимущественно в многоканальных цифровых системах связи, телеизмерения, передачи изображения, а также в многоканальных цифровых магнитофонах с высокой плотностью записи, когда имеет место взаимный перекос каналов движущегося носителя записи.Известно устройство, содержащее по следовательно соединенные первый ревер сивный счетчик, интерполятор, второй реверсивный счетчик, коммутатор и генератор 1 )Недостатком устрвозможность работывходным потоком. Кр ство не может быть использовано для работы с входным потоком в виде последовательности откликов нв маркерные синхрогруппы, так как в этом случае точность регулирования, определяемая длительностью цикла, т. е, интервалом между двумя маркерами, окажется недостаточной для подстройки символьной частоты. При этом недопустимо больщим будет время подстройки частоты генера.0 тораЦель изобретения - повьпаение помехоустойчивости.Для достижения цели в формировательуправляющих сигналов, содержащий последовательно соединенные первый реверсивный счетчик, интерполятор, второй реверсивный счетчик, коммутатор и генератор, введены последовательно со единенные преобразователь код-напряжэ нив, компаратор и счетный триггер, первый выход которого через первый вход первого элемента И непосредст а через последовательно соединенные10 30 Устройство работает следующим образом.В информационной цифровой последовательности каждого канала содержатся циклически расположенные чередующиеся маркерные синхрогруппы двух видов. Блина информационного цикла во всех каналах одинакова, однако маркеры различйых , каналов смещены во времени друг от носительно друга. 50 Структура и взаимное расположение информационных последовательностей в каналах показаны на эпюрах (фиг. 2 строки 1-4 а), В каждом канале с помощью чередующихся маркеров М 1 и М 2 образованы циклы длиной К символов, Хотя длина циклов во всех каналах одинакова, цикловые стробы (фиг. 2. строки 5-8 В), соответствующие строкам 1-413,55 формирователь установочных импульсов, делитель частоты на 2 К, триггер интервала и второй вход первого элемента И подсоединен ко входу "добавление" первого реверсивного счетчика, ко входу, вычитание" которого через второй элемент И подсоединен второй выход счет. ного триггера, третий вход первого. элемента И и второй вход второго элемента И обьединены и подключены к первому входу третьего элемента И, второй вход которого объединен с третьим входом второго элемента И и вторым выходом . триггера интервала, второй вход которого обьединен со входом делителя чаь тоты на 2 К, второй вход которого подключен к выходу третьего элемента И; выход генератора подсоединен ко входу делителя частоты на;К и щервому входу третьего элемента И, а выходы интер полятора через элемент ИЛИ подсоединены к дополнительному входу первого реверсивного счетчика.На фиг, 1 представлена структурно- электрическая схема формирователя управляющих сигналов, на фиг, 2 - эпюры, поясняющие работу устройства.Формирователь управляющих сигналов содержит преобразователь 1 код-напряжение, компаратор 2, счетный триггер 3 первый элемент И 4, второй элемент И 5, формирователь 6 установочных им пульсов, триггер 7 интервала, третий элемент И 8, делитель 9 на 2 К, делитель 10 на к, генератор 11, элемент ИЛИ 12, интерполятор 13, первый реверсивный счетчик 14, второй реверсивный счетчик, 15 и коммутатор 16. смещень двуг относительно друга, какза счет смещения маркеров, так и изза наличия холостых" слоев, длиной исимволов,Очевиднс что нельзя использоватьдля управления частотой считывания цикловые стробы какого-либо одного канала, так как их длительность и положениево времени существенно изменчивы, кроме того при выходе из строя выбранногоканала устройство в целом окажется неработоспособным. Поэтому для управления частотой необходимо сформироватьобобщенный цикловой строб по всем каналам. Лля этого цикловые стробы с первых входов 2 -21,1 устройства поступают на входы преобразователя 1 код-напряжение, на выходе которого начинаетнарастать напряжение (фиг, 2 строка 9 ц).Выход преобразователя 1 код-напряжениесоединен с первым входом компаратора2, на второй вход которого подан опорный сигнал Ез со второго входа устройства. Импульс на выходе компаратора 2появляется в момент (фиг. 2, стро -ка 1 ОО), когда на входы преобразовате,ля 1 код-напряжение поступает некоторое наперед заданное число положительных цикловых стробов любых каналов инапряжение на его выходе превышаетопорный сигнал Ео . Это чиспо предпочтительно выбирать равным половинечисла каналов, так как тогда работоспособнссть устройства в целом сохраняется при выходе из строя до половиныканалов или потере синхронизма в них.Импульсная последовательность с выхода компаратора 2 (фиг. 2, строки 1 Оили 10 с 1 ) поступает на вход счетноготриггера 3, на выходе которого образуется в общем случае несимметричный .инепостоянный по периоду меандр (фиг. 2,строки 20 и За).Несимметричность вызывается смещением маркеров в каналах от цикла к циклу, а изменения периода вызываются,например при магнитной записи, вариациями скорости носителя записи и появления за счет этого "холостых" слоевв цикле, Несимметричность и непостоян,ство периода выходного сигнала счетного триггера 3 являются первичными управляющими воздействиями для управления частотой считывания.Положительным перепадом второговыхода счетного триггера 3 с помощьюформирователя 6 установочных импульсов (фиг, 2, строка 4 О) триггер 7 ин896774 терввла и делитель 9 на 2 К устанавливаются в начальное состояние, в резуль-тате чего опсрывается третий элементИ 8 и на счетный вход делителя 9 на2 К начинают поступать импульсы символьной частоты с выхода генератора 11(фиг. 2, строки 5 о и 7 д), После этогокак делитель 9 на 2 К отсчитает 2 Кимпульсов, он формирует сигнал (фиг. 2,строка 80), который перебрасывает триггер 7 интервала, который закрывает третий элемент И 8, до прихода следующегоимпульса с выхода формирователя 6 установочных импульсов.При работе устройстьа возможны трислучая регулирования.1, Частота генератора 11 выше средней скорости поступления информации всхему выравнивания,В этом случае длительность положительного строба со второго выхода счетного триггера 3 (фиг. 2, строка 300 больше длительности отрицательного стробасо второго выхода триггера 7 интервала(фиг. 2, строка 6 О), определяемого временем счета 2 К импульсов генератора11 в делителе 9 на 2 К. Тогда черезвторой элемент И 5 на суммирующийвход первого реверсивного счетчика 14поступает количество импульсов, пропорциональное разности между длительностями стробов счетного триггера 3 и триггера 7 интервала (фиг, 2, строки 104 ),Если в результате суммирования состояние первого реверсивного счетчика14 достигает некоторого числа Й с.тона первом выходе интерпсаятора 13 появляется импульс (фиг. 2, строка 11 с 1),который поступает на вычитающий входвторого реверсивного счетчика 15 и уменьшает его состояние на единицу, в результате чего коммутатор 16 .уменьшает частоту генератора 11,Одновременно импульс с первого выхода интерполятора 13, пройдя через элемент ИЛИ 12 (фиг. 2, строка 1 ЗС) устанавливает первый реверсивныя счетчик14 в начальное состояние, равное некоторому йср, которое выбрано междуй -,и Йрсс,Иалее процесс подстройки частотыгенератора 11 продолжается аналогичнописанному до тех пор пока длительгность строба триггера интервала 7 станет равной длительности строба счетного триггера 3,2, Частота генератора 1 1 ниже средней скорости поступления информации всхему выравнивания,4В этом случае (фиг. 2, строки 2, 5, 9 О) через первый элемент И 4 на вычитающий вход первого реверсивного счетчика 14 поступает ксаичество импульсов пропорциональное разности между длительностями положительного строба первого выхода триггера 7 интервала и отрицательного строба первого выхода счетного триггера 3. Если в результате вычитания состояние первого реверсивного счетчика 14 достигает некоторого числа Мюи, то на втором выходе интерполятора 13 появляется импульс (фиг. 2, строки 12 О),1 ф который поступает на суммирующий вход второго реверсивного счетчика 15 и увеличивает его. состояние .на единицу, в результате чего коммутатор 16 увеличивает частоту генератора 11.Одновременно импульс со второго выхода интерпопятора 13, пройдя через элемент ИЛИ 12 (фиг. 2, строка 130), устанавливает первый реверсивныи счетчик 14 в начальное состояние, равное некоторому Мр, которое выбрано между Мспту " ауПалее процесс подстройки частоты ге- нератора 11 продсажается аналогично описанному до тех пор, пока .длительность строба триггера 7 интервала станет равной длительности строба счетного триггера 3.3. Частота генератора 11 соответствует средней скорости поступления информации в схему выравнивачия. В этом случае стробы счетного триггера 3 и триггера 7 интервала равны, поэтому первый и второй элементы И 4 и 5 закрыты для прохождения через их третьи входы. импульсов генератора 11 нв входы первого реверсивного счетчика 14.В результате состояния первого и второго реверсивных счетчиков 14 и 15 остаются неизменными и коммутатор 16 не изменяет . частоту генератора 11,симвсаьная частота которого поступает на первый выход устройства, а цикловая частота считывания, получаемая делением символьной в К раз на делителе 10 на К, поступает ыа второй выход устройства.Таким образом, устройство осуществляет слежения за средней скоростъю поступления информации и через каждые четыре канальных цикла производят .подстройку частоты генератора. Предлагаемый формирователь управляющих сигналов позволяет существенно .повысить помехоустойчивость, а возмож ность изменения порога срабатывания компаратора позволяет сохранить работоспособность устройства в целом даже при выходе из строя части каналов сиотемы передачи информации или потере синхронизма в них. Поэтому при применении устройства в схеме выравнивания потоков информации значительно сокращаются потери информации.формула изобретенияформирователь управляющих сигналов, содержащий последовательно соединенные первый реверсивный счетчик, интерполятор, второй реверсивный счетчик, комму, татор и генератор, о т л и ч а ю ш и йс я тем, что, с целью повьпнения помехоустойчивости, введены последовательно соединенные преобразователь код-напряжение, компаратар и счетный триггерр, первый выход которого через первый вход первого элемента И непосредственно, а через последовательно соединенные формирователь установочных импульсов, делитель частоты на 2 К, триггер интер,вала и второй вход первого элемента И 6774 8подсоединен ко входу "добавление первого реверсивного счетчика, ко входувычитание" котора о через второй эльмент И подсоединен второй выход счеъ-ного триггера, третий вход первого элемента И и второй вход второго элемента И объединены и подключены к первому входу третьего элемента И, второй .вход которого объединен с третьим вхо;1 Е дом второго элемента И и вторым выходом триггера интервала, второй входкоторого объединен со входом делителячастоть 1 на 2 К, второй вход которогоподключен к выходу .третьего элемента 1 И, выход генератора подсоединен ковходу делителя частотъ на К и первомувходу третъего элемента И, а выходыинтерполятора через элемент ИЛИ подсоединен к дополнительному входу пер 3 ф вого реверсивного счетчика.Источники информации, принятые во внимание при экспертизе1 1. Авторское свидетельство СССР М 498738, кл, Н 03 К 17/ 00, 1974 4 прототип).896774 ьфь НИИПИ Заказ 11726/ илиал ППП "Патент", г, Ужго ж 684 Подпис Проектная,

СмотретьЗаявка

2898358, 20.03.1980

ПРЕДПРИЯТИЕ ПЯ В-8466

МАРЕЕВ ИГОРЬ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04J 3/02

Метки: сигналов, управляющих, формирователь

Опубликовано: 07.01.1982

Код ссылки

<a href="https://patents.su/5-896774-formirovatel-upravlyayushhikh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь управляющих сигналов</a>

Предыдущий патент: Устройство для обнаружения и измерения инфранизкочастотных сигналов на фоне периодической помехи

Следующий патент: Устройство для асинхронной передачи цифровой информации по синхронному каналу связи

Случайный патент: Камера сгорания