Устройство для вычисления диаграмм разрежения индикаторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 873245

Авторы: Белоусов, Мурахлямов, Пушкарь, Ратманский, Тищенко

Текст

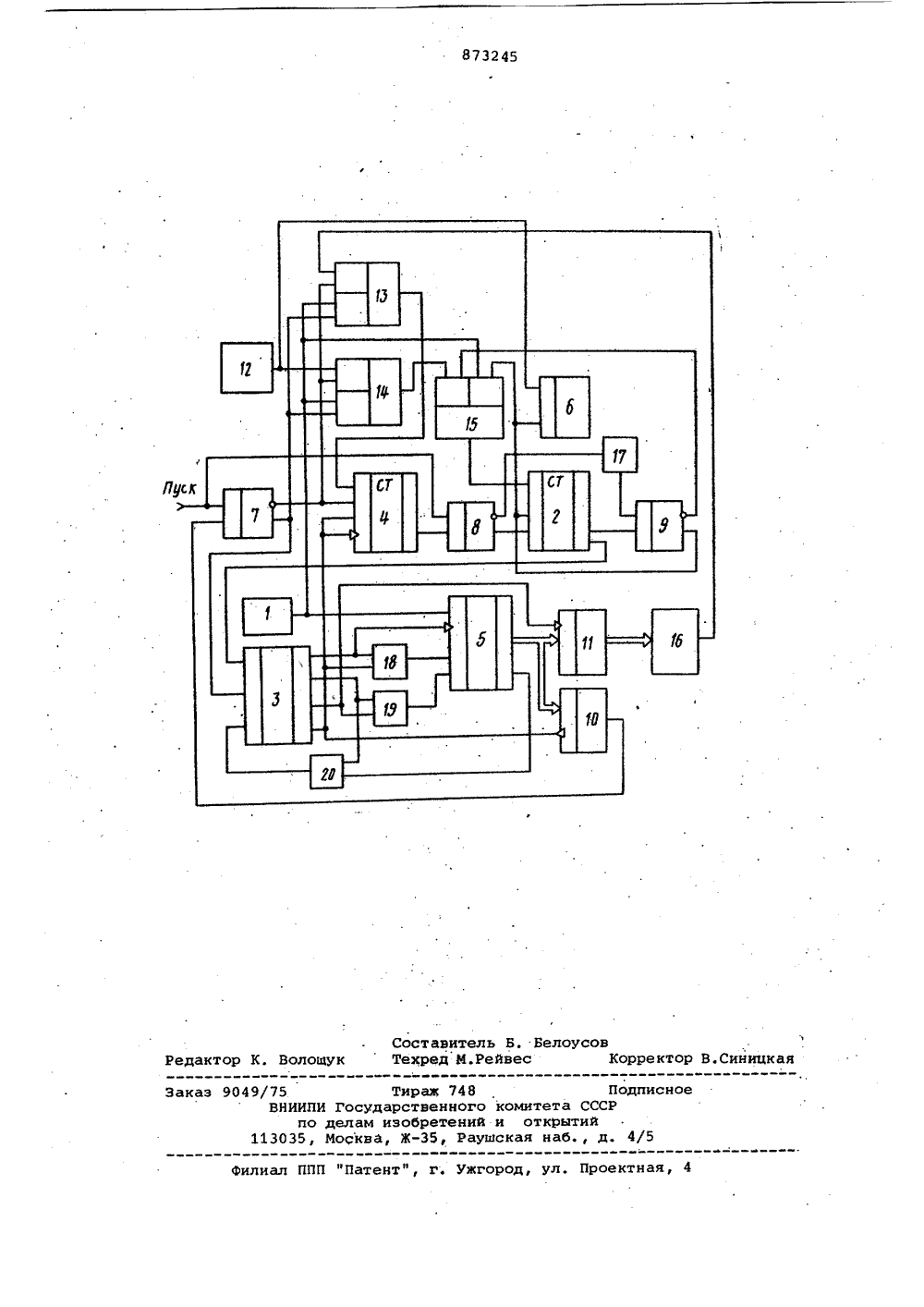

ы которых соецинены с входм устрой-ства, первый выход первого триггера соединен с первым входом интегратора, первый выход которого соединенс первым входом распределителя, первый выход которого соединен с первымвходом первого элемента.ИЛИ и вторымвходом первого счетчика, второй выход распределителя соединен с первыми входами элемента И и второго эле,мента ИЛИ, выход которого соединен стретьим входом первого счетчика, выход которого через элемент И соединенс вторым входом распределителя, третий выход которого соединен ао вторыми входами второго элемента ИЛИ и регистра, выход которого соединен с вхо-дом преобразователя код - частота,четвертый выход распределителя соедиЮен с первым и вторым входами второгосчетчика, вторыми входами дешифрато. -ра и первого элемента ИЛИ, выход кото рого соединен с четвертым входом пер.вого счетчика, выход дешифратора соединен с вторым входом второго триггера, первый выход которого соединенсо вторяк входами первого и второго 2элементов 2 И-ИЛИ и.третьим входомвторого счетчика,выход которого соединен с вторым входом первого триггера, второй выход второго триггерасоединен с третьим входом распределителя и третьими входами первого и второго элементов 2 И-ИЛИ, четвертые входы которых соединены соответственнос выходами преобразователя код - частота и генератора и выход первогоэлемента 2 И-ИЛИ соединен с четвертымвходом второго счетчика, третий счетчик, дополнительно введены элементзадержки, третий триггер и третийэлемент 2 И-ИЛИ, причем второй выходпервого триггера соединен с входом 40схемы задержки, выход которой соединен с первым входом третьего триггера, второй вход которого соединен свторым выходом интегратора, второйвход которого соединен с первым вы- ,.4ходом третьего триггера и первыми входами третьего элемента 2 И-ИЛИ и третьего счетчика, вторые входы которыхсоединены соответственно с выходамифункционального преобразователя и 5 ргенератора, второй выход третьеготриггера соединен с третьим входомтретьего элемента 2 И-ИЛИ, четвертыйвход которого соединен с выходом второго элемента 2 И-ИЛИ, а выход - стретьим входом интегратора.На чертеже показана блок-схемапредлагаемого устройства.Устройство додержит функциональный преобразователь 1, выдающий электрический сигнал в виде частоты импульсов, пропорциональный амплитудедиаграьвы Разрежения, интегратор 2,распределитель 3, счетчики 4-6,триггеры 7-9, дешифратор 10, регистр11, .генератор 12, элементы 2 И-ИЛИ 13-.15, преобразователь 16 код - частота, элемент задержки 17, элементыИЛИ 18 и 19, элемент И 20.Устройство работает следующим образом,В исходном состоянии интегратор 2,счетчики 4-6, триггеры 7-9, регистр11 и распределитель 3 установлены внулевое состояние. Пуск устройстваЬсуществляется подачей импульса наединичные входы триггеров 7 и 8, которые при этом устанавливаются в единичное состояние и открывают элементы2 И-ИЛИ 13 и 14, распределитель 3 иинтегратор 2. Последний начинает интегрировать входной сигнал путем счета числа импульсов, поступающих наего счетный вход с выхода первогоэлемента 2 И-ИЛИ 14.Первый цикл работы устройства начинается при поступлении на вход интегратора 2 числа импульсов, равного4 й, когда на его импульсном выходевозникает первый импульсный сигнал,запускающий распределитель 3. Далеена первом выходе распределителя временно появляется разрешающий потенциал,поступающий через элемент ИЛИ18 на управляющий вход сложения счетчика 5, который за это время зарегистрирует среднюю частоту импульсов, йоступающих на его вход с вйсода функционального преобразователя 1. Припоступлении очередных Ьй импульсовна вход интегратора 2 сигнал с выхода последнего запускает распределитель 3, на втором выходе которогбпоявляется временно разрешающий.по.тенциал, поступающий через элементИЛИ 19 на управляющий вход вычитаниясчетчика 5. При этом из первого значения средней частоты импульсов вычитается второе значение средней частоты импульсов. Поскольку на участкеподъема амплитуды диаграммы разрежения последующее значение средней частоты импульсов всегда больше предыдущего, то возникающий на выходе переноса счетчика 5 импульс поступает через открытый во втором такте элементИ 20 на установочный вход распределителя 3, устанавливая его в исходноесостояние.Аналогичным образом йроисходит работа и во всех последующих циклах наподъеме диаграмьы разрежения, когдакаждый цикл сравнения содержит дватакта измерения.После достижения максимального значения на диаграмме разрежения имеется участок, где средняя частота им- .пульсов, т.е. усредненное значениеамплитуды диаграммы разрежения, начинает умещшутся по экспоненте п(й)д ( со ) 2 О (1 ) и распределитель3 начинает работать циклически по четыре такта в каждом цикле. При этомв первом такте счетчик 5 работает насложение, во втором и тоетьем - на вывычитание и в четвертом - снова насложение. В конце четвертого тактакаждого цикла проверяется справедливость равенства и (со) - и ( ) - и(с )+й,+и0 (2) путем подключения дешнфратора 10 к счетчику 5. Так как в начальный период после достижения мак 5симума. амплитуда диаграммы разрежения уменьшается не строго по экспоненциальной зависимости (1), то равенство (2) не соблюдается, сигнал навыходе дешифратора 10 отсутствует и 1 Оинтегратор 2 по-прежнему продолжаетсчитать сумму всех импульсов, кото,рые поступают с функционального преобразователя 1 через элемент 2 ИИЛИ 14. 15На участке экспоненциальной зависимости средней частоты имйульсов отвремени равенство. (2 ) соблюдается,поэтому дешифратор 10 в очередномцикле, а именно в конце четвертого 20такта, выдает сигнал, который поступает на вход установки в нулевоесостояние триггера 7., в результатечего элементы 2 И-ИЛИ 13 и 14 закрываются по первым управляющим входам .ищоткрываются по вторым управляющим.входам, К этому моменту времени интегратор 2 зарегистрирует суммарноечисло. импульсов, равное Х и(й)д 1,поступающих на его вход за время.от начала интегрирования до моментадостижения равенства (2), а регистр11 - разность средних частот и(со )"и(С ) КЬЙ, которая переэаписываетсяиз счетчика 5 в регистр 11 в началетретьего такта, когда передний фронтразрешающего потенциала с выхода распределителя З.поступает на вход регистра 11. В счетчике 4 регистрируется число и(с ), которое равно средней частоте имйульса в четвертом такте, когда разрешающий потенциал с выхода распределителя поступает на входсчетчика 4. На выходе преобразователякод - частота 16, коэффициент преобразования которого устанавливают рав,ьным (, где Ь - целое положительноеофчисло, появляется частота Ф К Ьй - =айф К которая через открытый элемент 2 Й-ИЛИ 13 начинает поступать навход счетчика 4. С этого момента счетчик работает на вычитание. Одновременно частота Г= 10 Р с выхода генератора 12 через открытый элемент 2 И-ИЛИ14 начинает поступать на вход интегратора 2, появляющиеся импульсы навыходе которого уже не запускают распределитель 3, поскольку последнийзакрыт по управляющему входу.Интегратор 2 считает импульсычастотой 1 в течение времени, пока 60на выходе переноса счетчика 4 появляется сигнал. данный сигнал устанав.ливает триггер 8 в нулевое состояние.Это время определяется числом и,(й),которое было зарегистрировано счет.чиком 4 и частотой Ф, поступающейна вход счетчика 4, н равноиКД / 1За это время интегратор 2 к числуимпульсов ид досчитывает число,равное С.И (Ь 3 ) 8 ф Й Ъ ) и(13)-10 оъкт,е, содержимое интегратора увеличива-.,ется на величину площади под экстраполируемой частью диаграммы разрежения и станет равным М ц=иЬ)41+ - "кВ момент установки триггера 8 в нулевое состояние потенциал с его инверсного выхода запускает элемент задержки 17, на выходе которого появляетсясигнал, через время й задержки, равное 10-15 мин, в течение которого индикатор равномерно разменивается вкрови и амплитуда диаграммы разрежения достигает постоянного уровня, При этом средняя частота импульсов на выходе функционального преобразователя 1 также становится постоянной по величине, равное и(сЗс )==и. Импульсом с выхода элеменТазадержки 17 триггер 9 устанавливается в единичное состояние, в результате чего одновременно открываютсяинтегратор 2, элемент 2 И-ИЛИ 15 исчетчик б,.который начинает считатьимпульсы генератора 12 частоты Г,При этом на счетный вход интеграторанЪчинают поступать с выхода функционального преобразователя 1 через элемент 2 И-ИЛИ 15 импульсы частотой ИРаэ, КОТОРЫЕ ВЫЧИтаЮтСЯ ИЗ ЧИСЛа йово. В момент полного вычитания числа М в интеграторе 2 на его выходе переноса появляется импульс, который устанавливает триггер 9 в нуЛЬ- вое состояние, прекращая регистрацию частоты и. Время, в течение которого происходит полное опорожнение интегратора, определяется равенствомшв.3 оищ ирсен цоткуда тц=раин-" - 3 Известно, что отношение площадй, ограниченной первой волной циркуляции индикатора, к постоянному уровню амплитуды диаграммы разрежения после равномерного разведения индикатора в крови равно среднему времени цирку.- ляции индикатсра, которое в предложенном устройстве регистрирует счетчик б с точностью .+ 10 с.Таким образом, предлагаемое.изобретение обеспечивает определение не только площади под диаграммой разрежения, но и среднего времени циркуляции индикатора, которое является более информативным параметром, так как оно равно времени центральной циркуляции крови и используется в качестве самостоятельного показателя при оценке производительности сердца. Среднее время циркуляции индикатора является достаточно точным показателем, позволяющим оценивать степень недостаточности кровообращения, различать одышку сердечного происхождения от одышки при легочных заболеваниях, Наиболее выраженное увеличение этого показателя наблюдается при застое крови в малом круге кровообращения, Отсутствие увеличения этого показателя при сердечной недостаточности наблюдается у больных с анемией, тиреотоксикозом, лихорадкой, при которых ускоряется кровоток,Формула изобретенияУстройство для вычисления диаграмм разрежения индикаторов, содержащее Функциональный преобразователь, выход которого соединен с первыми входами 15 первого и второго элементов 2 И-ИЛИ и первого счетчика, информационный выход которого. соединен с первыми входами регистра и дешифратора, первый .и второй триггеры, первые входы кото- Щ рых соединены со входом устройства, первый выход первого триггера соединен с первым входом интегратора, первый выход которого соединен с пер,вым входом распределителя, первый выход которого соединен с первым входом первого элемента ИЛИ и вторым входом первого счетчика, второй выход распределителя соединен с первыми входами элемента И и второго элемента ИЛИ, выход которого соединен с треть-им входом первого счетчика, выход которого через элемент И соединен с вто-, рым входом распределителя, третий выход которого соединен со вторыми входами второго элемента ИЛИ и регистра, выход которого соединен с входом преобразователя код - частота, четвертый выход распределителя соединен с первым и вторым входами второго счетчика, вторыми входами дешифрато ра и первого элемента ИЛИ, выход кото-. рого соединен с четвертым входом первого счетчика, выход дешифратора соединен с вторым входом второго триггера, первый выход которого соединен совторыми входами первого и второго элементов 2 И-ИЛИ и третьим входом второго счетчика, выход которого соединенс вторым входом первого триггера, второй выход второго триггера соединен с .с третьим входом распределителя и;третьими входами первого и второгоэлементов 2 И-ИЛИ, четвертые входы которых соединены соответственно с вы-,ходами преобразователя код - частотаи генератора, а выход первого элемента 2 И-ИЛИ соединен с четвертым вхо-.дом эторого счетчика, третий счетчик,о т л и ч а ю щ е е с я тем, что, сцелью повышения достоверности, в него введены элемент задержки, третийтриггер и третий элемент 2 И-ИЛИ, причем второй выход первого триггера соединен через элемент задержки с первым входом третьего триггера, второйвход которого соединен с вторым выходом интегратора, второй вход кото-.рого соединен с первым выходом третьего триггера и первыми входами третьего элемента 2 И-ИЛИ и третьего счетчика, вторые входы которых соединенысоответственно с выходами функционального преобразователя и генератора,второй выход третьего триггера соединен с третьим входом третьего элемента 2 И-ИЛИ, четвертый вход которогосоединен с выходом второго элемента2 И-ИЛИ, а выход - с третьим входом ининтегратора.Источники инФормации,принятые во внимание при экспертизе1. Авторское свидетельство СССРпо заявке Р 2547355/18-24,кл. 6 06 Г 15/52, 1977.2 . Авторское свидетельство СССРпо заявке У 2702909/18-24,кл. О Об Г 15/52, 1978 (прототип),873245 Составитель Б. Белоусоведактор К. Волоцук Техред И,Рейвес Коррек иницкая аз 9049/75ВНИ пи 03 илиал ППП "Патент Ужгород, ул. Проектная аж 748венного комитет ретений и откр 35, Раушская на Ти Государс делам изо Москва, Ж

СмотретьЗаявка

2809337, 14.08.1979

ВСЕСОЮЗНЫЙ КАРДИОЛОГИЧЕСКИЙ НАУЧНЫЙ ЦЕНТР АМН СССР, ПРЕДПРИЯТИЕ ПЯ А-3361

ТИЩЕНКО ФЕДОР МИХАЙЛОВИЧ, РАТМАНСКИЙ АНИСИМ ЮЛЬЕВИЧ, МУРАХЛЯМОВ НУРМУХАМЕД МУХАМЕДОВИЧ, ПУШКАРЬ ЮРИЙ ТИМОФЕЕВИЧ, БЕЛОУСОВ БОРИС ЕФИМОВИЧ

МПК / Метки

МПК: G06F 15/42

Метки: вычисления, диаграмм, индикаторов, разрежения

Опубликовано: 15.10.1981

Код ссылки

<a href="https://patents.su/5-873245-ustrojjstvo-dlya-vychisleniya-diagramm-razrezheniya-indikatorov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления диаграмм разрежения индикаторов</a>