Устройство для дифференцирования частотно-импульсных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 742967

Автор: Калинников

Текст

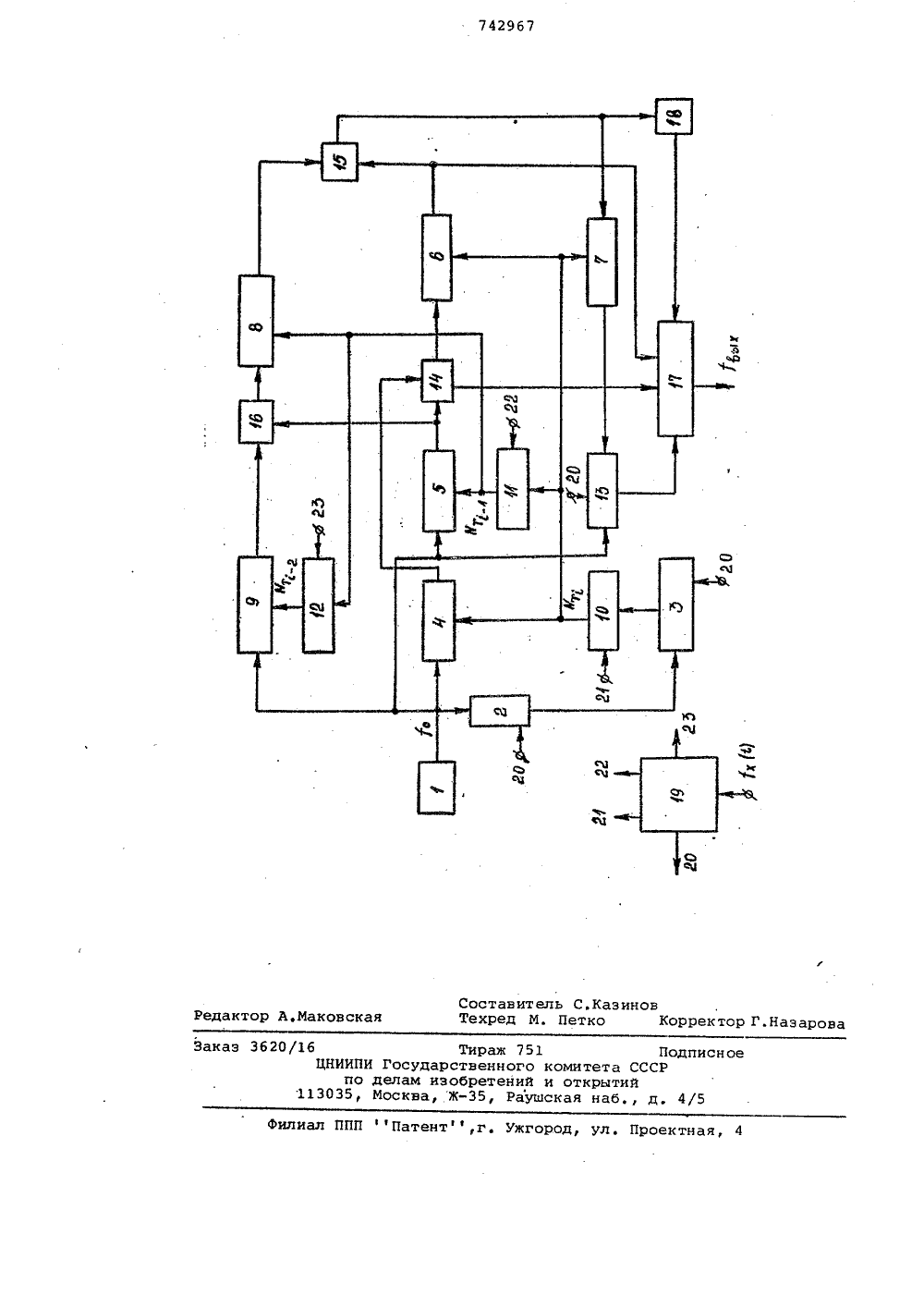

Союз Советских Социалистических РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 742967(23) Приоритет -Государственный комитет СССР по делам изобретений и открытийДата опубликования описания 250680(54) УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ ЧАСТОТНО в .ИМПУЛЬСНЫХ СИГНАЛОВ Изобретение относится к антомати" ке и вычислительной технике, в частности к устройствам для однократного диФференцирования по времени частотно-импульсных сигналов.Известно устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, счетчик, делитель частоты, генератор опорной частоты, три регистра памяти, три управляемыхделителя частоты, переключательный блок и блок вычитания импульсов 1.Известно также частотно-импульсное дифференцирующее устройство, содержащее блок управления, генератор опорной частоты, счетчики, регистры памяти, распределитель импульсов, блок вычитания, группы элементов И и ИЛИ и блоки сложения-вычитания (2,Недостатком известных устройствявляется пониженная динамическаяточность дифференцирования. 25Наиболее близкое к предлагаемомуустройство для дифференцированиячастотно-импульсных сигналов содержиттри регистра памяти, информационныйнход первого из которых соединен с выходом счетчика, подключенного счетным нходом через делитель частоты квыходу генератора опорной частотыи к счетным входам первого и второгоуправляемых делителей частоты, авыход первого регистра памяти соединен с управляющим входом перного.Упранляемого делителя частоты и информационным входом второго регистрапамяти, выход которого подключен куправляющему входу второго управляемого делителя частоты, соединенноговыходом с перным входом первого блока вычитания импульсов, выход которого подключен к счетному входутретьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делите=ля частоты, причем входы упранлениязаписью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующимвыходам блока управления, соединенного входом с входной ажной устройства, а выход счетчика подключен кинформационному входу третьего регистра памяти, соединенного выходомс управляющим входом третьего управляемого делителя частоты, выходкоторого подключен к выходнойшине устройства 31,Как и указанные выще известныеустройства, данное устройство невнбсит динамических ошибок дифференцирования только при формированиипроизводных для линейно-изменяющихсяво времени входных сигналов. Придифференцировании нелинейно-изменяющихся во времени входных сигналоввыходной сигнал устройства имеет динамическую ошибку преобразования,:увеличивающуюся от нуля до максимумавнутри каждого очередного следования входных импульсов и пропорционаяьную второй производной входногосигнала. %Цель изобретения - уменьшение динамиЧеской ошибки,,Для достижения укаэанной цели вустройство для дифференцирования частотно-импульсных сигналов, содержащеЕ три регистра памяти, информационный вход первого иэ которых соединенс выходом счетчика, подключенногосчетным входом. через делитель частотык выходу генератора опорной частоты ик счетным входам первого и второгоуправляемых делителей частоты, а выход первого регистра памяти соединенс управляющим входом первого управляемого делителя частоты и с информационным входом второго регистрапаМяти, выход которого подключен куправляющему входу второго управляемого делителя частоты, соединенноговыХодом с первым входом первогоблока вычитания импульсов, первый выход которого подключен к счетномувходу третьего управляемого делителя частоты, а второй вход соединенс выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и.обнулящие входы счетчика и делителячастоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, дополнительно введены четвертый, пятый и шестой управляемые делители частоты, второй и третий блоки вычитания импульсов, двоичныйумножитель, триггер и блок сум-мирования частот, соединенныйвыходом с выходной шиной устройства,и подключенный входами соответственно к выходу двоичного умножителя,второму выходу первого блока вычитаНия импульсов, входу третьего управляемого делителя частоты и выходутриггера, соединенного счетным входом с входом четвертого управляемогоделителя частоты и выходом второгоблока вычитания импульсов, входыкоторого подключены к выходам третье"го и пятого управляеьых делителейчастоты, причем счетный вход пятогоуправляемого делителя частоты, соединенного управляющим входом с выходом второго регистра памяти и информационным входом третьего регистра памяти, подключен к выходу третьего,блока вычитания импульсов, входы которого соединены с выходами второго ишестого управляемых делителей частоты, а счетный вход шестого управляемого делителя частоты, подключенногоуправляющим входом к выходу третьегорегистра памяти, соединен с выходомгенератора опорной частоты и первыминформационным входом двоичного умножителя, подключенного входом обнуления к соответствующему выходу блокауправления и соединенного вторым инФормационным входом с выходом четвер 15 того управляемого делителя частоты,управляющий вход которого подключенк выходу первого регистра памяти куправляющему входу третьего управляемого делителя частоты,2 О На чертеже изображена блок-схемаустройства для дифференцированиячастотно-импульсных сигналов.Устройство содержит генератор 1опорной частоты, делитель 2 частоты,счетчик 3, первый, второй, третий,четвертый, пятый и шестой управляемые делители 4-9 частоты, первый,второй и третий регистры 10-12 памяти, двоичный умножитель 13, первый,второй и третий блоки 14 - 16 вычитания импульсов, блок 17 суммирования частот, триггер 18 и блок 1 9управления, Вход блока 19 управления соединен с входной шиной устрой. ства. Выходы 20-23 блока 19 управления соединены соответственно с обнуляющими входами делителя 2 частоты,счетчика 3, двоичного умножителя13 и входами управления записьюрегистров 10-12 памяти40 Выход генератора 1 соединен сосчетными входами управляемых делителей 4, 5 и 9, первым информационным входом умножителя 13 и подключен через делитель 2 к счетномувходу счетчика 3, Выход счетчика 3соединен с информационным входомрегистра 10, подключенного выходомк управляющим входам делителей 4,6,7и к информационному входу регистра11, Выход регистра 11 соединен суправляющими входами делителей 5,и 9 с информационным входом регистра12, соединенного выходом с управляющим входом делителя 9, Выходы делителей 4 и 5 подключены к входам блока55 14 вычитания, соединенного первымвыходом со счетным входом делителя б.Выход блока 16 вычитания, подключен"ного входами к выходам делителей 5 и9,соединен со счетным входом делитео ля 8.Выходы делителей б и 8 подключеНЫ к входам блока 15 вычитания,соедИненного выходом со счетными входамитриггера 18 и делителя 7, выходкоторого подключен к второму информационному входу умножителя 13. Входыблока 17 суммирования частот, соединенного выходом с выходной шинойустройства, подключены соотнетственно к выходу умножителя 13, второмувыходу блока 14 вычитания, выходуделителя б и выходу триггера 18. 5Устройство работает следующимобразом,В блоке 19 управления из каждогоимпульса входной последовательностидифференцируемого сигнала Г(1) формируются управляющие сигналы навыходах 20-23, определяющие последовательность работы блоков устройства. С выхода генератора 1 импульсынысокой опорной частоты поступаютна вход делителя 2, счетные входыуправляемых делителей 4, 5 и 9 и первый информационный вход двоично(оумножителя 13. В делителе 2 опорнаячастота делится на постоянный коэффициент К пересчета. В делителях4, 5 и 9 опорная частота делится напеременные коэффициенты, записанные н виде параллельного кода всоответствующие регистры 10-12 памяти и обновляемые после окончаная каждого периода входной частоты,Импульсы с выхода делителя 2 поступают на счетный вход счетчика 3,где суммируются в промежутке времени, равном текущему периоду Т входного сигнала и формируемом путем подачи на обнуляющий вход счетчика 3сигналов с выхода 20 блока 19 управления после прихода каждого очередного импульса входной частоты. На 35выходе счетчика 3 в момент опроса образуется код, пропорциональный закончившемуся 1-му периоду входной частотыИ = - -Т" . 40КЭтот код перед обнулением счетчика 3 по сигналу с ныхода 21 блока 19 управления записывается н регистр 10 памяти. Перед записью. этого кода н 45 регистр 10 памяти содержащийся н регистре 10 код И пропорциональный предыдущему периоду Т - , переписывается по сигналу с выхода 22 блока управления в регистр 11 памяти. Соответственно, перед записью этого кода содержащийся в регистре 11 код Мт. , пропорциональный периоду Т тпо сигналу с выхода 23 блока управ- пения, перезаписывается в регистр 12 памяти.55Таким образом, после окончания 1-го периода входной частоты в регистре 10 памяти. записан код И ., в регистре 11 памяти - код М . ,1 а в регистре 12 - код Нт бОНа выходах упранля 8 мых делителей 4, 5 и 9 частоты Формируются соответственно частоты(, пропорциональные мгновенным значениям частот йх (1): Ех( 1 ) и Е ( ) входного сигйа ла в серединах периодон Т,(, Т; ,Т ,На первом выходе блока 14 вычитания образуется разность частот свыхода делителя 4 и выхода делителя5, которая в делителе б делится накод В ., записанный н регистре 10памятиНа выходе делителя б образуется частота1 Йх -(1-1)о Ткй)( (11),опропорциональная среднему значениюпервой производной по времени входного сигнала в 1-ом периоде. Знакэтой производной определяется знакомразности частот, формируеьым на втором выходе блока 14,В блоке 16 вычитания формируетсяразность частот с выходов делителей5 и 9 частоты. Выходная скоростьблока 16 делится в делителе 8 накод регистра 11 памяти. На выходеделителя 8 образуется частотаК(Гх(-) - Е (1-зЭ )8 й5,(1; ),пропорциональная среднему значениюпервой производной по времени входного сигнала н (1-1 -ом периоде.Частоты с выходов делителей б и 8поступают на входы блока 15 вычитания,на выходе которого образуетсяпоследовательность импульсов с час:тотой, пропорциональной приращениюсреднего значения первой производной входной частоты эа время 1-го периода. С выхода блока 16 сигнал поступает на счетный вход триггера 18,осуществляющего деление выходной)на счетный вход делителя 7, н котором выходная частота блока 16 делится на код Б . регистра 10 памяти.Частота на выходе делителя 7К йх( ) - Й (1(.) )Копропорциональна - среднему значениювторой производной по времени входного сигнала в 1-ом периоде.На информационные (счетные входысчетчиков) входы двоичного умножителя 13 поступают выходы частотыделителя 7 и генератора 1. Емкостьсчетчиков двоичного умножителя 13выбирается равной К - коэффициентуделения делителя 2. На выходе двоичного умножителя образуетсЯ последовательность импульсов со средней частотой опропорциональной текущему приращениюпервой производной, зависящему от скорости ее изменения, т.е. от второй производной входной частоты по времени.С.помощью блока 17 суммирования частот осуществляется алгебраическое (в зависимости от знака на втором выходе блока 14) суммирование частот с выхода делителя б, триггера 18 и умножителя 13, Выходной сигнал с бЛока 17 поступает на выходную шинУ устройства.Таким образом, выходной сигнал уотройства корректируется величиной пОловины приращения с выхода триггер 8 среднего значения первой производной по времени входного сигнала за время 1-го периода и ее текущим приращением с выхода умножителя 13, пропорциональным второй производной по времени входного сигнала. Благодаря этому компенсируется методическая 20 ошибка, связанная с тем, что значение.первой производной, найденное как отношение приращения входной частоты за время текущего периода, характеризует не мгновенное значение производ ной, а среднее значение за текущий период и должно быть отнесено к середине этого периода, а не к концу его.Введением текущего приращения первой производной по времени компенсируется динамическая ошибка, связанная с изменением значения первой производной за время следующего периода пропорционально второй производной входного сигнала по времени. Это позволяет уменьшить динамическую погрешность формирования сигнала, пропорциональНого первой производной входной частоты по времени. Таким образом, по Сравнению с известным устройством, 40 где выходной сигнал соответствует среднему значению первой производной по времени входной частоты за время закончившегося периода, в предлагаемом выходной сигнал соответствует мгновенному значению первой производной входной частоты по, времени. Формула изобретенияУстройство для дифференцирования 50 частотно-импульсных сигналов, содерЖащее три регистра памяти. информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель 55 частоты к выходу Генератора опорной Чистоты и к счетным вхбдам первого и второго управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом ц первого управляемого делителя частоты и с информационным входом второго ре(истра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входомпервого блока вычитания импульсов,первый выход которого подключен ксчетному входу третьего управляемогоделителя частоты, а второй входсоединен с выходом первого управляемого делителя частоты, причем входыуправления записью регистров памятии обнулящие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, о т л и ч а ю щ е е с я тем,что, с целью уменьшения динамической ошибки, в устройство дополнительно введены четвертый, пятый и шестойуправляемые делители частоты, второйи третий блоки вычитания импульсов,двоичный умножитель, триггер и блоксуммирования частот, соединенныйвыходом с выходной шиной устройстваи подключенный входами соответственно к выходу двоичного умножителя,второму выходу первого блока вычитания импульсов, входу третьего управляемого делителя частоты и выходутриггера, соединенного счетным входом с входом четвертого управляемогоделителя частоты и выходом второгоблока вычитания импульсов, входыкоторого подключены к выходам третьего и пятого управляемых делителейчастоты, причем счетный вход пятогоуправляемого делителя частоты, соединенного управляющим входом с выходомвторого регистра памяти и информационным входом третьего регистрапамяти, поцключен к выходу третьегоблока вычитания импульсов, входыкоторого соединены с выходами второгои шестого управляемых делителей частоты, а счетный вход шестого управляемого делителя частоты, подключенного управляющим входом к выходутретьего регистра памяти, соединен свыходом генератора опорной частотыи первым информационным входом двоичного умножителя, подключенного входом обнуления к соответствующему выходу блока управления и соединенноговторым информационным входом с выходом четвертого управляемого делителя частоты, управляющий вход которого подключен к выходу первого регистра памяти и управляющему входу третьего управляемого делителя частоты,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРР 495675, кл, 6 06 6 7/18, 1974.2. Авторское свидетельство СССРпо заявке Р 2506713/24,кл, 6 06 6 7/18, 1977,3. Авторское сдидетельство СССР9604008, кл. 6 06 6 7/18, 1976 (прототип),742967 Составитель С.КазиновЛ.Маковская Техред М. Петко Корректор Г.Н Редак Вака ПодписноеСР ППП фПатентф,г. Ужгород, ул. Проектн 16 ТирЦНИИПИ Государствепо делам изобре 113035, Москва, Ж751ого комитета С ний и открытий Раушская наб.,

СмотретьЗаявка

2584292, 01.03.1978

Заявитель

КАЛИННИКОВ ЮРИЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: дифференцирования, сигналов, частотно-импульсных

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/5-742967-ustrojjstvo-dlya-differencirovaniya-chastotno-impulsnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для дифференцирования частотно-импульсных сигналов</a>

Предыдущий патент: Время-импульсное делительное устройство

Следующий патент: Коррелятор

Случайный патент: Буксируемая система